JP6533129B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6533129B2 JP6533129B2 JP2015168522A JP2015168522A JP6533129B2 JP 6533129 B2 JP6533129 B2 JP 6533129B2 JP 2015168522 A JP2015168522 A JP 2015168522A JP 2015168522 A JP2015168522 A JP 2015168522A JP 6533129 B2 JP6533129 B2 JP 6533129B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- search

- match

- tcam

- control signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C15/00—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores

- G11C15/04—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores using semiconductor elements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C15/00—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores

- G11C15/04—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores using semiconductor elements

- G11C15/043—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores using semiconductor elements using capacitive charge storage elements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C15/00—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C15/00—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores

- G11C15/04—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores using semiconductor elements

- G11C15/046—Digital stores in which information comprising one or more characteristic parts is written into the store and in which information is read-out by searching for one or more of these characteristic parts, i.e. associative or content-addressed stores using semiconductor elements using non-volatile storage elements

Description

[TCAMセルの構成]

図1は、TCAMセルの構成の一例を示す回路図である。図1を参照して、TCAMセル(メモリセルMCとも称する)は、2個のSRAMセル(Static Random Access Memory Cell)11,12と、データ比較部13とを含む。SRAMセル11をXセルとも称し、SRAMセル12をYセルとも称する。Xセル11は、内部の記憶ノード対ND1,ND1_nに互いに相補となる(一方が“1”のとき他方が“0”となる)1ビット(bit)のデータを記憶する。Yセル12は、内部の記憶ノード対ND2,ND2_nに互いに相補となる1ビットのデータを記憶する。

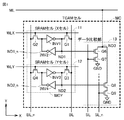

図3は、TCAM装置を構成する1つのサブアレイの構成を示すブロック図である。図3を参照して、サブアレイSAは、TCAMセルアレイ20(単にセルアレイとも称する)と、書込みドライバ21と、サーチ線(SL)ドライバ22と、マッチアンプ部23と、制御論理回路24とを含む。サブアレイSAは、さらに、図1のワード線WLX,WLYを駆動するためのワード線ドライバ(不図示)を含む。

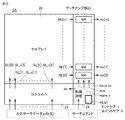

図4は、TCAM装置の構成を示すブロック図である。図4を参照して、TCAM装置100は、行列状に配列された複数のサブアレイSAと、プライオリティ・エンコーダ30と、データ入力回路31と、コマンド入力回路32とを含む。

図5は、各マッチアンプの検出結果のAND演算について説明するための図である。図5では代表的にサブアレイSA[0,0],SA[0,1]の1つのエントリのみ示されているが、他のエントリおよび他のサブアレイについても同様である。

図6は、データ検索システムの全体構成を示すブロック図である。図6のブロック図は、インターネットなどのネットワーク用のルータに設けられたデータ検索システム120の構成を示す。

図7は、ACLルールファイルの一例を表形式で示す図である。図7では、ACLが3行のみ示されているが、実際にはより多数の行によってACLルールファイルが構成される。図7に示すように、ACLは、ネットワークから入力されたパケットのプロトコル番号、宛先ポート番号、送信元ポート番号、宛先IPアドレス、および送信元IPアドレスをチェックするためのものである。これらのチェック要素は、範囲指定が可能となっている。

第1の実施形態では、TCAM装置内のサーチ結果が自明な領域、具体的にはドントケア(don't care)データ領域のサーチ動作を停止させながらも、正常なサーチ結果を出力する技術が提供される。これによって、従来技術において無駄に消費してしまう電流を削減することができるので、より低消費電力なTCAM装置ならびにTCAM装置を用いたデータ検索システムを提供することができる。以下、図面を参照して具体的に説明する。

図10は、第1の実施形態によるTCAM装置において、サブアレイの構成を示すブロック図である。図10を参照して、図10のサブアレイSAは、レジスタREG1をさらに含む点で、図3のサブアレイSAと異なる。図10では、レジスタREG1は、制御論理回路24の内部に設けられているように図示しているが、制御論理回路24の外部に設けられていても構わない。図10のその他の構成は図3の場合と同様であるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。図10ではデータ検索に関する部分を主として記載しているので、データ書込みに関する書込みドライバ21は図示していない。

図11は、図10の制御論理回路のうち、サーチ動作に関係する部分の構成を示す回路図である。図10および図11を参照して、制御論理回路24は、レジスタREG1と、インバータ42,47,48と、ANDゲート43,49,51と、Dフリップフロップ44,45と、遅延段50とを含む。レジスタREG1は、Dフリップフロップ40と、ANDゲート41とを含む。

図12は、図10のサーチ線ドライバの構成の一例を示す回路図である。図10および図12を参照して、サーチ線ドライバ22は、サーチ線イネーブル信号sleが“H”レベルに活性化されたときに、入力サーチデータsd[i](i=0,1,…,k)をサーチ線SL[i]に出力するとともに、入力サーチデータsd[i]の論理レベルを反転した信号を相補のサーチ線SL_n[i]に出力する。

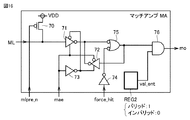

図13は、図10のマッチアンプの構成の一例を示す回路図である。図10および図13を参照して、マッチアンプMAは、プリチャージ回路としてのPチャネルMOSトランジスタ70と、インバータ71〜74と、論理ゲート(NANDゲート)75とを含む。図13では、プリチャージ回路としてのMOSトランジスタ70がマッチアンプMAの内部にあるように図示しているが、MOSトランジスタ70はマッチアンプMAの外部に設けられていても構わない。

以下、ある1つのサブアレイにおけるサーチ動作の例について、図14および図15のタイミング図を参照して説明する。

図14は、図10のサブアレイに設けられたレジスタREG1に非ドントケアを表す“0”が格納されているときのサーチ動作を示すタイミング図である。図14において、各サイクルはクロック信号clkのポジティブエッジから次のポジティブエッジまでの期間である。制御論理回路24から出力される制御信号force_hitは、“L”レベルである。

図15は、図10のサブアレイに設けられたレジスタREG1にドントケアを表すデータ“1”が格納されているときのサーチ動作を示すタイミング図である。

たとえば、図9のTCAM装置のサブアレイSA[15,1],SA[15,2],SA[15,3]については、データが格納されていないインバリッドエントリを含んでいる。すなわち、これらのサブアレイの各行は、全てのセルデータがドントケアに設定されているか、インバリッドエントリに該当するかのいずれかである。したがって、各行(エントリ)のサーチ結果は自明である。このような場合においても、図10の制御論理回路24内のレジスタREG1を“H”レベル(“1”)に設定することによって、当該サブアレイではサーチ動作を行わないようにすることによって、低消費電力化を図ることができる。ただし、これらのサブアレイのうちインバリッドエントリに該当する行に関しては、マッチアンプMAがサーチ結果として“L”レベル(ミス)を出力するように変更する必要がある。

上記の実施形態によれば、サーチ結果が自明なサブアレイは、サーチ動作を行わないようにしたうえで、当該サブアレイから正常なサーチ結果を出力するように制御できる。具体的に、サブアレイに含まれるすべてのTCAMセルのデータがドントケアである場合には、各マッチアンプMAからヒットを表わす“H”レベルの信号が出力される。サブアレイの各行が、全てドントケアのセルデータによって構成されているか、インバリッドエントリに該当するかのいずれかである場合には、ドントケアの場合に対応するマッチアンプMAからヒットを表す“H”レベルの信号が出力され、インバリッドエントリの場合に対応するマッチアンプからミスを表す“L”レベルの信号が出力される。この結果、当該サブアレイの各マッチアンプMAは、マッチ線のプリチャージ電流および動作電流を発生しないので、TCAM装置の消費電力を低減させることができる。

[TCAMサブアレイの構成]

図17は、第2の実施形態によるTCAM装置において、サブアレイSAの構成を示すブロック図である。図17に示すサブアレイSAは、列方向(Y方向)の両端に配置された2個の制御論理回路24A,24Bと、列方向(Y方向)の両端に配置された2個のサーチ線ドライバ22A,22Bとを含む点で、図10のサブアレイSAと異なる。図17では図示していないが、書込みドライバについても列方向(Y方向)の両端に配置されている。

上記の構成のサブアレイを備えたTCAM装置によれば、第1の実施形態のTCAM装置と同様の効果を奏するとともに、さらに次のような効果を奏する。まず、第1の実施形態の図10の構成のサブアレイに比べて、総エントリ(行)数が半分の領域に対してドントケア領域か否かの設定が可能になる。したがって、ドントケア領域が比較的小さなACLルールファイルに対しても省電力化を図ることができる。

たとえば、図9のサブアレイSA[6,1],SA[13,1]については、サブアレイ内の全ての行のTCAMセルがドントケアに設定されているわけではないので、図10および図11で説明したレジスタREG1を“H”レベル(“1”)に設定することはできない。しかしながら、一部の行のTCAMセルについては全てドントケアに設定されているので、これらの一部の行についてはサーチ結果がヒットになることは自明である。

図18は、第3の実施形態によるTCAM装置において、マッチアンプMAの構成を示す回路図である。図18のマッチアンプMAは、レジスタREG3、ORゲート77、ANDゲート78、およびインバータ79をさらに含む点で、図13のマッチアンプMAと異なる。さらに、図18のマッチアンプMAは、インバータ74に代えてNORゲート80を含む点で図13のマッチアンプMAと異なる。

以下、図18〜図21を参照して、レジスタREG3へのデータ設定方法について説明する。

図22は、図18のマッチアンプMAの変形例を示すブロック図である。図22のマッチアンプMAは、対応する行がデータの格納されていないインバリッドエントリの場合にも適用可能なものである。

上記のとおり、サブアレイ内の全てのセルデータがドントケアでない場合であっても、全セルデータがドントケアである行(以下、「ドントケアエントリ」と称する)を含んでいる場合、もしくは、データが設定されていないインバリッドエントリを含んでいる場合には、当該行のサーチ結果は自明である。このような場合には、当該行(ドントケアエントリまたはインバリッドエントリ)のマッチ線MLのプリチャージ動作が停止され、マッチアンプMAの回路動作が停止される。これによって、TCAM装置の消費電力を低減させることができる。そして、ドントケアエントリに対応するマッチアンプMAからの出力信号を“H”レベル(ヒット)に固定し、インバリッドエントリに対応するマッチアンプMAからの出力信号を“L”レベル(ミス)に固定することによって、正常なサーチ動作を行うことができる。

第4の実施形態のTCAM装置では、図10および図11で説明した、サブアレイ全体のサーチ動作を停止可能するためのレジスタREG1が設けられていない場合について説明する。この場合、図18および図22で説明したマッチアンプMAごとに設けられているレジスタREG3の設定値に基づいて、サブアレイ全体のサーチ動作を停止するか否かが判定される。以下、図面を参照して詳しく説明する。

図23は、第4の実施形態によるTCAM装置において、サブアレイの構成を模式的に示すブロック図である。図23のサブアレイSAは、制御論理回路24内のレジスタREG1が設けられておらず、このレジスタREG1に代えて論理積回路27が設けられている点で、図10のサブアレイSAと異なる。図23のその他の構成は図10と同様であるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

図24は、図23の制御論理回路24において、検索動作に関係する部分の構成を示す回路図である。図24の制御論理回路24は、レジスタREG1を含まない点で図11の制御論理回路24と異なる。図24の場合、インバータ42への入力される制御信号force_hitは、図23の論理積回路27から与えられる。

上記の構成によれば、サブアレイ内の全てのセルデータがドントケアに設定されており、これによって、サブアレイ内の行ごとに設けられたレジスタREG3が全てドントケアに設定されている場合には、自動的にサブアレイのサーチ動作を停止することができる。図19〜図21で説明したように、レジスタREG3の値の設定については、データ判定回路33を用いて自動的に行うことができるので、レジスタREG1の値を設定するために、TCAM装置へのデータ書込み後にTCAMセルデータの内容を解析する必要がないというメリットがある。

[バッファアンプ部の構成について]

図25は、制御論理回路24からの出力信号のために用いられるバッファアンプの配置について説明するための図である。

図26は、第5の実施形態のTCAM装置において、バッファアンプ部の構成を説明するための図である。図26のバッファアンプ部84は、低消費電力化のために、図25のバッファアンプ部84の構成を変更したものである。

図27は、電源立ち上げ後において、各レジスタREG1,REG2,REG3へのデータ書込みの手順について説明するための図である。図27では、3つのサブアレイSA[0,0],SA[1,0],SA[2,0]が代表的に示されている。各サブアレイには、図10および図11で説明したレジスタREG1が制御論理回路24に設けられ、図18および図22で説明したレジスタREG2,REG3が行ごとに設けられる。

上述した第1〜第6の実施形態で説明したTCAM装置の低消費電力化技術は、各サブアレイのマッチ線MLに接続されたTCAMセルが全てドントケア(don't care)に設定されている場合にのみ適用することができる。したがって、ドントケアに設定された比較的多数のTCAMセルが連続して並んでいたとしても、これらのTCAMセルが2つのマッチ線に跨っており、各マッチ線には“1”または“0”に設定されたTCAMセルも含まれている場合には、前述した低消費電力化技術を適用することはできない。

第1〜第7の実施形態では、全サブアレイがほぼ同じタイミングでサーチ動作を行い、各サブアレイの出力信号に基づいてプライオリティ・エンコーダがサーチ結果を出力していた。第8の実施形態では、行方向に並ぶ(よって、共通のエントリに対応する)複数のサブアレイがパイプライン方式で順番に検索を行うように構成された例を開示する。この場合、各サブアレイは、前段のサブアレイのサーチ動作の終了後にサーチ動作を開始する。

Claims (16)

- 各々がTCAM(Ternary Content Addressable Memory)セルアレイを含む複数のサブアレイを備え、

各前記サブアレイは、前記TCAMセルアレイの行ごとに格納された複数のデータのうち、入力されたサーチデータの対応部分に一致するものを検索し、前記行ごとに一致または不一致という検索結果を出力し、

各前記サブアレイは、前記TCAMセルアレイの全てのデータがドントケアであることに基づいて検索動作前にあらかじめ設定された、対応する第1の制御信号が活性化されている場合には、前記TCAMセルアレイについて検索を行わずに、一致という検索結果を前記行ごとに出力する、半導体装置。 - 各前記サブアレイは、

前記TCAMセルアレイの行にそれぞれ設けられ、対応する行の各TCAMセルが接続された複数のマッチ線と、

前記TCAMセルアレイの列にそれぞれ設けられた複数のサーチ線と、

検索時に、前記複数のサーチ線に前記サーチデータの対応部分を供給するサーチ線ドライバと、

前記複数のマッチ線にそれぞれ対応し、各々が検索時に、対応するマッチ線の電位に従って検索結果を出力する複数のマッチアンプと、

前記複数のマッチ線にそれぞれ対応し、各々が検索時に、対応するマッチ線をプリチャージする複数のプリチャージ回路と、

制御論理回路とを含み、

前記制御論理回路は、前記第1の制御信号が活性化されている場合には、前記サーチ線ドライバおよび前記複数のプリチャージ回路が動作しないように制御し、

各前記マッチアンプは、前記第1の制御信号が活性化されている場合には、対応する前記マッチ線の電位によらず一致という検索結果を出力するように構成される、請求項1に記載の半導体装置。 - 各前記サブアレイは、前記第1の制御信号を出力する第1のレジスタを含む、請求項2に記載の半導体装置。

- 各前記サブアレイは、前記TCAMセルアレイの行ごとに設けられ、各々が、第2の制御信号を出力する複数の第2のレジスタを含み、

前記マッチアンプは、対応する前記第2の制御信号が活性化されている場合には、前記第1の制御信号が活性化されていても、不一致という検索結果を出力するように構成される、請求項3に記載の半導体装置。 - 各前記サブアレイは、前記TCAMセルアレイの行ごとに設けられ、各々が第3の制御信号を出力する複数の第3のレジスタを含み、

各前記プリチャージ回路は、対応する前記第3の制御信号が活性化されている場合には、前記第1の制御信号が活性化されていなくても、対応する前記マッチ線をプリチャージせず、

各前記マッチアンプは、対応する前記第3の制御信号が活性化されている場合には、前記第1の制御信号が活性化されていなくても、対応する前記マッチ線の電位によらず一致という検索結果を出力する、請求項3に記載の半導体装置。 - 各前記サブアレイは、

前記TCAMセルアレイの行ごとに設けられ、各々が、第2の制御信号を出力する複数の第2のレジスタと、

前記TCAMセルアレイの行ごとに設けられ、各々が、第3の制御信号を出力する複数の第3のレジスタとを含み、

各前記プリチャージ回路は、対応する前記第2および第3の制御信号の少なくとも一方が活性化されている場合には、前記第1の制御信号が活性化されていなくても、対応する前記マッチ線をプリチャージせず、

各前記マッチアンプは、対応する前記第2の制御信号が活性化されておらず、対応する前記第3の制御信号が活性化されている場合には、前記第1の制御信号が活性化されていなくても、対応する前記マッチ線の電位によらず一致という検出結果を出力し、

各前記マッチアンプは、対応する前記第2の制御信号が活性化されている場合には、前記第1の制御信号および対応する前記第3の制御信号のいずれかが活性化されていても、対応する前記マッチ線の電位によらず不一致という検出結果を出力する、請求項3に記載の半導体装置。 - 前記TCAMセルアレイは、列方向に並ぶ第1のセルアレイと第2のセルアレイとに区分され、

前記サーチ線ドライバは、

前記第1のセルアレイに隣接して設けられ、前記第1のセルアレイに前記サーチデータの対応部分を供給する第1のドライバと、

前記第2のセルアレイに隣接して設けられ、前記第2のセルアレイに前記サーチデータの対応部分を供給する第2のドライバとを含む、請求項2に記載の半導体装置。 - 前記半導体装置は、

各前記サブアレイを構成する前記TCAMセルアレイの行ごとにデータを書込む際に、共通のマッチ線に接続された全てのTCAMセルにドントケアが書込まれた特定行があるか否かを判定するデータ判定回路をさらに備え、

前記データ判定回路は、前記特定行に対応する前記第3の制御信号が活性化されるように、前記特定行に対応する前記第3のレジスタの値を設定する、請求項5に記載の半導体装置。 - 各前記サブアレイは、さらに、

前記TCAMセルアレイの行ごとに設けられ、各々が、第3の制御信号を出力する複数の第3のレジスタと、

前記複数の第3のレジスタからそれぞれ出力された複数の前記第3の制御信号が全て活性化されている場合に、活性化された前記第1の制御信号を生成して出力する論理回路とを含む、請求項2に記載の半導体装置。 - 前記制御論理回路は、各前記プリチャージ回路の動作を制御するためのプリチャージイネーブル信号を生成し、

各前記サブアレイは、前記TCAMセルアレイの複数行ごとに設けられ、各々が、前記プリチャージイネーブル信号および前記第1の制御信号を整形し、整形後の前記プリチャージイネーブル信号および前記第1の制御信号を前記複数行に対応する前記プリチャージ回路および前記マッチアンプにそれぞれ供給する複数のバッファアンプ部をさらに含み、

各前記バッファアンプ部は、対応する前記複数行に設けられた前記第3のレジスタが出力する前記第3の制御信号が全て活性化されている場合には、出力する整形後の前記第1の制御信号を活性化するともに、出力する整形後の前記プリチャージイネーブル信号を非活性化することによって対応する各前記プリチャージ回路が動作しないように制御する、請求項5に記載の半導体装置。 - 前記半導体装置への電源供給後、いずれの前記サブアレイの前記TCAMセルにもデータが書き込まれていない状態において、各前記サブアレイの前記第1の制御信号および複数の前記第2の制御信号がいずれも活性状態となるように、各前記第1のレジスタおよび各前記第2のレジスタの値が初期設定される、請求項4に記載の半導体装置。

- 前記半導体装置への電源供給後、いずれの前記サブアレイの前記TCAMセルにもデータが書き込まれていない状態において、各前記サブアレイの前記第1の制御信号および複数の前記第3の制御信号がいずれも活性状態となるように、各前記第1のレジスタおよび各前記第3のレジスタの値が初期設定される、請求項5に記載の半導体装置。

- 前記半導体装置への電源供給後、いずれの前記サブアレイの前記TCAMセルにもデータが書き込まれていない状態において、各前記サブアレイの前記第1の制御信号および各前記サブアレイの前記第2の制御信号および複数の前記第3の制御信号がいずれも活性状態となるように、各前記第1のレジスタおよび各前記第2のレジスタおよび各前記第3のレジスタの値が初期設定される、請求項6に記載の半導体装置。

- 各前記サブアレイの前記TCAMセルアレイへの書込みデータの配列順および前記サーチデータの配列順を定められた規則に従って変更するデータ配列変更回路をさらに備える、請求項1に記載の半導体装置。

- 互いに行方向に並び、共通のエントリに対応する複数の前記サブアレイは、パイプライン方式で順番に検索を行うように構成され、

各前記サブアレイは、最初のステージで検索を行うサブアレイを除いて、前記TCAMセルアレイの行ごとに設けられ、各々が、前ステージのサブアレイの対応する行の検索結果を格納する複数のDフリップフロップを含み、

前記複数のDフリップフロップが設けられた各前記サブアレイにおいて、各前記プリチャージ回路は、対応する前記Dフリップフロップに不一致の検索結果が格納されている場合には、対応する前記マッチ線をプリチャージせず、

前記複数のDフリップフロップが設けられた各前記サブアレイにおいて、各前記マッチアンプは、対応する前記Dフリップフロップに不一致の検索結果が格納されている場合には、前記第1の制御信号が活性化されていても、不一致の検索結果を出力するように構成される、請求項2に記載の半導体装置。 - 前記サブアレイから出力された検索結果に基づいて、前記サーチデータの検索結果を出力するプライオリティ・エンコーダをさらに備える、請求項1に記載の半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015168522A JP6533129B2 (ja) | 2015-08-28 | 2015-08-28 | 半導体装置 |

| US15/227,161 US9824757B2 (en) | 2015-08-28 | 2016-08-03 | Semiconductor device including TCAM cell arrays capable of skipping TCAM-cell search in response to control signal |

| CN201610743715.5A CN106486159B (zh) | 2015-08-28 | 2016-08-26 | 半导体器件 |

| US15/787,406 US10068646B2 (en) | 2015-08-28 | 2017-10-18 | Semiconductor device including TCAM cell arrays capable of skipping TCAM-cell search in response to control signal |

| US16/056,321 US10366755B2 (en) | 2015-08-28 | 2018-08-06 | Semiconductor device including TCAM cell arrays capable of skipping TCAM-cell search in response to control signal |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015168522A JP6533129B2 (ja) | 2015-08-28 | 2015-08-28 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017045495A JP2017045495A (ja) | 2017-03-02 |

| JP2017045495A5 JP2017045495A5 (ja) | 2018-06-21 |

| JP6533129B2 true JP6533129B2 (ja) | 2019-06-19 |

Family

ID=58095691

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015168522A Active JP6533129B2 (ja) | 2015-08-28 | 2015-08-28 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (3) | US9824757B2 (ja) |

| JP (1) | JP6533129B2 (ja) |

| CN (1) | CN106486159B (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6533129B2 (ja) | 2015-08-28 | 2019-06-19 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2018206452A (ja) | 2017-05-30 | 2018-12-27 | ルネサスエレクトロニクス株式会社 | 内容参照メモリ及び半導体装置 |

| JP2019117678A (ja) * | 2017-12-27 | 2019-07-18 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US10910056B2 (en) | 2018-02-22 | 2021-02-02 | Renesas Electronics Corporation | Semiconductor device |

| JP2020047351A (ja) * | 2018-09-20 | 2020-03-26 | 株式会社東芝 | Camマクロ回路および半導体集積回路 |

| CN109637571B (zh) * | 2018-12-21 | 2020-11-20 | 成都海光集成电路设计有限公司 | 三态内容可寻址存储器搜索线分割控制装置、系统和方法 |

| TWI794510B (zh) * | 2019-06-12 | 2023-03-01 | 聯華電子股份有限公司 | 三元內容可定址記憶體單元 |

| US10930348B1 (en) * | 2019-08-13 | 2021-02-23 | Hewlett Packard Enterprise Development Lp | Content addressable memory-encoded crossbar array in dot product engines |

| US11404121B2 (en) * | 2019-10-22 | 2022-08-02 | Mediatek Singapore Pte. Ltd. | Methods for writing ternary content addressable memory devices |

| US11894054B2 (en) | 2019-10-22 | 2024-02-06 | Mediatek Singapore Pte. Ltd. | Methods for writing ternary content addressable memory devices |

| CN110993005B (zh) * | 2019-12-11 | 2021-03-26 | 海光信息技术股份有限公司 | 电路结构、芯片、训练方法及训练装置 |

| US11133065B1 (en) | 2020-03-06 | 2021-09-28 | Micron Technology, Inc. | Architecture for ternary content-addressable memory search |

| US11599090B2 (en) * | 2020-09-30 | 2023-03-07 | Rockwell Automation Technologies, Inc. | System and method of network synchronized time in safety applications |

| US11967377B2 (en) * | 2021-01-08 | 2024-04-23 | Mediatek Singapore Pte. Ltd. | Dynamically gated search lines for low-power multi-stage content addressable memory |

| TWI744204B (zh) * | 2021-03-15 | 2021-10-21 | 瑞昱半導體股份有限公司 | 適用於內容可定址記憶體的遮蔽電路與預充電電路 |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR950008676B1 (ko) * | 1986-04-23 | 1995-08-04 | 가부시기가이샤 히다찌세이사꾸쇼 | 반도체 메모리 장치 및 그의 결함 구제 방법 |

| JP2585227B2 (ja) * | 1986-07-25 | 1997-02-26 | 株式会社日立製作所 | 半導体メモリ装置 |

| JPH10275479A (ja) * | 1997-03-31 | 1998-10-13 | Kawasaki Steel Corp | 連想メモリおよびネットワークフレーム中継器 |

| JP3478749B2 (ja) * | 1999-02-05 | 2003-12-15 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 連想メモリ(cam)のワードマッチラインのプリチャージ回路および方法 |

| JP2002197873A (ja) * | 2000-12-27 | 2002-07-12 | Kawasaki Microelectronics Kk | 連想メモリ |

| JP2003272386A (ja) * | 2002-03-20 | 2003-09-26 | Mitsubishi Electric Corp | Tcamセル、tcamセルアレイ、アドレス検索メモリおよびネットワークアドレス検索装置 |

| JP4541077B2 (ja) * | 2004-01-13 | 2010-09-08 | 株式会社日立超エル・エス・アイ・システムズ | 半導体記憶装置 |

| US20080006280A1 (en) * | 2004-07-20 | 2008-01-10 | Anthony Aliberto | Magnetic navigation maneuvering sheath |

| BRPI0607430B8 (pt) * | 2005-02-14 | 2021-06-22 | Johnson & Johnson Vision Care | dispositivo oftálmico confortável e métodos de sua produção |

| JP4343859B2 (ja) * | 2005-02-17 | 2009-10-14 | 株式会社日立製作所 | 半導体装置 |

| US7274581B1 (en) * | 2006-05-04 | 2007-09-25 | Texas Instruments Incorporated | Array fault testing approach for TCAMs |

| US7414872B2 (en) * | 2006-09-12 | 2008-08-19 | Jinn-Shyan Wang | Segmented search line circuit device for content addressable memory |

| US7760135B2 (en) * | 2007-11-27 | 2010-07-20 | Lockheed Martin Corporation | Robust pulse deinterleaving |

| US7940541B2 (en) * | 2008-05-21 | 2011-05-10 | Texas Instruments Incorporated | Bit cell designs for ternary content addressable memory |

| US7881090B2 (en) * | 2009-03-16 | 2011-02-01 | Netlogic Microsystems, Inc. | Content addressable memory (CAM) array capable of implementing read or write operations during search operations |

| US8320148B1 (en) * | 2009-06-25 | 2012-11-27 | Adesto Technologies Corporation | PMC-based non-volatile CAM |

| JP5477621B2 (ja) * | 2009-08-03 | 2014-04-23 | ルネサスエレクトロニクス株式会社 | 連想メモリ |

| JP2011181147A (ja) * | 2010-03-02 | 2011-09-15 | Renesas Electronics Corp | 連想記憶装置 |

| CN101859596A (zh) * | 2010-06-02 | 2010-10-13 | 中国科学院声学研究所 | 一种内容可寻址存储器 |

| JP5893465B2 (ja) * | 2012-03-27 | 2016-03-23 | ルネサスエレクトロニクス株式会社 | 連想記憶装置 |

| US8891273B2 (en) * | 2012-12-26 | 2014-11-18 | Qualcomm Incorporated | Pseudo-NOR cell for ternary content addressable memory |

| US9275735B2 (en) * | 2014-01-06 | 2016-03-01 | International Business Machines Corporation | Array organization and architecture to perform range-match operations with content addressable memory (CAM) circuits |

| JP6533129B2 (ja) * | 2015-08-28 | 2019-06-19 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP6592310B2 (ja) * | 2015-09-01 | 2019-10-16 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

-

2015

- 2015-08-28 JP JP2015168522A patent/JP6533129B2/ja active Active

-

2016

- 2016-08-03 US US15/227,161 patent/US9824757B2/en active Active

- 2016-08-26 CN CN201610743715.5A patent/CN106486159B/zh active Active

-

2017

- 2017-10-18 US US15/787,406 patent/US10068646B2/en active Active

-

2018

- 2018-08-06 US US16/056,321 patent/US10366755B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US10068646B2 (en) | 2018-09-04 |

| JP2017045495A (ja) | 2017-03-02 |

| US20170062051A1 (en) | 2017-03-02 |

| US20180040373A1 (en) | 2018-02-08 |

| CN106486159B (zh) | 2021-10-26 |

| US20180350439A1 (en) | 2018-12-06 |

| US9824757B2 (en) | 2017-11-21 |

| CN106486159A (zh) | 2017-03-08 |

| US10366755B2 (en) | 2019-07-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6533129B2 (ja) | 半導体装置 | |

| US7848129B1 (en) | Dynamically partitioned CAM array | |

| US7894227B2 (en) | Content addressable memory | |

| US6961810B2 (en) | Synchronous content addressable memory | |

| EP3675127B1 (en) | Content addressable memory | |

| US20080144345A1 (en) | Semiconductor memory device | |

| CN114175160A (zh) | 具有突发模式地址比较器的sram | |

| US6385070B1 (en) | Content Addressable Memory array, cell, and method using 5-transistor compare circuit and avoiding crowbar current | |

| US7035968B1 (en) | Content addressable memory with range compare function | |

| US10297291B2 (en) | Semiconductor device | |

| US10373684B2 (en) | Semiconductor device | |

| WO1999023663A1 (en) | Synchronous content addressable memory with single cycle operation | |

| US20160358654A1 (en) | Low-power ternary content addressable memory | |

| US8023300B1 (en) | Content addressable memory device capable of parallel state information transfers | |

| US11017858B1 (en) | Low power content addressable memory | |

| Raju et al. | A low power content addressable memory with self-control mechanism and segmented matchlines | |

| Sulthana et al. | DIFFERENTIAL 10T TCAM WITH PARALLEL PAI-SIGMA MATCHLINE | |

| Ijjada et al. | Ultra low power Tri-CAM designs for high speed processors | |

| CN117941000A (en) | Pseudo-dual port SRAM with burst mode address comparator | |

| BABU et al. | An Efficient Novel Precharge-Free, Low-Power Content-Addressable Memory |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180510 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180510 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180912 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180918 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190226 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190415 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190514 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190523 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6533129 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |