JP6485019B2 - 半導体発光素子 - Google Patents

半導体発光素子 Download PDFInfo

- Publication number

- JP6485019B2 JP6485019B2 JP2014244157A JP2014244157A JP6485019B2 JP 6485019 B2 JP6485019 B2 JP 6485019B2 JP 2014244157 A JP2014244157 A JP 2014244157A JP 2014244157 A JP2014244157 A JP 2014244157A JP 6485019 B2 JP6485019 B2 JP 6485019B2

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- semiconductor layer

- insulating film

- light emitting

- type semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/832—Electrodes characterised by their material

- H10H20/833—Transparent materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/831—Electrodes characterised by their shape

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/831—Electrodes characterised by their shape

- H10H20/8312—Electrodes characterised by their shape extending at least partially through the bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/832—Electrodes characterised by their material

- H10H20/835—Reflective materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/84—Coatings, e.g. passivation layers or antireflective coatings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

- H10H20/032—Manufacture or treatment of electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/819—Bodies characterised by their shape, e.g. curved or truncated substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/832—Electrodes characterised by their material

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/544—Solar cells from Group III-V materials

Landscapes

- Led Devices (AREA)

Description

特許文献1では、各電極と半導体層との間には絶縁膜が設けられており、電極と半導体層との間は複数の貫通電極によって導通されている。しかしながら、遮光面積を減らすためにn側電極及びp側電極を互いに重ねているので、貫通電極と各電極とを接続しにくい。そこで、各電極に、発光面と平行な面内に延在する突出部を複数設けて、この突出部において貫通電極と接続している。なお、n側電極の突出部とp側電極の突出部は、発光面側から観察したときに互いに重ならないように配置されている。

そこで、本発明は、光取出し効率の高い半導体発光素子を提供することを目的とする。

n型又はp型のいずれか一方の第1導電型半導体層、発光層及び他方の第2導電型半導体層を、下面側から上面側に向かって順に有し、前記上面側から光を取り出す半導体発光素子であって、

前記第1導電型半導体層上に設けられ、第1パッド部と、前記第1パッド部から延伸する第1延伸部と、を有する第1電極と、

前記第1延伸部を覆う第1絶縁膜と、

前記第2導電型半導体層の上面に接続され、前記第1絶縁膜上に延在する透光性電極と、

前記第1絶縁膜上において前記透光性電極に接続された第2電極であって、第2パッド部と、前記第2パッド部から前記第1延伸部に沿って延伸し前記第1延伸部と重なるように配置された第2延伸部と、を有する第2電極と、

を備えることを特徴とする。

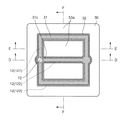

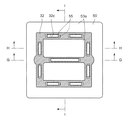

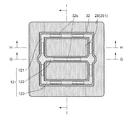

図1〜2に示す本発明に係る発光素子1は、特に、発光素子1の上面1a側から光を取り出すような実装形態(いわゆる、フェースアップ実装)に適した発光素子1である。本実施の形態の第1の特徴は、発光素子1の上面1a側から観察したときに、第2電極20の第2延伸部22が第1電極10の第1延伸部12と重なるように配置されていることである(図1、図2(a)〜図2(c))。第2の特徴は、第2電極20が第1絶縁膜31の上側に形成されており、第2電極20と第2導電型半導体層53との導通は、第2導電型半導体層53の上面53aから第1絶縁膜31上まで延在された透光性電極25を介して行われることである(図2(a)〜図2(c))。

図1〜図2に示す発光素子1は、下面1b側に基板60が配置され、上面1a側に半導体積層体50が配置されている。また、半導体積層体50の上面には、発光素子1に通電するための電極10、20が形成されている。

本実施の形態では、n型半導体層51とn側延伸部12とが接触することにより、n型半導体層51とn側電極10とが電気的に接続される。n側パッド部11は、n側延伸部12の上に設けられている(図2(a))。

上記第1絶縁膜31はさらに、露出部55の側面55cを覆ってもよい。なお、側面55cを確実に絶縁するために、露出部55を超えて、露出部55近傍のp型半導体層53の上面53aまで第1絶縁膜31を延在させてもよい。

そして、n側延伸部12と露出部55の側面55cとの間は、第1絶縁膜31によって絶縁されている。これにより、n側延伸部12が、側面55cに露出した活性層52及び/又はp型半導体層53に接触するのを確実に回避できる。

この透光性電極25は、さらに第1絶縁膜31上に延在して、発光素子1の上面1aのほぼ全面を覆っている(図1)。なお、透光性電極25には開口25cが設けられており、その内径は、第1絶縁膜31の開口31cの内径より大きくされている。そして、透光性電極25には開口25cから、第1絶縁膜31の開口31c全体が露出するように位置決めすることにより、透光性電極25とn側電極10(n側延伸部12及びn側パッド部11)とが接触するのを回避することができる(図1、図2(a))。

p側電極20は、第1絶縁膜31上において透光性電極に接続されている。図1に示されているように、p側延伸部22は、n側延伸部12に沿って延伸している。そして、p側延伸部22は、発光素子1の上面1aから見たときにp側延伸部22とn側延伸部12とが重なるように配置されている(図1、図2(a)〜図2(c))。なお、p側パッド部21の直下にも、n側電極10が存在していてよい。

これに対して、本発明では、p側電極20の少なくとも一部がn側電極10と重なるように設けることにより、p側電極20の少なくとも一部には光が到達しない。これにより、n側電極10とp側電極20の面積を減らすことなしに、遮光面積だけを低減でき、その結果として光取出し効率を向上することができる。

n型窒化物半導体用のn側電極には、例えばAlなどの反射率の高い金属材料を利用できる。よって、n側電極の反射率を高めて、n電極に到達する光の吸収を抑制し、最終的な光取出し効率を高めることができる。

その一方、p型窒化物半導体のp側電極には、以下の理由から、Alを使用するのが困難である。p型窒化物半導体の電気抵抗が高いため、そのほぼ全面に電極を接触させる必要があり、多くの場合に導電性酸化物(例えばITO)から成る透光性電極を設けている。Alから成るp側電極をこの透光性電極に接触させると、透光性電極との接触面からAlが酸化して絶縁化(Al2O3化)し、透光性電極とp側電極との間が絶縁されるおそれがある。

このような理由から、p側電極には、反射率の高い金属材料を用いることができない。よって、(低反射率材料から形成した)p側電極に光が到達すると、p側電極による光吸収が生じて、光取出し効率が低下する。

これに対して、本実施の形態の発光素子1によれば、p側電極に到達する光が低減されるので、p側電極を低反射率材料から形成した場合であっても、p側電極による光吸収が確実に低減できるので、光取出し効率を向上させることができる。

特に、窒化物半導体発光素子の場合、p型窒化物半導体層が高抵抗であるので、p型窒化物半導体層とp側貫通電極との接触抵抗は特に高くなるだろう。なお、引用文献1にはp型窒化物半導体層の上面に透光性電極を形成できることが開示されているものの、透光性電極を形成する導電性酸化物材料(例えばITO)は、金属材料に比べれば十分に抵抗が高い。従って、小直径の貫通電極を用いる限りは、発光素子の電気抵抗を顕著に低減できる効果は期待できない。

なお、本実施の形態の発光素子1では、p側電極20は、第1絶縁膜31を介してn側電極10上に形成されているので、p側電極20及びn側電極10の形状や形成位置を、互いの位置関係等に制限されずに決定することができる。よって、発光強度分布を考慮して、p側電極20及びn側電極10の各々を、発光素子1の中心線に対して線対称に形成して、発光強度の面内均一性を向上することもできる。

これは、p側パッド部21は、強発光領域(通常は発光素子1の中央付近)から遠く離れた位置、例えば発光素子の縁部近傍に形成することもできるのに対して、p側延伸部22は強発光領域に十分な電流を拡散するため、発光素子の中央近傍にも形成され得るためである。例えば、本実施の形態では、p側延伸部222は、発光素子1の中央を横切っている。このように、p側延伸部22はp側パッド部21に比べて遮光作用が顕著になりやすい。よって、p側延伸部22の大部分をn側電極10と重ねることにより、遮光面積を低減することができ、これにより、光取出し効率を効率よく向上させることができる。

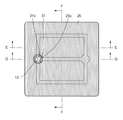

図3〜図4に示すように、基板60の上面60a上にn型半導体層51、発光層52及びp型半導体層53をこの順に形成して半導体積層体50を形成した後、p型半導体層53及び発光層52を部分的に除去して、n型半導体層51が露出した露出部55を形成する。本実施の形態では、露出部55は溝状部分であり(図4(b)、図4(c))、上面視すると所定の形状を描いている(図3)。この実施の形態における露出部55は、図3の上面視においては、略正方形に延在する第1の部分と、前記第1の部分のうち対向する2辺(図3では、左右に離間して、上下方向に延びている平行な2辺)の中点を繋ぐように左右方向に延びている第2の部分と、第1の部分と第2の部分との交点に設けられた円形部分とを有している。

例えば、上述したように、基板60上に半導体積層体50を均一に積層した後に、p型半導体層53及び発光層52をエッチング等により部分的に除去する方法である。この方法は技術的に確立されているので、比較的実施しやすい利点がある。

別の方法としては、基板60上に半導体積層体50を形成する際に、基板60の上面60aの全面にn型半導体層51を形成した後、発光層52及びp型半導体層53が形成されない部分(これが後に露出部55になる)が残るように、発光層52及びp型半導体層53を所定のパターンで形成する方法がある。この方法は、発光層52及びp型半導体層53を部分的に除去する工程が不要になる反面、発光層52及びp型半導体層53を所定パターンで成長させるための特殊な操作が必要になる。

図5〜図6に示すように、露出部55の底面から露出したn型半導体層51の上にn側延伸部12(121〜123)を形成する。ここで、n側延伸部12を3つの符号121〜123で表示しているが、上面図(図5等)と断面図(図6等)との間のn側延伸部12の対応関係を明確にするためである。

n側延伸部12を露出部55内に設けることにより、n型半導体層51とn側延伸部12とが電気的に接続される。なお、n型半導体層51とn側延伸部12とが電気的に接続されていればよいので、図6に示すようにn型半導体層51の上にn側延伸部12を直接形成する以外に、n型半導体層51とn側延伸部12との間に導電性の部材を介在させてもよい。

図7〜図8に示すように、露出部55内に設けられたn側延伸部12を覆うように、第1絶縁膜31を形成する。第1絶縁膜31には、n側延伸部12を部分的に露出させるための開口31cが設けられている。この第1絶縁膜31は、n側延伸部12をp側の電極(p側電極20及び透光性電極25)から絶縁するものである。また、これらp側及びn側の電極が露出部55の側面55cに接触することを防止するために、第1絶縁膜31は、さらに露出部55の側面55cを覆うことが好ましい。なお、このときに、側面55cを確実に絶縁するために、第1絶縁膜31を、露出部55を超えて、露出部55近傍のp型半導体層53の上面53aまで延在させてもよい。

また、上記「2.n側延伸部12の形成」で説明したように、n側延伸部12の形成の際には、n側延伸部12と露出部55の側面55cとの間に隙間を設けている。第1絶縁膜31を形成する際に、この隙間も第1絶縁膜31で埋めることにより、n側延伸部12と側面55cとの間を確実に絶縁することができる。

図9〜図10に示すように、p型半導体層53の上面53aと第1絶縁膜31の上面31aをほぼ全て覆うように、透光性電極25を形成する。これにより、透光性電極25は、p型半導体層53の上面53aと接続し、且つ第1絶縁膜31上に延在した状態となる。

透光性電極25には開口25cが設けられており、その内径は、第1絶縁膜31の開口31cの内径より大きくされている。そして、透光性電極25には開口25cから、第1絶縁膜31の開口31c全体が露出するように位置決めされている。これにより、透光性電極25の開口25c及び第1絶縁膜31の開口31cを通して、n側延伸部12を部分的に露出し、且つn側延伸部12に透光性電極25が接触するのを回避できる。

透光性電極25がITO等の導電性酸化物からなる場合は、透光性電極25を形成した後に、透光性電極25とp型半導体層53との間の接触抵抗の低減と、透光性電極25の透明度の上昇のために、熱処理を行い得る。なお、熱処理は、透光性電極25を形成した後で、発光素子1が完成するまでのどの段階で行ってもよい。例えば、p側電極20を形成する前に熱処理を行う。

図1〜2に示すように、透光性電極25上にp側電極20(p側パッド部21及びp側延伸部22)を形成して、p側電極20を透光性電極25に接続する。このとき、p側延伸部22は、n側延伸部12に沿って延伸した形状で形成されており(図1)、第1絶縁膜31を介してn側延伸部12と重なるように配置されている(図1、図2)。この例では、p側パッド部21とp側延伸部22とは、同時に、一体として形成しているが、これに限定されない。例えば、p側パッド部21とp側延伸部22とを異なる厚さにする場合や、異なる金属で形成する場合には、別々の工程で形成してもよい。また、p側パッド部21を厚く形成するためにまずはp側パッド部21とp側延伸部22とを同時に形成し、その後にp側パッド部21上だけに、追加の金属層を形成してもよい。

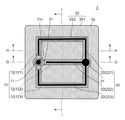

図11〜12に図示した本実施の形態に係る発光素子2は、露出部55の形態を変更した点と、それに付随して、第1絶縁膜31に加えて第2絶縁膜32を設けた点で、実施の形態1の発光素子1と相違する。その他の点は、実施の形態1の発光素子1とほぼ同様である。実施の形態1との相違点を中心に、以下に詳述する。

第2の絶縁膜32を設ける際には、露出部55の位置に合わせて(より正確には、露出部55内に露出したn型半導体層51の位置に合わせて)開口32cを設ける必要がある。この開口32cを通して、n側延伸部12は露出部55内に露出したn型半導体層51に接続することができる。

n側パッド部11の直下において、n側延伸部12がn型半導体層51と接続していると、n側パッド部11に通電されたときに、電流がn側パッド部11からそのまま直下のn型半導体層51に流れやすい。そのため、n側パッド部11近傍の発光強度が高くなりやすく、発光強度分布の均一性が低下する可能性がある。そこで、n側パッド部11の直下には露出部55を設けないことにより(つまり、n側パッド部11を、第1絶縁膜31を介してp型半導体層53上に配置することにより)、n側パッド部11の近傍における強発光を抑制して、均一な発光強度分布に近づけることができる。

また、p側パッド部21も、第1絶縁膜31上に配置されていることにより、p側パッド部21からそのまま直下のp型半導体層53に電流が流れることがないので、p側パッド部21の直下に電流が集中するのを抑制して、発光強度を均一な分布に近づけることができる。

実施の形態1と同様に、基板60の上面60aに半導体積層体50を形成し、次いでp型半導体層53及び発光層52を部分的に除去して露出部55を形成する(図13〜図14)。但し、露出部55の形態については実施の形態1とは異なり、分離した複数の露出部55として形成している(図13〜図14)。

実施の形態1とは異なり、第2絶縁膜32を形成する。第2絶縁膜32は、n側延伸部12を配線する経路上において、露出部55の側面55cとp型半導体層53の上面53aとを覆うように設けられる(図15〜図16)。第2絶縁膜32には、各露出部55の位置に合わせて開口32cが設けられている。後で設けられるn側延伸部12は、この開口32cを通して、各露出部55から露出しているn型半導体層51に接続することができる。

実施の形態1と同様に、n側延伸部12(121〜123)を形成する(図17〜図18)。但し、n側延伸部12は、露出部55の底面から露出したn型半導体層51上だけでなく、露出部55の側面55cとp型半導体層53の上面53aとを覆う第2絶縁膜32の上にも形成される点で、実施の形態1と異なる。上述した通り、n側延伸部12は、第2絶縁膜32に設けた開口32cを通して、各露出部55内でn型半導体層51と電気的に接続される。

実施の形態1と同様に、n側延伸部12を覆うように、第1絶縁膜31を形成する(図19〜図20)。但し、本実施の形態の第1絶縁膜31は、露出部55の内部に設けられたn側延伸部12のみならず、第2絶縁膜32を介してp型半導体層53上に設けられたn側延伸部12も覆っている。第1絶縁膜31には、n側延伸部12を部分的に露出させるための開口31cが設けられている。

実施の形態1と同様に、p型半導体層53の上面53aと第1絶縁膜31の上面31aを全て覆うように、透光性電極25を形成する(図21〜図22)。本実施の形態の透光性電極25は、上面視において、第2絶縁膜32もほぼ覆うように形成されている(図22)。

また、実施の形態1と同様に、透光性電極25には開口25cが設けられており、その開口25cから、透光性電極25の開口25c及び第1絶縁膜31の開口31cを通して、n側延伸部12を部分的に露出している(図22(a))。

実施の形態1と同様に、p側電極20(p側パッド部21及びp側延伸部22)と、n側パッド部11とを形成する。但し、n側パッド部11は、第2絶縁膜32を介してp型半導体層53の上面53a上に形成され、p側パッド部21は、第2絶縁膜32、n側延伸部12、第1絶縁膜31、透光性電極25を介してp型半導体層53の上面53a上に形成されている。

なお、n側延伸部12の一部が、第2絶縁膜32を介してp型半導体層53上に形成されているので、第2絶縁膜32に亀裂や隙間等があった場合には、n側延伸部12がp型半導体層53に短絡しやすい。また、絶縁膜を2回に分けて形成するため、製造工程が1回増えている。これらの点では、実施の形態1のほうが有利であるといえる。

図23〜図24に図示した本実施の形態に係る発光素子3は、透光性電極25を2回(第1透明導電層251、第2透明導電層252)に分けて形成する点で、実施の形態2の発光素子2と相違する。その他の点は、実施の形態2の発光素子2とほぼ同様である。実施の形態2との相違点を中心に、以下に詳述する。

また、本発明のような発光素子の形態では、n側延伸部12の上面側に透光性電極25を備えているので、n側延伸部12の形成後に、透光性電極25を形成する必要がある。

よって、本実施の形態に係る発光素子3により、電力効率と光取出し効率とを向上することができる。

実施の形態2と同様に、基板60の上面60aに半導体積層体50を形成し、次いでp型半導体層53及び発光層52を部分的に除去して露出部55を形成する(図25〜図26)。

実施の形態2と同様に、第2絶縁膜32を形成する。第2絶縁膜32は、n側延伸部12を配線する経路上において、露出部55の側面55cとp型半導体層53の上面53aとを覆うように設けられる(図27〜図28)。第2絶縁膜32には、各露出部55の位置に合わせて開口32cが設けられている。

実施の形態2とは異なり、p型半導体層53の上面53aを覆うように、ITO等の導電性酸化物からなる第1透明導電層251を形成する(図29〜図30)。図に示すように、後で形成される第2透明導電層252との接触を確実にするために、第1透明導電層251は、第2絶縁膜32の外縁部上まで延在させてもよい。

第1透明導電層251を形成した後に、第1透明導電層251とp型半導体層53との間の接触抵抗を低減するために、第1の温度(例えば400〜650℃)で熱処理を行う。第1の温度は十分に高いので、当該第1の温度での熱処理により、第1透明導電層251の透明度上昇も同時に行うことができる。

実施の形態2と同様に、n側延伸部12(121〜123)を形成する(図31〜図32)。n側延伸部12は、第2絶縁膜32に設けた開口32cを通して、各露出部55内でn型半導体層51と電気的に接続される。

なお、n型半導体層51が第1透明導電層251と接触しないように、n型半導体層51と第1透明導電層251との間に隙間を空けておく。

実施の形態2と同様に、n側延伸部12を覆うように、第1絶縁膜31を形成する(図33〜図34)。第1絶縁膜31には、n側延伸部12を部分的に露出させるための開口31cが設けられている。なお、第1絶縁膜31を形成する際に、n型半導体層51と第1透明導電層251との間の隙間も第1絶縁膜31で埋めることにより、n型半導体層51と第1透明導電層251との間を確実に絶縁することができる(図34(c))。

実施の形態2と異なり、第1絶縁膜31の上面31aを覆うように、ITO等の導電性酸化物からなる第2透明導電層252を形成する(図35〜図36)。p型半導体層53の上面53aには、第1透明導電層251が既に設けられているので、第1透明導電層251をさらに第2透明導電層252で覆う必要はない。但し、第1透明導電層251を第2透明導電層252に接触させて、導通させる必要はある。第1透明導電層251が、第2絶縁膜32の外縁部まで延在していると、第2絶縁膜32を第2透明導電層252で覆うことにより、第2透明導電層252を第1透明導電層251に接触させることができる。また、第1透明導電層251と第2透明導電層252との間の接続を確実にするために、第1透明導電層251の外縁部に第2透明導電層252の外縁部を重ねることもできる(図36(b)、(c))。

実施の形態2と同様に、p側電極20(p側パッド部21及びp側延伸部22)と、n側パッド部11とを形成する(図23〜図24)。

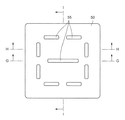

図37〜図38に図示した本実施の形態に係る発光素子4は、n側電極10とp側電極20の形態を変更している点で実施の形態3の発光素子3と相違する。また、p側電極20のp側パッド部21の直下に、半導体積層体50、n側電極10及びp側電極20から完全に絶縁された金属反射膜40を設けた点も相違する。その他の点は、実施の形態3の発光素子2とほぼ同様である。実施の形態3との相違点を中心に以下に詳述する。

金属反射膜40は、下面の反射率が高い膜である。例えば、半導体積層体50で発光した光に対する反射率の高い金属材料(例えばAl)から成る層を少なくとも下面近傍に有する。金属反射膜40は、第2絶縁膜32上に形成された島状の部材であり(図45)、第1絶縁膜31で覆われている(図38(c)、図47、図48)。よって、金属反射膜40は、n型半導体層51及びp型半導体層53から絶縁されている。さらに、金属反射膜40はn側電極10から分離されているので(図45、図46)、n側電極10からも絶縁されている。すなわち、本実施の形態では、金属反射膜40は、n型半導体層51及びp型半導体層53を含む半導体積層体50からも、n側電極10及びp側電極20からも絶縁されている。

金属反射膜40がp側パッド部21と重なって配置されているので、p側パッド部21に金属ワイヤをワイヤボンドしたときに、金属反射膜40がワイヤボンドの衝撃を緩和して、半導体積層体50へのダメージを軽減し得る。また、ワイヤボンドの際の衝撃で、p側パッド部21直下の第1絶縁膜31に亀裂や隙間等が生じることを仮定すると、p側パッド部21が金属反射膜40に接触する可能性がある。ここで、金属反射膜40はn側電極10や半導体積層体50から絶縁されているので、p側パッド部21が金属反射膜40に接触したとしても、短絡を生じるおそれがない。そして、金属反射膜40とp側パッド部21とがほぼ重なっているので、p側パッド部21に到達する光を低減することができる。

実施の形態2〜3と同様に、基板60の上面60aに半導体積層体50を形成し、次いでp型半導体層53及び発光層52を部分的に除去して複数の露出部55を形成する(図39〜図40)。但し、露出部55の形態については実施の形態2〜3とは異なり、帯状の4つの露出部55を形成している(図39)。

実施の形態2〜3と同様に、第2絶縁膜32を形成する。第2絶縁膜32は、n側延伸部12を配線する経路上において、露出部55の側面55cとp型半導体層53の上面53aとを覆うように設けられる(図41〜図42)。第2絶縁膜32には、各露出部55の位置に合わせて開口32cが設けられている。

実施の形態3と同様に、p型半導体層53の上面53aを覆うように、第1透明導電層251を形成する(図43〜図44)。

第1透明導電層251がITO等の導電性酸化物からなる場合は、第1透明導電層251を形成した後に、第1透明導電層251とp型半導体層53との間の接触抵抗を低減するために、第1の温度(例えば400〜650℃)で熱処理を行う。

実施の形態3と同様に、n側延伸部12を形成する(図45〜図46)。n側延伸部12は、第2絶縁膜32に設けた開口32cを通して、各露出部55内でn型半導体層51と電気的に接続される。

なお、n型半導体層51が第1透明導電層251と接触しないように、n型半導体層51と第1透明導電層251との間に隙間を空けておく。

本実施の形態では実施の形態3と異なり、n側延伸部12の形成の際に、n側延伸部12と分離した金属反射膜40も形成する。金属反射膜40は、例えば、n側延伸部12と同じ材料を用いて同時に形成する。金属反射膜40は、第2絶縁膜32上に形成されており、n型半導体層51とも、p型半導体層53とも絶縁されている。

実施の形態3と同様に、n側延伸部12を覆うように、第1絶縁膜31を形成する(図47〜図48)。第1絶縁膜31には、n側延伸部12を部分的に露出させるための開口31cが設けられている。また、実施の形態3とは異なり、第1絶縁膜31は金属反射膜40も覆っている。

なお、第1絶縁膜31を形成する際に、n型半導体層51と第1透明導電層251との間の隙間も第1絶縁膜31で埋めることにより、n型半導体層51と第1透明導電層251との間を確実に絶縁することができる(図48(a))。さらに、n側延伸部12と金属反射膜40との隙間も第1絶縁膜31で埋めることにより、n側延伸部12と金属反射膜40との間を確実に絶縁することができる(図48(c))。

実施の形態3と同様に、第1絶縁膜31の上面31aを覆うように、第2透明導電層252を形成する(図49〜図50)。

実施の形態3と同様に、p側電極20(p側パッド部21及びp側延伸部22)と、n側パッド部11とを形成する(図37〜図38)。

n側電極10を構成するn側延伸部12とn側パッド部11とは、同一の材料から形成することもできるが、異なる材料から形成してもよい。例えば、後述するp側電極20と同様に、n側延伸部12とn側パッド部11を、同一の材料から一体に形成することもできる。

n側電極10は、下面における反射率が高いことが好ましい。具体的には、半導体積層体50で発光した光に対する反射率の高い金属材料からなる層を、n側電極10の下面(n側延伸部12の下面)付近に有することが好ましい。また、n側延伸部12の上面を覆う第1絶縁膜31が剥離するのを抑制するために、n側延伸部12の上面は絶縁材料(例えばSiO2)との密着性に優れた金属材料であるとより好ましい。例えば、n側延伸部12を複数の金属層からなる多層構造とし、下面付近に高反射率の下側金属層を配置し、最上面に第1絶縁膜31との密着性に優れた上側金属層を配置する。下側金属層に好適な材料としてはAl、Agが挙げられる。上側金属層に好適な材料としてはTi、Ni、Cr、Alが挙げられる。

n側延伸部12を構成する金属積層構造体の一例として、n型半導体層51側から順に、Al、Ti、Pt、Tiを積層した構造がある。

n側パッド部11は、金属ワイヤ等の外部接続に用いる部材との密着性に優れた金属材料を最表面に備えることが好ましい。好適な材料としては、Auが挙げられる。

n側延伸部12とn側パッド部11を別体で設ける場合には、n側延伸部12の最表面に第1絶縁膜31との密着性に優れた金属材料(例えばTi)を用い、n側パッド部11の最表面には金属ワイヤ等との密着性に優れた金属材料(例えばAu)を用いることができるので、第1絶縁膜31との密着性と金属ワイヤ等との密着性の両方に優れたn側電極10を形成することができる。

p側電極20を構成するp側延伸部22とp側パッド部21とは、同一の金属材料から形成することができる。例えば、p側延伸部22とp側パッド部21を一体に形成する。p側電極20には、透光性電極25との接触抵抗が低い金属材料が好適である。p側電極20を複数の金属層からなる多層構造で形成する場合には、最下層の金属層を、このような金属材料で構成する。また、最表面は、n側電極10と同様に、金属ワイヤ等との密着性に優れた金属材料で構成することが好ましい。

p側電極20は、例えば、p型半導体層52側から順に、Ti、Rh、Auを積層して形成することができる。

また、透光性電極25とp型半導体層53とが直接接触する領域は半導体発光素子の主要な光取り出し面であるので、p側電極20は上面視においてこの領域と重ならないように設けることが好ましい。具体的には、p側電極20は第1絶縁膜31上にのみ形成することが好ましい。

透光性電極25は、透光性の導電材料から形成することができ、特に、導電性酸化物が好適である。導電性酸化物としては、例えば、ZnO、In2O3、ITO、SnO2、MgOが挙げられる。特にITOは、可視光(可視領域)において高い光透過性を有し、導電率の高い材料であることから好ましい。

第1絶縁膜31、第2絶縁膜32は、絶縁膜からなるものであって、特に酸化膜からなるものが好ましい。第1絶縁膜31、第2絶縁膜32は、例えば、二酸化ケイ素(SiO2)やZr酸化膜(ZrO2)から形成することができる。また、第2絶縁膜32は、誘電体反射膜、例えばSiO2/Nb2O5からなる多層膜でもよい。第2絶縁膜32が誘電体反射膜であれば、半導体積層体50内で伝播する光を第2絶縁膜32で反射できるので、n側延伸部12における光の吸収を低減することができる。第2絶縁膜32が反射膜である場合は、遮光面積の増大を防ぐため、図15等に示すように、n側延伸部12と同様の形状で形成することが好ましい。

半導体積層体50は、様々な半導体材料から形成することができる。例えば、一般式がInxAlyGa1−x−yN(0≦x≦1、0≦y≦1、0≦x+y≦1)で示される窒化ガリウム系化合物半導体から形成することができる。当該一般式で示される具体的な半導体としては、例えば、GaN、AlGaN、InGaN、AlGaInN等が挙げられる。

n型半導体層51は、例えば、n型不純物としてSiやGe、O等を含む窒化ガリウム系化合物半導体から形成することができる。

発光層52は、例えば、InGaNから形成することができる。

p型半導体層53は、例えば、p型不純物としてMgを含む窒化ガリウム系化合物半導体から形成することができる。

半導体積層体50は、n型半導体層51、発光層52、p型半導体層53の他にも層を含んでいてよい。例えば、n型不純物及びp型不純物を含有せずに形成したアンドープ層を含んでいてもよい。

基板60としては、典型的には、C面、A面、R面のいずれかを主面とするサファイア(A12O3)等の絶縁性基板を用いる。また、SiC(6H、4H、3C)、シリコン、ZnS、ZnO、GaAs、窒化物半導体基板(GaN、AlN等)等を用いることもできる。

基板60の表面60aは平面であってもよいが、半導体積層体50の内部で繰り返し反射される光を効率よく外部に取り出すために、凹凸を設けてもよい。

なお、本明細書の開示内容は、以下の態様を含み得る。

(態様1)

n型又はp型のいずれか一方の第1導電型半導体層、発光層及び他方の第2導電型半導体層を、下面側から上面側に向かって順に有し、前記上面側から光を取り出す半導体発光素子であって、

前記第1導電型半導体層上に設けられ、第1パッド部と、前記第1パッド部から延伸する第1延伸部と、を有する第1電極と、

前記第1延伸部を覆う第1絶縁膜と、

前記第2導電型半導体層の上面に接続され、前記第1絶縁膜上に延在する透光性電極と、

前記第1絶縁膜上において前記透光性電極に接続された第2電極であって、第2パッド部と、前記第2パッド部から前記第1延伸部に沿って延伸し前記第1延伸部と重なるように配置された第2延伸部と、を有する第2電極と、

を備えることを特徴とする半導体発光素子。

(態様2)

上面視において、前記第2電極の90%以上が前記第1電極と重なっていることを特徴とする態様1に記載の半導体発光素子。

(態様3)

前記第1電極は、前記第1導電型半導体層が露出した露出部上に形成されていることを特徴とする態様1又は2に記載の半導体発光素子。

(態様4)

前記第1電極は、前記露出部上から前記第2導電型半導体層の前記上面まで延在しており、

前記半導体発光素子は、前記第1電極と前記第2導電型半導体層との間に形成され、前記第1電極と前記第2導電型半導体層とを絶縁する第2絶縁膜をさらに備えることを特徴とする態様3に記載の半導体発光素子。

(態様5)

前記第1パッド部は、前記第2絶縁膜を介して前記第2導電型半導体層上に配置されていることを特徴とする態様4に記載の半導体発光素子。

(態様6)

前記第2パッド部は、上面視において前記第1電極と重ならない位置に配置されており、

前記半導体発光素子は、前記第2パッド部の直下に、前記第1導電型半導体層及び前記第2導電型半導体層から絶縁された金属反射膜をさらに備えることを特徴とする態様1〜5のいずれか1つに記載の半導体発光素子。

(態様7)

前記第1延伸部は下側金属層から形成され、

前記第1パッド部は前記下側金属層上に設けられた上側金属層から形成されていることを特徴とする態様1〜6のいずれか1つに記載の半導体発光素子。

(態様8)

前記第1延伸部及び前記第2延伸部の少なくともいずれか一方は、同じ方向に延伸する部分を複数有することを特徴とする態様1〜7のいずれか1つに記載の半導体発光素子。

(態様9)

第1導電型半導体層、発光層及び第2導電型半導体層をこの順に形成する工程と、

前記第2導電型半導体層及び前記発光層を部分的に除去して前記第1導電型半導体層が露出した露出部を形成し、前記露出部と接続された第1電極であって、第1パッド部と、前記第1パッド部から延伸する第1延伸部と、を有する第1電極を形成する工程と、

前記第1延伸部を覆う第1絶縁膜を形成する工程と、

前記第2導電型半導体層の上面に接続し且つ前記第1絶縁膜上に延在する透光性電極を形成する工程と、

前記第1絶縁膜上において前記透光性電極に接続された第2電極であって、第2パッド部と、前記第2パッド部から前記第1延伸部に沿って延伸し前記第1延伸部と重なるように配置された第2延伸部と、を有する第2電極を形成する工程と、を含むことを特徴とする半導体発光素子の製造方法。

(態様10)

前記透光性電極を形成する工程は、

前記第2導電型半導体層の上面に導電性酸化物からなる第1透明導電層を形成し、第1の温度で熱処理する工程と、

前記第1透明導電層と前記第2電極とを接続するように前記第1絶縁膜上に導電性酸化物からなる第2透明導電層を形成し、前記第1の温度よりも低温の第2の温度で熱処理する工程と、を含み、

前記第1の温度で熱処理する工程は、前記第1電極を形成する工程及び前記第2電極を形成する工程より前に行い、

前記第2の温度で熱処理する工程は、前記第1電極を形成する工程及び前記第2電極を形成する工程より後に行うことを特徴とする態様9に記載の半導体発光素子の製造方法。

10 第1電極(n側電極)

11 第1パッド部(n側パッド部)

12 第1延伸部(n側延伸部)

20 第2電極(p側電極)

21 第2パッド部(p側パッド部)

22 第2延伸部(p側延伸部)

25 透光性電極

31 第1絶縁膜

32 第2絶縁膜

50 半導体積層体

51 第1導電型半導体層(n型半導体層)

52 発光層

53 第2導電型半導体層(p型半導体層)

55 露出部

60 基板

Claims (9)

- n型又はp型のいずれか一方の第1導電型半導体層、発光層及び他方の第2導電型半導体層を、下面側から上面側に向かって順に有する半導体積層体を含み、前記上面側から光を取り出す半導体発光素子であって、

前記第1導電型半導体層上に設けられ、第1パッド部と、前記第1パッド部から延伸する第1延伸部と、を有する第1電極と、

前記第1延伸部を覆う第1絶縁膜と、

前記第2導電型半導体層の上面に接続され、前記第1絶縁膜上に延在する透光性電極と、

前記第1絶縁膜上において前記透光性電極に接続された第2電極であって、第2パッド部と、前記第2パッド部から前記第1延伸部に沿って延伸し前記第1延伸部と重なるように配置された第2延伸部と、を有する第2電極と、

前記第2導電型半導体層上に設けられた第2絶縁膜と、

を備え、

前記半導体積層体は、前記第2導電型半導体層側に、前記第1導電型半導体層を露出させる露出部を有し、

前記第1延伸部は、前記露出部内に露出した前記第1導電型半導体層上から、前記第2絶縁膜を介して前記第2導電型半導体層上まで延在して配置されており、

前記第1パッド部は、前記第2絶縁膜を介して前記第2導電型半導体層上に配置され、

前記第2パッド部は、前記第1絶縁膜を介して前記第1電極上に配置されたことを特徴とする半導体発光素子。 - 上面視において、前記第2電極の90%以上が前記第1電極と重なっていることを特徴とする請求項1に記載の半導体発光素子。

- 前記露出部は複数設けられており、複数の前記露出部の合計面積は、前記半導体発光素子の全体の面積の10%以下である、請求項1または2に記載の半導体発光素子。

- 前記第1導電型半導体層はn型半導体層であり、前記第2導電型半導体層はp型半導体層である、請求項1〜3のいずれか1項に記載の半導体発光素子。

- 前記第1延伸部は下側金属層から形成され、

前記第1パッド部は前記下側金属層上に設けられた上側金属層から形成されていることを特徴とする請求項1〜4のいずれか1項に記載の半導体発光素子。 - 前記第1延伸部及び前記第2延伸部の少なくともいずれか一方は、同じ方向に延伸する部分を複数有することを特徴とする請求項1〜5のいずれか1項に記載の半導体発光素子。

- 第1導電型半導体層、発光層及び第2導電型半導体層をこの順に形成する工程と、

前記第2導電型半導体層及び前記発光層を部分的に除去して前記第1導電型半導体層が露出した露出部を形成する工程と、

前記露出部と接続された第1電極であって、第1パッド部と、前記第1パッド部から延伸する第1延伸部と、を有する第1電極を形成する工程と、

前記第1延伸部を覆う第1絶縁膜を形成する工程と、

前記第2導電型半導体層の上面に接続し且つ前記第1絶縁膜上に延在する透光性電極を形成する工程と、

前記第1絶縁膜上において前記透光性電極に接続された第2電極であって、第2パッド部と、前記第2パッド部から前記第1延伸部に沿って延伸し前記第1延伸部と重なるように配置された第2延伸部と、を有する第2電極を形成する工程と、を含み、

さらに、前記第1電極を形成する工程より前に、前記第2導電型半導体層上に第2絶縁膜を形成する工程を含み、

前記第1延伸部は、前記露出部に露出した前記第1導電型半導体層上から、前記第2絶縁膜を介して前記第2導電型半導体層上まで延在して配置されており、

前記第1パッド部は、前記第2絶縁膜を介して前記第2導電型半導体層上に配置され、

前記第2パッド部は、前記第1絶縁膜を介して前記第1電極上に配置されたことを特徴とする半導体発光素子の製造方法。 - 前記透光性電極を形成する工程は、

前記第2導電型半導体層の上面に導電性酸化物からなる第1透明導電層を形成し、第1の温度で熱処理する工程と、

前記第1透明導電層と前記第2電極とを接続するように前記第1絶縁膜上に導電性酸化物からなる第2透明導電層を形成し、前記第1の温度よりも低温の第2の温度で熱処理する工程と、を含み、

前記第1の温度で熱処理する工程は、前記第1電極を形成する工程及び前記第2電極を形成する工程より前に行い、

前記第2の温度で熱処理する工程は、前記第1電極を形成する工程及び前記第2電極を形成する工程より後に行うことを特徴とする請求項7に記載の半導体発光素子の製造方法。 - 前記第2透明導電層は、前記第1絶縁膜及び前記第2絶縁膜の上にのみ形成する、請求項8に記載の半導体発光素子の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014244157A JP6485019B2 (ja) | 2013-12-19 | 2014-12-02 | 半導体発光素子 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013262438 | 2013-12-19 | ||

| JP2013262438 | 2013-12-19 | ||

| JP2014244157A JP6485019B2 (ja) | 2013-12-19 | 2014-12-02 | 半導体発光素子 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019028016A Division JP6870695B2 (ja) | 2013-12-19 | 2019-02-20 | 半導体発光素子 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015135951A JP2015135951A (ja) | 2015-07-27 |

| JP2015135951A5 JP2015135951A5 (ja) | 2018-01-18 |

| JP6485019B2 true JP6485019B2 (ja) | 2019-03-20 |

Family

ID=52146178

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014244157A Active JP6485019B2 (ja) | 2013-12-19 | 2014-12-02 | 半導体発光素子 |

| JP2019028016A Active JP6870695B2 (ja) | 2013-12-19 | 2019-02-20 | 半導体発光素子 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019028016A Active JP6870695B2 (ja) | 2013-12-19 | 2019-02-20 | 半導体発光素子 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US9123865B2 (ja) |

| EP (1) | EP2887408B1 (ja) |

| JP (2) | JP6485019B2 (ja) |

| KR (1) | KR102299959B1 (ja) |

| CN (1) | CN104733599B (ja) |

| AU (1) | AU2014277727B2 (ja) |

| TW (1) | TWI649898B (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9847457B2 (en) | 2013-07-29 | 2017-12-19 | Seoul Viosys Co., Ltd. | Light emitting diode, method of fabricating the same and LED module having the same |

| KR102409964B1 (ko) * | 2015-08-04 | 2022-06-16 | 삼성전자주식회사 | 반도체 발광소자 및 제조방법 |

| KR20170018201A (ko) * | 2015-08-06 | 2017-02-16 | 삼성전자주식회사 | 반도체 발광소자 및 제조방법 |

| US9530934B1 (en) * | 2015-12-22 | 2016-12-27 | Epistar Corporation | Light-emitting device |

| CN105742418A (zh) * | 2016-03-18 | 2016-07-06 | 华灿光电股份有限公司 | 一种发光二极管芯片及其制作方法 |

| DE102016112587A1 (de) * | 2016-07-08 | 2018-01-11 | Osram Opto Semiconductors Gmbh | Strahlungsemittierender Halbleiterchip |

| KR102707425B1 (ko) * | 2017-01-06 | 2024-09-20 | 서울바이오시스 주식회사 | 전류 차단층을 가지는 발광 소자 |

| TWI790984B (zh) * | 2017-01-26 | 2023-01-21 | 晶元光電股份有限公司 | 發光元件 |

| US11024770B2 (en) * | 2017-09-25 | 2021-06-01 | Nichia Corporation | Light emitting element and light emitting device |

| EP3561884A1 (en) * | 2018-04-26 | 2019-10-30 | Nichia Corporation | Light-emitting device |

| JP7054430B2 (ja) * | 2018-04-26 | 2022-04-14 | 日亜化学工業株式会社 | 発光素子 |

| DE102018119438A1 (de) * | 2018-08-09 | 2020-02-13 | Osram Opto Semiconductors Gmbh | Optoelektronischer halbleiterchip, optoelektronisches bauteil und verfahren zur herstellung eines optoelektronischen bauteils |

| DE102018124341B4 (de) * | 2018-10-02 | 2024-05-29 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Bauelement mit vergrößerter aktiver Zone und Verfahren zur Herstellung |

| CN109817781A (zh) * | 2019-01-31 | 2019-05-28 | 深圳第三代半导体研究院 | 一种正装集成单元发光二极管 |

| TWD219684S (zh) * | 2021-07-09 | 2022-07-01 | 晶元光電股份有限公司 | 發光二極體之部分 |

| JP2025099960A (ja) * | 2023-12-22 | 2025-07-03 | セイコーエプソン株式会社 | 発光装置、電子機器、および発光装置の製造方法 |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN100595938C (zh) | 2002-08-01 | 2010-03-24 | 日亚化学工业株式会社 | 半导体发光元件及其制造方法、使用此的发光装置 |

| TWI220578B (en) * | 2003-09-16 | 2004-08-21 | Opto Tech Corp | Light-emitting device capable of increasing light-emitting active region |

| JP4449405B2 (ja) * | 2003-10-20 | 2010-04-14 | 日亜化学工業株式会社 | 窒化物半導体発光素子およびその製造方法 |

| JP4899825B2 (ja) * | 2006-11-28 | 2012-03-21 | 日亜化学工業株式会社 | 半導体発光素子、発光装置 |

| JP5130730B2 (ja) | 2007-02-01 | 2013-01-30 | 日亜化学工業株式会社 | 半導体発光素子 |

| JP4882792B2 (ja) * | 2007-02-25 | 2012-02-22 | 日亜化学工業株式会社 | 半導体発光素子 |

| CN102779918B (zh) | 2007-02-01 | 2015-09-02 | 日亚化学工业株式会社 | 半导体发光元件 |

| DE102007022947B4 (de) * | 2007-04-26 | 2022-05-05 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Optoelektronischer Halbleiterkörper und Verfahren zur Herstellung eines solchen |

| KR101020910B1 (ko) * | 2008-12-24 | 2011-03-09 | 엘지이노텍 주식회사 | 반도체 발광소자 및 그 제조방법 |

| JP5713650B2 (ja) * | 2009-12-08 | 2015-05-07 | Dowaエレクトロニクス株式会社 | 発光素子およびその製造方法 |

| TWI433357B (zh) * | 2010-08-26 | 2014-04-01 | Huga Optotech Inc | 高亮度發光二極體結構 |

| JP5628615B2 (ja) * | 2010-09-27 | 2014-11-19 | スタンレー電気株式会社 | 半導体発光装置およびその製造方法 |

| TW201216517A (en) * | 2010-10-06 | 2012-04-16 | Chi Mei Lighting Tech Corp | Light-emitting diode device and manufacturing method thereof |

| US8987772B2 (en) * | 2010-11-18 | 2015-03-24 | Seoul Viosys Co., Ltd. | Light emitting diode chip having electrode pad |

| JP5605189B2 (ja) * | 2010-11-26 | 2014-10-15 | 豊田合成株式会社 | 半導体発光素子 |

| JP2012124306A (ja) * | 2010-12-08 | 2012-06-28 | Toyoda Gosei Co Ltd | 半導体発光素子 |

| JP2012204373A (ja) * | 2011-03-23 | 2012-10-22 | Toyoda Gosei Co Ltd | 半導体発光素子 |

| JP5541261B2 (ja) * | 2011-03-23 | 2014-07-09 | 豊田合成株式会社 | Iii族窒化物半導体発光素子 |

| KR101883842B1 (ko) * | 2011-12-26 | 2018-08-01 | 엘지이노텍 주식회사 | 발광소자 및 이를 포함하는 조명시스템 |

| TWI479694B (zh) * | 2012-01-11 | 2015-04-01 | Formosa Epitaxy Inc | Light emitting diode wafers |

-

2014

- 2014-12-02 JP JP2014244157A patent/JP6485019B2/ja active Active

- 2014-12-15 KR KR1020140180116A patent/KR102299959B1/ko active Active

- 2014-12-17 AU AU2014277727A patent/AU2014277727B2/en active Active

- 2014-12-17 EP EP14198483.1A patent/EP2887408B1/en active Active

- 2014-12-17 TW TW103144160A patent/TWI649898B/zh active

- 2014-12-18 CN CN201410795354.XA patent/CN104733599B/zh active Active

- 2014-12-18 US US14/575,807 patent/US9123865B2/en active Active

-

2015

- 2015-07-21 US US14/804,876 patent/US9293658B2/en active Active

-

2019

- 2019-02-20 JP JP2019028016A patent/JP6870695B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| KR102299959B1 (ko) | 2021-09-09 |

| US20150325751A1 (en) | 2015-11-12 |

| EP2887408A2 (en) | 2015-06-24 |

| EP2887408B1 (en) | 2019-11-06 |

| CN104733599A (zh) | 2015-06-24 |

| JP6870695B2 (ja) | 2021-05-12 |

| TWI649898B (zh) | 2019-02-01 |

| US9123865B2 (en) | 2015-09-01 |

| US20150179890A1 (en) | 2015-06-25 |

| US9293658B2 (en) | 2016-03-22 |

| EP2887408A3 (en) | 2015-11-04 |

| CN104733599B (zh) | 2018-12-28 |

| JP2015135951A (ja) | 2015-07-27 |

| AU2014277727B2 (en) | 2019-04-04 |

| AU2014277727A1 (en) | 2015-07-09 |

| JP2019075591A (ja) | 2019-05-16 |

| KR20150072344A (ko) | 2015-06-29 |

| TW201528548A (zh) | 2015-07-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6485019B2 (ja) | 半導体発光素子 | |

| JP5719110B2 (ja) | 発光素子 | |

| JP5246199B2 (ja) | Iii族窒化物半導体発光素子 | |

| CN106415859B (zh) | 半导体发光元件及其制造方法 | |

| JP2010171376A (ja) | Iii族窒化物系化合物半導体発光素子 | |

| JP6149878B2 (ja) | 発光素子 | |

| JP2009043934A (ja) | フリップチップ型発光素子 | |

| JP2015060886A (ja) | Iii族窒化物半導体発光素子 | |

| JP2007287849A (ja) | 半導体発光素子 | |

| JP2011198997A (ja) | Iii族窒化物半導体発光素子 | |

| JP2008218878A (ja) | GaN系LED素子および発光装置 | |

| JP6028597B2 (ja) | Iii族窒化物半導体発光素子 | |

| JP5729328B2 (ja) | Iii族窒化物半導体発光素子およびその製造方法 | |

| JP2013258174A (ja) | 半導体発光素子 | |

| JP2017117904A (ja) | 発光素子及びその製造方法 | |

| JP6994663B2 (ja) | 発光素子 | |

| WO2016152397A1 (ja) | 窒化物半導体発光素子 | |

| JP2011071340A (ja) | 発光素子 | |

| JP6189525B2 (ja) | 窒化物半導体発光素子 | |

| JP2009238931A (ja) | 半導体発光素子およびそれを用いる照明装置ならびに半導体発光素子の製造方法 | |

| CN117650212A (zh) | 一种发光二极管及发光装置 | |

| JP2013251400A (ja) | 半導体発光素子 | |

| CN103606604A (zh) | 一种发光二极管的制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20160216 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171201 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20171201 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180823 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180905 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181031 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190122 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190204 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6485019 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |