JP6250737B2 - 誤り率測定装置及び誤り率測定方法 - Google Patents

誤り率測定装置及び誤り率測定方法 Download PDFInfo

- Publication number

- JP6250737B2 JP6250737B2 JP2016112901A JP2016112901A JP6250737B2 JP 6250737 B2 JP6250737 B2 JP 6250737B2 JP 2016112901 A JP2016112901 A JP 2016112901A JP 2016112901 A JP2016112901 A JP 2016112901A JP 6250737 B2 JP6250737 B2 JP 6250737B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- voltage range

- error rate

- range

- threshold voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Tests Of Electronic Circuits (AREA)

- Detection And Prevention Of Errors In Transmission (AREA)

- Dc Digital Transmission (AREA)

Description

前記1チャンネルの受信モジュールは、

前記入力データを所定のサンプリング周期でデジタル値に変換するA/D変換部31aと、

閾値電圧Vthと位相をパラメータとして個別に可変するパラメータ可変部31cと、

該パラメータ可変部にて前記閾値電圧を可変して前記デジタル値が飽和する上限の閾値電圧を前記高電圧範囲の上限電圧として検出するとともに、前記デジタル値が飽和する下限の閾値電圧を前記低電圧範囲の下限電圧として検出し、これら検出した前記高電圧範囲の上限電圧と前記低電圧範囲の下限電圧を用いて前記中電圧範囲の中心電圧を算出し、該算出した前記中電圧範囲の中心電圧を用いて前記高電圧範囲の中心電圧と前記低電圧範囲の中心電圧とをそれぞれ算出し、該算出した前記高電圧範囲の中心電圧の電圧値を中心に前記閾値電圧を可変してビット誤り率が最小になる閾値電圧を前記高電圧範囲の閾値電圧Vth1として自動設定し、前記算出した前記中電圧範囲の中心電圧の電圧値を中心に前記閾値電圧を可変してビット誤り率が最小になる閾値電圧を中電圧範囲の閾値電圧Vth2として自動設定し、前記算出した前記低電圧範囲の中心電圧の電圧値を中心に前記閾値電圧を可変してビット誤り率が最小になる閾値電圧を低電圧範囲の閾値電圧Vth3として自動設定し、また、前記デジタル値から前記測定パターンの位相方向の両端位置を検出し、その位相方向の中心を起点として位相を増減してビット誤り率が最小になる位置を前記測定パターンの中心Pとして位相を自動設定するパラメータ検出設定部31bと、

前記中電圧範囲及び低電圧範囲をマスク処理したデジタル値と前記自動設定された前記高電圧範囲の閾値電圧とを比較して前記高電圧範囲のビット誤り率を測定し、前記デジタル値と前記自動設定された前記中電圧範囲の閾値電圧とを比較して前記中電圧範囲のビット誤り率を測定し、前記高電圧範囲及び中電圧範囲をマスク処理したデジタル値と前記自動設定された前記低電圧範囲の閾値電圧とを比較して低電圧範囲のビット誤り率を測定するビットエラー測定部31dとを含む信号処理部31を備え、

前記3つのビット誤り率の測定結果を用いて前記4PAM信号のトータルビット誤り率を算出することを特徴とする。

少なくとも前記操作部4にて前記測定パターンを選択するための表示項目と、前記自動設定された各電圧範囲E1,E2,E3毎の閾値電圧Vth1,Vth2,Vth3及び前記位相の値と、前記ビットエラー測定部31dにて測定された前記各電圧範囲毎のビット誤り率及び前記4PAM信号のトータルビット誤り率の測定結果とを一つの表示画面6a上に表示する表示部6を備えたことを特徴とする。

前記入力データを所定のサンプリング周期でデジタル値に変換するステップと、

閾値電圧Vthと位相をパラメータとして個別に可変するステップと、

前記閾値電圧を可変して前記デジタル値が飽和する上限の閾値電圧を前記高電圧範囲の上限電圧として検出するとともに、前記デジタル値が飽和する下限の閾値電圧を前記低電圧範囲の下限電圧として検出するステップと、

前記検出した前記高電圧範囲の上限電圧と前記低電圧範囲の下限電圧を用いて前記中電圧範囲の中心電圧を算出するステップと、

前記算出した前記中電圧範囲の中心電圧を用いて前記高電圧範囲の中心電圧と前記低電圧範囲の中心電圧とをそれぞれ算出するステップと、

前記算出した前記高電圧範囲の中心電圧の電圧値を中心に前記閾値電圧を可変してビット誤り率が最小になる閾値電圧を前記高電圧範囲の閾値電圧Vth1として自動設定するステップと、

前記算出した前記中電圧範囲の中心電圧の電圧値を中心に前記閾値電圧を可変してビット誤り率が最小になる閾値電圧を中電圧範囲の閾値電圧Vth2として自動設定するステップと、

前記算出した前記低電圧範囲の中心電圧の電圧値を中心に前記閾値電圧を可変してビット誤り率が最小になる閾値電圧を低電圧範囲の閾値電圧Vth3として自動設定するステップと、

前記デジタル値から前記測定パターンの位相方向の両端位置を検出し、その位相方向の中心を起点として位相を増減してビット誤り率が最小になる位置を前記測定パターンの中心Pとして位相を自動設定するステップと、

前記中電圧範囲及び低電圧範囲をマスク処理したデジタル値と前記自動設定された前記高電圧範囲の閾値電圧とを比較して前記高電圧範囲のビット誤り率を測定するステップと、

前記デジタル値と前記自動設定された前記中電圧範囲の閾値電圧とを比較して前記中電圧範囲のビット誤り率を測定するステップと、

前記高電圧範囲及び中電圧範囲をマスク処理したデジタル値と前記自動設定された前記低電圧範囲の閾値電圧とを比較して低電圧範囲のビット誤り率を測定するステップと、

前記3つのビット誤り率の測定結果を用いて前記4PAM信号のトータルビット誤り率を算出するステップとを含むことを特徴とする。

少なくとも前記測定パターンを選択するための表示項目と、前記自動設定された各電圧範囲E1,E2,E3毎の閾値電圧Vth1,Vth2,Vth3及び前記位相の値と、前記各電圧範囲毎のビット誤り率及び前記4PAM信号のトータルビット誤り率の測定結果とを一つの表示画面6a上に表示するステップをさらに含むことを特徴とする。

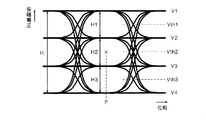

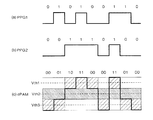

本発明は、被試験デバイス(DUT)に既知パターンのテスト信号を入力し、このテスト信号の入力に伴って被試験デバイスから受信した入力データのビット誤り率を被試験デバイスに入力したテスト信号とのビット比較によって測定する誤り率測定装置及び誤り率測定方法に関するものであり、1チャンネルのEDモジュールを用い、被試験デバイスから受信した4PAM信号を入力データとし、その振幅電圧範囲Eの高電圧範囲H1、中電圧範囲H2、低電圧範囲H3のそれぞれのビット誤り率(以下、BERという)を算出し、これら算出したBERに基づいて4PAM信号のトータルビット誤り率(以下、トータルBERという)を算出して自動測定を行う自動測定機能を有する。

図1に示すように、本実施の形態の誤り率測定装置1は、上述した4PAM信号のトータルBERの自動測定機能を実現するため、送信モジュールとしてのPPGモジュール2、受信モジュールとしての1チャンネルのEDモジュール3、操作部4、記憶部5、表示部6、制御部7を備えて概略構成される。

次に、上記のように構成される誤り率測定装置1を用い、1チャンネルのEDモジュール3で4PAM信号のトータルBERを自動測定する自動測定機能を実行する場合の測定方法について説明する。

2 PPGモジュール(送信モジュール)

3(3A,3B,3C) EDモジュール(受信モジュール)

4 操作部

5 記憶部

6 表示部

6a 表示画面

7 制御部

11 装置本体

21 第1パターン発生部

22 第2パターン発生部

23 パターン合成出力部

31 信号処理部

31a A/D変換部

31b パラメータ検出設定部

31c パラメータ可変部

31d ビットエラー測定部

41 EDモジュールの設定項目

42 測定パターンの設定項目

43 測定時間の設定項目

44 高電圧範囲H1の閾値電圧Vth1の自動設定項目

45 中電圧範囲H2の閾値電圧Vth2の自動設定項目

46 低電圧範囲H3の閾値電圧Vth3の自動設定項目

47 高電圧範囲H1の位相の自動設定項目

48 中電圧範囲H2の位相の自動設定項目

49 低電圧範囲H3の位相の自動設定項目

50 高電圧範囲H1のエラーレートの測定結果項目

51 中電圧範囲H2のエラーレートの測定結果項目

52 低電圧範囲H3のエラーレートの測定結果項目

53 高電圧範囲H1のエラーカウント値の測定結果項目

54 中電圧範囲H2のエラーカウント値の測定結果項目

55 低電圧範囲H3のエラーカウント値の測定結果項目

56 高電圧範囲H1のアラームの表示項目

57 中電圧範囲H2のアラームの表示項目

58 低電圧範囲H3のアラームの表示項目

59 4PAM信号のトータルエラーレートの測定結果項目

60 4PAM信号のトータルエラーカウント値の測定結果項目

E 振幅電圧範囲

E1 高電圧範囲

E2 中電圧範囲

E3 低電圧範囲

Vth(Vth1,Vth2,Vth3) 閾値電圧

P 測定範囲の中心

W 被試験デバイス

Claims (4)

- 全体の振幅電圧範囲(E)が電圧レベルの高い方から高電圧範囲(H1)、中電圧範囲(H2)、低電圧範囲(H3)に分けられた3つのアイパターン開口部による連続した範囲からなる4PAM信号を入力データとして受信する1チャンネルの受信モジュール(3)と、前記4PAM信号の測定パターンを選択して設定する操作部(4)とを備え、前記4PAM信号のトータルビット誤り率を測定する誤り率測定装置(1)であって、

前記1チャンネルの受信モジュールは、

前記入力データを所定のサンプリング周期でデジタル値に変換するA/D変換部(31a)と、

閾値電圧(Vth)と位相をパラメータとして個別に可変するパラメータ可変部(31c)と、

該パラメータ可変部にて前記閾値電圧を可変して前記デジタル値が飽和する上限の閾値電圧を前記高電圧範囲の上限電圧として検出するとともに、前記デジタル値が飽和する下限の閾値電圧を前記低電圧範囲の下限電圧として検出し、これら検出した前記高電圧範囲の上限電圧と前記低電圧範囲の下限電圧を用いて前記中電圧範囲の中心電圧を算出し、該算出した前記中電圧範囲の中心電圧を用いて前記高電圧範囲の中心電圧と前記低電圧範囲の中心電圧とをそれぞれ算出し、該算出した前記高電圧範囲の中心電圧の電圧値を中心に前記閾値電圧を可変してビット誤り率が最小になる閾値電圧を前記高電圧範囲の閾値電圧(Vth1)として自動設定し、前記算出した前記中電圧範囲の中心電圧の電圧値を中心に前記閾値電圧を可変してビット誤り率が最小になる閾値電圧を中電圧範囲の閾値電圧(Vth2)として自動設定し、前記算出した前記低電圧範囲の中心電圧の電圧値を中心に前記閾値電圧を可変してビット誤り率が最小になる閾値電圧を低電圧範囲の閾値電圧(Vth3)として自動設定し、また、前記デジタル値から前記測定パターンの位相方向の両端位置を検出し、その位相方向の中心を起点として位相を増減してビット誤り率が最小になる位置を前記測定パターンの中心(P)として位相を自動設定するパラメータ検出設定部(31b)と、

前記中電圧範囲及び低電圧範囲をマスク処理したデジタル値と前記自動設定された前記高電圧範囲の閾値電圧とを比較して前記高電圧範囲のビット誤り率を測定し、前記デジタル値と前記自動設定された前記中電圧範囲の閾値電圧とを比較して前記中電圧範囲のビット誤り率を測定し、前記高電圧範囲及び中電圧範囲をマスク処理したデジタル値と前記自動設定された前記低電圧範囲の閾値電圧とを比較して低電圧範囲のビット誤り率を測定するビットエラー測定部(31d)とを含む信号処理部(31)を備え、

前記3つのビット誤り率の測定結果を用いて前記4PAM信号のトータルビット誤り率を算出することを特徴とする誤り率測定装置。 - 少なくとも前記操作部(4)にて前記測定パターンを選択するための表示項目と、前記自動設定された各電圧範囲(E1,E2,E3)毎の閾値電圧(Vth1,Vth2,Vth3)及び前記位相の値と、前記ビットエラー測定部(31d)にて測定された前記各電圧範囲毎のビット誤り率及び前記4PAM信号のトータルビット誤り率の測定結果とを一つの表示画面(6a)上に表示する表示部(6)を備えたことを特徴とする請求項1記載の誤り率測定装置。

- 全体の振幅電圧範囲(E)が電圧レベルの高い方から高電圧範囲(H1)、中電圧範囲(H2)、低電圧範囲(H3)に分けられた3つのアイパターン開口部による連続した範囲からなる4PAM信号を入力データとして受信する1チャンネルの受信モジュール(3)と、前記4PAM信号の測定パターンを選択して設定する操作部(4)とを備えた誤り率測定装置を用いて前記4PAM信号のトータルビット誤り率を測定する誤り率測定方法であって、

前記入力データを所定のサンプリング周期でデジタル値に変換するステップと、

閾値電圧(Vth)と位相をパラメータとして個別に可変するステップと、

前記閾値電圧を可変して前記デジタル値が飽和する上限の閾値電圧を前記高電圧範囲の上限電圧として検出するとともに、前記デジタル値が飽和する下限の閾値電圧を前記低電圧範囲の下限電圧として検出するステップと、

前記検出した前記高電圧範囲の上限電圧と前記低電圧範囲の下限電圧を用いて前記中電圧範囲の中心電圧を算出するステップと、

前記算出した前記中電圧範囲の中心電圧を用いて前記高電圧範囲の中心電圧と前記低電圧範囲の中心電圧とをそれぞれ算出するステップと、

前記算出した前記高電圧範囲の中心電圧の電圧値を中心に前記閾値電圧を可変してビット誤り率が最小になる閾値電圧を前記高電圧範囲の閾値電圧(Vth1)として自動設定するステップと、

前記算出した前記中電圧範囲の中心電圧の電圧値を中心に前記閾値電圧を可変してビット誤り率が最小になる閾値電圧を中電圧範囲の閾値電圧(Vth2)として自動設定するステップと、

前記算出した前記低電圧範囲の中心電圧の電圧値を中心に前記閾値電圧を可変してビット誤り率が最小になる閾値電圧を低電圧範囲の閾値電圧(Vth3)として自動設定するステップと、

前記デジタル値から前記測定パターンの位相方向の両端位置を検出し、その位相方向の中心を起点として位相を増減してビット誤り率が最小になる位置を前記測定パターンの中心(P)として位相を自動設定するステップと、

前記中電圧範囲及び低電圧範囲をマスク処理したデジタル値と前記自動設定された前記高電圧範囲の閾値電圧とを比較して前記高電圧範囲のビット誤り率を測定するステップと、

前記デジタル値と前記自動設定された前記中電圧範囲の閾値電圧とを比較して前記中電圧範囲のビット誤り率を測定するステップと、

前記高電圧範囲及び中電圧範囲をマスク処理したデジタル値と前記自動設定された前記低電圧範囲の閾値電圧とを比較して低電圧範囲のビット誤り率を測定するステップと、

前記3つのビット誤り率の測定結果を用いて前記4PAM信号のトータルビット誤り率を算出するステップとを含むことを特徴とする誤り率測定方法。 - 少なくとも前記測定パターンを選択するための表示項目と、前記自動設定された各電圧範囲(E1,E2,E3)毎の閾値電圧(Vth1,Vth2,Vth3)及び前記位相の値と、前記各電圧範囲毎のビット誤り率及び前記4PAM信号のトータルビット誤り率の測定結果とを一つの表示画面(6a)上に表示するステップをさらに含むことを特徴とする請求項3記載の誤り率測定方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016112901A JP6250737B2 (ja) | 2016-06-06 | 2016-06-06 | 誤り率測定装置及び誤り率測定方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016112901A JP6250737B2 (ja) | 2016-06-06 | 2016-06-06 | 誤り率測定装置及び誤り率測定方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017220756A JP2017220756A (ja) | 2017-12-14 |

| JP6250737B2 true JP6250737B2 (ja) | 2017-12-20 |

Family

ID=60657849

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016112901A Active JP6250737B2 (ja) | 2016-06-06 | 2016-06-06 | 誤り率測定装置及び誤り率測定方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6250737B2 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6625095B2 (ja) * | 2017-07-03 | 2019-12-25 | アンリツ株式会社 | 誤り検出装置および誤り検出方法 |

| JP6776298B2 (ja) * | 2018-05-25 | 2020-10-28 | アンリツ株式会社 | 信号発生装置および信号発生方法と誤り率測定装置および誤り率測定方法 |

| JP6739488B2 (ja) * | 2018-09-11 | 2020-08-12 | アンリツ株式会社 | Pamデコーダおよびpamデコード方法と誤り検出装置および誤り検出方法 |

| JP6739489B2 (ja) * | 2018-09-11 | 2020-08-12 | アンリツ株式会社 | Pamデコーダおよびpamデコード方法と誤り検出装置および誤り検出方法 |

| JP6776320B2 (ja) * | 2018-12-26 | 2020-10-28 | アンリツ株式会社 | Pam4シンボルエラー付加装置および方法と誤り率測定装置および方法 |

| JP6821717B2 (ja) * | 2019-01-10 | 2021-01-27 | アンリツ株式会社 | 誤り検出装置および誤り検出方法 |

| JP6818055B2 (ja) * | 2019-01-18 | 2021-01-20 | アンリツ株式会社 | 誤り率測定装置及び誤り率測定方法 |

| JP6818056B2 (ja) * | 2019-01-18 | 2021-01-20 | アンリツ株式会社 | 誤り率測定装置及び誤り率測定方法 |

| JP6774512B2 (ja) * | 2019-01-23 | 2020-10-28 | アンリツ株式会社 | Fecエラー付加装置、それを用いた試験信号発生装置、及びfecエラー付加方法 |

| JP6818064B2 (ja) * | 2019-02-13 | 2021-01-20 | アンリツ株式会社 | 誤り率測定装置及び誤り率測定方法 |

| JP6827484B2 (ja) * | 2019-02-18 | 2021-02-10 | アンリツ株式会社 | 誤り率測定装置および誤り率測定方法 |

| US10541763B1 (en) * | 2019-05-08 | 2020-01-21 | Bae Systems Information And Electronic Systems Integration Inc. | Apparatus and method for digitally characterizing communication channel noise and interference |

| JP7200203B2 (ja) * | 2020-12-14 | 2023-01-06 | アンリツ株式会社 | 誤り検出装置および誤り検出方法 |

| JP7200274B2 (ja) * | 2021-02-12 | 2023-01-06 | アンリツ株式会社 | 誤り検出装置および誤り検出方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0454043A (ja) * | 1990-06-22 | 1992-02-21 | Fujitsu Ltd | 受信データ識別回路 |

| JPH06291668A (ja) * | 1993-04-01 | 1994-10-18 | Nippon Denshin Kogyo Kk | 多値信号復号回路 |

| JP2959435B2 (ja) * | 1995-06-02 | 1999-10-06 | 日本電気株式会社 | 判定回路 |

| JP2004320104A (ja) * | 2003-04-11 | 2004-11-11 | Yokogawa Electric Corp | 符号誤り率測定装置および符号誤り率測定方法 |

| JP4218581B2 (ja) * | 2004-05-12 | 2009-02-04 | 横河電機株式会社 | 符号誤り率測定装置および符号誤り率測定方法 |

| JP5580862B2 (ja) * | 2012-09-27 | 2014-08-27 | アンリツ株式会社 | 誤り率測定表示装置及び方法 |

| US9136952B2 (en) * | 2014-01-17 | 2015-09-15 | Tektronix, Inc. | Pulse amplitude modulation (PAM) bit error test and measurement |

| JP6281303B2 (ja) * | 2014-02-03 | 2018-02-21 | 富士通株式会社 | 多値強度変復調システムおよび方法 |

-

2016

- 2016-06-06 JP JP2016112901A patent/JP6250737B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2017220756A (ja) | 2017-12-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6250737B2 (ja) | 誤り率測定装置及び誤り率測定方法 | |

| JP6250738B2 (ja) | 誤り率測定装置及び誤り率測定方法 | |

| US7957462B2 (en) | Integrated compact eye pattern analyzer for next generation networks | |

| JP7200273B2 (ja) | 誤り検出装置および誤り検出方法 | |

| US11379331B2 (en) | Error rate measuring apparatus and error counting method | |

| US11506711B2 (en) | Error rate measuring apparatus and data division display method | |

| US11714130B2 (en) | Error rate measuring apparatus and error distribution display method | |

| US11979229B2 (en) | Error rate measuring apparatus and error count display method | |

| US11293983B2 (en) | Error rate measuring apparatus and setting screen display method | |

| JP6025883B2 (ja) | 誤り率測定装置及び誤り率測定方法 | |

| JP6818055B2 (ja) | 誤り率測定装置及び誤り率測定方法 | |

| US11442801B2 (en) | Error rate measuring apparatus and error counting method | |

| JP6818056B2 (ja) | 誤り率測定装置及び誤り率測定方法 | |

| JP2020136707A (ja) | 誤り率測定装置及び誤り率測定方法 | |

| JP6827484B2 (ja) | 誤り率測定装置および誤り率測定方法 | |

| JP2022099902A (ja) | 誤り率測定装置及びコードワード位置表示方法 | |

| JP2013178240A (ja) | ジッタ測定用トリガ発生器及びこれを用いたジッタ測定装置、ジッタ測定用トリガ発生方法及びジッタ測定方法 | |

| JP5290213B2 (ja) | 誤り率測定装置及び方法 | |

| JP5410454B2 (ja) | パルスパターン発生装置及び該装置を用いた誤り率測定システム並びにパルスパターン発生方法 | |

| JP6951399B2 (ja) | 誤り率測定器のデータ表示装置及びエラーカウント方法 | |

| JP6836569B2 (ja) | 誤り率測定装置および誤り率測定方法 | |

| JP6625095B2 (ja) | 誤り検出装置および誤り検出方法 | |

| JP7046883B2 (ja) | 誤り率測定装置及び誤り率測定方法 | |

| JP7731404B2 (ja) | パターン発生装置およびパターン発生方法と誤り率測定装置および誤り率測定方法 | |

| US20240230759A9 (en) | Determination device, test system, and generation device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20171025 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20171107 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20171122 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6250737 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |