JP6211971B2 - 半導体テスト回路及びicチップ - Google Patents

半導体テスト回路及びicチップ Download PDFInfo

- Publication number

- JP6211971B2 JP6211971B2 JP2014063880A JP2014063880A JP6211971B2 JP 6211971 B2 JP6211971 B2 JP 6211971B2 JP 2014063880 A JP2014063880 A JP 2014063880A JP 2014063880 A JP2014063880 A JP 2014063880A JP 6211971 B2 JP6211971 B2 JP 6211971B2

- Authority

- JP

- Japan

- Prior art keywords

- scan

- counter

- state

- signal

- data signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000012360 testing method Methods 0.000 title claims description 70

- 239000004065 semiconductor Substances 0.000 title claims description 25

- 230000007704 transition Effects 0.000 claims description 25

- 238000010586 diagram Methods 0.000 description 24

- 230000000630 rising effect Effects 0.000 description 21

- 238000013461 design Methods 0.000 description 5

- 102100029469 WD repeat and HMG-box DNA-binding protein 1 Human genes 0.000 description 1

- 101710097421 WD repeat and HMG-box DNA-binding protein 1 Proteins 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

Images

Landscapes

- Tests Of Electronic Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

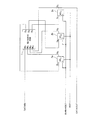

図1は、一般的なLSI回路の例を示す回路構成図である。入力ピンDATAINと、出力ピンDATAOUTと、FFのリセット用ピンRSTと、FFのCLK用ピンSystemCLKをピンとして有している。FFA2a、FFB2b、FFC2cは、SystemCLKで動作するFFである。それぞれのFFの入力DA、DB、DCは、組み合わせ回路1の出力OA、OB、OCと接続し、FFの出力QA、QB、QCとDATAINピンは組み合わせ回路の入力INA、INB、INC、INDに接続されるように構成された回路である。

SCAN化された回路は、SCAN動作により、回路中の任意のノードに任意の値を設定できる制御と(control)、回路中の任意のノードの値を出力できる(observe)観測が自由となる。つまり、回路中の組み合わせ回路等に自由な値を設定し、その出力をモニタすることによって、故障検出率の高いテストを行うことができる。

SCANIN:SCANデータの入力ピン

SCANENB:SCANパスと通常パスを切り替える入力ピン

SCANCLK:SCAN回路のCLK

SCANOUT:SCAN回路の出力ピン

SCANRST:SCAN回路のリセットピン

TESTMODE:SCANテストの許可ピン

(1);SCANENBを1にして全FFをSCAN動作可能にする。

(2);全FFに所望の値をSCAN動作によりセットする(図3ではFFA、;FFB、FFBにそれぞれDA1、DB1、DC1をセットしている)。

(3);SCANENBを0にして通常パスに戻す。

(4);SCANCLKから1CLK入力し、通常パスの出力(=組み合わせ回路の出力)を各FFに取り込む(図3ではFFA、FFB、FFBにそれぞれ組み合わせ回路出力のOA1、OB1、OC1が取り込まれる)。

(5);SCANENBを1にして全FFをSCAN動作可能にする。

(6);SCANCLKを入力して全FFの値(OA1、OB1、OC1)をSCANOUTから出力しモニタする(この際同時に全FFに次の所望の値DA2、DB2、DC2をセットする)。

(7);上記(3)〜(6)を繰り返す。

以上が一般的なスキャン化した回路のテスト動作である。

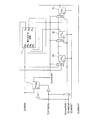

図4は、特許文献1に記載されているSCANテストを可能にした回路構成図である。以下のような特徴を有している。

SCAN回路はSCANCLKの正転信号をCLKとする。

SCANINをデータ、SCANCLKの反転信号をCLK入力としたFFであるFFENB3の出力をSCANENBとする。

(1);SCANCLKが1のときにSCANINを1にする。

(2);SCANCLKの立ち下がりEdgeでSCANINからSCANENB用FFであるFFENBに1を取り込むことでSCAN動作を可能にする。

(3);SCANCLKが0のときにSCANINを所望の値にする。

(4);SCANCLKの立ち上がりEdgeでSCANINからSCAN化されたFFAに所望の値を取り込む(図5ではFFAにDC1をセットしている)。

(5);SCANCLKが1のときにSCANINを1にする。

(7);上記(3)〜(6)を繰り返し全FFに所望の値をセットする(図5ではFFA、FFB、FFBにそれぞれDA1、DB1、DC1をセットしている)。

(8);SCANCLKが1のときにSCANINを0にする。

(9);SCANCLKの立ち下がりEdgeでSCANINからSCANENB用FFであるFFENBに0を取り込むことで通常パスに戻す。

(10)SCANCLKの立ち上がりEdgeで、通常パスの出力(=組み合わせ回路の出力)を各FFに取り込む(図5ではFFA、FFB、FFBにそれぞれ組み合わせ回路出力のOA1、OB1、OC1が取り込まれる)。

(12);SCANCLKの立ち下がりEdgeでSCANINからSCANENB用FFであるFFENBに1を取り込むことでSCAN動作を可能にする。

(13);SCANCLKを入力して全FFの値(OA1、OB1、OC1)をSCANOUTから出力しモニタする(この際同時に全FFに次の所望の値DA2、DB2、DC2をセットする。SCANENBは1のままになるようにしておく)。

(14);上記(8)〜(12)を繰り返す。

本発明は、このような問題に鑑みてなされたもので、その目的とするところは、設計の自由度が高く、また、テスト時間が短い半導体テスト回路及びICチップを提供することにある。

また、請求項3に記載の発明は、請求項1又は2に記載の発明において、前記スキャンデータ信号は、前記複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、前記複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるカウンタ制御信号と、を有し、前記カウンタにおいて、前記カウンタ制御信号により、前記スキャンイネーブル信号が立ち上がる又は立ち下がることを特徴とする。

また、請求項5に記載の発明は、請求項4に記載の発明において、前記カウンタは、少なくとも4つの状態を遷移し、前記データ信号と前記スキャンクロック信号により、第1の状態と第2の状態の遷移を繰り返し、また、第3の状態と第4の状態の遷移を繰り返し、前記カウンタ制御信号により、前記第1の状態又は前記第2の状態から、前記第3の状態又は第4の状態への遷移、または、前記第3の状態又は前記第4の状態から、前記第1の状態又は第2の状態への遷移を行い、前記第1の状態又は前記第2の状態に対応するカウント値が通常動作に対応する前記イネーブル信号であり、前記第3の状態又は前記第4の状態に対応するカウント値がスキャン動作に対応する前記イネーブル信号であることを特徴とする。

また、請求項7に記載の発明は、請求項1〜6のいずれか一項に記載の発明において、前記カウンタは、2bitバイナリカウンタであり、前記スキャンイネーブル信号は、前記カウンタのカウント値のMSB又はLSBであることを特徴とする。

また、請求項10に記載の発明は、請求項8又は9に記載の発明において、前記スキャンデータ信号は、前記複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、前記複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるパルス信号と、を有することを特徴とする。

また、請求項12に記載の発明は、請求項11に記載の発明において、前記次のスキャンクロックが配された後、別のデータ信号を前記複数のフリップフロップに、前記スキャンクロックに同期して設定するために順次データが入力されるまでの間に、前記パルス信号が配されることを特徴とする。

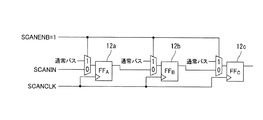

図6は、本発明に係るシフトレジスタ回路の回路構成図で、図7は、図6に示したシフトレジスタ回路の動作を説明するためのタイミングチャートを示す図である。図中符号12a,12b,12cは第1乃至第3のフリップフロップ(FFA、FFB、FFC)を示している。

本実施形態の半導体テスト回路は、SCANINをCLKとするカウンタを用いて、そのカウンタ値をSCANENBとすることにより、SCANINとSCANENBを同一ピンで制御できるため、ピン数の削減ができることを特徴とする。また、カウンタを用いることで、設計の自由度が高く、また、テスト時間が短いテストが可能となる。

本実施形態は、SCANINとSCANENBを共用するために、SCANENBをSCANCLKではなくSCANINをCLKとしたカウンタの値とすることを特徴とする。

以下に、基本原理について説明する。

SCAN動作は、SCANCLKのEdgeでSCANINを取り込みシフトレジスタ動作する。図6及び図7に示すように、SCANCLKのEdge以外では、SCANINは、どのように変化してもFFに取り込む値は変わらない。よって、SCANCLKのEdgeの前にSCANINにパルスを発生させ、そのSCANINをCLKとするカウンタを用意し、そのカウンタ値をもってSCANENBを生成する。

本発明の半導体テスト回路は、デジタル回路の故障検知を行うテストモードを有する半導体テスト回路である。

複数のフリップフロップ12a〜12cは、スキャンイネーブル信号に基づいて、通常動作とスキャンデータ信号が入力されるシフトレジスタを構成するスキャン動作とを選択する選択回路を有する。

また、スキャンデータ信号は、複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるカウンタ制御信号と、を有し、カウンタにおいて、カウンタ制御信号により、スキャンイネーブル信号が制御される。

また、カウンタ13は、スキャンデータ信号とスキャンクロック信号が入力され、状態遷移するカウンタである。

また、カウンタ13は、少なくとも4つの状態を遷移し、データ信号とスキャンクロック信号により、第1の状態と第2の状態の遷移を繰り返し、また、第3の状態と第4の状態の遷移を繰り返し、カウンタ制御信号により、第1の状態又は第2の状態から、第3の状態又は第4の状態への遷移、または、第3の状態又は第4の状態から、第1の状態又は第2の状態への遷移を行い、第1の状態又は第2の状態に対応するカウント値が通常動作に対応するイネーブル信号であり、第3の状態又は第4の状態に対応するカウント値がスキャン動作に対応するイネーブル信号である。

また、カウンタ13は、2bitバイナリカウンタであり、スキャンイネーブル信号は、カウンタのカウント値のMSB(最上位ビット)である。なお、LSB(最下位ビット)をスキャンイネーブル信号とする構成であってもよい。

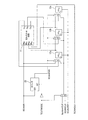

SCAN回路が、SCANCLKの立ち上がりEdgeで動作するときの新回路の例を図8に示している。SCANENBを、SCANINをCLKとしたカウンタの出力とするように構成する。

図10は、図8に示したSCANテスト動作を説明するためのタイミングチャートを示す図である。

(2);SCANCLKが0のときにSCANINを所望の0または1にする(図9では1にセットしている。この際カウンタは2進数表記で11となる)。

(3);SCANCLKを入れてFFAに所望の値を取り込む(図9では1をとりこむ。このときカウンタはSCANCLKが1のためLSBがリセットされ必ず2進数表記で10になる)。

(5);SCANCLKが0のときにSCANINから2発パルスを入れることでカウンタを2進数表記で10⇒11⇒00とし、SCANENBを0(=通常パス)にする。

(6);SCANCLKから1CLK入力し、通常パスの出力(=組み合わせ回路の出力)を各FFに取り込む(図10ではFFA、FFB、FFBにそれぞれ組み合わせ回路出力のQA1、QB1、QC1が取り込まれる。このときカウンタはSCANCLKが1のためLSBがリセットされ必ず2進数表記で00になる)。

(8);SCANCLKを入力して全FFの値(QA1、QB1、QC1)をSCANOUTから出力しモニタする(この際同時に全FFに次の所望の値をセットする。図10では0、1、0をそれぞれセットしている)。

(9);上記(5)〜(8)を繰り返す。

更に、本実施例1は、カウンタのLSBのリセット信号にSCANCLKの1を入力しているが、これはSCANCLKが1となるとカウンタが2進数表記で00又は10となり、カウンタの値を把握しやすくするためのものであり、取り除いても構わない。その場合の構成例を以下の実施例2に示す。

SCAN回路がSCANCLKの立ち上がりEdgeで動作するときの新回路の例を図11に示してある。SCANENBを、SCANINをCLKとしたカウンタ13の出力とするように構成する。カウンタ13は、SCANテストを行うTESTMODE=1以外はリセットされる。

図13は、図11に示したSCANテスト動作を説明するためのタイミングチャートを示す図である。

(2);SCANENBが1かつSCANINを所望の0または1にする(図13では1にセットしている。この際カウンタは2進数表記で10⇒11となる)。

(3);SCANENBが1のままでSCANCLKを入れてFFAに所望の値を取り込む(図13では1をとりこむ。このときカウンタは2進数表記で11のまま)。

(5);SCANENBが1かつSCANINを所望の0または1にする。(図13では次にSCANINを1にしてFFA、FFB、FFBにそれぞれ1、0、1を取り込ませるが、その際カウンタが1周して00になりSCANENBが0になってしまうため、その前にSCANINにパルスを3発いれ、カウンタを2進数表記で11⇒00⇒01⇒10とし、SCANENBを1にして全FFをSCAN動作可能にしている。その後SCANINを1にしている。この際カウンタは2進数表記で10⇒11となる)。

(6);SCANENBが1のままでSCANCLKを入れて全FFに所望の値をセットする(図13ではFFA、FFB、FFBにそれぞれ1、0、1をセットしている。この際カウンタは2進数表記で11のまま)。

(8);SCANENBが0のままでSCANCLKから1CLK入力し、通常パスの出力(=組み合わせ回路の出力)を各FFに取り込む(図13ではFFA、FFB、FFBにそれぞれ組み合わせ回路出力のQA1、QB1、QC1が取り込まれる。このときカウンタはSCANINを1にしたため2進数表記で01になっている)。

(10);SCANENBが1でSCANCLKを入力して全FFの値(QA1、QB1、QC1)をSCANOUTから出力しモニタする(この際同時に全FFに次の所望の値をセットする。図13では0、1、0をそれぞれセットしている)。

(11);上記(8)〜(10)を繰り返す。

図14は、本発明に係る半導体テスト回路の実施例3を説明するための回路構成図で、SCANINとSCANENBとを共通化したSCANテストを可能にした回路構成図である。なお、図11と同じ機能を有する構成要素には同一に符号を付してある。

SCAN回路がSCANCLKの立ち上がりEdgeで動作するときの新回路の例を図14に示してある。SCANENBを、SCANINをCLKとしたカウンタ23の出力とするように構成する。カウンタ23は、SCANテストを行うTESTMODE=1以外はリセットされる。

図16は、図14に示したSCANテスト動作を説明するためのタイミングチャートを示す図である。

(2);SCANENBが1かつSCANINを所望の0または1にする(図16では1にセットしている。この際カウンタは2進数表記で1のまま)。

(3);SCANENBが1のままでSCANCLKを入れてFFAに所望の値を取り込む(図16では1をとりこむ。このときカウンタは2進数表記で1のまま)。

(5);SCANENBが1かつSCANINを所望の0または1にする。(図16では次にSCANINを1にしてFFA、FFB、FFBにそれぞれ1、0、1を取り込ませるが、その際カウンタが1周して0になりSCANENBが0になってしまうため、その前にSCANINにパルスを1発いれ、カウンタを2進数表記で1⇒0とする。その後SCANINを1にしている。この際カウンタは2進数表記で0⇒1となり、SCANENBを1にして全FFをSCAN動作可能にする)。

(6);SCANENBが1のままでSCANCLKを入れて全FFに所望の値をセットする(図13ではFFA、FFB、FFBにそれぞれ1、0、1をセットしている。この際カウンタは2進数表記で1のまま)。

(8);SCANENBが0のままでSCANCLKから1CLK入力し、通常パスの出力(=組み合わせ回路の出力)を各FFに取り込む(図16ではFFA、FFB、FFBにそれぞれ組み合わせ回路出力のQA1、QB1、QC1が取り込まれる。このときカウンタはSCANINを1にしたため2進数表記で0のまま)。

(10);SCANENBが1でSCANCLKを入力して全FFの値(QA1、QB1、QC1)をSCANOUTから出力しモニタする(この際同時に全FFに次の所望の値をセットする。図16では0、1、0をそれぞれセットしている)。

(11);上記(8)〜(10)を繰り返す。

同様に、SCAN回路を全てSCANCLKの立ち下がりEdgeのみで動作させる場合、従来技術とは異なり、SCANCLKの立ち上がりEdgeをSCANENB用に使用しないため、FFのセットアップタイムが不要となり、SCANCLKのLowの幅を短くできるため、テスト時間の削減ができる。

本発明のICチップは、複数のフリップフロップと組み合わせ回路とを有するデジタルブロックを、スキャンクロックと、スキャンデータ信号と、スキャンイネーブル信号と、によりスキャンテストを行うICチップである。

スキャンクロックが入力される第1のPAD(SCANCLK)と、スキャンデータ信号が入力される第2のPAD(SCANIN)と、第2のPADに接続され、スキャンデータ信号からスキャンイネーブル信号を出力するカウンタと、を備えている。

また、カウンタのクロックラインに、第2のPADが接続され、カウンタの第1のリセットラインに、第1のPADが論理素子を介して接続されている。

また、スキャンデータ信号は、複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるパルス信号と、を有している。

また、次のスキャンクロックが配された後、別のデータ信号を複数のフリップフロップに、スキャンクロックに同期して設定するために順次データが入力されるまでの間に、パルス信号が配される。

このような構成により、設計の自由度が高く、また、テスト時間が短い半導体テスト回路を組み入れたICチップを実現することができる。

2a,2b,2c,12a,12b,12c 第1乃至第3のフリップフロップ(FFA、FFB、FFC)

3 フリップフロップ(FFENB)

11 組み合わせ回路

13,23 カウンタ

Claims (12)

- デジタル回路の故障検知を行うテストモードを有する半導体テスト回路において、

スキャンイネーブル信号に基づいて、通常動作とスキャンデータ信号が入力されるシフトレジスタを構成するスキャン動作とを選択する選択回路を有する複数のフリップフロップ(12a〜12c)と、

前記スキャンデータ信号が入力されて前記複数のフリップフロップへ出力する組み合わせ回路(11)と、

前記スキャンデータ信号が入力されて前記スキャンイネーブル信号を出力するカウンタ(13)と、

を備える半導体テスト回路。 - 前記スキャンデータ信号は、前記複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、前記複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるカウンタ制御信号と、を有し、

前記カウンタにおいて、前記カウンタ制御信号により、前記スキャンイネーブル信号が制御される請求項1に記載の半導体テスト回路。 - 前記スキャンデータ信号は、前記複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、前記複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるカウンタ制御信号と、を有し、

前記カウンタにおいて、前記カウンタ制御信号により、前記スキャンイネーブル信号が立ち上がる又は立ち下がる請求項1又は2に記載の半導体テスト回路。 - 前記カウンタは、前記スキャンデータ信号と前記スキャンクロック信号が入力され、状態遷移するカウンタである請求項2又は3に記載の半導体テスト回路。

- 前記カウンタは、少なくとも4つの状態を遷移し、

前記データ信号と前記スキャンクロック信号により、第1の状態と第2の状態の遷移を繰り返し、また、第3の状態と第4の状態の遷移を繰り返し、

前記カウンタ制御信号により、前記第1の状態又は前記第2の状態から、前記第3の状態又は第4の状態への遷移、または、前記第3の状態又は前記第4の状態から、前記第1の状態又は第2の状態への遷移を行い、

前記第1の状態又は前記第2の状態に対応するカウント値が通常動作に対応する前記イネーブル信号であり、前記第3の状態又は前記第4の状態に対応するカウント値がスキャン動作に対応する前記イネーブル信号である請求項4に記載の半導体テスト回路。 - 前記カウンタは、前記スキャンクロック信号により、第1の状態又は第2の状態から第1の状態へリセットする遷移を行い、及び、第3の状態又は第4の状態から第3の状態へリセットする遷移を行う請求項5に記載の半導体テスト回路。

- 前記カウンタは、2bitバイナリカウンタであり、

前記スキャンイネーブル信号は、前記カウンタのカウント値のMSB又はLSBである請求項1〜6のいずれか一項に記載の半導体テスト回路。 - 複数のフリップフロップと組み合わせ回路とを有するデジタルブロックを、スキャンクロックと、スキャンデータ信号と、スキャンイネーブル信号と、によりスキャンテストを行うICチップであって、

スキャンクロックが入力される第1のPAD(SCANCLK)と、

スキャンデータ信号が入力される第2のPAD(SCANIN)と、

前記第2のPADに接続され、前記スキャンデータ信号から前記スキャンイネーブル信号を出力するカウンタと、

を備えるICチップ。 - 前記カウンタのクロックラインに、前記第2のPADが接続され、

前記カウンタの第1のリセットラインに、前記第1のPADが論理素子を介して接続される請求項8に記載のICチップ。 - 前記スキャンデータ信号は、前記複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、前記複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるパルス信号と、を有する請求項8又は9に記載のICチップ。

- 前記データ信号を前記複数のフリップフロップに、前記スキャンクロックに同期して設定するために順次データが入力された後、次にスキャンクロックが配されるまでの間に、前記パルス信号が配される請求項10に記載のICチップ。

- 前記次のスキャンクロックが配された後、別のデータ信号を前記複数のフリップフロップに、前記スキャンクロックに同期して設定するために順次データが入力されるまでの間に、前記パルス信号が配される請求項11に記載のICチップ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014063880A JP6211971B2 (ja) | 2014-03-26 | 2014-03-26 | 半導体テスト回路及びicチップ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014063880A JP6211971B2 (ja) | 2014-03-26 | 2014-03-26 | 半導体テスト回路及びicチップ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015184265A JP2015184265A (ja) | 2015-10-22 |

| JP6211971B2 true JP6211971B2 (ja) | 2017-10-11 |

Family

ID=54350934

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014063880A Active JP6211971B2 (ja) | 2014-03-26 | 2014-03-26 | 半導体テスト回路及びicチップ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6211971B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111682867B (zh) * | 2020-06-19 | 2024-04-02 | 深圳市麦积电子科技有限公司 | 一种触发电路 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2624169B2 (ja) * | 1994-04-15 | 1997-06-25 | 日本電気株式会社 | スキャンパスを有する論理集積回路 |

| JPH0989993A (ja) * | 1995-09-27 | 1997-04-04 | Kawasaki Steel Corp | スキャン回路 |

| JP2003121499A (ja) * | 2001-10-09 | 2003-04-23 | Hitachi Ltd | 組込みテスト機能付き半導体集積回路、テストコード生成プログラムから成る電子設計データを保存する記憶媒体、該半導体集積回路のテスト方法、テストコード生成自動化方法及びそのプログラム |

| JP2004347537A (ja) * | 2003-05-23 | 2004-12-09 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| JP4963196B2 (ja) * | 2006-07-12 | 2012-06-27 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置 |

| JP2013036960A (ja) * | 2011-08-11 | 2013-02-21 | Renesas Electronics Corp | 遅延スキャンテスト方法、半導体装置及び半導体装置の設計方法 |

| US8972807B2 (en) * | 2012-05-14 | 2015-03-03 | Texas Instruments Incorporated | Integrated circuits capable of generating test mode control signals for scan tests |

-

2014

- 2014-03-26 JP JP2014063880A patent/JP6211971B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015184265A (ja) | 2015-10-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100442074C (zh) | 通过单个测试访问端口连接多个测试访问端口控制器 | |

| JPS63182585A (ja) | テスト容易化機能を備えた論理回路 | |

| JP2008275479A (ja) | スキャンテスト回路、及びスキャンテスト制御方法 | |

| JP2010276479A (ja) | 半導体集積回路、及びそのテスト方法 | |

| US20160349318A1 (en) | Dynamic Clock Chain Bypass | |

| CN111624478B (zh) | 一种时钟信号控制电路及设备 | |

| US9021323B1 (en) | Test techniques and circuitry | |

| JPWO2006132329A1 (ja) | マイクロコンピュータ及びそのテスト方法 | |

| CN101371151B (zh) | 减少的插脚计数扫描链实施方案 | |

| JP2017015597A (ja) | 集積回路におけるセルフテスト回路およびデータ処理回路 | |

| JP6211971B2 (ja) | 半導体テスト回路及びicチップ | |

| JP2009122009A (ja) | テスト回路 | |

| US20170146600A1 (en) | Scan Logic For Circuit Designs With Latches And Flip-Flops | |

| US7456657B2 (en) | Common input/output terminal control circuit | |

| JP2006145307A (ja) | スキャンテスト回路 | |

| US20100033189A1 (en) | Semiconductor integrated circuit and test method using the same | |

| JP2003121497A (ja) | 論理回路テスト用スキャンパス回路及びこれを備えた集積回路装置 | |

| US11017135B2 (en) | Scan logic for circuit designs with latches and flip-flops | |

| JP5761819B2 (ja) | スキャン非同期記憶素子およびそれを備えた半導体集積回路ならびにその設計方法およびテストパターン生成方法 | |

| US10288682B2 (en) | Integrated electronic device having a test architecture, and test method thereof | |

| JP6534592B2 (ja) | スキャンテスト回路及びスキャンテスト装置 | |

| JP4610919B2 (ja) | 半導体集積回路装置 | |

| JP6459806B2 (ja) | 半導体集積回路 | |

| CN113391178A (zh) | 用于检测有缺陷逻辑装置的方法及设备 | |

| CN1793999B (zh) | 半导体集成电路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161208 |

|

| TRDD | Decision of grant or rejection written | ||

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170831 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170905 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170914 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6211971 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |