JP6094290B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP6094290B2 JP6094290B2 JP2013056496A JP2013056496A JP6094290B2 JP 6094290 B2 JP6094290 B2 JP 6094290B2 JP 2013056496 A JP2013056496 A JP 2013056496A JP 2013056496 A JP2013056496 A JP 2013056496A JP 6094290 B2 JP6094290 B2 JP 6094290B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- wiring layer

- plating

- wiring

- conductive layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/531—Shapes of wire connectors

- H10W72/536—Shapes of wire connectors the connected ends being ball-shaped

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/59—Bond pads specially adapted therefor

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

この態様によれば、配線層の外周の少なくとも一部に沿って導電層が位置し、第1メッキ層を形成する際のメッキ液の液流を導電層が緩和するので、配線層の上に位置する第1メッキ層に段差が形成されることを抑制することができる。

このように、導電層の上に位置する第2メッキ層の膜厚にばらつきがある場合でも、第1メッキ層を形成する際のメッキ液の液流を導電層が緩和するので、第1メッキ層の膜厚のばらつきを低減でき、第1メッキ層に段差が形成されることを抑制することができる。

これによれば、導電層が配線層の外周を構成する多角形の複数の辺に沿って位置し、第1メッキ層を形成する際のメッキ液の液流を導電層が緩和するので、配線層の上に位置する第1メッキ層に段差が形成されることを複数の辺に沿って抑制することができる。

これによれば、配線層の上に位置する第1メッキ層に段差が形成されることを配線層の外周の全周に沿って抑制することができる。

これによれば、配線層の上に位置する第1メッキ層に段差が形成されることを配線層の外周の全周にわたって抑制することができる。

この態様によれば、配線層の外周の少なくとも一部に沿って導電層が位置し、かつ、導電層の位置が配線層の位置よりもメッキ液流の上流側となるので、配線層の上に位置する第1メッキ層を形成する際のメッキ液の液流を導電層が緩和し、第1メッキ層に段差が形成されることを抑制することができる。

この態様によれば、配線層の外周の少なくとも一部に沿って導電層が位置するので、配線層の上に位置する第1メッキ層を形成する際のメッキ液の液流を導電層が緩和し、第1メッキ層に段差が形成されることを抑制することができる。

図1は、本発明の実施形態に係る半導体装置を示す図である。図1(A)は半導体ウエハーの平面図であり、図1(B)は図1(A)に示される半導体ウエハーから分離された1つの半導体チップの平面図であり、図1(C)は図1(B)に示される半導体チップのIC−IC線における拡大断面図である。

図1(B)に示されるように、配線層40の外周は、平面視で方形(長方形又は正方形)となっている

図1(B)に示されるように、導電層50は、配線層40の外周の全周に沿って位置している。導電層50は、配線層40の外周の全周に沿って連続した形状を有するのが望ましい。導電層50は、配線層40とほぼ同じ厚さでもよいし、配線層40より厚くてもよい。

図1に示された実施形態によれば、配線層40の外周に沿って導電層50を形成しておくことにより、配線層40の上の第1メッキ層60の厚みがほぼ一定で、第1メッキ層60の上面が平坦となるため、電極22と電気的に接続するためのボンディングワイヤー80を第1メッキ層60に固定するための面積を第1メッキ層60の上面に確保することができる。

また、ニッケル層61及びこれを含む第1メッキ層60の厚みがほぼ一定となるため、ニッケル層61又は第1メッキ層60の形成後の外観検査工程において、異常品として検出される可能性が低減され、製品製造を円滑化することができる。

図2は、本発明の実施形態に係る半導体装置の導電層の形状に関する変形例を示す平面図である。本発明においては、導電層50(図1参照)が図1に示される形状である場合に限定されず、以下に述べるように他の形状であってもよい。

図3は、本発明の実施形態に係る半導体装置の配線層及び導電層の配置に関する変形例を示す平面図である。本発明においては、導電層50(図1参照)が1つ1つの配線層40を個別に囲んでいる場合に限定されず、以下に述べるように他の配置であってもよい。

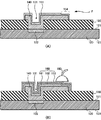

図4及び図5は、本発明の実施形態に係る半導体装置を製造する方法の1つの例を示す断面図である。まず、図4(A)に示されるように、半導体基板20に、半導体基板20の第1の面21に電極22が位置するように、電子回路(図示せず)を形成する。

本実施形態によれば、ニッケル層61の厚みがほぼ一定であるため、パラジウム層62及び金層63の厚みもほぼ一定に形成され、第1メッキ層60全体の厚みもほぼ一定となる。従って、ボンディングワイヤー80(図1参照)を第1メッキ層60に固定するための面積を第1メッキ層60の上面に確保することができる。

以上の工程により、半導体装置を製造することができる。

Claims (12)

- 第1の面を有する半導体基板と、

前記半導体基板に位置し、前記第1の面に電極を有する電子回路と、

前記第1の面の上に位置し、前記電極の上に開口を有する樹脂と、

前記樹脂の上の第1領域及び前記開口内にまたがって位置し、前記電極と電気的に接続された配線層と、

前記樹脂の上の第2領域に、前記配線層の外周の少なくとも一部に沿って位置する導電層と、

前記配線層の上に位置する第1メッキ層及び前記導電層の上に位置する第2メッキ層と、

前記第1メッキ層に固定されたボンディングワイヤーと、

を含む半導体装置。 - 第1の面を有する半導体基板と、

前記半導体基板に位置し、前記第1の面に電極を有する電子回路と、

前記第1の面の上に位置し、前記電極の上に開口を有する絶縁層と、

前記絶縁層の上の第1領域及び前記開口内にまたがって位置し、前記電極と電気的に接続された配線層と、

前記絶縁層の上の第2領域に、前記配線層の外周の少なくとも一部に沿って位置する導電層と、

前記配線層の上に位置する第1メッキ層及び前記導電層の上に位置する第2メッキ層と、

を含み、

前記第2メッキ層は、第1の位置における膜厚が、前記第1の位置よりも前記配線層に近い第2の位置における膜厚よりも小さい半導体装置。 - 前記配線層の外周は平面視で多角形であり、

前記導電層は、前記配線層の外周を構成する多角形の複数の辺に沿って位置する、

請求項1又は請求項2記載の半導体装置。 - 前記導電層は、前記配線層の外周の全周に沿って位置する、

請求項1乃至請求項3のいずれか一項記載の半導体装置。 - 前記導電層は、前記配線層の外周の全周に沿って連続した形状を有する、

請求項1乃至請求項3のいずれか一項記載の半導体装置。 - 前記導電層の内周と、前記配線層の外周との距離が、前記配線層の外周の全周にわたってほぼ等しい、請求項4又は請求項5記載の半導体装置。

- 前記配線層の外周は平面視で方形であり、

前記導電層の内周は平面視で前記配線層の外周を囲む方形であり、

前記配線層の外周を構成する方形の第1の頂点から、前記導電層の内周を構成する方形の前記第1の頂点に対向する第2の頂点までの距離aが、前記配線層の外周を構成する方形の第1の辺から、前記導電層の内周を構成する方形の前記第1の辺に対向する第2の辺までの距離bより大きい、

請求項4又は請求項5記載の半導体装置。 - 前記電子回路、前記絶縁層、前記配線層、前記導電層、前記第1メッキ層及び前記第2メッキ層は、半導体ウエハーから分離された複数のチップのうちの1つに含まれている、

請求項2記載の半導体装置。 - 前記第1メッキ層及び前記第2メッキ層は、いずれもニッケル(Ni)を含む、

請求項1乃至請求項8のいずれか一項記載の半導体装置。 - 前記第1メッキ層及び前記第2メッキ層は、いずれも無電解メッキ法によって形成されている、

請求項1乃至請求項9のいずれか一項記載の半導体装置。 - 半導体基板に、前記半導体基板の第1の面に電極が位置する電子回路を形成する工程(a)と、

前記第1の面の上に、前記電極の上に開口を有する絶縁層を形成する工程(b)と、

前記絶縁層の上の第1領域及び前記開口内に、前記電極と電気的に接続された配線層を形成するとともに、前記絶縁層の上の第2領域に、前記配線層の外周の少なくとも一部に沿って位置する導電層を形成する工程(c)と、

前記配線層の上に位置する第1メッキ層及び前記導電層の上に位置する第2メッキ層を形成する工程(d)と、

を含み、

前記工程(d)は、前記導電層の位置が前記配線層の位置よりもメッキ液流の上流側となるように、前記半導体基板を前記メッキ液流に浸すことを含み、

前記第2メッキ層は、第1の位置における膜厚が、前記第1の位置よりも前記配線層に近い第2の位置における膜厚よりも小さい、

半導体装置の製造方法。 - 半導体基板に、前記半導体基板の第1の面に電極が位置する電子回路を形成する工程(a)と、

前記第1の面の上に、前記電極の上に開口を有する絶縁層を形成する工程(b)と、

前記絶縁層の上の第1領域及び前記開口内に、前記電極と電気的に接続された配線層を形成するとともに、前記絶縁層の上の第2領域に、前記配線層の外周の少なくとも一部に沿って位置する導電層を形成する工程(c)と、

前記配線層の上に位置する第1メッキ層及び前記導電層の上に位置する第2メッキ層を無電解メッキ法によって形成する工程(d)と、

を含み、

前記第2メッキ層は、第1の位置における膜厚が、前記第1の位置よりも前記配線層に近い第2の位置における膜厚よりも小さい、

半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013056496A JP6094290B2 (ja) | 2013-03-19 | 2013-03-19 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013056496A JP6094290B2 (ja) | 2013-03-19 | 2013-03-19 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014183177A JP2014183177A (ja) | 2014-09-29 |

| JP6094290B2 true JP6094290B2 (ja) | 2017-03-15 |

Family

ID=51701606

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013056496A Expired - Fee Related JP6094290B2 (ja) | 2013-03-19 | 2013-03-19 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6094290B2 (ja) |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4277692B2 (ja) * | 2004-01-15 | 2009-06-10 | 株式会社デンソー | 半導体装置の製造方法 |

| US20090057909A1 (en) * | 2007-06-20 | 2009-03-05 | Flipchip International, Llc | Under bump metallization structure having a seed layer for electroless nickel deposition |

| JP2011258687A (ja) * | 2010-06-08 | 2011-12-22 | Renesas Electronics Corp | 半導体装置およびその製造方法 |

-

2013

- 2013-03-19 JP JP2013056496A patent/JP6094290B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014183177A (ja) | 2014-09-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7363972B2 (ja) | 貫通電極基板及びその製造方法、並びに実装基板 | |

| JP5143451B2 (ja) | 半導体装置及びその製造方法 | |

| US20100032196A1 (en) | Multilayer wiring board, semiconductor package and method of manufacturing the same | |

| KR101307030B1 (ko) | 반도체 소자 탑재용 기판 및 그 제조 방법 | |

| US20180047691A1 (en) | Semiconductor device and manufacturing method thereof | |

| JP5151158B2 (ja) | パッケージ、およびそのパッケージを用いた半導体装置 | |

| CN102473639B (zh) | 半导体装置的制造方法及半导体装置 | |

| US9673139B2 (en) | Semiconductor device | |

| JP6109078B2 (ja) | リードクラックが強化された電子素子用テープ | |

| JP6936963B2 (ja) | リードフレーム | |

| JP2011014644A (ja) | 配線基板およびその製造方法 | |

| JP2008218932A (ja) | 半導体素子搭載用基板およびその製造方法 | |

| JP6094290B2 (ja) | 半導体装置及びその製造方法 | |

| JP6617955B2 (ja) | リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 | |

| WO2006112337A1 (ja) | 半導体装置および半導体装置の製造方法 | |

| TWI538597B (zh) | 電路板及電路板的製造方法 | |

| US20140091472A1 (en) | Semiconductor device and manufacturing method of the same | |

| JP6757213B2 (ja) | 半導体装置の製造方法 | |

| JP4288277B2 (ja) | 半導体装置 | |

| JP4010298B2 (ja) | 半導体装置及びその製造方法、回路基板並びに電子機器 | |

| JP5991712B2 (ja) | 半導体素子搭載用基板及びその製造方法 | |

| TWI435427B (zh) | 半導體承載件暨封裝件及其製法 | |

| JP7254602B2 (ja) | 半導体装置、および半導体装置の製造方法 | |

| JP4552978B2 (ja) | 半導体装置及びその製造方法、回路基板並びに電子機器 | |

| JP5807815B2 (ja) | 半導体装置およびその製造方法、ならびに半導体装置用基板およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20151124 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160913 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160915 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161027 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170117 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170130 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6094290 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |