JP5979781B2 - 表示装置及び表示装置の製造方法 - Google Patents

表示装置及び表示装置の製造方法 Download PDFInfo

- Publication number

- JP5979781B2 JP5979781B2 JP2012130258A JP2012130258A JP5979781B2 JP 5979781 B2 JP5979781 B2 JP 5979781B2 JP 2012130258 A JP2012130258 A JP 2012130258A JP 2012130258 A JP2012130258 A JP 2012130258A JP 5979781 B2 JP5979781 B2 JP 5979781B2

- Authority

- JP

- Japan

- Prior art keywords

- signal line

- semiconductor layer

- display device

- array substrate

- scanning signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 23

- 239000000758 substrate Substances 0.000 claims description 75

- 239000004065 semiconductor Substances 0.000 claims description 61

- 239000004973 liquid crystal related substance Substances 0.000 claims description 57

- 238000000034 method Methods 0.000 claims description 24

- 229910052802 copper Inorganic materials 0.000 claims description 9

- 230000008569 process Effects 0.000 claims description 9

- 230000001678 irradiating effect Effects 0.000 claims description 5

- 229910052751 metal Inorganic materials 0.000 claims description 4

- 229910052793 cadmium Inorganic materials 0.000 claims description 3

- 229910052733 gallium Inorganic materials 0.000 claims description 3

- 229910052738 indium Inorganic materials 0.000 claims description 3

- 229910044991 metal oxide Inorganic materials 0.000 claims description 3

- 150000004706 metal oxides Chemical group 0.000 claims description 3

- 229910052718 tin Inorganic materials 0.000 claims description 3

- 229910052725 zinc Inorganic materials 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 75

- 239000010408 film Substances 0.000 description 30

- 239000000463 material Substances 0.000 description 9

- 239000010409 thin film Substances 0.000 description 9

- 239000010949 copper Substances 0.000 description 8

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 6

- 239000011521 glass Substances 0.000 description 5

- 239000011241 protective layer Substances 0.000 description 5

- 230000005684 electric field Effects 0.000 description 4

- 210000002858 crystal cell Anatomy 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 230000010287 polarization Effects 0.000 description 3

- 238000002834 transmittance Methods 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 239000003566 sealing material Substances 0.000 description 1

- 238000009751 slip forming Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- XLOMVQKBTHCTTD-UHFFFAOYSA-N zinc oxide Inorganic materials [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 1

- 229960001296 zinc oxide Drugs 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134363—Electrodes characterised by their geometrical arrangement for applying an electric field parallel to the substrate, i.e. in-plane switching [IPS]

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/127—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- General Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Optics & Photonics (AREA)

- Mathematical Physics (AREA)

- Manufacturing & Machinery (AREA)

- Geometry (AREA)

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

Description

Claims (6)

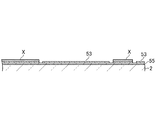

- アレイ基板を用意する工程と、

前記アレイ基板上に走査信号線を形成する工程と、

前記アレイ基板上にゲート絶縁膜を形成する工程と、

前記アレイ基板上に酸化物半導体の層を形成する工程と、

前記アレイ基板上に映像信号線を形成する工程であって、平面視において、前記映像信号線のうち前記走査信号線と直交する方向に延伸する部分と、前記走査信号線とが重なる領域内において前記酸化物半導体の層の一部分と重なり合うように映像信号線を形成する工程と、

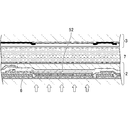

前記酸化物半導体の層の一部分にエネルギー線を照射して画素電極を形成する工程と、

を有する表示装置の製造方法。 - 前記酸化物半導体の層は、平面視において、その一部分が前記ゲート絶縁膜を介して前記走査信号線と重なり合うように形成される請求項1記載の表示装置の製造方法。

- 前記エネルギー線を照射して画素電極を形成する工程は、前記アレイ基板とカラーフィルタ基板を液晶層を狭持するよう貼り合わせた後に実施される請求項1または2記載の表示装置の製造方法。

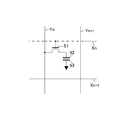

- アレイ基板と、

前記アレイ基板上に形成された映像信号線と走査信号線により区画された複数の画素と、

前記画素内に配置された透明電極によって構成された共通電極と、

前記画素毎に配置されるTFTと、

前記画素内に前記共通電極上に絶縁層を介して重畳するように配置された画素電極と、

前記映像信号線上に絶縁層を介して重畳する遮蔽電極を有し、

前記TFTのチャネル半導体層と前記画素電極は一続きに連続する酸化物半導体の層であり、

平面視において、前記映像信号線のうち前記走査信号線と直交する方向に延伸する部分と、前記走査信号線とが重なる領域内において前記チャネル半導体層と前記映像信号線とが接する表示装置。 - 前記酸化物半導体は、In、Ga,Zn、Sn、Cu、Cdから選択された1つ乃至複数の金属元素を含む金属酸化物である請求項4記載の表示装置。

- 平面視において、前記チャネル半導体層は、ゲート絶縁膜を介して前記走査信号線と重なり合い、

前記走査信号線は、前記TFTのゲート電極として機能する請求項4又は5記載の表示装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012130258A JP5979781B2 (ja) | 2012-06-07 | 2012-06-07 | 表示装置及び表示装置の製造方法 |

| PCT/JP2013/003072 WO2013183230A1 (ja) | 2012-06-07 | 2013-05-14 | 液晶表示装置及び液晶表示装置の製造方法 |

| US14/539,506 US9847350B2 (en) | 2012-06-07 | 2014-11-12 | Liquid crystal display device and method of manufacturing a liquid crystal display device |

| US15/811,130 US10276595B2 (en) | 2012-06-07 | 2017-11-13 | Liquid crystal display device and method of manufacturing a liquid crystal display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012130258A JP5979781B2 (ja) | 2012-06-07 | 2012-06-07 | 表示装置及び表示装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013254121A JP2013254121A (ja) | 2013-12-19 |

| JP2013254121A5 JP2013254121A5 (ja) | 2015-02-19 |

| JP5979781B2 true JP5979781B2 (ja) | 2016-08-31 |

Family

ID=49711639

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012130258A Active JP5979781B2 (ja) | 2012-06-07 | 2012-06-07 | 表示装置及び表示装置の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US9847350B2 (ja) |

| JP (1) | JP5979781B2 (ja) |

| WO (1) | WO2013183230A1 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105097710A (zh) * | 2014-04-25 | 2015-11-25 | 上海和辉光电有限公司 | 薄膜晶体管阵列基板及其制造方法 |

| JP6436660B2 (ja) | 2014-07-07 | 2018-12-12 | 三菱電機株式会社 | 薄膜トランジスタ基板およびその製造方法 |

| TW201614850A (en) * | 2014-10-01 | 2016-04-16 | Chunghwa Picture Tubes Ltd | Thin film transistor and manufacturing method thereof |

| WO2017150617A1 (ja) * | 2016-03-02 | 2017-09-08 | 国立研究開発法人産業技術総合研究所 | 半導体-絶縁体可逆変化薄膜及びその製造方法 |

| WO2017158967A1 (ja) * | 2016-03-18 | 2017-09-21 | 三菱電機株式会社 | 薄膜トランジスタ、薄膜トランジスタ基板、液晶表示装置および薄膜トランジスタの製造方法 |

| CN111722445A (zh) * | 2019-03-22 | 2020-09-29 | 咸阳彩虹光电科技有限公司 | 一种阵列基板、液晶显示面板及显示装置 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6397919A (ja) * | 1986-10-15 | 1988-04-28 | Seiko Epson Corp | 液晶パネル |

| JP2003050405A (ja) * | 2000-11-15 | 2003-02-21 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタアレイ、その製造方法およびそれを用いた表示パネル |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| KR101096718B1 (ko) * | 2004-12-24 | 2011-12-22 | 엘지디스플레이 주식회사 | 수평 전계 박막 트랜지스터 기판의 제조 방법 |

| JP2010147351A (ja) * | 2008-12-20 | 2010-07-01 | Videocon Global Ltd | 液晶表示装置及びその製造方法 |

| JP2010230744A (ja) * | 2009-03-26 | 2010-10-14 | Videocon Global Ltd | 液晶表示装置及びその製造方法 |

| JP2010263064A (ja) | 2009-05-07 | 2010-11-18 | Videocon Global Ltd | 薄膜トランジスタ、液晶表示装置及びこれらの製造方法 |

| JP5589408B2 (ja) * | 2010-01-28 | 2014-09-17 | 三菱電機株式会社 | 液晶表示装置 |

| WO2013115052A1 (ja) * | 2012-01-31 | 2013-08-08 | シャープ株式会社 | 半導体装置およびその製造方法 |

-

2012

- 2012-06-07 JP JP2012130258A patent/JP5979781B2/ja active Active

-

2013

- 2013-05-14 WO PCT/JP2013/003072 patent/WO2013183230A1/ja active Application Filing

-

2014

- 2014-11-12 US US14/539,506 patent/US9847350B2/en active Active

-

2017

- 2017-11-13 US US15/811,130 patent/US10276595B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US10276595B2 (en) | 2019-04-30 |

| WO2013183230A1 (ja) | 2013-12-12 |

| JP2013254121A (ja) | 2013-12-19 |

| US20180069029A1 (en) | 2018-03-08 |

| US9847350B2 (en) | 2017-12-19 |

| US20150069388A1 (en) | 2015-03-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10276595B2 (en) | Liquid crystal display device and method of manufacturing a liquid crystal display device | |

| JP5659708B2 (ja) | 液晶表示パネル、及び液晶表示装置 | |

| CN103728799B (zh) | 具有最小边框的液晶显示装置 | |

| JP4589256B2 (ja) | 横電界方式の液晶表示素子及びその製造方法 | |

| JP3871764B2 (ja) | 反射型の表示装置 | |

| KR20160114510A (ko) | 터치 패널 | |

| TWI307803B (en) | Transflective liquid crystal display | |

| TWI519878B (zh) | 顯示面板及其製作方法 | |

| US20140339563A1 (en) | Pixel structure, display panel and method for fabricating pixel structure | |

| US8553192B2 (en) | Liquid crystal display | |

| JP2003195330A (ja) | 液晶表示装置 | |

| US9853164B2 (en) | Semiconductor device and display device | |

| JP6050379B2 (ja) | 表示装置 | |

| JP6775325B2 (ja) | 薄膜トランジスタ基板および液晶表示装置 | |

| CN108508661B (zh) | 液晶显示面板及液晶显示装置 | |

| EP2821845B1 (en) | Liquid crystal display device | |

| WO2012090788A1 (ja) | 表示素子 | |

| US20120319144A1 (en) | Display panel and display device | |

| JP2008165029A (ja) | 液晶表示装置 | |

| CN106066551A (zh) | 一种阵列基板及显示装置 | |

| US20110304791A1 (en) | Display device | |

| US20120081273A1 (en) | Pixel structure, pixel array and display panel | |

| US9684216B2 (en) | Pixel structure and fabrication method thereof | |

| JP2007248903A (ja) | 液晶表示装置及び液晶表示装置の製造方法 | |

| KR102081604B1 (ko) | 액정표시장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20141218 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20141218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20151014 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20151208 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160204 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160719 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160725 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5979781 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |