JP5776669B2 - エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 - Google Patents

エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 Download PDFInfo

- Publication number

- JP5776669B2 JP5776669B2 JP2012249221A JP2012249221A JP5776669B2 JP 5776669 B2 JP5776669 B2 JP 5776669B2 JP 2012249221 A JP2012249221 A JP 2012249221A JP 2012249221 A JP2012249221 A JP 2012249221A JP 5776669 B2 JP5776669 B2 JP 5776669B2

- Authority

- JP

- Japan

- Prior art keywords

- silicon wafer

- epitaxial

- epitaxial silicon

- manufacturing

- carbon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P30/00—Ion implantation into wafers, substrates or parts of devices

- H10P30/20—Ion implantation into wafers, substrates or parts of devices into semiconductor materials, e.g. for doping

- H10P30/224—Ion implantation into wafers, substrates or parts of devices into semiconductor materials, e.g. for doping of a cluster, e.g. using a gas cluster ion beam

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/011—Manufacture or treatment of image sensors covered by group H10F39/12

- H10F39/026—Wafer-level processing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/22—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials using physical deposition, e.g. vacuum deposition or sputtering

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/24—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials using chemical vapour deposition [CVD]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/29—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials characterised by the substrates

- H10P14/2901—Materials

- H10P14/2902—Materials being Group IVA materials

- H10P14/2905—Silicon, silicon germanium or germanium

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/34—Deposited materials, e.g. layers

- H10P14/3402—Deposited materials, e.g. layers characterised by the chemical composition

- H10P14/3404—Deposited materials, e.g. layers characterised by the chemical composition being Group IVA materials

- H10P14/3411—Silicon, silicon germanium or germanium

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/34—Deposited materials, e.g. layers

- H10P14/3438—Doping during depositing

- H10P14/3441—Conductivity type

- H10P14/3442—N-type

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/36—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials characterised by treatments done before the formation of the materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P36/00—Gettering within semiconductor bodies

- H10P36/03—Gettering within semiconductor bodies within silicon bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P36/00—Gettering within semiconductor bodies

- H10P36/20—Intrinsic gettering, i.e. thermally inducing defects by using oxygen present in the silicon body

Landscapes

- Recrystallisation Techniques (AREA)

- Crystals, And After-Treatments Of Crystals (AREA)

- Chemical Vapour Deposition (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Physical Vapour Deposition (AREA)

Description

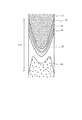

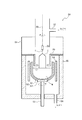

ルツボ52の外側には、ルツボ52を囲繞する抵抗加熱式のヒーター54が配設され、その外側には、チャンバー51の内面に沿って断熱材60が配設されている。ルツボ52の上方には、ルツボ回転昇降軸53と同軸上で逆方向または同一方向に所定の速度で回転するワイヤなどの引き上げ軸55が配され、この引き上げ軸55の下端に取り付けた種結晶保持器56によって種結晶Sが保持されている。

チャンバー51内には、ルツボ52内の上方で育成中のインゴットIを囲繞する円筒状の熱遮蔽体59が配置されている。熱遮蔽体59は、育成中のインゴットIに対して、ルツボ52内の原料融液Mやヒーター54やルツボ52の側壁からの高温の輻射熱を入光量や、結晶成長界面近傍の熱の拡散量を調整するもので、単結晶インゴット中心部および単結晶インゴット外周部の引き上げ軸方向の温度勾配を制御する役割を担う。

チャンバー51の上部には、Arガスなどの不活性ガスをチャンバー51内に導入するガス導入口57が設けられている。チャンバー51の下部には、図示しない真空ポンプの駆動によりチャンバー51内の気体を吸引して排出する排気口58が設けられている。ガス導入口57からチャンバー51内に導入された不活性ガスは、育成中のシリコン単結晶インゴットIと熱遮蔽体59との間を下降し、熱遮蔽体59の下端と原料融液Mの液面との隙間を経た後、熱遮蔽体59の外側、さらにルツボ52の外側に向けて流れ、その後にルツボ52の外側を下降し、排気口58から排出される。

本実施例では、径方向全域にわたり無欠陥領域となる単結晶インゴットを育成できるように、育成中の単結晶インゴットの温度が融点から1300℃までの範囲にて、引き上げ軸方向の単結晶インゴット中心部の温度勾配Gcと単結晶インゴット外周部の温度勾配Geとの関係がGc/Ge>1の条件を満足するように、熱遮蔽体59の寸法形状や設置高さ位置を設定した状態で、引き上げ速度を高速(1.0mm/分)から低速(0.3mm/分)まで変化させるようにして、直胴部長さ方向に結晶領域分布が異なるようにして単結晶インゴットIを育成した。育成した単結晶シリコンインゴットIは、結晶方位<100>、直胴部直径310mm、リンドープ(1×1015atoms/cm3〜1×1017atoms/cm3)したn型の単結晶シリコンインゴットであり、インゴットIの酸素濃度(ASTM F121-1979)は12〜14×1017atoms/cm3である。

ウェーハ(a):ウェーハ全面がCOP発生領域

ウェーハ(b):OSF潜在核領域とPv(1)領域とからなる混合領域

ウェーハ(c):OSF潜在核領域とPv(2)領域とからなる混合領域

ウェーハ(d):Pv(2)領域とPi領域とからなる混合領域

上述のように作製されたウェーハ(b)を用い、クラスターイオン発生装置(日新イオン機器社製、型番:CLARIS)を用いて、クラスターイオンとしてC5H5クラスターを生成し、ドーズ量9.00×1013Clusters/cm2(炭素のドーズ量4.50×1014atoms/cm2)、炭素1原子当たりの加速電圧14.8keV/atomの条件で、シリコンウェーハに照射した。その後、シリコンウェーハをHF洗浄した後、枚葉式エピタキシャル成長装置(アプライドマテリアルズ社製)内に搬送し、装置内で1120℃の温度で30秒の水素ベーク処理を施した後、水素をキャリアガス、トリクロロシランをソースガスとして1150℃でCVD法により、シリコンウェーハ上にシリコンのエピタキシャル層(厚さ:8μm、ドーパント種類:リン、ドーパント濃度:1×1015atoms/cm3)をエピタキシャル成長させ、本発明に従うシリコンエピタキシャルウェーハとした。

基板としてのシリコンウェーハをウェーハ(c)(本発明例2)およびウェーハ(d)(本発明例3)に変更した以外は、本発明例1と同様にして本発明に従うエピタキシャルシリコンウェーハを製造した。なお、本発明例1〜3では、80keV/Clusterでクラスターイオンを照射したが、各クラスターは、5の炭素原子(原子量12)および5の水素原子(原子量1)からなる。そのため、炭素原子1つが受けるエネルギーは、80×{12×5/(12×5+1×5)}/5≒14.8keVとなる。

クラスターイオン照射工程に替えて、CO2を材料ガスとして、炭素のモノマーイオンを生成し、ドーズ量9.00×1013atoms/cm2、加速電圧300keV/atomの条件でモノマーイオン注入工程を行った以外は、本発明例1〜3と同様にして、比較例にかかるエピタキシャルシリコンウェーハを製造した。具体的には、比較例1〜3では、基板としてそれぞれウェーハ(b)〜(d)を用い、炭素のモノマーイオンを300keVの加速電圧でシリコンウェーハに照射した。

シリコンウェーハを、ウェーハ(a)に変更した以外は、本発明例1と同様にして比較例にかかるエピタキシャルシリコンウェーハを製造した。

シリコンウェーハを、ウェーハ(a)に変更した以外は、比較例1と同様にして比較例にかかるエピタキシャルシリコンウェーハを製造した。

まず、クラスターイオンの照射直後と、モノマーイオンの注入直後における、炭素の分布の相違を明らかにするため、本発明例3および比較例3について、エピタキシャル層形成の前のシリコンウェーハについて、SIMS測定を行った。得られた炭素濃度プロファイルを図6に参考に示す。ここで、図6の横軸の深さはシリコンウェーハの表面をゼロとしている。

本発明例および比較例で作製した各サンプルのシリコンウェーハ表面を、Ni汚染液(1.0×1012/cm2)で、それぞれスピンコート汚染法を用いて故意に汚染し、引き続き900℃、30分の熱処理を施した。その後、SIMS測定を行った。測定結果を代表して、本発明例3および比較例3についてのNi濃度プロファイルを、それぞれ炭素濃度プロファイルとともに示す(図7(A),(B))。他の本発明例および比較例については、ゲッタリング能力評価の結果を表1に示す。なお、評価基準をNi濃度プロファイルのピーク濃度の値によって以下のとおりに分類した。

◎:1.0×1017atoms/cm3以上

○:5.0×1016atoms/cm3以上1.0×1017atoms/cm3未満

△:1.0×1016atoms/cm3以上5.0×1016atoms/cm3未満

本発明例および比較例で作製した各サンプルのエピタキシャルウェーハの表面を、KLA−Tenchor社製:Surfscan SP−2を用いて観察評価し、LPDの発生状況を調べた。その際、観察モードはObliqueモード(斜め入射モード)とし、表面ピットの推定は、Wide Narrowチャンネルの検出サイズ比に基づいて行った。続いて、走査型電子顕微鏡(SEM:Scanning Electron Microscope)を用いて、LPDの発生部位を観察評価して、LPDが積層欠陥(SF:Stacking Fault)であるか否かを評価した。その後、収束イオンビーム(FIB:Focused Ion Beam)加工により、SFの発生部位を含む断面観察用評価サンプルを作製した。最後に、この評価サンプルを透過型電子顕微鏡(TEM:Transmission Electron Microscope)を用いて観察評価して、COP起因のSFであるか否かを評価した。SFの個数を表1に示す。

10 シリコンウェーハ

10A シリコンウェーハの表面

16 クラスターイオン

18 改質層

20 エピタキシャル層

41 COP発生領域

42 OSF潜在核領域

43 酸素析出促進領域(Pv(1)領域)

44 酸素析出促進領域(Pv(2)領域)

45 酸素析出抑制領域(Pi領域)

46 転位クラスター領域

50 単結晶製造装置

51 チャンバー

52 ルツボ

52a 石英ルツボ

52b 黒鉛ルツボ

53 ルツボ回転昇降軸

54 ヒーター

55 引き上げ軸

56 種結晶保持器

57 ガス導入口

58 排気口

59 熱遮蔽体

60 断熱材

I 単結晶シリコンインゴット

S 種結晶

M 原料融液

Claims (13)

- 転位クラスターおよびCOPを含まないシリコンウェーハに、ゲッタリングに寄与する構成元素を含むクラスターイオンを照射して、該シリコンウェーハの表面に、前記クラスターイオンの構成元素から形成された改質層を形成する第1工程と、

前記シリコンウェーハの改質層上にエピタキシャル層を形成する第2工程と、

を有し、該第2工程後の改質層における前記構成元素の深さ方向の濃度プロファイルの半値幅が100nm以下であるエピタキシャルシリコンウェーハを得ることを特徴とするエピタキシャルシリコンウェーハの製造方法。 - 前記クラスターイオンが構成元素として炭素を含む、請求項1に記載のエピタキシャルシリコンウェーハの製造方法。

- 前記クラスターイオンが構成元素として炭素を含む2種以上の元素を含む、請求項2に記載のエピタキシャルシリコンウェーハの製造方法。

- 前記第1工程の後、前記シリコンウェーハに対して結晶性回復のための熱処理を行うことなく、前記シリコンウェーハをエピタキシャル成長装置に搬送して第2工程を行う、請求項1〜3のいずれか一項に記載のエピタキシャルシリコンウェーハの製造方法。

- 前記第1工程では、前記シリコンウェーハの表面からの深さが150nm以下の範囲内に、前記改質層における前記構成元素の深さ方向の濃度プロファイルのピークが位置するように、前記クラスターイオンを照射する、請求項1〜4のいずれか一項に記載のエピタキシャルシリコンウェーハの製造方法。

- 前記第1工程は、炭素1原子あたりの加速電圧が50keV/atom以下、クラスターサイズが100個以下、炭素のドーズ量が1×1016atoms/cm2以下の条件で行う、請求項5に記載のエピタキシャルシリコンウェーハの製造方法。

- 前記第1工程は、炭素1原子あたりの加速電圧が40keV/atom以下、クラスターサイズが60個以下、炭素のドーズ量が5×1015atoms/cm2以下の条件で行う、請求項5に記載のエピタキシャルシリコンウェーハの製造方法。

- 転位クラスターおよびCOPを含まないシリコンウェーハと、該シリコンウェーハの表面に形成された、該シリコンウェーハ中に固溶しゲッタリングに寄与する所定元素から形成された改質層と、該改質層上のエピタキシャル層と、を有し、

前記改質層における前記所定元素の深さ方向の濃度プロファイルの半値幅が100nm以下であることを特徴とするエピタキシャルシリコンウェーハ。 - 前記シリコンウェーハの表面からの深さが150nm以下の範囲内に、前記改質層における前記濃度プロファイルのピークが位置する、請求項8に記載のエピタキシャルシリコンウェーハ。

- 前記改質層における前記濃度プロファイルのピーク濃度が、1×1015atoms/cm3以上である、請求項8または9に記載のエピタキシャルシリコンウェーハ。

- 前記所定元素が炭素を含む、請求項8〜10のいずれか一項に記載のエピタキシャルシリコンウェーハ。

- 前記所定元素が炭素を含む2種以上の元素を含む、請求項11に記載のエピタキシャルシリコンウェーハ。

- 請求項1〜7のいずれか一項に記載の製造方法で製造されたエピタキシャルシリコンウェーハまたは請求項8〜12のいずれか一項に記載のエピタキシャルシリコンウェーハの、表面に位置するエピタキシャル層に、固体撮像素子を形成することを特徴とする固体撮像素子の製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012249221A JP5776669B2 (ja) | 2012-11-13 | 2012-11-13 | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 |

| TW102141074A TWI521567B (zh) | 2012-11-13 | 2013-11-12 | 磊晶矽晶圓的製造方法、磊晶矽晶圓及固體攝影元件的製造方法 |

| US14/078,217 US9224601B2 (en) | 2012-11-13 | 2013-11-12 | Method of producing epitaxial silicon wafer, epitaxial silicon wafer, and method of producing solid-state image sensing device |

| US14/946,661 US9396967B2 (en) | 2012-11-13 | 2015-11-19 | Method of producing epitaxial silicon wafer, epitaxial silicon wafer, and method of producing solid-state image sensing device |

| US15/182,443 US9576800B2 (en) | 2012-11-13 | 2016-06-14 | Method of producing epitaxial silicon wafer, epitaxial silicon wafer, and method of producing solid-state image sensing device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012249221A JP5776669B2 (ja) | 2012-11-13 | 2012-11-13 | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014099450A JP2014099450A (ja) | 2014-05-29 |

| JP2014099450A5 JP2014099450A5 (ja) | 2015-04-23 |

| JP5776669B2 true JP5776669B2 (ja) | 2015-09-09 |

Family

ID=50682097

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012249221A Active JP5776669B2 (ja) | 2012-11-13 | 2012-11-13 | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (3) | US9224601B2 (ja) |

| JP (1) | JP5776669B2 (ja) |

| TW (1) | TWI521567B (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20140009565A (ko) * | 2011-05-13 | 2014-01-22 | 가부시키가이샤 사무코 | 반도체 에피택셜 웨이퍼의 제조 방법, 반도체 에피택셜 웨이퍼, 및 고체 촬상 소자의 제조 방법 |

| JP5776669B2 (ja) * | 2012-11-13 | 2015-09-09 | 株式会社Sumco | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 |

| DE102014208815B4 (de) * | 2014-05-09 | 2018-06-21 | Siltronic Ag | Verfahren zur Herstellung einer Halbleiterscheibe aus Silizium |

| JP6566683B2 (ja) * | 2014-07-02 | 2019-08-28 | 東京エレクトロン株式会社 | 基板洗浄方法および基板洗浄装置 |

| US10026843B2 (en) | 2015-11-30 | 2018-07-17 | Taiwan Semiconductor Manufacturing Co., Ltd. | Fin structure of semiconductor device, manufacturing method thereof, and manufacturing method of active region of semiconductor device |

| JP6504082B2 (ja) | 2016-02-29 | 2019-04-24 | 株式会社Sumco | 半導体エピタキシャルウェーハおよびその製造方法ならびに固体撮像素子の製造方法 |

| JP6299835B1 (ja) * | 2016-10-07 | 2018-03-28 | 株式会社Sumco | エピタキシャルシリコンウェーハおよびエピタキシャルシリコンウェーハの製造方法 |

| JP2020501997A (ja) | 2016-12-19 | 2020-01-23 | ユーピーエル リミテッドUpl Limited | 水分バリア包装体 |

| JP6724824B2 (ja) * | 2017-03-08 | 2020-07-15 | 株式会社Sumco | 半導体エピタキシャルウェーハの製造方法、品質予測方法および品質評価方法 |

| CN110164959A (zh) * | 2019-05-15 | 2019-08-23 | 中国电子科技集团公司第十三研究所 | 一种衬底及外延片 |

| JP7207204B2 (ja) * | 2019-07-02 | 2023-01-18 | 信越半導体株式会社 | 炭素ドープシリコン単結晶ウェーハの製造方法 |

| JP7259706B2 (ja) * | 2019-11-06 | 2023-04-18 | 株式会社Sumco | エピタキシャルシリコンウェーハのパッシベーション効果評価方法 |

| CN111273158B (zh) * | 2020-02-26 | 2022-04-15 | 上海韦尔半导体股份有限公司 | 一种排查弹坑的测试方法、装置及智能打线设备 |

| US11551904B2 (en) * | 2020-09-09 | 2023-01-10 | Applied Materials, Inc. | System and technique for profile modulation using high tilt angles |

| CN117316798B (zh) * | 2023-09-28 | 2025-03-21 | 西安奕斯伟材料科技股份有限公司 | 确定产生外延缺陷的部件的方法、装置及介质 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3311004B2 (ja) * | 1991-03-28 | 2002-08-05 | 株式会社東芝 | 固体撮像装置 |

| JP3384506B2 (ja) | 1993-03-30 | 2003-03-10 | ソニー株式会社 | 半導体基板の製造方法 |

| JP3460551B2 (ja) | 1997-11-11 | 2003-10-27 | 信越半導体株式会社 | 結晶欠陥の少ないシリコン単結晶ウエーハ及びその製造方法 |

| JP3816484B2 (ja) * | 2003-12-15 | 2006-08-30 | 日本航空電子工業株式会社 | ドライエッチング方法 |

| WO2005079318A2 (en) * | 2004-02-14 | 2005-09-01 | Epion Corporation | Methods of forming doped and un-doped strained semiconductor and semiconductor films by gas-cluster ion irradiation |

| WO2007070321A2 (en) * | 2005-12-09 | 2007-06-21 | Semequip Inc. | System and method for the manufacture of semiconductor devices by the implantation of carbon clusters |

| WO2007146395A2 (en) * | 2006-06-13 | 2007-12-21 | Semequip, Inc. | Ion beam apparatus and method employing magnetic scanning |

| JP2008294245A (ja) | 2007-05-25 | 2008-12-04 | Shin Etsu Handotai Co Ltd | エピタキシャルウェーハの製造方法およびエピタキシャルウェーハ |

| JP5374883B2 (ja) * | 2008-02-08 | 2013-12-25 | 富士電機株式会社 | 半導体装置およびその製造方法 |

| JP2010040864A (ja) * | 2008-08-06 | 2010-02-18 | Sumco Corp | エピタキシャルシリコンウェーハ及びその製造方法 |

| JP2010114409A (ja) * | 2008-10-10 | 2010-05-20 | Sony Corp | Soi基板とその製造方法、固体撮像装置とその製造方法、および撮像装置 |

| JP5099023B2 (ja) | 2009-01-27 | 2012-12-12 | 信越半導体株式会社 | エピタキシャルウエーハの製造方法及び固体撮像素子の製造方法 |

| JP5515406B2 (ja) * | 2009-05-15 | 2014-06-11 | 株式会社Sumco | シリコンウェーハおよびその製造方法 |

| JP2011054879A (ja) * | 2009-09-04 | 2011-03-17 | Sumco Corp | 裏面照射型イメージセンサ用エピタキシャル基板およびその製造方法。 |

| JP2011151318A (ja) * | 2010-01-25 | 2011-08-04 | Renesas Electronics Corp | 半導体装置およびその製造方法 |

| JP2012059849A (ja) * | 2010-09-08 | 2012-03-22 | Shin Etsu Handotai Co Ltd | シリコンエピタキシャルウェーハおよびシリコンエピタキシャルウェーハの製造方法 |

| JP5776670B2 (ja) | 2012-11-13 | 2015-09-09 | 株式会社Sumco | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 |

| JP5776669B2 (ja) * | 2012-11-13 | 2015-09-09 | 株式会社Sumco | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 |

-

2012

- 2012-11-13 JP JP2012249221A patent/JP5776669B2/ja active Active

-

2013

- 2013-11-12 TW TW102141074A patent/TWI521567B/zh active

- 2013-11-12 US US14/078,217 patent/US9224601B2/en active Active

-

2015

- 2015-11-19 US US14/946,661 patent/US9396967B2/en active Active

-

2016

- 2016-06-14 US US15/182,443 patent/US9576800B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US9396967B2 (en) | 2016-07-19 |

| US20140134779A1 (en) | 2014-05-15 |

| US9224601B2 (en) | 2015-12-29 |

| US20160293426A1 (en) | 2016-10-06 |

| JP2014099450A (ja) | 2014-05-29 |

| US9576800B2 (en) | 2017-02-21 |

| US20160148964A1 (en) | 2016-05-26 |

| TWI521567B (zh) | 2016-02-11 |

| TW201428823A (zh) | 2014-07-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5776669B2 (ja) | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 | |

| JP6278591B2 (ja) | 半導体エピタキシャルウェーハの製造方法、半導体エピタキシャルウェーハ、および固体撮像素子の製造方法 | |

| JP5776670B2 (ja) | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 | |

| JP6065848B2 (ja) | 半導体エピタキシャルウェーハの製造方法、半導体エピタキシャルウェーハ、および固体撮像素子の製造方法 | |

| JP6107068B2 (ja) | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 | |

| JP6427946B2 (ja) | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 | |

| TWI611482B (zh) | 半導體磊晶晶圓的製造方法及固體攝像元件的製造方法 | |

| JP6614066B2 (ja) | シリコン接合ウェーハの製造方法 | |

| JP6427894B2 (ja) | エピタキシャルウェーハの製造方法 | |

| JP6280301B2 (ja) | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 | |

| JP2017123477A (ja) | 半導体エピタキシャルウェーハの製造方法、半導体エピタキシャルウェーハ、および固体撮像素子の製造方法 | |

| JP6361779B2 (ja) | エピタキシャルシリコンウェーハの製造方法、エピタキシャルシリコンウェーハ、および固体撮像素子の製造方法 | |

| JP2015220242A (ja) | 半導体エピタキシャルウェーハの製造方法および固体撮像素子の製造方法 | |

| JP6318728B2 (ja) | 半導体エピタキシャルウェーハの製造方法、半導体エピタキシャルウェーハ、および固体撮像素子の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150304 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150304 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20150304 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20150501 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150609 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150622 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5776669 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |