JP5723377B2 - 半導体のためのエッチングプロセス - Google Patents

半導体のためのエッチングプロセス Download PDFInfo

- Publication number

- JP5723377B2 JP5723377B2 JP2012537938A JP2012537938A JP5723377B2 JP 5723377 B2 JP5723377 B2 JP 5723377B2 JP 2012537938 A JP2012537938 A JP 2012537938A JP 2012537938 A JP2012537938 A JP 2012537938A JP 5723377 B2 JP5723377 B2 JP 5723377B2

- Authority

- JP

- Japan

- Prior art keywords

- etching

- semiconductor

- photoresist

- semiconductors

- reactive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 117

- 238000005530 etching Methods 0.000 title claims description 63

- 238000000034 method Methods 0.000 title claims description 42

- 230000008569 process Effects 0.000 title description 21

- 239000000463 material Substances 0.000 claims description 30

- 238000000992 sputter etching Methods 0.000 claims description 14

- 238000004140 cleaning Methods 0.000 claims description 6

- 238000005406 washing Methods 0.000 claims 1

- 229920002120 photoresistant polymer Polymers 0.000 description 48

- 239000007789 gas Substances 0.000 description 28

- 238000001020 plasma etching Methods 0.000 description 18

- 239000000758 substrate Substances 0.000 description 17

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 14

- 239000000460 chlorine Substances 0.000 description 14

- 238000000605 extraction Methods 0.000 description 12

- 150000002500 ions Chemical class 0.000 description 11

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 8

- 238000001878 scanning electron micrograph Methods 0.000 description 8

- 229910052786 argon Inorganic materials 0.000 description 7

- 229910052793 cadmium Inorganic materials 0.000 description 6

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 description 5

- 229910052801 chlorine Inorganic materials 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 230000005693 optoelectronics Effects 0.000 description 5

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 4

- 239000006096 absorbing agent Substances 0.000 description 4

- 238000001312 dry etching Methods 0.000 description 4

- 239000000203 mixture Substances 0.000 description 4

- 229910052757 nitrogen Inorganic materials 0.000 description 4

- 238000005424 photoluminescence Methods 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 239000006227 byproduct Substances 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 229910052734 helium Inorganic materials 0.000 description 3

- 238000009616 inductively coupled plasma Methods 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 238000012546 transfer Methods 0.000 description 3

- 238000003631 wet chemical etching Methods 0.000 description 3

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- BUGBHKTXTAQXES-UHFFFAOYSA-N Selenium Chemical compound [Se] BUGBHKTXTAQXES-UHFFFAOYSA-N 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- NINIDFKCEFEMDL-UHFFFAOYSA-N Sulfur Chemical compound [S] NINIDFKCEFEMDL-UHFFFAOYSA-N 0.000 description 2

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 230000000052 comparative effect Effects 0.000 description 2

- 239000012776 electronic material Substances 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 229910052711 selenium Inorganic materials 0.000 description 2

- 239000011669 selenium Substances 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 229910052717 sulfur Inorganic materials 0.000 description 2

- 239000011593 sulfur Substances 0.000 description 2

- 229910052714 tellurium Inorganic materials 0.000 description 2

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- 229910052724 xenon Inorganic materials 0.000 description 2

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 2

- 229910052725 zinc Inorganic materials 0.000 description 2

- 239000011701 zinc Substances 0.000 description 2

- VZSRBBMJRBPUNF-UHFFFAOYSA-N 2-(2,3-dihydro-1H-inden-2-ylamino)-N-[3-oxo-3-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)propyl]pyrimidine-5-carboxamide Chemical compound C1C(CC2=CC=CC=C12)NC1=NC=C(C=N1)C(=O)NCCC(N1CC2=C(CC1)NN=N2)=O VZSRBBMJRBPUNF-UHFFFAOYSA-N 0.000 description 1

- VXEGSRKPIUDPQT-UHFFFAOYSA-N 4-[4-(4-methoxyphenyl)piperazin-1-yl]aniline Chemical compound C1=CC(OC)=CC=C1N1CCN(C=2C=CC(N)=CC=2)CC1 VXEGSRKPIUDPQT-UHFFFAOYSA-N 0.000 description 1

- 229910000980 Aluminium gallium arsenide Inorganic materials 0.000 description 1

- 229910014265 BrCl Inorganic materials 0.000 description 1

- KZBUYRJDOAKODT-UHFFFAOYSA-N Chlorine Chemical compound ClCl KZBUYRJDOAKODT-UHFFFAOYSA-N 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- 229910000661 Mercury cadmium telluride Inorganic materials 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 229910007709 ZnTe Inorganic materials 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- CODNYICXDISAEA-UHFFFAOYSA-N bromine monochloride Chemical compound BrCl CODNYICXDISAEA-UHFFFAOYSA-N 0.000 description 1

- -1 cadmium halides Chemical class 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000007795 chemical reaction product Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 238000002508 contact lithography Methods 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 238000001918 dark-field optical micrograph Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000000593 degrading effect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 238000000025 interference lithography Methods 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000001451 molecular beam epitaxy Methods 0.000 description 1

- 239000002086 nanomaterial Substances 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 239000000047 product Substances 0.000 description 1

- 238000005086 pumping Methods 0.000 description 1

- 239000000376 reactant Substances 0.000 description 1

- SBIBMFFZSBJNJF-UHFFFAOYSA-N selenium;zinc Chemical compound [Se]=[Zn] SBIBMFFZSBJNJF-UHFFFAOYSA-N 0.000 description 1

- 239000005049 silicon tetrachloride Substances 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 231100000331 toxic Toxicity 0.000 description 1

- 230000002588 toxic effect Effects 0.000 description 1

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/3065—Plasma etching; Reactive-ion etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/02—Details

- H01L31/0236—Special surface textures

- H01L31/02363—Special surface textures of the semiconductor body itself, e.g. textured active layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/34—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies not provided for in groups H01L21/0405, H01L21/0445, H01L21/06, H01L21/16 and H01L21/18 with or without impurities, e.g. doping materials

- H01L21/46—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/428

- H01L21/461—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/428 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/465—Chemical or electrical treatment, e.g. electrolytic etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2933/00—Details relating to devices covered by the group H01L33/00 but not provided for in its subgroups

- H01L2933/0083—Periodic patterns for optical field-shaping in or on the semiconductor body or semiconductor body package, e.g. photonic bandgap structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0095—Post-treatment of devices, e.g. annealing, recrystallisation or short-circuit elimination

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/20—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a particular shape, e.g. curved or truncated substrate

- H01L33/22—Roughened surfaces, e.g. at the interface between epitaxial layers

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

Description

「抽出素子」は、発光ダイオードのような自己放出型光源からの光の抽出を高める任意のタイプ及び配置のナノ/微小構造物を指す。

「非反応性ガス」は、物理的スパッタリングによって基板をエッチングするために使用可能なガスを指す。スパッタエッチングは、運動エネルギー移動によって表面の原子をはじき出すか又は追い出すことが可能な、表面のエネルギー種による物理的衝突によって主に生じる。それらの活性な種は基板とは実質的に反応せず、放出される材料は一般的には不揮発性である。

「反応性イオンエッチング」は、プラズマ放電の中で反応性のガスをイオン化させかつそのガスを基板に向けて加速させ、基板において反応性の種が基板と化学反応して揮発性の種を形成することができるプロセスを指す。

「スパッタエッチング」は、イオンを基板に衝突させ、イオンから基板上の材料への運動量移動によって基板から材料を除去することを指す。これは、そのエッチングガス中の種が運動量移動によって基板材料を物理的に除去することにおいて、反応性イオンエッチングと区別される。

ネガ型フォトレジスト(ニュージャージー州FranklinのFuturrexより入手可能なNR1−1000P)及び従来のコンタクトリソグラフィを用いて、上述のようにフォトレジスト稜線パターンをII〜VI型半導体構造物上に作製した。次いで、下記実施例で説明するようなエッチング用に試料を小片に切断した。エッチングは市販の反応性イオンシステム(英国YattonのOxford Instrumentsより入手可能なRIE、Model PLASMA LAB System 100)で行った。

ニュージャージー州FranklinのFuterrexから入手可能なNR9−1000Pネガ型フォトレジストを用い、縞パターンのあるフォトレジストマスクを用いて上記II〜VI型半導体色変換体の試料をオーバーコートした。縞パターンの寸法は2μm及び100μmであった。II〜VI型半導体の小さく切断された試料の上にフォトレジストマスクを載せたものをSiキャリアウェハ上に置き、RIEチャンバーに入れ、5〜50sccmのAr、20〜200ワットの無線周波数(RF)電力、700〜2000ワットの誘導結合プラズマ電力(ICP)を用い、4〜30mTorr(0.5〜4.0Pa)の圧力で、60秒間隔で5回エッチングした。2μmと小さい幅を有するピクセル縞は、処理後数ヶ月間にかけて強いフォトルミネセンスを呈し続けた。エッチング時間を30秒間隔で6回にした(その間隔に基板を冷却させるために)ことを除き比較実施例1と同一の条件でCl2によりエッチングした同じ試料は、1日後に急激なフォトルミネセンスの劣化を示した。図3は、アルゴンスパッタエッチングプロセスを用いてエッチングした半導体の顕微鏡写真である。得られたエッチングプロファイルは約63度の側壁角を有していた。フォトレジストに対するこの半導体のエッチング速度の比率は約6〜約12の範囲で変化し、RF電力を変えることによって制御可能であった。RF電力を下げるとその比率は増加するが、エッチングの速度は低下した。II〜VI型半導体色変換体のエッチング速度は300nm/分〜500nm/分の範囲であった。

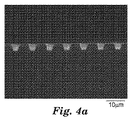

ニュージャージー州FranklinのFuturrexから入手可能なNR9−3000PYネガ型フォトレジストを用い、光リソグラフィによって、表1に上述したようにII〜VI型半導体色変換体構造物上にパターン化フォトレジストを作製し、実施例1の手順を用いてエッチングした。図4aは、得られた構造物の走査電子顕微鏡写真であり、横断寸法約6μmに稜線を残して作られた幅3μmの溝のパターンを示す。図4bは、半導体稜線のフォトルミネセンスを示す暗視野光学顕微鏡写真である。半導体色変換体が損なわれないまま残された(エッチングの間、フォトレジストによって保護された)ところに一連の発光「ピクセル」が観察される。

表1に上述したようなII〜VI半導体色変換体構造物上にパターン化フォトレジストを下記のように作製した。レーザーダイオード光源に基づく干渉リソグラフィを用い、光抽出のための穴又は柱構造物を有する2次元格子パターンをTELR−P003PMフォトレジスト(マサチューセッツ州MarlboroughのShipleyより入手可能)に作製した。この格子は1μmピッチで400〜500nmの特徴部を有するものであった。パターン化フォトレジストコーティングされた半導体を、実施例1で説明したような条件でArエッチングした。図5aは、エッチング前の半導体上に直径400nmの柱構造物を有するフォトレジストパターンの走査電子顕微鏡写真である。図5bは図5aと同じ視点の、フォトレジストがなお置かれた状態でのArプラズマエッチング後の顕微鏡写真である。エッチングの後、残りのフォトレジストはピラミッド状構造物であり、フォトレジストの周囲の半導体はエッチングされて、レジストの下に円錐柱が残されている(残ったフォトレジストと半導体との間の境界は、図5bで円錐構造物の基底から頂点にかけて約3分の2のところに見られる)。更なるArエッチングにより、図5cに示される半導体のパターンが得られた。図5cに図示したエッチングされた試料のフォトルミネセンス測定値は50.4%の外部量子効率を示した。エッチングの前の平面試料のフォトルミネセンス測定値は29.7%の外部量子効率を示した。この例は、II〜VI半導体上の光抽出構造物が、放射される光の収率をいかに増すかを示すものである。

Claims (1)

- それ自体の上にエッチングマスクを有する半導体を真空チャンバー中に供給する工程と、

前記エッチングマスクを介して非反応性エッチングガスで前記半導体をスパッタエッチングして前記半導体の表面から材料を取り除き、少なくとも1つのエッチングされた表面を与える工程と、

前記真空チャンバーから、少なくとも1つのエッチングされた表面を有する前記半導体を取り出す工程と、

前記真空チャンバーを洗浄する工程と、

前記真空チャンバーを洗浄後、少なくとも1つのエッチングされた表面を有する前記半導体を前記真空チャンバーに戻す工程と、

前記エッチングマスクを介して非反応性エッチングガスで前記半導体を更にスパッタエッチングする工程と、

を含み、

前記半導体がIII〜V型半導体、II〜VI型半導体、又はそれらの組合わせを含み、

前記真空チャンバーを洗浄する工程が、反応性ガスを前記真空チャンバーに導入する工程と、前記反応性ガスでプラズマを形成し前記真空チャンバーの内部の堆積物を揮発させる工程と、を含む、半導体のエッチング方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US25929909P | 2009-11-09 | 2009-11-09 | |

| US61/259,299 | 2009-11-09 | ||

| PCT/US2010/055096 WO2011056783A2 (en) | 2009-11-09 | 2010-11-02 | Etching process for semiconductors |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013510442A JP2013510442A (ja) | 2013-03-21 |

| JP2013510442A5 JP2013510442A5 (ja) | 2013-08-29 |

| JP5723377B2 true JP5723377B2 (ja) | 2015-05-27 |

Family

ID=43970710

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012537938A Expired - Fee Related JP5723377B2 (ja) | 2009-11-09 | 2010-11-02 | 半導体のためのエッチングプロセス |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US8765611B2 (ja) |

| EP (1) | EP2499663A2 (ja) |

| JP (1) | JP5723377B2 (ja) |

| KR (1) | KR20120095411A (ja) |

| CN (1) | CN102893378A (ja) |

| TW (1) | TW201135832A (ja) |

| WO (1) | WO2011056783A2 (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5710433B2 (ja) * | 2011-09-13 | 2015-04-30 | 株式会社東芝 | 成膜装置のクリーニング方法および成膜装置 |

| FR2984769B1 (fr) * | 2011-12-22 | 2014-03-07 | Total Sa | Procede de texturation de la surface d'un substrat de silicium, substrat structure et dispositif photovoltaique comportant un tel substrat structure |

| US8883028B2 (en) | 2011-12-28 | 2014-11-11 | Lam Research Corporation | Mixed mode pulsing etching in plasma processing systems |

| EP2922103B1 (en) | 2012-08-21 | 2017-04-05 | Oji Holdings Corporation | Substrate for semiconductor light emitting elements and semiconductor light emitting element |

| WO2014051909A1 (en) * | 2012-09-25 | 2014-04-03 | Applied Materials, Inc. | Chamber clean with in gas heating source |

| CN103901516B (zh) * | 2012-12-26 | 2016-06-15 | 清华大学 | 光栅的制备方法 |

| US8941145B2 (en) * | 2013-06-17 | 2015-01-27 | The Boeing Company | Systems and methods for dry etching a photodetector array |

| US9012305B1 (en) * | 2014-01-29 | 2015-04-21 | Applied Materials, Inc. | Wafer dicing using hybrid laser scribing and plasma etch approach with intermediate non-reactive post mask-opening clean |

| JP6871706B2 (ja) | 2016-09-30 | 2021-05-12 | 日機装株式会社 | 半導体発光素子の製造方法 |

| JPWO2021095608A1 (ja) * | 2019-11-12 | 2021-05-20 | ||

| CN113823992B (zh) * | 2021-09-14 | 2022-11-11 | 苏州长瑞光电有限公司 | 半导体器件制造方法及半导体器件 |

| CN115343788B (zh) * | 2022-08-18 | 2024-03-15 | 上海交通大学 | 基于循环刻蚀工艺的石英微透镜制备方法及石英微透镜 |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0294522A (ja) * | 1988-09-30 | 1990-04-05 | Toshiba Corp | ドライエッチング方法 |

| US5404027A (en) * | 1991-05-15 | 1995-04-04 | Minnesota Mining & Manufacturing Compay | Buried ridge II-VI laser diode |

| DE69320963T2 (de) * | 1992-06-22 | 1999-05-12 | Lam Res Corp | Plasmareinigungsverfahren zum entfernen von rückständen in einer plasmabehandlungskammer |

| DE4241045C1 (de) * | 1992-12-05 | 1994-05-26 | Bosch Gmbh Robert | Verfahren zum anisotropen Ätzen von Silicium |

| JPH07335620A (ja) * | 1994-06-09 | 1995-12-22 | Sony Corp | Ii−vi族化合物半導体の選択的ドライエッチング方法 |

| EP0774772A1 (en) | 1995-11-17 | 1997-05-21 | Applied Materials, Inc. | Methods for physically etching silicon electrically conducting surfaces |

| DE19736370C2 (de) * | 1997-08-21 | 2001-12-06 | Bosch Gmbh Robert | Verfahren zum anisotropen Ätzen von Silizium |

| KR100269323B1 (ko) * | 1998-01-16 | 2000-10-16 | 윤종용 | 반도체장치의백금막식각방법 |

| IT1301840B1 (it) * | 1998-06-30 | 2000-07-07 | Stmicroelettronica S R L | Metodo per incrementare la seletttvita' tra un film di materialefotosensibile ed uno strato da sottoporre ed incisione in processi |

| DE19919832A1 (de) * | 1999-04-30 | 2000-11-09 | Bosch Gmbh Robert | Verfahren zum anisotropen Plasmaätzen von Halbleitern |

| SE9903213D0 (sv) * | 1999-06-21 | 1999-09-10 | Carl Fredrik Carlstroem | Dry etching process of compound semiconductor materials |

| US6352081B1 (en) * | 1999-07-09 | 2002-03-05 | Applied Materials, Inc. | Method of cleaning a semiconductor device processing chamber after a copper etch process |

| US6347874B1 (en) * | 2000-02-16 | 2002-02-19 | 3M Innovative Properties Company | Wedge light extractor with risers |

| JP3776824B2 (ja) * | 2002-04-05 | 2006-05-17 | 株式会社東芝 | 半導体発光素子およびその製造方法 |

| DE10247913A1 (de) * | 2002-10-14 | 2004-04-22 | Robert Bosch Gmbh | Plasmaanlage und Verfahren zum anisotropen Einätzen von Strukturen in ein Substrat |

| US7238970B2 (en) * | 2003-10-30 | 2007-07-03 | Matsushita Electric Industrial Co., Ltd. | Semiconductor device and method for fabricating the same |

| JP2005353972A (ja) | 2004-06-14 | 2005-12-22 | Canon Inc | プラズマ処理方法 |

| US7402831B2 (en) * | 2004-12-09 | 2008-07-22 | 3M Innovative Properties Company | Adapting short-wavelength LED's for polychromatic, broadband, or “white” emission |

| US7575007B2 (en) * | 2006-08-23 | 2009-08-18 | Applied Materials, Inc. | Chamber recovery after opening barrier over copper |

| WO2008083188A2 (en) | 2006-12-29 | 2008-07-10 | 3M Innovative Properties Company | Led light source with converging extractor in an optical element |

| US8179034B2 (en) * | 2007-07-13 | 2012-05-15 | 3M Innovative Properties Company | Light extraction film for organic light emitting diode display and lighting devices |

| CN101472455A (zh) | 2007-12-29 | 2009-07-01 | 3M创新有限公司 | 电磁屏蔽衬垫和用于填充电磁屏蔽系统中的间隙的方法 |

| CN102473817A (zh) * | 2009-06-30 | 2012-05-23 | 3M创新有限公司 | 无镉再发光半导体构造 |

-

2010

- 2010-11-02 JP JP2012537938A patent/JP5723377B2/ja not_active Expired - Fee Related

- 2010-11-02 US US12/917,826 patent/US8765611B2/en not_active Expired - Fee Related

- 2010-11-02 KR KR1020127014823A patent/KR20120095411A/ko not_active Application Discontinuation

- 2010-11-02 WO PCT/US2010/055096 patent/WO2011056783A2/en active Application Filing

- 2010-11-02 EP EP10828972A patent/EP2499663A2/en not_active Withdrawn

- 2010-11-02 CN CN2010800506808A patent/CN102893378A/zh active Pending

- 2010-11-08 TW TW099138381A patent/TW201135832A/zh unknown

Also Published As

| Publication number | Publication date |

|---|---|

| CN102893378A (zh) | 2013-01-23 |

| KR20120095411A (ko) | 2012-08-28 |

| TW201135832A (en) | 2011-10-16 |

| US20110108956A1 (en) | 2011-05-12 |

| US8765611B2 (en) | 2014-07-01 |

| WO2011056783A3 (en) | 2011-07-28 |

| WO2011056783A2 (en) | 2011-05-12 |

| EP2499663A2 (en) | 2012-09-19 |

| JP2013510442A (ja) | 2013-03-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5723377B2 (ja) | 半導体のためのエッチングプロセス | |

| EP3026716B1 (en) | Semiconductor light emitting element and method for manufacturing same | |

| CN102598223B (zh) | 用于半导体的各向异性蚀刻的工艺 | |

| KR20060051165A (ko) | 반도체 발광 장치 및 그것의 제조 방법 | |

| WO2005004247A1 (en) | Iii-nitride compound semiconductor light emitting device | |

| Park et al. | Enhancement of photo-and electro-luminescence of GaN-based LED structure grown on a nanometer-scaled patterned sapphire substrate | |

| US20130140593A1 (en) | Light emitting diode | |

| Carlström et al. | Cl 2∕ O 2-inductively coupled plasma etching of deep hole-type photonic crystals in InP | |

| US20130089939A1 (en) | Method for making light emitting diode | |

| US8796716B2 (en) | Light emitting diode | |

| US9029889B2 (en) | Light emitting diode | |

| US9041030B2 (en) | Light emitting diode | |

| KR20180061093A (ko) | 나노패턴의 형성방법, 발광소자의 제조방법 및 그에 의해 제조된 발광소자 | |

| KR20180060585A (ko) | 나노패턴의 형성방법, 발광소자의 제조방법 및 그에 의해 제조된 발광소자 | |

| US8790940B2 (en) | Method for making light emitting diode | |

| JP6548024B2 (ja) | 凹凸構造を含む基板の製造方法及び半導体発光素子の製造方法 | |

| JP5499920B2 (ja) | 半導体光デバイスの製造方法 | |

| US20120032306A1 (en) | Method for Patterning a Semiconductor Surface, and Semiconductor Chip | |

| Byeon et al. | Enhancement of the photon extraction of green and blue LEDs by patterning the indium tin oxide top layer | |

| KR101586441B1 (ko) | 광전자소자용 팔라듐 금속층의 식각 방법 | |

| KR100780832B1 (ko) | 산화아연 물질에 대한 건식 식각 방법 | |

| CN115903383A (zh) | 一种用于在蓝宝石衬底上形成亚微米图案的双光刻胶互补光刻的方法 | |

| Lee et al. | Emission Enhancement of InGaN/GaN Light Emitting Diode by Using Ag Nanoparticles | |

| Pearton | Dry Etching of Semiconductors at the Nano-and Micro-Scale | |

| Forchel et al. | InP/InGaAs nanofabrication and optical characterization |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130712 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130712 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140428 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140520 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140815 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150303 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150327 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5723377 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |