以下、図面を参照して、本発明を適用した実施の形態について説明する。

〈本発明の概要〉

本発明を適用した固体撮像素子は、複数の単位画素を有しており、各単位画素には、フォトダイオード、転送ゲート、リセットトランジスタ、および浮遊拡散領域が少なくとも設けられている。また、固体撮像素子では、フォトダイオードで光を受光して得られた電荷が、転送ゲートを介して、電荷電圧変換部としての浮遊拡散領域に転送されて電圧に変換され、その電圧が相関二重サンプリングにより読み出される。

具体的には、図4に示すように、固体撮像素子の単位画素では、単位画素内の所定の素子に、その素子を駆動するための画素駆動信号が供給され、リセットトランジスタには、適宜、浮遊拡散領域をリセットするための電圧(リセットパルス)が供給される。なお、図中、横方向は時間を示しており、C11およびC12は、それぞれ画素駆動信号の波形とリセットパルスRSTの波形を示している。

固体撮像素子では、単位画素の露光期間において、一旦、リセットトランジスタにリセットパルスRST11が印加され、浮遊拡散領域がリセットされる。そして、フォトダイオードから浮遊拡散領域に電荷が転送されて電圧に変換され、期間RD31において、浮遊拡散領域の電圧が信号レベルとして読み出される。さらに、その後、リセットトランジスタにリセットパルスRST12が印加されて、浮遊拡散領域がリセットされ、期間RD32において、リセット後の浮遊拡散領域の電圧がリセットレベルとして読み出される。

このとき、固体撮像素子は、浮遊拡散領域と、他の信号線や素子等の部位との間のカップリングに影響を与える画素駆動信号の状態を制御することにより、浮遊拡散領域と他の部位とのカップリングにより生じるカップリングノイズを低減させる。例えば、画素駆動信号は、選択トランジスタに印加される選択パルス、転送ゲートに印加される転送パルスなどとされる。

具体的には、画素駆動信号の波形C11における、リセットパルスRST11の印加時と同じ時刻の部分R1の状態と、波形C11における、リセットパルスRST12の印加時と同じ時刻の部分R2の状態とが同じとなるようにされる。

より詳細には、時刻t1と時刻t2における画素駆動信号の状態が同じ状態となるようにされる。ここで、時刻t1は、リセットトランジスタにリセットパルスRST11が印加されて、リセットパルスRSTが活性化された後、リセットパルスRSTが非活性化される時刻である。換言すれば、リセットパルスRSTの波形が立ち上がった後、立ち下がる瞬間の時刻である。

同様に、時刻t2は、リセットトランジスタにリセットパルスRST12が印加されて、リセットパルスRSTが活性化された後、リセットパルスRSTが非活性化される時刻、つまりリセットパルスRSTの波形が立ち上がった後、立ち下がる瞬間の時刻である。

なお、画素駆動信号の状態とは、例えば画素駆動信号のレベル(電圧)であり、時刻t1と時刻t2における画素駆動信号の電圧が等しくなるように、制御される。

さらに、時刻t1と時刻t2の画素駆動信号の状態に加えて、信号レベルが読み出される期間RD31における画素駆動信号の部分B1の状態と、リセットレベルが読み出される期間RD32における画素駆動信号の部分B2の状態とが同じとなるようにされる。

このように、信号レベル読み出し直前、つまりフォトダイオードから浮遊拡散領域への電荷の転送直前の浮遊拡散領域のリセット時と、リセットレベル読み出し直前の浮遊拡散領域のリセット時の画素駆動信号の状態が等しく、かつ信号レベル読み出し時とリセットレベル読み出し時の画素駆動信号の状態が等しくなるように制御される。これにより、信号レベル読み出し時に生じるカップリングノイズと、リセットレベル読み出し時に生じるカップリングノイズとを、ほぼ同じ大きさのノイズとすることができ、カップリングノイズによる画素信号への影響を低減させることができる。その結果、より正確な値の画素信号を得ることができる。

〈第1の実施の形態〉

[固体撮像素子の構成]

次に、本発明を適用した具体的な実施の形態について説明する。

図5は、本発明が適用される固体撮像素子としてのCMOS(Complementary Metal Oxide Semiconductor)イメージセンサの構成例を示すブロック図である。

CMOSイメージセンサ50は、画素アレイ部61、垂直駆動部62、カラム処理部63、水平駆動部64、およびシステム制御部65を含んで構成される。画素アレイ部61、垂直駆動部62、カラム処理部63、水平駆動部64、およびシステム制御部65は、図示せぬ半導体基板(チップ)上に形成されている。

画素アレイ部61には、入射光量に応じた電荷量の光電荷(以下、単に「電荷」と記述する場合もある)を発生して内部に蓄積する光電変換素子を有する単位画素(図6の単位画素90)が行列状に2次元配置されている。なお、以下では、入射光量に応じた電荷量の光電荷を、単に「電荷」と記述し、単位画素を、単に「画素」と記述する場合もある。

画素アレイ部61にはさらに、行列状の画素配列に対して行ごとに画素駆動線66が図の左右方向(画素行の画素の配列方向)に沿って形成され、列ごとに垂直信号線67が図の上下方向(画素列の画素の配列方向)に沿って形成されている。図5では、画素駆動線66について1本として示しているが、1本に限られるものではない。画素駆動線66の一端は、垂直駆動部62の各行に対応した出力端に接続されている。

CMOSイメージセンサ50はさらに、信号処理部68およびデータ格納部69を備えている。信号処理部68およびデータ格納部69については、CMOSイメージセンサ50とは別の基板に設けられる外部信号処理部、例えばDSP(Digital Signal Processor)やソフトウェアによる処理でも構わないし、CMOSイメージセンサ50と同じ基板上に搭載しても構わない。

垂直駆動部62は、シフトレジスタやアドレスデコーダなどによって構成され、画素アレイ部61の各画素を、全画素同時あるいは行単位等で駆動する画素駆動部である。この垂直駆動部62は、その具体的な構成については図示を省略するが、読出し走査系と、掃出し走査系あるいは、一括掃き出し、一括転送を有する構成となっている。

読出し走査系は、単位画素から信号を読み出すために、画素アレイ部61の単位画素を行単位で順に選択走査する。行駆動の場合、掃き出しについては、読出し走査系によって読出し走査が行われる読出し行に対して、その読出し走査よりもシャッタスピードの時間分だけ先行して掃出し走査が行なわれる。また、グローバル露光の場合は、一括転送よりもシャッタスピードの時間分先行して一括掃き出しが行なわれる。

この掃出しにより、読出し行の単位画素の光電変換素子から不要な電荷が掃き出される(リセットされる)。そして、不要電荷の掃き出し(リセット)により、いわゆる電子シャッタ動作が行われる。ここで、電子シャッタ動作とは、光電変換素子の光電荷を捨てて、新たに露光を開始する(光電荷の蓄積を開始する)動作のことを言う。

読出し走査系による読出し動作によって読み出される信号は、その直前の読出し動作または電子シャッタ動作以降に入射した光量に対応するものである。行駆動の場合は、直前の読出し動作による読出しタイミングまたは電子シャッタ動作による掃出しタイミングから、今回の読出し動作による読出しタイミングまでの期間が、単位画素における光電荷の蓄積時間(露光時間)となる。グローバル露光の場合は、一括掃き出しから一括転送までの時間が蓄積時間(露光時間)となる。

垂直駆動部62によって選択走査された画素行の各単位画素から出力される画素信号は、垂直信号線67の各々を通してカラム処理部63に供給される。カラム処理部63は、画素アレイ部61の画素列ごとに、選択行の各単位画素から垂直信号線67を通して出力される画素信号に対して所定の信号処理を行うとともに、信号処理後の画素信号を一時的に保持する。

具体的には、カラム処理部63は、信号処理として少なくとも、ノイズ除去処理、例えばCDS(Correlated Double Sampling;相関二重サンプリング)処理を行う。このカラム処理部63による相関二重サンプリングにより、リセットノイズや増幅トランジスタの閾値ばらつき等の画素固有の固定パターンノイズが除去される。カラム処理部63にノイズ除去処理以外に、例えば、AD(アナログ−デジタル)変換機能を持たせ、信号レベルをデジタル信号で出力することも可能である。

水平駆動部64は、シフトレジスタやアドレスデコーダなどによって構成され、カラム処理部63の画素列に対応する単位回路を順番に選択する。この水平駆動部64による選択走査により、カラム処理部63で信号処理された画素信号が順番に信号処理部68に出力される。

システム制御部65は、各種のタイミング信号を生成するタイミングジェネレータ等によって構成され、タイミングジェネレータで生成された各種のタイミング信号を基に垂直駆動部62、カラム処理部63および水平駆動部64などの駆動制御を行う。

信号処理部68は、少なくとも加算処理機能を有し、カラム処理部63から出力される画素信号に対して加算処理等の種々の信号処理を行う。データ格納部69は、信号処理部68での信号処理に当たって、その処理に必要なデータを一時的に格納する。

[単位画素の構造]

次に、図5の画素アレイ部61に行列状に配置されている単位画素の具体的な構造について説明する。単位画素は、光電変換素子から転送される光電荷を保持(蓄積)する浮遊拡散領域(容量)を有している。

図6は、単位画素の構成を示す図である。

単位画素90は、光電変換素子として例えばフォトダイオード(PD)121を有している。フォトダイオード121は、例えば、N型基板131上に形成されたP型ウェル層132に対して、P型層133を基板表面側に形成してN型埋め込み層134を埋め込むことによって形成される埋め込み型フォトダイオードである。

単位画素90は、フォトダイオード121に加えて、転送ゲート122および浮遊拡散領域(FD:Floating Diffusion)123を有する。なお、浮遊拡散領域123は遮光されている。

転送ゲート122は、フォトダイオード121で光電変換され、その内部に蓄積された電荷を、ゲート電極122Aに転送パルスTRGが印加されることによって転送する。浮遊拡散領域123は、N型層からなる電荷電圧変換部であり、転送ゲート122によってフォトダイオード121から転送された電荷を電圧に変換する。

単位画素90はさらに、リセットトランジスタ124、増幅トランジスタ125および選択トランジスタ126を有している。リセットトランジスタ124、増幅トランジスタ125および選択トランジスタ126は、図6の例では、NチャネルのMOSトランジスタを用いている。しかし、図6で例示したリセットトランジスタ124、増幅トランジスタ125および選択トランジスタ126の導電型の組み合わせは一例に過ぎず、これらの組み合わせに限られるものではない。

リセットトランジスタ124は、電源VDBと浮遊拡散領域123との間に接続されており、ゲート電極にリセットパルスRSTが印加されることによって浮遊拡散領域123をリセットする。増幅トランジスタ125は、ドレイン電極が電源VDOに接続され、ゲート電極が浮遊拡散領域123に接続されており、浮遊拡散領域123の電圧を読み出す。

選択トランジスタ126は、例えば、ドレイン電極が増幅トランジスタ125のソース電極に、ソース電極が垂直信号線67にそれぞれ接続されており、ゲート電極に選択パルスSELが印加されることで、画素信号を読み出すべき単位画素90を選択する。なお、選択トランジスタ126については、電源VDOと増幅トランジスタ125のドレイン電極との間に接続した構成を採ることも可能である。

なお、リセットトランジスタ124、増幅トランジスタ125および選択トランジスタ126については、その一つあるいは複数を画素信号の読み出し方法によって省略したり、複数の画素間で共有したりすることも可能である。

このようにして構成されるCMOSイメージセンサ50は、全画素同時に露光を開始し、全画素同時に露光を終了し、フォトダイオード121に蓄積された電荷を、遮光された浮遊拡散領域123へ転送することで、グローバル露光を実現する。このグローバル露光により、全画素一致した露光期間による歪みのない撮像が可能となる。

なお、本実施の形態での全画素とは、画像に現れる部分の画素の全てということであり、ダミー画素などは除外される。また、時間差や画像の歪みが問題にならない程度に十分小さければ、全画素同時の動作の代わりに複数行(例えば、数十行)ずつに高速に走査するものも含まれる。

ここで、単位画素90におけるグローバル露光動作について説明する。

まず、全画素同時に埋め込みフォトダイオード121の蓄積電荷を空にする電荷排出動作が実行された後、露光が開始される。すなわち、ゲート電極122Aに転送パルスTRGが印加されるとともに、リセットトランジスタ124のゲート電極にリセットパルスRSTが印加され、フォトダイオード121および浮遊拡散領域123がリセットされ、露光が開始される。

これにより、フォトダイオード121のPN接合容量に光電荷が蓄積される。露光期間終了時点で、全画素同時に、転送ゲート122がオンされ、フォトダイオード121で蓄積された光電荷が全て浮遊拡散領域123へと転送される。転送ゲート122を閉じることで、全画素同一の露光期間で蓄積された光電荷が浮遊拡散領域123で保持される。

その後、浮遊拡散領域123で保持された光電荷(電圧)が、信号レベルとして垂直信号線67を通してカラム処理部63に読み出される。そして、浮遊拡散領域123がリセットされ、しかる後、リセットレベルが垂直信号線67を通してカラム処理部63に読み出される。このような信号レベルの読み出しと、リセットレベルの読み出しとが、順次、各行について行われる。

なお、以下、ゲート電極122A、リセットトランジスタ124のゲート電極、および選択トランジスタ126のゲート電極に、転送パルスTRG、リセットパルスRST、および選択パルスSELが印加された状態とすることを、各パルスをオンするまたは活性化するとも称する。また、ゲート電極122A、リセットトランジスタ124のゲート電極、および選択トランジスタ126のゲート電極に、転送パルスTRG、リセットパルスRST、および選択パルスSELが印加されていない状態とすることを、各パルスをオフするまたは非活性化するとも称する。

[カップリングノイズの低減について]

ところで、CMOSイメージセンサ50では、図4を参照して説明したように、垂直駆動部62が、各単位画素90を駆動する画素駆動信号を適切に制御することで、単位画素から読み出される画素信号に含まれるカップリングノイズを低減させる。

以下では、画素駆動信号が、画素駆動線66を介して選択トランジスタ126のゲート電極に供給される選択パルスSELである場合を例として説明する。

そのような場合、例えば、図7に示すように、垂直駆動部62は、浮遊拡散領域123のリセット直後における選択パルスSELの状態が等しくなり、かつ信号レベルおよびリセットレベルの読み出しの期間における選択パルスSELの状態が等しくなるようにする。

なお、図7において、横方向は時間を示しており、図4における場合と対応する部分には、同一の符号を付してある。また、図7中、SEL、RST、FD、およびVoutは、選択パルスSELの電圧、リセットパルスRSTの電圧、浮遊拡散領域123の電圧、および垂直信号線67の電圧を示している。また、図7では、説明を分かり易くするため、信号電荷は暗時信号とされている。すなわち、実質的にフォトダイオード121から浮遊拡散領域123への電荷の転送は行なわれないものとする。

図7では、選択パルスSELがオフ(非活性)である状態、つまり選択パルスSELの波形が下に凸である状態では、浮遊拡散領域123からの電圧(電荷)の読み出しは行なわれず、垂直信号線67の電圧Voutは0Vとされている。

このような状態で、全単位画素90での同時露光期間中に、リセットパルスRSTとして、リセットパルスRST11がリセットトランジスタ124のゲート電極に印加されると、浮遊拡散領域123はリセットされ、浮遊拡散領域123の電圧FDは立ち上がる。ここで、選択パルスSELの状態は、リセットパルスRST11の印加直後の時刻t1においてもオフ、つまりローのままである。

その後、単位画素90での露光が終了し、選択パルスSELがオンされると、選択パルスSELの波形は立ち上がり、垂直信号線67の電圧Voutは0VからVsig0まで遷移しようとする。

浮遊拡散領域123は増幅トランジスタ125のゲート電極に接続され、垂直信号線67は増幅トランジスタ125のソースに接続されている。そのため、電圧Voutが0VからVsig0に遷移すると、カップリングフィードスルーにより、浮遊拡散領域123の電圧は変調を受け、Vfd1へと変化する。すると、垂直信号線67の電圧VoutはVsig0から、浮遊拡散領域123の電圧FD=Vfd1により定まる電圧Vsigに遷移し、期間RD31に電圧Vout=Vsigが信号レベルとしてカラム処理部63に読み出される。

一方、信号レベル読み出し後、垂直駆動部62は、選択パルスSELを一時的にオフ(非活性化)させる。これにより、垂直信号線67の電圧VoutはVsigから0Vに遷移し、浮遊拡散領域123の電圧FDもVfd1から立ち下がる。

その後、垂直駆動部62は、選択パルスSELをオフした状態のままで、リセットパルスRSTとして、リセットパルスRST12をリセットトランジスタ124のゲート電極に印加する。つまり、リセットパルスRSTがオン(活性化)される。これにより、浮遊拡散領域123がリセットされ、浮遊拡散領域123の電圧FDは立ち上がる。

なお、このとき、選択パルスSELはオフのままであるので、垂直信号線67の電圧はVout=0Vのままである。また、選択パルスSELの状態は、リセットパルスRST12の印加直後の時刻t2においてもオフ、つまりローのままである。

そして、リセットレベルの読み出しのため、再び垂直駆動部62が選択パルスSELをオンすると、選択パルスSELの波形は立ち上がり、垂直信号線67の電圧Voutは0VからVrst0まで遷移しようとする。

この場合においても、信号レベルの読み出し時と同様に、電圧Voutが0VからVrst0に遷移すると、カップリングフィードスルーにより、浮遊拡散領域123の電圧は変調を受け、Vfd2へと変化する。すると、垂直信号線67の電圧VoutはVrst0から、浮遊拡散領域123の電圧FD=Vfd2により定まる電圧Vrstに遷移し、期間RD32に電圧Vout=Vrstがリセットレベルとしてカラム処理部63に読み出される。

CMOSイメージセンサ50では、このようにして各単位画素90から信号レベルとリセットレベルが読み出される。このとき、CMOSイメージセンサ50では、選択パルスSELを適切に制御することにより、信号レベルとリセットレベルの読み出しの直前に選択パルスSELが活性化されたとき、ほぼ同じ条件下で垂直信号線67の電圧Voutの遷移を発生させることができる。

図7の例では、信号レベルの読み出しの直前における選択パルスSELの活性化では、垂直信号線67の電圧Voutは0VからVsig0まで遷移し、リセットレベルの読み出し直前における選択パルスSELの活性化では、電圧Voutは0VからVrst0まで遷移する。

ここで、電圧Vsig0とVrst0は同じ値であるから、信号レベルの読み出し時と、リセットレベルの読み出し時とで、浮遊拡散領域123が受けるカップリングは等しくなり、同じ大きさのカップリングノイズが、信号レベルとリセットレベルとに含まれることになる。その結果、信号レベルとして読み出される電圧Vout=Vsigと、リセットレベルとして読み出される電圧Vout=Vrstが等しくなり、それらの信号の差、つまり画素信号に含まれることになるカップリングノイズ△Vcup=0Vとなる。すなわち、画素信号を得るために、信号レベルとリセットレベルとの差分を求めると、これらの信号レベルとリセットレベルに含まれているカップリングノイズが相殺され、より正確な値の画素信号が得られる。

このように、CMOSイメージセンサ50によれば、各リセットパルスRSTの活性化時の選択パルスSELの状態を同じとし、かつ浮遊拡散領域123からの電圧の読み出し期間の選択パルスSELの状態を同じとすることで、よりカップリングノイズによる影響を低減させることができる。

[撮像処理の説明]

次に、図8のフローチャートを参照して、CMOSイメージセンサ50がユーザの操作等に応じて、画像を撮像する処理である撮像処理について説明する。

ステップS11において、垂直駆動部62は、電子シャッタ動作を行い、全単位画素90に同時に露光を開始させる。すなわち、垂直駆動部62は、全ての単位画素90に対して、リセットトランジスタ124のゲート電極にリセットパルスRSTを印加するとともに、転送ゲート122のゲート電極122Aに転送パルスTRGを印加する。

これにより、これまでフォトダイオード121に蓄積されていた電荷が掃き出され、電子シャッタ動作後に新たに受光した、被写体からの光から得られた電荷がフォトダイオード121に蓄積されることになる。

また、このとき、垂直駆動部62は、全ての単位画素90の選択トランジスタ126のゲート電極に供給される選択パルスSELをオフとする。

ステップS12において、垂直駆動部62は、全ての単位画素90の浮遊拡散領域123を、同時にリセットする。すなわち、全ての単位画素90のリセットトランジスタ124に供給するリセットパルスRSTをオンし、浮遊拡散領域123に蓄積されている電荷を排出させる。

ステップS13において、垂直駆動部62は、全ての単位画素90について、転送ゲート122のゲート電極122Aに供給する転送パルスを同時にオンし、フォトダイオード121に蓄積された電荷を、浮遊拡散領域123に転送させる。浮遊拡散領域123は、フォトダイオード121から転送されてきた電荷を電圧に変換し、保持する。

ステップS14において、垂直駆動部62は、複数の単位画素90からなる各行のうちの1つを処理対象行として、処理対象行を構成する単位画素90について、選択トランジスタ126のゲート電極に供給する選択パルスSELをオンする。これにより、浮遊拡散領域123の電圧の読み出しが可能となる。

ステップS15において、カラム処理部63は、処理対象行の各単位画素90について、垂直信号線67、選択トランジスタ126、および増幅トランジスタ125を介して、浮遊拡散領域123の電圧を信号レベルとして読み出す。

ステップS16において、垂直駆動部62は、処理対象行の各単位画素90について、選択トランジスタ126のゲート電極に供給する選択パルスSELをオフする。

ステップS17において、垂直駆動部62は、処理対象行の各単位画素90について、リセットトランジスタ124に供給するリセットパルスRSTをオンし、浮遊拡散領域123を所定電圧にリセットする。

ステップS18において、垂直駆動部62は、処理対象行の各単位画素90について、選択トランジスタ126のゲート電極に供給する選択パルスSELをオンする。そして、ステップS19において、カラム処理部63は、処理対象行の各単位画素90について、垂直信号線67、選択トランジスタ126、および増幅トランジスタ125を介して、浮遊拡散領域123の電圧をリセットレベルとして読み出す。

ステップS20において、垂直駆動部62は、処理対象行の各単位画素90について、選択トランジスタ126のゲート電極に供給する選択パルスSELをオフする。

さらに、ステップS21において、カラム処理部63は、処理対象行の各単位画素90について、読み出した信号レベルとリセットレベルとの差分を求めて画素信号を生成し、信号処理部68に出力する。このようにして出力された画素信号は、被写体の画像の各画素のデータとされる。

ステップS22において、CMOSイメージセンサ50は、画素アレイ部61を構成する全ての行を処理対象行として処理したか否かを判定する。ステップS22において、まだ全ての行を処理していないと判定された場合、処理はステップS14に戻り、上述した処理が繰り返される。すなわち、次の行が新たな処理対象行とされて、処理対象行の各単位画素90から画素信号が読み出される。

これに対してステップS22において、全ての行を処理したと判定された場合、撮像処理は終了する。

このようにして、CMOSイメージセンサ50は、全画素同時に電子シャッタ動作を行い、被写体の画像を撮像する。また、CMOSイメージセンサ50は、画像の読み出し時において、適切に画素駆動信号としての選択パルスSELを制御することで、画素信号に含まれるカップリングノイズを低減させる。

なお、以上においては、画素信号の読み出しが行ごとに行なわれると説明したが、画素ごと、または複数の画素ごとに行われるようにしてもよい。

〈変形例1〉

[カップリングノイズの低減について]

また、以上においては、選択パルスSELをオフとしたときの垂直信号線67のレベル(電圧)が0Vであると説明したが、浮遊拡散領域123のリセットレベルにより近い値Viniとしてもよい。

垂直信号線67に電圧Viniを印加しておくことで、選択パルスSELをオンとしたときの垂直信号線67の電圧Voutの遷移量をより小さくすることができ、カップリング電圧をより小さくすることができる。すなわち、カップリングノイズの大きさ自体を、より小さくすることができる。なお、垂直信号線67の電圧Viniの値は、内部発生または外部発生により最適な値に設定可能である。

このように、選択パルスSELがオフであるときの垂直信号線67の電圧をVout=Viniとする場合、垂直駆動部62は、図9に示すように、選択パルスSELおよびリセットパルスRSTの状態を制御する。

なお、図9において、横方向は時間を示しており、図中、SEL、RST、FD、およびVoutは、選択パルスSELの電圧、リセットパルスRSTの電圧、浮遊拡散領域123の電圧、および垂直信号線67の電圧を示している。また、図中、図7と対応する部分には、同一の符号を付してあり、その説明は省略する。さらに、図9では、説明を分かり易くするため、信号電荷は暗時信号とされている。

図9の例では、選択パルスSELの波形と、リセットパルスRSTの波形は、図7の選択パルスSELおよびリセットパルスRSTの波形と同じとなっている。すなわち、垂直駆動部62は、選択トランジスタ126およびリセットトランジスタ124に対して、図7を参照して説明した場合と全く同じ制御を行なう。

但し、図9の例では、選択パルスSELがオフであるときの垂直信号線67の電圧Vout=Viniが、0Vよりも大きい値とされている。そのため、選択パルスSELがオンされたときに生じる、垂直信号線67の電圧Vout=ViniからVsigへの遷移量と、電圧VoutのViniからVrstへの遷移量とがより小さくなり、その分だけカップリングノイズも小さくなる。したがって、画素信号に含まれるカップリングノイズの影響をさらに低減させることができる。なお、図9では、電圧VoutのViniからVsigへの遷移量と、ViniからVrstへの遷移量とは同じ大きさとなっている。

〈第2の実施の形態〉

[単位画素の構成]

なお、各単位画素90に、ブルーミング防止用のオーバーフローゲートが設けられるようにしてもよい。そのような場合、単位画素90は、例えば、図10に示すように構成される。なお、図10において、図6における場合と対応する部分には、同一の符号を付してあり、その説明は適宜省略する。

図10に示す単位画素90には、図6に示した単位画素90に加えて、さらにトランジスタなどからなるオーバーフローゲート161が設けられている。図10では、オーバーフローゲート161は、電源VDAとフォトダイオード121との間に接続されている。オーバーフローゲート161は、垂直駆動部62から画素駆動線66を介して、制御パルスABGが供給されると、フォトダイオード121をリセットする。すなわち、オーバーフローゲート161は、フォトダイオード121に蓄積されている電荷を排出する。

[オーバーフローゲートの動作の説明]

ところで、オーバーフローゲートは、フォトダイオードに蓄積された電荷が、浮遊拡散領域に漏れ込むことを防止するために設けられるので、通常、フォトダイオードから浮遊拡散領域に電荷が転送された後、画素信号の読み出しが完了するまで、継続して動作する。

特に、グローバル露光時においては、全単位画素において、同時に露光が行なわれ、フォトダイオードに蓄積された電荷が、浮遊拡散領域に転送されて蓄積される。浮遊拡散領域に蓄積された電荷は、信号レベルの読み出しまで保持されるが、グローバル露光では、行単位で順番に単位画素から画素信号が読み出されるため、読み出しの順番が遅い単位画素では、その分だけ長い時間、電荷が浮遊拡散領域に保持される。例えば、最終行では、約1フレーム分の期間だけ、浮遊拡散領域に電荷が保持されることになる。

そこで、浮遊拡散領域への電荷の転送後、浮遊拡散領域から信号レベルとリセットレベルが読み出されるまで、オーバーフローゲートに制御パルスが継続して印加され、フォトダイオードから浮遊拡散領域への電荷の漏れ(ブルーミング)が防止される。

なお、以下、オーバーフローゲートに制御パルスが印加される状態とすることを、制御パルスをオンする、または制御パルスのレベルをハイとするという。同様に、オーバーフローゲートに制御パルスが印加されない状態とすることを、制御パルスをオフする、または制御パルスのレベルをローとするという。

このように、オーバーフローゲートを設ければ、ブルーミングを防止することはできるが、浮遊拡散領域とオーバーフローゲートとの間に寄生容量がある場合、継続して制御パルスをオンさせると、信号レベルのみにカップリングノイズが含まれることになる。

すなわち、選択パルスのカップリングノイズと同様の理由で、信号レベルの読み出し時には、制御パルスがオフ(非活性)からオン(活性)とされることで、浮遊拡散領域がカップリングを受ける。これに対して、リセットレベルの読み出し時には、制御パルスはオンとされたままであるので、浮遊拡散領域はカップリングを受けない。したがって、信号レベルのみにカップリングノイズが含まれることになる。

このような浮遊拡散領域と、オーバーフローゲートの間の寄生容量により生じるカップリングノイズは、浮遊拡散領域とオーバーフローゲートの間にシールド用の配線を設ければ、低減させることができる。しかしながら、シールド用の配線を設けると、各単位画素の面積が増大することになる。そうすると、本来、浮遊拡散領域で電荷を保持する方式の固体撮像素子の利点であるはずの小型化が、実現できなくなってしまう。また、微細化、小画素化が進むと配線間の距離が短くなるため、信号(素子)間の寄生容量によるカップリングの影響は、より大きくなる。

さらに、カップリングノイズは、電源ゆれや画素のレイアウトに依存するため、画像上ではパターンノイズのように見え、かつ暗時でも発生するノイズであるため、暗時のシェーディングとして問題となる。しかも、カップリングノイズは、電源ゆれの影響を受けるため、2次元的なシェーディングとなることが多く、いわゆるOPB(Optical Black)などで除去することが困難である。

そこで、CMOSイメージセンサ50は、オーバーフローゲート161に供給される制御パルスABGを、図4で説明した画素駆動信号とし、この制御パルスABGの状態を制御することにより、画素信号に含まれるカップリングノイズを低減させる。

具体的には、例えば垂直駆動部62は、図11に示すように、各単位画素90のオーバーフローゲート161の動作を制御する。

なお、図11において、横方向は時間を示している。また、ABG(i−1)、RST(i−1)、およびFD(i−1)は、画素アレイ部61を構成する(i−1)行目の単位画素90に供給される制御パルスABGの電圧、リセットパルスRSTの電圧、および浮遊拡散領域123の電圧を示している。同様に、ABG(i)、RST(i)、およびFD(i)は、画素アレイ部61を構成するi行目の単位画素90に供給される制御パルスABGの電圧、リセットパルスRSTの電圧、および浮遊拡散領域123の電圧を示している。さらに、図11では、説明を分かり易くするため、信号電荷は暗時信号とされている。

CMOSイメージセンサ50では、全単位画素90で同時に電子シャッタ動作が行われた後、各単位画素90の浮遊拡散領域123が同時にリセットされる。すなわち、(i−1)行目の単位画素90では、リセットパルスRST21により浮遊拡散領域123がリセットされ、i行目の単位画素90では、リセットパルスRST22により浮遊拡散領域123がリセットされる。

このとき、全ての行の単位画素90のオーバーフローゲート161に供給される制御パルスABGはオフされている。例えば、制御パルスABGは、リセットパルスRST21およびリセットパルスRST22が立ち下がる時刻t21においても、オフとされている。

その後、露光期間が終了すると、全ての単位画素90において、同時にフォトダイオード121から浮遊拡散領域123への電荷の転送が行なわれる。そして、浮遊拡散領域123への電荷の転送が終了すると、時刻t22において、全ての単位画素90で、フォトダイオード121から浮遊拡散領域123への電荷の漏れを防止するために、制御パルスABGがオン(活性化)される。これにより、オーバーフローゲート161と浮遊拡散領域123とのカップリングが生じ、(i−1)行目およびi行目の浮遊拡散領域123の電圧FD(i−1)およびFD(i)は立ち上がり、Vfd1に遷移する。

さらに、その後、各行ごとに、画素信号の読み出しが開始される。このとき、各行の単位画素90において、制御パルスABGは、オン(活性化)されたままである。図11の例では、まず、(i−1)行目の単位画素90から画素信号が読み出され、次に、i行目の単位画素90から画素信号が読み出される。

すなわち、期間RD51において、カラム処理部63により、(i−1)行目の浮遊拡散領域123から信号レベルの読み出しが行なわれる。続いて、時刻t23において、(i−1)行目の単位画素90の制御パルスABGがオフされる。これにより、浮遊拡散領域123の電圧FD(i−1)は、立ち下がる。

また、その後、(i−1)行目のリセットパルスRSTがオンされると、すなわち、リセットトランジスタ124にリセットパルスRST23が印加されると、浮遊拡散領域123はリセットされ、浮遊拡散領域123の電圧FD(i−1)は、立ち上がる。ここで、リセットパルスRST23が立ち下がる時刻t24において、(i−1)行目の制御パルスABGは、オフされたままであり、時刻t24で電圧FD(i−1)は立ち下がる。

さらに、その後、(i−1)行目の制御パルスABGがオンされると、オーバーフローゲート161と浮遊拡散領域123とのカップリングが生じ、(i−1)行目の浮遊拡散領域123の電圧FD(i−1)は立ち上がり、Vfd2に遷移する。そして、期間RD52において、カラム処理部63により、(i−1)行目の浮遊拡散領域123からリセットレベルの読み出しが行なわれる。このとき、(i−1)行目の制御パルスABGはオンのままとされ、以後、継続してオンの状態が維持される。

このように、(i−1)行目の単位画素90では、時刻t21および時刻t24において、制御パルスABGはともにオフの状態とされる。そのため、信号レベルおよびリセットレベルの読み出しの前に制御パルスABGをオンすると、信号レベルの読み出し前と、リセットレベルの読み出し前とで、カップリング時の電圧FD(i−1)の遷移量が同じとなる。その結果、遷移後の電圧FD(i−1)もVfd1=Vfd2となり、同じとなる。これにより、信号レベルとリセットレベルに含まれるカップリングノイズが同じ大きさとなり、画素信号の生成時に相殺される。

(i−1)行目の単位画素90から画素信号が読み出されると、続いてi行目の単位画素90からの画素信号の読み出しが行なわれる。i行目の単位画素90では、時刻t22で制御パルスABGがオンされた後、画素信号の読み出しが開始されるまで、継続して制御パルスABGがオンされたままとされる。

まず、期間RD53において、i行目の制御パルスABGがオンされたままの状態で、カラム処理部63により、i行目の浮遊拡散領域123から信号レベルの読み出しが行なわれる。続いて、時刻t25において、i行目の単位画素90の制御パルスABGがオフされて、浮遊拡散領域123の電圧FD(i)は、立ち下がる。

また、i行目のリセットトランジスタ124にリセットパルスRST24が印加されると、浮遊拡散領域123はリセットされ、浮遊拡散領域123の電圧FD(i)は、立ち上がる。ここで、リセットパルスRST24が立ち下がる時刻t26において、i行目の制御パルスABGは、オフされたままである。

さらに、その後、i行目の制御パルスABGがオンされると、オーバーフローゲート161と浮遊拡散領域123とのカップリングが生じ、i行目の浮遊拡散領域123の電圧FD(i)は、Vfd2に遷移する。そして、期間RD54において、カラム処理部63により、i行目の浮遊拡散領域123からリセットレベルの読み出しが行なわれる。このとき、i行目の制御パルスABGはオンのままとされ、以後、継続してオンの状態が維持される。

このように、CMOSイメージセンサ50では、信号レベル読み出し直前の浮遊拡散領域123のリセット時、およびリセットレベル読み出し直前の浮遊拡散領域123のリセット時の制御パルスABGの状態が等しくなるようにされる。また、信号レベル読み出し時およびリセットレベル読み出し時の制御パルスABGの状態が等しくなるようにされる。

これにより、信号レベルとリセットレベルに含まれるカップリングノイズの大きさを、ほぼ同じ大きさとすることができ、カップリングノイズによる画素信号への影響を低減させることができる。

〈第3の実施の形態〉

[オーバーフローゲートの動作の説明]

なお、図11の例では、信号レベルとリセットレベルの読み出し時に、制御パルスABGがオンの状態であると説明したが、信号レベルとリセットレベルの読み出し時に、制御パルスABGがオフの状態とされるようにしもよい。

そのような場合、垂直駆動部62は、図12に示すように、各行の単位画素90の動作タイミングを制御する。

なお、図12において、横方向は時間を示しており、図12中、図11と対応する部分には、同じ符号を付してあり、その説明は適宜省略する。また、図12では、説明を分かり易くするため、信号電荷は暗時信号とされている。

図12では、全単位画素90で同時に電子シャッタ動作が行われた後、全単位画素90の浮遊拡散領域123が同時にリセットされる。このとき、リセットパルスRSTの活性化前後、特に時刻t21において、全行のオーバーフローゲート161の制御パルスABGがオフとされた状態とされる。

そして、浮遊拡散領域123への電荷の転送後、時刻t22において、各行のオーバーフローゲート161の制御パルスABGがオンされると、各行の浮遊拡散領域123は、オーバーフローゲート161とのカップリングを受ける。これにより、浮遊拡散領域123の電圧FD(i−1)およびFD(i)は立ち上がる。

さらに、行ごとの画素信号の読み出しが開始されると、全ての行のオーバーフローゲート161の制御パルスABGがオフされ、これにより浮遊拡散領域123の電圧FD(i−1)およびFD(i)は立ち下がって、Vfd1に遷移する。

その後、期間RD51において、カラム処理部63により、(i−1)行目の浮遊拡散領域123から信号レベルの読み出しが行なわれ、(i−1)行目のリセットトランジスタ124に、リセットパルスRST23が供給(印加)される。リセットパルスRST23の印加により、(i−1)行目の浮遊拡散領域123の電圧FD(i−1)は、一旦、立ち上がるが、時刻t24におけるリセットパルスRST23の立下りとともに、電圧FD(i−1)も立下り、Vfd2に遷移する。

さらに、期間RD52において、カラム処理部63により、(i−1)行目の浮遊拡散領域123からリセットレベルの読み出しが行なわれる。なお、信号レベルの読み出しの期間RD51の直前から、リセットレベルの読み出しの期間RD52の終了後まで、(i−1)行目の制御パルスABGは、継続してオフされたままの状態とされる。

このように、(i−1)行目の単位画素90では、時刻t21および時刻t24において、制御パルスABGはともにオフの状態であり、信号レベルおよびリセットレベルの読み出し時にも、制御パルスABGはオフの状態とされる。これにより、浮遊拡散領域123が、オーバーフローゲート161から受けるカップリングの影響を低減させ、その結果、画素信号に含まれるカップリングノイズを低減させることができる。

(i−1)行目の単位画素90からの画素信号の読み出しが行なわれると、その後、同様にして、i行目の単位画素90からの画素信号の読み出しが行なわれる。

すなわち、まず全ての行の制御パルスABGが同時にオンされた後、オフされる。このとき、(i−1)行目およびi行目の浮遊拡散領域123の電圧FD(i−1)および電圧FD(i)は、一旦、立ち上がってから、制御パルスABGのオフとともに立ち下がる。

そして、期間RD53で、i行目の浮遊拡散領域123から信号レベルが読み出され、リセットパルスRST24によりi行目の浮遊拡散領域123がリセットされた後、期間RD54で、i行目の浮遊拡散領域123からリセットレベルが読み出される。

このように、CMOSイメージセンサ50では、信号レベル読み出し直前の浮遊拡散領域123のリセット時、およびリセットレベル読み出し直前の浮遊拡散領域123のリセット時の制御パルスABGの状態がオフとなるようにされる。また、信号レベル読み出し時およびリセットレベル読み出し時の制御パルスABGの状態がオフとなるようにされる。

これにより、信号レベルとリセットレベルに含まれるカップリングノイズを低減させることができ、カップリングノイズによる画素信号への影響を低減させることができる。

図12の例では、図11の例よりも、浮遊拡散領域123のレベル(電圧)を低いレベルに保持することができるので、暗電流を低減できるという利点がある。しかしながら、図12の例では、制御パルスABGがオンの期間、つまりフォトダイオード121の電荷を排出する期間は、図11の例と比べて短くなるため、ブルーミング耐性は図11の例が、より優れている。

〈第4の実施の形態〉

[垂直駆動部の構成]

ところで、信号レベルを読み出してから、リセットレベルを読み出す信号先読みの相関二重サンプリングは、浮遊拡散領域を利用したグローバル露光機能を有する固体撮像素子で行なわれる。

このような固体撮像素子では、露光時の浮遊拡散領域のリセット(以下、露光中リセットと称する)は、全行活性で実施されるのに対し、リセットレベルの読み出しのための浮遊拡散領域のリセット(以下、読み出しリセットと称する)は、行活性で実施される。

そのため、露光中リセットでは全行活性により電源ゆれが大きいのに対して、読み出しリセットでは、電源ゆれは小さい。したがって、これらの電源ゆれの効果を考慮すると、浮遊拡散領域が、露光中リセット時に受けるカップリングと、読み出しリセット時に受けるカップリングは異なってくる。

そこで、画素信号に含まれるカップリングノイズを低減させる画素駆動信号の制御だけでなく、垂直駆動部62自体にも電源ゆれを小さくする工夫をすれば、カップリングノイズの画素信号への影響をさらに低減させることができる。

例えば、電源ゆれを小さくする垂直駆動部62の構成として、図13に示す構成が考えられる。すなわち、図13は、垂直駆動部62の構成例を示す図である。

図13に示す垂直駆動部62は、ドライバ191−1〜ドライバ191−Nを含むように構成され、これらのドライバ191−1〜ドライバ191−Nは、並列に接続されている。なお、以下、ドライバ191−1〜ドライバ191−Nのそれぞれを個々に区別する必要のない場合、単にドライバ191とも称する。

ドライバ191には電源VDDと電源VSSが接続されており、ドライバ191は、特定行を構成する各単位画素90に、画素駆動信号SIGn(但し、0≦n≦N−1)を供給する。ここで、電源VDDのレベル(電圧)が画素駆動信号SIGnのハイとされ、電源VSSのレベルが、ハイよりもレベルの低い、画素駆動信号SIGnのローとされる。垂直駆動部62には、このような各行に画素駆動信号を供給するドライバ191が、選択パルスSEL等の画素駆動信号の種別ごとに設けられている。

[ドライバの構成]

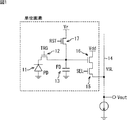

このようなドライバ191は、例えば、図14に示すように、P型のトランジスタ221と、N型のトランジスタ222とから構成される。

トランジスタ221とトランジスタ222のソースには、それぞれ電源VDDと電源VSSが接続されている。また、トランジスタ221のドレインと、トランジスタ222のドレインとが互いに接続されており、それらのトランジスタ221とトランジスタ222の間の電圧が、画素駆動信号SIGnとして単位画素90に供給される。例えば、画素駆動信号SIGnが選択パルスSELであれば、画素駆動信号SIGnは、ドライバ191から、選択トランジスタ126のゲート電極に印加される。

具体的には、トランジスタ221のゲートに供給される駆動信号XDRPが活性されると、すなわち駆動信号XDRPのレベルがローとされると、画素駆動信号SIGnのレベルはハイとなる。また、トランジスタ222のゲートに供給される駆動信号DRNが活性されると、すなわち駆動信号DRNのレベルがハイとされると、画素駆動信号SIGnのレベルはローとなる。

[ドライバの動作]

このような構成のドライバ191においては、駆動信号XDRPは、画素駆動信号SIGnをオン(ハイ)に駆動する信号であり、駆動信号DRNは、画素駆動信号SIGnをオフ(ロー)に駆動する信号である。ところが、これらの駆動信号XDRPと駆動信号DRNが同時に活性されると、電源VDDから電源VSSに貫通電流が流れる電源ゆれが大きくなってしまう。

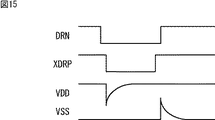

そこで、垂直駆動部62は、図15に示すように各ドライバ191を駆動し、貫通電流が流れることを抑制する。なお、図15において、横方向は時間を示しており、DRN、XDRP、VDD、およびVSSは、駆動信号DRN、駆動信号XDRP、電源VDD、および電源VSSの各電圧を示している。

また、駆動信号DRNおよび駆動信号XDRPの波形において、図中、上に凸の区間は、それらの駆動信号のレベルがハイ(オン)である区間であり、下に凸の区間は、それらの駆動信号のレベルがロー(オフ)である区間である。

垂直駆動部62は、画素駆動信号SIGnがオフの状態から、画素駆動信号SIGnをオンとして、さらにその後、オフに切り替える場合、次のように動作する。

画素駆動信号SIGnがオフである状態では、駆動信号DRNと駆動信号XDRPはオンの状態である。この状態から、画素駆動信号SIGnをオンとするために、垂直駆動部62は、駆動信号DRNをオフしてから、その後、駆動信号XDRPをオフする。駆動信号XDRPをオフしたとき、瞬時的に電源VDDの電圧が降下する。

このようにして画素駆動信号SIGnがオンとなった後、再び画素駆動信号SIGnをオフしようとする場合、垂直駆動部62は、まず駆動信号XDRPをオンさせてから、その後、駆動信号DRNをオンさせる。駆動信号DRNをオンしたとき、瞬時的に電源VSSの電圧が上昇する。

このように、垂直駆動部62は、駆動信号XDRPと駆動信号DRNの立ち上がり、および立下りのタイミングをずらすことにより、トランジスタ221とトランジスタ222に同時に電流が流れないようにして、貫通電流の発生を抑制する。これにより、全行同時に単位画素90の画素駆動信号を活性化させるときに生じる電源ゆれを、抑制することができる。

〈第5の実施の形態〉

[ドライバの構成]

なお、図14に示したドライバ191に電流リミッタを設け、さらに電源ゆれを少なくするようにしてもよい。そのような場合、ドライバ191は、図16に示すように構成される。図16に示すドライバ191には、図14に示したドライバ191に、さらに電流リミッタ251が設けられており、電流リミッタ251は、トランジスタ221とトランジスタ222の間に配置されている。

電流リミッタ251は、P型のトランジスタ261と、N型のトランジスタ262とから構成され、トランジスタ261のドレインと、トランジスタ262のドレインとが互いに接続されている。これらのトランジスタ261とトランジスタ262の間の電圧が、画素駆動信号SIGnとして単位画素90に供給される。

また、トランジスタ261のソースは、トランジスタ221のドレインに接続され、トランジスタ262のソースは、トランジスタ222のドレインに接続されている。さらに、トランジスタ261のゲートに印加される駆動信号biaspは、トランジスタ261に一定の電流が流れるようにするためのバイアスである。同様に、トランジスタ262のゲートに印加される駆動信号biasnは、トランジスタ262に一定の電流が流れるようにするためのバイアスである。

[ドライバの動作]

図16に示すように構成されるドライバ191は、垂直駆動部62によって、図17に示すように駆動される。なお、図17において、横方向は時間を示しており、DRN、XDRP、VDD、およびVSSは、駆動信号DRN、駆動信号XDRP、電源VDD、および電源VSSの各電圧を示している。また、図中、Biasp、Biasn、およびSIGは、駆動信号biasp、駆動信号biasn、および画素駆動信号SIGnの電圧を示している。

図17の例では、垂直駆動部62は、図15の例と同じタイミングでトランジスタ221およびトランジスタ222を制御する。すると、図中、SIGにより示される画素駆動信号SIGnは、オフの状態からオンとなり、その後、再びオフとなる。

ここで、曲線C31および曲線C32は、それぞれ図13の中央付近のドライバ191から出力される画素駆動信号SIGnの波形、および図13の端付近のドライバ191から出力される画素駆動信号SIGnの波形を表している。

例えば、曲線C31はドライバ191−4の画素駆動信号の波形であり、曲線C32はドライバ191−1の画素駆動信号の波形である。電源付近にあるドライバ191の曲線C32は、波形の立ち上がり、および立下りが急峻であるが、中央付近にあるドライバ191の曲線C31は、曲線C32と比べて、波形がなまっている。これは、後述するように、中央付近のドライバ191ほど、トランジスタに電流が流れにくくなるからである。

また、電流リミッタ251では、一定電圧値の駆動信号biasp、および駆動信号biasnが、継続してトランジスタ261のゲート、およびトランジスタ262のゲートに印加されている。これにより、ドライバ191の駆動時の貫通電流が抑制されるため、図17の例では、図15の場合と比較して、電源VDDおよび電源VSSのゆれが、より小さくなっている。

〈第6の実施の形態〉

[ドライバの構成]

ところで、図16のドライバ191では、電流リミッタ251を設けることで、電源ゆれをより小さくすることはできるが、駆動信号biaspと駆動信号biasnは一定電圧であるので、電源のAC(Alternating Current)的なゆれに追従するような構成となっていない。

すなわち、電源VDDおよび電源VSSから遠い位置にある、図13中、中央付近のドライバ191において電源ゆれが顕著となる。ところが、中央付近のドライバ191では、電源VDDや電源VSSがゆれるのにも関わらず、駆動信号biaspと駆動信号biasnの電圧は一定であるため、トランジスタ261とトランジスタ262における、ゲートとソース間の電圧Vgsは小さくなる。その結果、中央付近のドライバ191ほど、トランジスタ261やトランジスタ262に電流が流れにくくなってしまう。

そのため、図17に示したように、電源VDDや電源VSSに近いドライバ191と、遠いドライバ191とで、画素駆動信号SIGnの遷移時間差が生じる。この遷移時間差は、単位画素90ごとのカップリングの不均一性として現れるため、遷移時間を揃えることが望ましい。

そこで、ドライバ191を図18に示す構成とすれば、各ドライバ191から出力される画素駆動信号SIGnの立ち上がり、立下りの遷移時間をほぼ同じ時間とすることができる。なお、図18において、図16における場合と対応する部分には、同一の符号を付してあり、その説明は省略する。

図18に示すドライバ191は、図16のドライバ191に加えて、さらにキャパシタ291、スイッチ292、キャパシタ293、およびスイッチ294を備えている。

すなわち、トランジスタ261のゲートには、スイッチ292とバイアス線である信号線295を介して、電源Biaspが接続されている。この電源Biaspから、トランジスタ261のゲートに供給される駆動信号Biaspiは、トランジスタ261に一定の電流が流れるようにする電圧である。また、トランジスタ261のゲートは、電源VDDと直列に、キャパシタ291により接続されている。

同様に、トランジスタ262のゲートには、スイッチ294とバイアス線である信号線296を介して、電源Biasnが接続されている。この電源Biasnから、トランジスタ262のゲートに供給される駆動信号Biasniは、トランジスタ262に一定の電流が流れるようにする電圧である。また、トランジスタ262のゲートは、電源VSSと直列に、キャパシタ293により接続されている。

なお、キャパシタ291およびキャパシタ293は、安定化電源のためではなく、駆動信号Biaspiと駆動信号Biasniを、電源VDDおよび電源VSSのゆれに追従させるために挿入されているものである。また、スイッチ292やスイッチ294に代えて、高抵抗がトランジスタ261と信号線295の間、およびトランジスタ262と信号線296の間に設けられてもよい。

[ドライバの動作]

次に、図18に示すドライバ191の動作について説明する。

ドライバ191では、予めスイッチ292がオンされ、電源Biaspの電圧が、駆動信号Biaspiとして、トランジスタ261のゲートに印加されるようになされている。同様に、予めスイッチ294がオンされ、電源Biasnの電圧が、駆動信号Biasniとして、トランジスタ262のゲートに印加されるようになされている。

そして、垂直駆動部62は、全ての単位画素90が同時に、画素駆動信号により動作するグローバル駆動の直前に、スイッチ292およびスイッチ294をオフし、駆動信号Biaspiおよび駆動信号Biasniをホールド状態とする。

その後、グローバル駆動が開始されると、電源VDDや電源VSSにゆれが発生するが、そのゆれの分だけ駆動信号Biaspiおよび駆動信号Biasniが変動する。これにより、ドライバ191の電源VDDおよび電源VSSからの距離によらず、トランジスタ261とトランジスタ262のゲートとソース間の電圧は一定に保たれる。その結果、各行のドライバ191から出力される画素駆動信号SIGnの立ち上がり、および立下りの遷移時間を揃えることができ、画素駆動信号SIGnに起因する各行の単位画素90のカップリングを、均一にすることができる。

なお、図18に示す構成とされるドライバ191は、垂直駆動部62によって、図19に示すように駆動される。なお、図19において、横方向は時間を示しており、DRN、XDRP、VDD、およびVSSは、駆動信号DRN、駆動信号XDRP、電源VDD、および電源VSSの各電圧を示している。また、図中、Biaspi、Biasni、およびSIGは、駆動信号Biaspi、駆動信号Biasni、および画素駆動信号SIGnの電圧を示している。

図19の例では、垂直駆動部62は、図17の例と同じタイミングでトランジスタ221およびトランジスタ222を制御する。すると、図中、SIGにより示される画素駆動信号SIGnは、オフの状態からオンとなり、その後、再びオフとなる。

このとき、VDDおよびVSSに示されるように、図17の場合と同様の電源VDDおよび電源VSSのゆれが生じる。しかし、図18のドライバ191には、キャパシタ291とキャパシタ293が設けられているので、図19中、BiaspiおよびBiasniに示されるように、駆動信号Biaspiと駆動信号Biasniは、電源のゆれに追従して変動する。その結果、トランジスタ261およびトランジスタ262には、ほぼ均一に電流が流れ、SIGにより示される画素駆動信号SIGnは、なまることなく急峻に立ち上がり、また立ち下がっている。

このように、図14、図16、および図18に示すようにドライバ191を構成すれば、グローバル駆動時の電源ゆれの影響をより少なくすることができ、グローバル駆動時に発生するカップリングノイズの行ごとの不均一性を、低減させることができる。

なお、図16と図18に示したドライバ191には、電流リミッタ251が設けられているが、電源ゆれの大きいグローバル駆動時のみ電流リミッタ251が動作し、電源ゆれの小さい各行の単位画素90からの画素信号読み出し時には、電流リミッタ251が動作しないようにしてもよい。そのような場合、例えばグローバル駆動時には、トランジスタ261やトランジスタ262のゲートに所定の電圧が印加される。また、単一の行の画素信号読み出し時には、トランジスタ261やトランジスタ262のゲートに電源VDDや電源VSSのレベルに近い電圧が印加され、リミッタがかからないようにされる。

また、トランジスタ261のゲートと、電源VDD(トランジスタ221のソース)との間にキャパシタ291を設けると説明したが、電気容量(カップリング容量)を待たせることのできる素子であれば、どのような素子であってもよい。同様に、トランジスタ262のゲートと、電源VSS(トランジスタ222のソース)との間に電気容量を持たせることができれば、キャパシタ293ではなく、他の素子であってもよい。

以上のように、CMOSイメージセンサ50によれば、画素駆動信号による単位画素90の駆動を適切に制御することで、他の信号線遷移による浮遊拡散領域123のカップリングの影響をより少なくし、よりカップリングノイズの少ない画像を得ることができる。また、暗時のシェーディングも低減させることができる。

さらに、画素駆動信号の適切な制御により、他の信号配線と浮遊拡散領域123との間の寄生容量によるカップリングの影響をより少なくすることができるので、他の信号配線と浮遊拡散領域123との間にシールド配線を設ける必要がない。したがって、単位画素90の小型化や、同じ面積での高開口率化を図ることができる。また、単位画素90内の各素子のレイアウトの自由度を向上させることが可能となる。

〈単位画素のその他の構成例〉

[単位画素のその他の第1の構成例]

なお、本発明は、上述した実施の形態で説明した単位画素以外の構造にも採用することができる。以下、本発明が適用可能なその他の単位画素の構造について説明する。また、以下の図において、図6または図10と対応する部分には同一符号を付してあり、その説明は適宜省略する。

図20は、単位画素90のその他の第1の構成例を示す図である。

図20の単位画素90Bでは、図6の構成に加えて、フォトダイオード121と転送ゲート122との間に、第2転送ゲート321とメモリ部322が設けられており、さらにフォトダイオード121の図中、左側に図10に示したオーバーフローゲート161が設けられている。

第2転送ゲート321は、フォトダイオード121で光電変換され、その内部に蓄積された電荷を、ゲート電極321Aに転送パルスTRXが印加されることによって転送する。メモリ部322は、遮光されており、ゲート電極321Aの下に形成されたN型の埋め込みチャネル331によって形成され、第2転送ゲート321によってフォトダイオード121から転送された電荷を蓄積する。メモリ部322が埋め込みチャネル331によって形成されていることで、Si−SiO2界面での暗電流の発生を抑えることができるため画質の向上に寄与できる。

このメモリ部322において、その上部にゲート電極321Aを配置し、そのゲート電極321Aに転送パルスTRXを印加することでメモリ部322に変調をかけることができる。すなわち、ゲート電極321Aに転送パルスTRXが印加されることで、メモリ部322のポテンシャルが深くなる。これにより、メモリ部322の飽和電荷量を、変調を掛けない場合よりも増やすことができる。

また、図20の単位画素90Bでは、転送ゲート122は、ゲート電極122Aに転送パルスTRGが印加されると、メモリ部322に蓄積された電荷を、浮遊拡散領域123に転送する。

単位画素90Bはさらに、フォトダイオード121の蓄積電荷を排出するための電荷排出部としてのオーバーフローゲート161を有している。このオーバーフローゲート161は、露光開始時にゲート電極161Aに制御パルスABGが印加されることで、フォトダイオード121の電荷をN型層のドレイン部332に排出する。オーバーフローゲート161はさらに、露光終了後の読み出し期間中にフォトダイオード121が飽和して電荷が溢れるのを防ぐ作用をなす。ドレイン部332には、所定の電圧VDAが印加されている。

[メモリ部のゲート電極の電位]

ここで、電荷保持領域としてのメモリ部322のゲート電極、即ち、第2転送ゲート321のゲート電極321Aの電位について説明する。

本実施形態においては、電荷保持領域としてのメモリ部322のゲート電極の電位が、第2転送ゲート321および転送ゲート122のうち少なくともいずれか、たとえば第2転送ゲート321を非導通状態とする期間に、ピニング状態とする電位に設定される。より具体的には、第2転送ゲート321若しくは転送ゲート122のいずれか一方、または両方を非導通状態とする際に、ゲート電極321A,122Aに印加する電圧が、ゲート電極直下のSi表面にキャリアを蓄積できるピニング状態となるように設定される。

本実施形態のように、転送ゲートを形成するトランジスタがN型の場合、第2転送ゲート321を非導通状態とする際に、ゲート電極321Aに印加する電圧がP型ウェル層132に対しグランドGNDよりも負電位となる電圧に設定される。なお、図示しないが、転送ゲートを形成するトランジスタがP型である場合、P型ウェル層がN型ウェル層となり、このN型ウェル層に対して電源電圧VDDよりも高い電圧に設定される。

第2転送ゲート321を非導通状態とする際に、ゲート電極321Aに印加する電圧を、ゲート電極直下のSi表面にキャリアを蓄積できるピニング状態となるような電圧に設定する理由は以下の通りである。

第2転送ゲート321のゲート電極321Aの電位を、P型ウェル層132に対して同電位(例えば0V)とすると、Si表面の結晶欠陥から発生するキャリアがメモリ部322に蓄積され、暗電流となり画質を劣化させるおそれがある。このため、本実施形態においては、メモリ部322上に形成されるゲート電極321Aのオフ(OFF)電位を、P型ウェル層132に対して負電位、例えば−2.0Vとする。これにより、本実施形態においては、電荷保持期間中はメモリ部322のSi表面に正孔(ホール:Hole)を発生させ、Si表面で発生した電子(エレクトロン:Electron)を再結合させることが可能で、その結果、暗電流を低減することが可能である。

なお、図20の構成においては、メモリ部322の端部に、転送ゲート122のゲート電極122Aが存在することから、このゲート電極122Aも負電位とすることで、メモリ部322の端部で発生す暗電流を同様に抑えることが可能である。

[単位画素のその他の第2の構成例]

図21は、単位画素90のその他の第2の構成例である単位画素90Cの構造を示す図である。

単位画素90Cでは、ゲート電極321Aの下で、かつ、フォトダイオード121とメモリ部322との境界部分に、P−の不純物拡散領域361を設けることによりオーバーフローパス362を形成した点が図20の単位画素90Bと異なる。

オーバーフローパス362を形成するためには、不純物拡散領域361のポテンシャルを低くする必要がある。不純物拡散領域361に軽くN不純物をドープしてP不純物濃度を下げることで、P−の不純物拡散領域361を形成することができる。あるいはポテンシャルバリア形成の際に不純物拡散領域361にP不純物をドープする場合はその濃度を下げることで、P−の不純物拡散領域361を形成することができる。

単位画素90Cでは、低照度での発生電荷を優先的にフォトダイオード121で蓄積する手段として、フォトダイオード121とメモリ部322との境界部分に形成されたオーバーフローパス362が用いられる。

フォトダイオード121とメモリ部322との境界部分に、P−の不純物拡散領域361を設けることで境界部分のポテンシャルが下がる。このポテンシャルが下がった部分がオーバーフローパス362となる。そして、フォトダイオード121で発生し、オーバーフローパス362のポテンシャルを超えた電荷は、自動的にメモリ部322に漏れて、蓄積される。換言すれば、オーバーフローパス362のポテンシャル以下の発生電荷はフォトダイオード121に蓄積される。

オーバーフローパス362は中間電荷転送部としての機能を持つ。すなわち、中間電荷転送部としてのオーバーフローパス362は、複数の単位画素の全てが同時に撮像動作を行う露光期間において、フォトダイオード121での光電変換によって発生し、オーバーフローパス362のポテンシャルで決まる所定電荷量を超える電荷を信号電荷としてメモリ部322へ転送する。

なお、図21の例では、P−の不純物拡散領域361を設けることによりオーバーフローパス362を形成した構造が採用されている。しかし、P−の不純物拡散領域361を設ける代わりに、N−の不純物拡散領域361を設けることによりオーバーフローパス362を形成した構造をとることも可能である。

[単位画素のその他の第3の構成例]

図22は、単位画素90のその他の第3の構成例である単位画素90Dの構造を示す図である。

単位画素90Dは、図6の単位画素90の構成に、浮遊拡散領域123と同様のメモリ部322が設けられた構成となっている。即ち、単位画素90Dでは、第2転送ゲート321のゲート電極321Aがフォトダイオード121とメモリ部322の境界のP型ウェル層132の上部に設けられている。また、単位画素90Dでは、メモリ部322が浮遊拡散領域123と同様のN型層391によって形成される。

単位画素90Dにおけるグローバル露光動作は、例えば、次の手順で実行される。まず、電荷排出動作が全画素同時に実行され、同時露光が開始される。発生した光電荷がフォトダイオード121に蓄積される。露光終了時点で、第2転送ゲート321が全画素同時にオンされ、蓄積された光電荷がメモリ部322へ転送され、保持される。露光終了後、順次動作にてリセットレベルと信号レベルが読み出される。即ち、浮遊拡散領域123がリセットされ、次にリセットレベルが読み出される。続いて、メモリ部322の保持電荷が浮遊拡散領域123へ転送され、信号レベルが読み出される。

[単位画素のその他の第4の構成例]

図23は、単位画素90のその他の第4の構成例である単位画素90Eの構造を示す図である。

図20の単位画素90Bでは、メモリ部322が埋め込みチャネル331によって形成された構成となっている。これに対して、図23の単位画素90Eでは、メモリ部322を、埋め込み型のN型拡散領域421によって形成した構成が採用されている。

メモリ部322をN型拡散領域421によって形成した場合であっても、埋め込みチャネル331によって形成した場合と同様の作用効果を得ることができる。具体的には、P型ウェル層132の内部にN型拡散領域421を形成し、基板表面側にP型層422を形成することで、Si−SiO2界面で発生する暗電流がメモリ部322のN型拡散領域421に蓄積されることを回避できるため画質の向上に寄与できる。

ここで、メモリ部322のN型拡散領域421の不純物濃度は、浮遊拡散領域123の不純物濃度よりも低くすることが好ましい。このような不純物濃度の設定により、転送ゲート122によるメモリ部322から浮遊拡散領域123への電荷の転送効率を高めることができる。単位画素90Eにおけるグローバル露光動作は、図20の単位画素90Bと同様である。

なお、図23に示した単位画素90Eの構成では、メモリ部322を埋め込み型のN型拡散領域421によって形成したが、メモリ部322で発生する暗電流が増加することがあるものの、埋め込み型にしない構造としてもよい。

また、単位画素90Eの構成において、オーバーフローゲート161を省略し、転送パルスTRX,TRGおよびリセットパルスRSTを全てアクティブ状態にする構成を採ることができる。この構成を採ることにより、オーバーフローゲート161と同等の作用効果、即ちフォトダイオード121の電荷を排出し、また、読み出し期間中にフォトダイオード121で溢れた電荷を基板側に逃がすことができる。

[単位画素のその他の第5の構成例]

図24は、単位画素90のその他の第5の構成例である単位画素90Fの構造を示す図である。

図20の単位画素90Bでは、フォトダイオード121と浮遊拡散領域123の間に1つのメモリ部(MEM)322が配置されていたが、図24の単位画素90Fでは、さらにもう1つのメモリ部(MEM2)451が配置されている。即ち、メモリ部が2段構成となっている。

第3転送ゲート452は、メモリ部322に蓄積された電荷を、ゲート電極452Aに転送パルスTRX2が印加されることによって転送する。メモリ部451は、ゲート電極452Aの下に形成されたN型の埋め込みチャネル453によって形成され、第3転送ゲート452によってメモリ部322から転送された電荷を蓄積する。メモリ部451が埋め込みチャネル453によって形成されていることで、Si−SiO2界面での暗電流の発生を抑えることができるため画質の向上に寄与できる。

メモリ部451は、メモリ部322と同様の構成とされているので、メモリ部322と同様、変調を掛けた場合には、メモリ部451の飽和電荷量を変調を掛けない場合よりも増やすことができる。

単位画素90Fにおけるグローバル露光動作では、全画素同時に蓄積された光電荷はフォトダイオード121またはメモリ部322で保持される。メモリ部451は、画素信号が読み出されるまでの間、光電荷を保持するために使用される。

なお、上述した単位画素90におけるデバイス構造の導電型は一例に過ぎず、N型、P型が逆でも構わないし、また、基板131の導電型についてもN型、P型のどちらでも構わない。

[本発明を適用した電子機器の構成例]

なお、本発明は、固体撮像素子への適用に限られるものではない。即ち、本発明は、デジタルスチルカメラやビデオカメラ等の撮像装置や、撮像機能を有する携帯端末装置や、画像読取部に固体撮像素子を用いる複写機など、画像取込部(光電変換部)に固体撮像素子を用いる電子機器全般に対して適用可能である。固体撮像素子は、ワンチップとして形成された形態であってもよいし、撮像部と信号処理部または光学系とがまとめてパッケージングされた撮像機能を有するモジュール状の形態であってもよい。

図25は、本発明を適用した電子機器としての、撮像装置の構成例を示すブロック図である。

図25の撮像装置600は、レンズ群などからなる光学部601、上述した単位画素90の各構成が採用される固体撮像素子(撮像デバイス)602、およびカメラ信号処理回路であるDSP(Digital Signal Processor)回路603を備える。また、撮像装置600は、フレームメモリ604、表示部605、記録部606、操作部607、および電源部608も備える。DSP回路603、フレームメモリ604、表示部605、記録部606、操作部607および電源部608は、バスライン609を介して相互に接続されている。

光学部601は、被写体からの入射光(像光)を取り込んで固体撮像素子602の撮像面上に結像する。固体撮像素子602は、光学部601によって撮像面上に結像された入射光の光量を画素単位で電気信号に変換して画素信号として出力する。この固体撮像素子602として、上述した実施の形態に係るCMOSイメージセンサ50等の固体撮像素子、即ちグローバル露光によって歪みのない撮像を実現できる固体撮像素子を用いることができる。

表示部605は、例えば、液晶パネルや有機EL(electro luminescence)パネル等のパネル型表示装置からなり、固体撮像素子602で撮像された動画または静止画を表示する。記録部606は、固体撮像素子602で撮像された動画または静止画を、ビデオテープやDVD(Digital Versatile Disk)等の記録媒体に記録する。

操作部607は、ユーザによる操作の下に、撮像装置600が持つ様々な機能について操作指令を発する。電源部608は、DSP回路603、フレームメモリ604、表示部605、記録部606および操作部607の動作電源となる各種の電源を、これら供給対象に対して適宜供給する。

上述したように、固体撮像素子602として、上述した実施の形態に係るCMOSイメージセンサ50を用いることで、画素トランジスタの閾値バラツキに起因するノイズを低減し、高いS/Nを確保することができる。従って、ビデオカメラやデジタルスチルカメラ、さらには携帯電話機等のモバイル機器向けカメラモジュールなどの撮像装置600においても、撮像画像の高画質化を図ることができる。

また、上述した実施形態においては、可視光の光量に応じた信号電荷を物理量として検知する単位画素が行列状に配置されてなるCMOSイメージセンサに適用した場合を例に挙げて説明した。しかしながら、本発明はCMOSイメージセンサへの適用に限られるものではなく、画素アレイ部の画素列ごとにカラム処理部を配置してなるカラム方式の固体撮像素子全般に対して適用可能である。

また、本発明は、可視光の入射光量の分布を検知して画像として撮像する固体撮像素子への適用に限らず、赤外線やX線、あるいは粒子等の入射量の分布を画像として撮像する固体撮像素子や、広義の意味として、圧力や静電容量など、他の物理量の分布を検知して画像として撮像する指紋検出センサ等の固体撮像素子(物理量分布検知装置)全般に対して適用可能である。

なお、本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。