JP5555685B2 - 磁気スタックおよびメモリセル、ならびにセルを製造する方法 - Google Patents

磁気スタックおよびメモリセル、ならびにセルを製造する方法 Download PDFInfo

- Publication number

- JP5555685B2 JP5555685B2 JP2011275641A JP2011275641A JP5555685B2 JP 5555685 B2 JP5555685 B2 JP 5555685B2 JP 2011275641 A JP2011275641 A JP 2011275641A JP 2011275641 A JP2011275641 A JP 2011275641A JP 5555685 B2 JP5555685 B2 JP 5555685B2

- Authority

- JP

- Japan

- Prior art keywords

- magnetic

- layer

- afm

- saf

- tunnel junction

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000005291 magnetic effect Effects 0.000 title claims description 71

- 238000004519 manufacturing process Methods 0.000 title description 4

- 230000005290 antiferromagnetic effect Effects 0.000 claims description 20

- 238000000137 annealing Methods 0.000 claims description 19

- 230000005415 magnetization Effects 0.000 claims description 17

- 125000006850 spacer group Chemical group 0.000 claims description 15

- 230000001965 increasing effect Effects 0.000 claims description 13

- 230000000694 effects Effects 0.000 claims description 11

- 238000009792 diffusion process Methods 0.000 claims description 10

- 230000005294 ferromagnetic effect Effects 0.000 claims description 10

- 238000000034 method Methods 0.000 claims description 4

- 230000005641 tunneling Effects 0.000 claims description 2

- 150000002697 manganese compounds Chemical class 0.000 claims 2

- 230000001629 suppression Effects 0.000 claims 1

- 239000000463 material Substances 0.000 description 12

- 238000013500 data storage Methods 0.000 description 8

- 238000010586 diagram Methods 0.000 description 6

- 230000006870 function Effects 0.000 description 6

- 238000012986 modification Methods 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- 238000012546 transfer Methods 0.000 description 4

- 239000007787 solid Substances 0.000 description 3

- 238000003860 storage Methods 0.000 description 3

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 2

- 238000003491 array Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 230000002708 enhancing effect Effects 0.000 description 2

- 238000007726 management method Methods 0.000 description 2

- 239000011572 manganese Substances 0.000 description 2

- 238000013508 migration Methods 0.000 description 2

- 230000005012 migration Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 229910003321 CoFe Inorganic materials 0.000 description 1

- 229910019236 CoFeB Inorganic materials 0.000 description 1

- 229910001030 Iron–nickel alloy Inorganic materials 0.000 description 1

- -1 Ni and Co Chemical class 0.000 description 1

- 229910019041 PtMn Inorganic materials 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 230000003139 buffering effect Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 239000003112 inhibitor Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 239000000696 magnetic material Substances 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 230000005055 memory storage Effects 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- 238000013519 translation Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/14—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using thin-film elements

- G11C11/15—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using thin-film elements using multiple magnetic layers

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y40/00—Manufacture or treatment of nanostructures

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/161—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect details concerning the memory cell structure, e.g. the layers of the ferromagnetic memory cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1675—Writing or programming circuits or methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F10/00—Thin magnetic films, e.g. of one-domain structure

- H01F10/32—Spin-exchange-coupled multilayers, e.g. nanostructured superlattices

- H01F10/324—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer

- H01F10/3254—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer the spacer being semiconducting or insulating, e.g. for spin tunnel junction [STJ]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F10/00—Thin magnetic films, e.g. of one-domain structure

- H01F10/32—Spin-exchange-coupled multilayers, e.g. nanostructured superlattices

- H01F10/324—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer

- H01F10/329—Spin-exchange coupled multilayers wherein the magnetisation of the free layer is switched by a spin-polarised current, e.g. spin torque effect

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F41/00—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties

- H01F41/14—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for applying magnetic films to substrates

- H01F41/30—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for applying magnetic films to substrates for applying nanostructures, e.g. by molecular beam epitaxy [MBE]

- H01F41/302—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for applying magnetic films to substrates for applying nanostructures, e.g. by molecular beam epitaxy [MBE] for applying spin-exchange-coupled multilayers, e.g. nanostructured superlattices

- H01F41/303—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for applying magnetic films to substrates for applying nanostructures, e.g. by molecular beam epitaxy [MBE] for applying spin-exchange-coupled multilayers, e.g. nanostructured superlattices with exchange coupling adjustment of magnetic film pairs, e.g. interface modifications by reduction, oxidation

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/10—Magnetoresistive devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F10/00—Thin magnetic films, e.g. of one-domain structure

- H01F10/32—Spin-exchange-coupled multilayers, e.g. nanostructured superlattices

- H01F10/324—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer

- H01F10/3268—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer the exchange coupling being asymmetric, e.g. by use of additional pinning, by using antiferromagnetic or ferromagnetic coupling interface, i.e. so-called spin-valve [SV] structure, e.g. NiFe/Cu/NiFe/FeMn

- H01F10/3272—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer the exchange coupling being asymmetric, e.g. by use of additional pinning, by using antiferromagnetic or ferromagnetic coupling interface, i.e. so-called spin-valve [SV] structure, e.g. NiFe/Cu/NiFe/FeMn by use of anti-parallel coupled [APC] ferromagnetic layers, e.g. artificial ferrimagnets [AFI], artificial [AAF] or synthetic [SAF] anti-ferromagnets

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Power Engineering (AREA)

- Nanotechnology (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Mram Or Spin Memory Techniques (AREA)

- Hall/Mr Elements (AREA)

- Semiconductor Memories (AREA)

Description

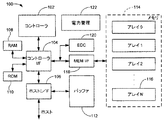

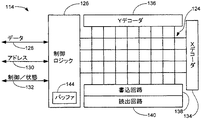

本発明のさまざまな実施形態は、概して、横方向磁気ピニング層を用いて構成される不揮発性メモリセルに向けられる。

本開示は、概して、スピントルクランダムアクセスメモリ(STRAM)セルのような、不揮発性メモリセルに関する。ソリッドステート不揮発性メモリは、フォームファクタを低減しつつ、信頼性のあるデータ記憶および高速データ転送を提供することを狙った、開発中の技術である。しかしながら、低い全体のデータ容量をもたらす大スイッチング電流、低動作マージン、および低面積密度のような、ソリッドステートセルに関連するいくつかの問題は、実際的な用途を抑制する。最近の試みにおいては、高揮発性は、セルのトンネル磁気抵抗(TMR)効果を低下させることによって、ソリッドステートセルをさらに苦しめ、それはセルの読出可能性(readability)および書込可能性(writeability)を低減させる。

Claims (15)

- 磁気スタックであって、

下から順番に積層される、下部電極と、合成反強磁性層(SAF)と、磁気トンネル接合と、磁気自由層と、上部電極とを備え、

前記磁気トンネル接合、前記磁気自由層および前記上部電極の横方向に配置されて、前記磁気トンネル接合を超えて横方向に伸延する前記SAFのピニング領域との接触を通じて、前記SAFの磁化を固定する反強磁性層(AFM)と、

前記磁気自由層および前記上部電極から、前記反強磁性層(AFM)を物理的かつ磁気的に分離するための非磁気スペーサ層とを備えた磁気スタック。 - トンネル磁気抵抗効果は、昇温および面内磁場の存在下における焼鈍を通して増加される、請求項1に記載の磁気スタック。

- 前記ピニング領域は、焼鈍中に、揮発性AFM原子の拡散を抑制する、請求項1に記載の磁気スタック。

- 前記磁気自由層は、第1の幅を有し、

前記磁気トンネル接合は、第2の幅を有し、

前記SAFは、第3の幅を有し、

前記ピニング領域は、前記第2の幅と前記第3の幅との差によって定められる、請求項1に記載の磁気スタック。 - 前記ピニング領域は、前記磁気自由層の横方向の両側に配置される、請求項1に記載の磁気スタック。

- 磁気スタックであって、

下から順番に積層される、下部電極と、単一の強磁性層と、磁気トンネル接合と、磁気自由層と、上部電極とを備え、

前記磁気トンネル接合、前記磁気自由層および前記上部電極の横方向に配置されて、前記磁気トンネル接合を超えて横方向に伸延する前記単一の強磁性層のピニング領域との接触を通じて、前記単一の強磁性層の磁化を固定する反強磁性層(AFM)と、

前記磁気自由層および前記上部電極から、前記反強磁性層(AFM)を物理的かつ磁気的に分離するための非磁気スペーサ層とを備えた磁気スタック。 - 前記AFMは、マンガン化合物である、請求項1に記載の磁気スタック。

- 前記マンガン化合物は、IrMnである、請求項7に記載の磁気スタック。

- 前記磁気スタックは不揮発性であり、スピン偏極電流を用いて前記磁気自由層に論理状態がプログラムされる、請求項1に記載の磁気スタック。

- 下から順番に積層される、下部電極と、合成反強磁性層(SAF)と、磁気トンネル接合と、磁気自由層と、上部電極とを提供するステップと、

前記磁気トンネル接合、前記磁気自由層および前記上部電極の横方向に反強磁性層(AFM)を提供するステップと、

前記磁気自由層および前記上部電極から、前記反強磁性層(AFM)を物理的かつ磁気的に分離するための非磁気スペーサ層を提供するステップと、

前記AFMを用いて、前記磁気トンネル接合を超えて横方向に伸延する前記SAFのピニング領域との接触を通じて、前記SAFの磁化を固定するステップとを備える、方法。 - 前記AFMは、交換バイアス場を用いて前記SAFを固定する、請求項10に記載の方法。

- 前記SAFは、前記磁気自由層の幅の少なくとも2倍の長さの幅を有する、請求項10に記載の方法。

- 前記ピニング領域は、前記磁気トンネル接合の側面部を除去することによって形成される、請求項10に記載の方法。

- メモリセルであって、

下から順番に積層される、下部電極と、合成反強磁性層(SAF)と、磁気トンネル接合と、磁気自由層と、上部電極とを備え、前記磁気自由層は、第1の幅を有し、前記磁気トンネル接合は、前記第1の幅よりも大きい第2の幅を有し、前記合成反強磁性層(SAF)は、少なくとも前記第1の幅の2倍である第3の幅を有し、

前記磁気トンネル接合、前記磁気自由層および前記上部電極の横方向に配置されて、前記磁気トンネル接合を超えて横方向に伸延する前記SAFのピニング領域との接触を通じて、前記SAFの磁化を固定する反強磁性層(AFM)と、

前記磁気自由層および前記上部電極から、前記反強磁性層(AFM)を物理的かつ磁気的に分離するための非磁気スペーサ層とを備え、

前記ピニング領域は、昇温および面内磁場の存在下における焼鈍中に、AFM原子の拡散を抑制する、メモリセル。 - 前記AFM原子の拡散の抑制は、前記SAFの磁気安定性を増加し、

前記焼鈍は、前記メモリセルについてのトンネル磁気抵抗を増加する、請求項14に記載のメモリセル。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/973,536 US8541247B2 (en) | 2010-12-20 | 2010-12-20 | Non-volatile memory cell with lateral pinning |

| US12/973,536 | 2010-12-20 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012134495A JP2012134495A (ja) | 2012-07-12 |

| JP2012134495A5 JP2012134495A5 (ja) | 2012-09-13 |

| JP5555685B2 true JP5555685B2 (ja) | 2014-07-23 |

Family

ID=46233284

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011275641A Expired - Fee Related JP5555685B2 (ja) | 2010-12-20 | 2011-12-16 | 磁気スタックおよびメモリセル、ならびにセルを製造する方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8541247B2 (ja) |

| JP (1) | JP5555685B2 (ja) |

| KR (1) | KR101361568B1 (ja) |

| CN (1) | CN102544352B (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8455117B2 (en) * | 2009-03-04 | 2013-06-04 | Seagate Technology Llc | Bit-patterned stack with antiferromagnetic shell |

| US9203017B2 (en) | 2013-08-02 | 2015-12-01 | Samsung Electronics Co., Ltd. | Method and system for providing magnetic junctions including a package structure usable in spin transfer torque memories |

| US9196825B2 (en) | 2013-09-03 | 2015-11-24 | Taiwan Semiconductor Manufacturing Co., Ltd. | Reversed stack MTJ |

| US9230630B2 (en) | 2013-09-09 | 2016-01-05 | Qualcomm Incorporated | Physically unclonable function based on the initial logical state of magnetoresistive random-access memory |

| US9214172B2 (en) * | 2013-10-23 | 2015-12-15 | Western Digital (Fremont), Llc | Method of manufacturing a magnetic read head |

| KR102214507B1 (ko) | 2014-09-15 | 2021-02-09 | 삼성전자 주식회사 | 자기 메모리 장치 |

| US9559294B2 (en) * | 2015-01-29 | 2017-01-31 | Taiwan Semiconductor Manufacturing Co., Ltd. | Self-aligned magnetoresistive random-access memory (MRAM) structure for process damage minimization |

| CN104659202A (zh) * | 2015-02-13 | 2015-05-27 | 西南应用磁学研究所 | 提高隧道结薄膜磁电阻效应的制备方法 |

| CN110970550B (zh) * | 2018-09-28 | 2023-06-23 | 联华电子股份有限公司 | 磁阻元件及其制作方法 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6738236B1 (en) | 1998-05-07 | 2004-05-18 | Seagate Technology Llc | Spin valve/GMR sensor using synthetic antiferromagnetic layer pinned by Mn-alloy having a high blocking temperature |

| US6700753B2 (en) | 2000-04-12 | 2004-03-02 | Seagate Technology Llc | Spin valve structures with specular reflection layers |

| JP4352659B2 (ja) * | 2002-06-25 | 2009-10-28 | ソニー株式会社 | 磁気抵抗効果素子の製造方法 |

| JP4143020B2 (ja) * | 2003-11-13 | 2008-09-03 | 株式会社東芝 | 磁気抵抗効果素子および磁気メモリ |

| US6960480B1 (en) * | 2004-05-19 | 2005-11-01 | Headway Technologies, Inc. | Method of forming a magnetic tunneling junction (MTJ) MRAM device and a tunneling magnetoresistive (TMR) read head |

| JP4337641B2 (ja) | 2004-06-10 | 2009-09-30 | ソニー株式会社 | 不揮発性磁気メモリ装置及びフォトマスク |

| JP2006059869A (ja) * | 2004-08-17 | 2006-03-02 | Sony Corp | トグルモード書込型不揮発性磁気メモリ装置 |

| CN101000821B (zh) * | 2006-01-11 | 2010-05-12 | 中国科学院物理研究所 | 一种闭合形状的磁性多层膜及其制备方法和用途 |

| US20070187785A1 (en) | 2006-02-16 | 2007-08-16 | Chien-Chung Hung | Magnetic memory cell and manufacturing method thereof |

| US7595520B2 (en) * | 2006-07-31 | 2009-09-29 | Magic Technologies, Inc. | Capping layer for a magnetic tunnel junction device to enhance dR/R and a method of making the same |

| TWI307507B (en) | 2006-10-20 | 2009-03-11 | Ind Tech Res Inst | Magnetic tunnel junction devices and magnetic random access memory |

| JP2008277621A (ja) * | 2007-05-01 | 2008-11-13 | Fujitsu Ltd | 磁気記憶装置 |

| US7688615B2 (en) | 2007-12-04 | 2010-03-30 | Macronix International Co., Ltd. | Magnetic random access memory, manufacturing method and programming method thereof |

| US7834385B2 (en) | 2008-08-08 | 2010-11-16 | Seagate Technology Llc | Multi-bit STRAM memory cells |

| US9929211B2 (en) * | 2008-09-24 | 2018-03-27 | Qualcomm Incorporated | Reducing spin pumping induced damping of a free layer of a memory device |

| US7939188B2 (en) * | 2008-10-27 | 2011-05-10 | Seagate Technology Llc | Magnetic stack design |

| US9165625B2 (en) | 2008-10-30 | 2015-10-20 | Seagate Technology Llc | ST-RAM cells with perpendicular anisotropy |

-

2010

- 2010-12-20 US US12/973,536 patent/US8541247B2/en not_active Expired - Fee Related

-

2011

- 2011-12-16 KR KR1020110136390A patent/KR101361568B1/ko not_active IP Right Cessation

- 2011-12-16 JP JP2011275641A patent/JP5555685B2/ja not_active Expired - Fee Related

- 2011-12-19 CN CN201110427752.2A patent/CN102544352B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US8541247B2 (en) | 2013-09-24 |

| US20120153413A1 (en) | 2012-06-21 |

| KR101361568B1 (ko) | 2014-02-12 |

| JP2012134495A (ja) | 2012-07-12 |

| CN102544352A (zh) | 2012-07-04 |

| KR20120069577A (ko) | 2012-06-28 |

| CN102544352B (zh) | 2015-04-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5555685B2 (ja) | 磁気スタックおよびメモリセル、ならびにセルを製造する方法 | |

| US9043740B2 (en) | Fabrication of a magnetic tunnel junction device | |

| JP5496911B2 (ja) | 個別の読み出しおよび書き込みパスを備えた磁気トンネル接合装置 | |

| EP2523193B1 (en) | An improved high capacity low cost multi-state magnetic memory | |

| US10868079B2 (en) | Magnetic detection circuit, MRAM and operation method thereof | |

| KR102363995B1 (ko) | 반도체 장치 및 이의 제조 방법 | |

| JP4997789B2 (ja) | 磁気メモリ | |

| US8729648B2 (en) | Magnetic body device and manufacturing method thereof | |

| US20090039450A1 (en) | Structure of magnetic memory cell and magnetic memory device | |

| JP2005210126A (ja) | 磁気トンネル接合型メモリセルおよびその製造方法、磁気トンネル接合型メモリセルアレイ | |

| KR20140095792A (ko) | 스핀 홀 효과를 이용한 메모리 소자와 그 제조 및 동작방법 | |

| TW201110435A (en) | Memory | |

| US20120120718A1 (en) | Multi-Bit Magnetic Memory with Independently Programmable Free Layer Domains | |

| JP2009094226A (ja) | 半導体装置およびその製造方法 | |

| JP2012014787A (ja) | 記憶装置 | |

| JP5529102B2 (ja) | 磁性積層体、方法、およびメモリセル | |

| US8203870B2 (en) | Flux programmed multi-bit magnetic memory | |

| WO2022087768A1 (zh) | 磁性隧道结、磁阻式随机存取存储器和电子器件 | |

| JPWO2009044609A1 (ja) | 磁気抵抗記憶素子、磁気抵抗記憶装置及び磁気抵抗記憶装置の動作方法 | |

| JP2004228406A (ja) | 磁気記憶素子およびその製造方法および磁気記憶素子の集積回路装置 | |

| JP2008235659A (ja) | ヨーク型磁気記憶装置の製造方法、ヨーク型磁気記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120731 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120731 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131206 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140107 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140404 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140507 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140602 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5555685 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |