JP5529648B2 - 磁気センサ積層体、その成膜方法、成膜制御プログラムおよび記録媒体 - Google Patents

磁気センサ積層体、その成膜方法、成膜制御プログラムおよび記録媒体 Download PDFInfo

- Publication number

- JP5529648B2 JP5529648B2 JP2010149407A JP2010149407A JP5529648B2 JP 5529648 B2 JP5529648 B2 JP 5529648B2 JP 2010149407 A JP2010149407 A JP 2010149407A JP 2010149407 A JP2010149407 A JP 2010149407A JP 5529648 B2 JP5529648 B2 JP 5529648B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- substrate

- forming

- magnetic

- stack

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000005291 magnetic effect Effects 0.000 title claims description 312

- 238000000034 method Methods 0.000 title claims description 135

- 230000015572 biosynthetic process Effects 0.000 title claims description 67

- 239000000758 substrate Substances 0.000 claims description 157

- 230000005290 antiferromagnetic effect Effects 0.000 claims description 81

- 229920002120 photoresistant polymer Polymers 0.000 claims description 36

- 238000005530 etching Methods 0.000 claims description 32

- 230000005294 ferromagnetic effect Effects 0.000 claims description 31

- 238000000151 deposition Methods 0.000 claims description 16

- 238000010884 ion-beam technique Methods 0.000 claims description 13

- 238000009966 trimming Methods 0.000 claims description 10

- 239000012528 membrane Substances 0.000 claims 2

- 230000008020 evaporation Effects 0.000 claims 1

- 238000001704 evaporation Methods 0.000 claims 1

- 230000005389 magnetism Effects 0.000 claims 1

- 239000010410 layer Substances 0.000 description 492

- 239000010408 film Substances 0.000 description 176

- 239000013078 crystal Substances 0.000 description 41

- 230000008569 process Effects 0.000 description 30

- 229910045601 alloy Inorganic materials 0.000 description 24

- 239000000956 alloy Substances 0.000 description 24

- 238000007737 ion beam deposition Methods 0.000 description 24

- 238000005304 joining Methods 0.000 description 20

- 230000005415 magnetization Effects 0.000 description 20

- 229910018979 CoPt Inorganic materials 0.000 description 18

- 238000005240 physical vapour deposition Methods 0.000 description 17

- 238000010586 diagram Methods 0.000 description 15

- 230000000694 effects Effects 0.000 description 13

- 238000012545 processing Methods 0.000 description 13

- 230000004907 flux Effects 0.000 description 12

- 230000002829 reductive effect Effects 0.000 description 12

- 238000004544 sputter deposition Methods 0.000 description 12

- 230000008878 coupling Effects 0.000 description 11

- 238000010168 coupling process Methods 0.000 description 11

- 238000005859 coupling reaction Methods 0.000 description 11

- 229910052804 chromium Inorganic materials 0.000 description 10

- 125000006850 spacer group Chemical group 0.000 description 10

- 229910020707 Co—Pt Inorganic materials 0.000 description 9

- 229910001030 Iron–nickel alloy Inorganic materials 0.000 description 9

- 238000001020 plasma etching Methods 0.000 description 9

- 229910052719 titanium Inorganic materials 0.000 description 9

- 238000012546 transfer Methods 0.000 description 9

- 239000012212 insulator Substances 0.000 description 8

- 230000007423 decrease Effects 0.000 description 7

- 230000008021 deposition Effects 0.000 description 7

- 239000000696 magnetic material Substances 0.000 description 7

- 239000002245 particle Substances 0.000 description 7

- 230000009467 reduction Effects 0.000 description 7

- 238000005229 chemical vapour deposition Methods 0.000 description 6

- 238000003860 storage Methods 0.000 description 6

- YTPMCWYIRHLEGM-BQYQJAHWSA-N 1-[(e)-2-propylsulfonylethenyl]sulfonylpropane Chemical compound CCCS(=O)(=O)\C=C\S(=O)(=O)CCC YTPMCWYIRHLEGM-BQYQJAHWSA-N 0.000 description 5

- 230000001154 acute effect Effects 0.000 description 5

- 238000000231 atomic layer deposition Methods 0.000 description 5

- 239000000203 mixture Substances 0.000 description 5

- 150000004767 nitrides Chemical class 0.000 description 5

- 230000035945 sensitivity Effects 0.000 description 5

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 4

- 229910019236 CoFeB Inorganic materials 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 239000003302 ferromagnetic material Substances 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 238000003475 lamination Methods 0.000 description 4

- 239000000463 material Substances 0.000 description 4

- 238000005259 measurement Methods 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 238000007740 vapor deposition Methods 0.000 description 4

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- 239000002885 antiferromagnetic material Substances 0.000 description 3

- 239000012298 atmosphere Substances 0.000 description 3

- 239000000470 constituent Substances 0.000 description 3

- RKTYLMNFRDHKIL-UHFFFAOYSA-N copper;5,10,15,20-tetraphenylporphyrin-22,24-diide Chemical group [Cu+2].C1=CC(C(=C2C=CC([N-]2)=C(C=2C=CC=CC=2)C=2C=CC(N=2)=C(C=2C=CC=CC=2)C2=CC=C3[N-]2)C=2C=CC=CC=2)=NC1=C3C1=CC=CC=C1 RKTYLMNFRDHKIL-UHFFFAOYSA-N 0.000 description 3

- 230000003247 decreasing effect Effects 0.000 description 3

- 230000005381 magnetic domain Effects 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- -1 Ta—N Chemical class 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 230000000052 comparative effect Effects 0.000 description 2

- 239000012141 concentrate Substances 0.000 description 2

- 239000013067 intermediate product Substances 0.000 description 2

- 238000010030 laminating Methods 0.000 description 2

- 230000000873 masking effect Effects 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 238000001228 spectrum Methods 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- 239000013077 target material Substances 0.000 description 2

- 239000011800 void material Substances 0.000 description 2

- 229910000859 α-Fe Inorganic materials 0.000 description 2

- 229910001149 41xx steel Inorganic materials 0.000 description 1

- 229910019222 CoCrPt Inorganic materials 0.000 description 1

- 229910020515 Co—W Inorganic materials 0.000 description 1

- 229910000599 Cr alloy Inorganic materials 0.000 description 1

- 229910002546 FeCo Inorganic materials 0.000 description 1

- 229910000914 Mn alloy Inorganic materials 0.000 description 1

- 229910000943 NiAl Inorganic materials 0.000 description 1

- NPXOKRUENSOPAO-UHFFFAOYSA-N Raney nickel Chemical compound [Al].[Ni] NPXOKRUENSOPAO-UHFFFAOYSA-N 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000011156 evaluation Methods 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 238000009499 grossing Methods 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 238000004091 panning Methods 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 239000000047 product Substances 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 238000001552 radio frequency sputter deposition Methods 0.000 description 1

- 238000007670 refining Methods 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 230000005641 tunneling Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/127—Structure or manufacture of heads, e.g. inductive

- G11B5/33—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only

- G11B5/39—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only using magneto-resistive devices or effects

- G11B5/3903—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only using magneto-resistive devices or effects using magnetic thin film layers or their effects, the films being part of integrated structures

- G11B5/3906—Details related to the use of magnetic thin film layers or to their effects

- G11B5/3929—Disposition of magnetic thin films not used for directly coupling magnetic flux from the track to the MR film or for shielding

- G11B5/3932—Magnetic biasing films

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R33/00—Arrangements or instruments for measuring magnetic variables

- G01R33/02—Measuring direction or magnitude of magnetic fields or magnetic flux

- G01R33/06—Measuring direction or magnitude of magnetic fields or magnetic flux using galvano-magnetic devices

- G01R33/09—Magnetoresistive devices

- G01R33/098—Magnetoresistive devices comprising tunnel junctions, e.g. tunnel magnetoresistance sensors

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/127—Structure or manufacture of heads, e.g. inductive

- G11B5/31—Structure or manufacture of heads, e.g. inductive using thin films

- G11B5/3163—Fabrication methods or processes specially adapted for a particular head structure, e.g. using base layers for electroplating, using functional layers for masking, using energy or particle beams for shaping the structure or modifying the properties of the basic layers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/127—Structure or manufacture of heads, e.g. inductive

- G11B5/33—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only

- G11B5/39—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only using magneto-resistive devices or effects

- G11B5/3903—Structure or manufacture of flux-sensitive heads, i.e. for reproduction only; Combination of such heads with means for recording or erasing only using magneto-resistive devices or effects using magnetic thin film layers or their effects, the films being part of integrated structures

- G11B5/398—Specially shaped layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/10—Magnetoresistive devices

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Hall/Mr Elements (AREA)

- Measuring Magnetic Variables (AREA)

- Magnetic Heads (AREA)

- Thin Magnetic Films (AREA)

Description

前記基板の上に前記反強磁性層および前記強磁性スタックを成膜する手順と、

前記強磁性スタックの上にフォトレジストマスクのパターンを形成する手順と、

前記強磁性スタックの一部をエッチングする手順と、

前記フォトレジストマスクの幅をトリミングする手順と、

前記トリミングされたフォトレジストマスクを使用して、前記強磁性スタックおよび前記反強磁性層をエッチングして、前記対向する2つの接合壁面の両方に、前記反強磁性層と前記強磁性スタックとで形成される段形状部分を有する前記段形状の磁気抵抗素子を形成する手順と、

前記フィールド領域にハードバイアス積層体を成膜する手順と、

前記段形状の磁気抵抗素子および前記ハードバイアス積層体の表面を平坦化する手順と、

を有することを特徴とする磁気センサ積層体の成膜方法である。

〔磁気センサ積層体の構造〕

まず、図1および図2を参照して、磁気抵抗素子を備える磁気センサ積層体の構造について説明する。図1は、本実施形態に係る磁気センサ積層体を模式的に示す概略図である。図2は、本実施形態に係る磁気センサ積層体の積層方向に対して垂直なプロフィールを示す概略図である。

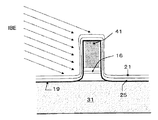

次に、図3から図9を参照して、上記磁気センサ積層体1の作用を説明すると共に、本実施形態に係る磁気センサ積層体1の成膜方法について説明する。

次に、図10および図11を参照して、第2の実施形態の磁気センサ積層体100およびその成膜方法について説明する。図10は、第1の実施形態の図5(f)(g)に相当する手順の概略図である。図11は、本実施形態による磁気センサ積層体の完成形を示す概略図である。なお、第1の実施形態と同一構成の部材については、同一の符号を付して説明する。

〔磁気センサ積層体の構造〕

まず、図12および図13を参照して、磁気抵抗素子を備える磁気センサ積層体の構造について説明する。図12は、本実施形態に係る磁気センサ積層体を模式的に示す概略図である。図13は、本実施形態に係る磁気センサ積層体の積層方向に対して垂直なプロフィールを示す概略図である。

次に、図7及び図14から図20を参照して、本実施形態の磁気センサ積層体1の成膜方法を説明すると共に、上記磁気センサ積層体1の作用について説明する。図14は、磁気抵抗素子上にフォトレジストマスクを配置した磁気センサ積層体を示す概略図である。図15は、本実施形態の磁気センサ積層体を構成するハードバイアス積層体をフィールド領域に成膜する手順を示す工程図である。

次に図21を参照して、第4の実施形態の成膜方法に用いる成膜装置について説明する。図21は、本実施形態の成膜装置を模式的に示す概略図である。なお、第3の実施形態と同様の構成要素については同一の符号を付して説明する。

第5の実施形態は、上記成膜方法を連続処理装置に適用する場合の適用例である。図25は、本実施形態の連続処理装置の装置構成例を示す平面図である。なお、第3の実施形態と同様の構成要素については同一の符号を付して説明する。

10 磁気抵抗素子(リーダースタック)

10a、10b 接合壁面

11 プレシード層

12 第3のシード層

13 反強磁性ピニング層(反強磁性層(AFM層))

14 シンセティックアンチフェロ層(SAF層)

14a ピンド層

14b カップリング層

14c リファレンス層

15 スペーサ層

16 フリー層

17,17a、17b 第3のキャッピング層

18 強磁性スタック(FMスタック)

19 絶縁層

20 ハードバイアス積層体

21 下地層

22 フィールド領域

22a 第1の磁性層

22b 第2の磁性層

23 第1のキャッピング層

24 第2のキャッピング層

25 第2のシード層

26 磁性層

31 基板(ボトムシールド層)

32 トップシールド層

41 フォトレジストマスク

41a トリミングマスク

51 成膜装置

52 基板ホルダ

53 シャッタ

54 スリット

122 磁性層

IB イオンビーム

T ターゲット

71 成膜装置

72 ターゲットホルダ

73 カソード

74 基板ホルダ

75 シャッタ

76 スリット

81 連続処理装置

82 搬送チャンバ

83 エッチング処理チャンバ

84 絶縁層成膜チャンバ

85 傾斜成膜チャンバ

86 IBDチャンバ

87 ロードロックモジュール

Claims (19)

- 基板上に、少なくとも、反強磁性層上の一部に強磁性スタックを備える段形状の磁気抵抗素子を配置し、前記磁気抵抗素子の対向する2つの接合壁面の側方のフィールド領域に、前記磁気抵抗素子にバイアス磁界を与えるためのハードバイアス積層体を成膜する磁気センサ積層体の成膜方法であって、

前記基板の上に前記反強磁性層および前記強磁性スタックを成膜する手順と、

前記強磁性スタックの上にフォトレジストマスクのパターンを形成する手順と、

前記強磁性スタックの一部をエッチングする手順と、

前記フォトレジストマスクの幅をトリミングする手順と、

前記トリミングされたフォトレジストマスクを使用して、前記強磁性スタックおよび前記反強磁性層をエッチングして、前記対向する2つの接合壁面の両方に、前記反強磁性層と前記強磁性スタックとで形成される段形状部分を有する前記段形状の磁気抵抗素子を形成する手順と、

前記フィールド領域にハードバイアス積層体を成膜する手順と、

前記段形状の磁気抵抗素子および前記ハードバイアス積層体の表面を平坦化する手順と、

を有することを特徴とする磁気センサ積層体の成膜方法。 - 前記段形状の磁気抵抗素子は、前記接合壁面が対向する方向に沿った前記強磁性スタックの最上面の幅が、前記接合壁面が対向する方向に沿った前記反強磁性層の最上面の幅よりも小さく形成されていることを特徴とする請求項1に記載の磁気センサ積層体の成膜方法。

- 前記ハードバイアス積層体を成膜する手順は、

前記基板の法線から成膜角度θ1(θ1=0〜25度)で、下地層を成膜する手順と、

前記基板の法線から成膜角度θ2(θ2=50〜90度)で、第1の磁性層を成膜する手順と、

前記基板の法線から成膜角度θ3(θ3=0〜25度)で、第2の磁性層を成膜する手順と、

前記基板の法線から成膜角度θ4(θ4=0〜45度)で、第1のキャッピング層を成膜する手順と、

を有することを特徴とする請求項1または2に記載の磁気センサ積層体の成膜方法。 - 前記第1の磁性層は、前記磁気抵抗素子の接合壁面と平行な細長いターゲットの下で、前記基板を一定の速度で直線的に移動させて、前記磁気抵抗素子の接合壁面の一方の面に成膜し、

次いで、前記基板をその中央垂直軸を中心に180度回転させ、前記ターゲットの下で前記基板を一定の速度で直線的に移動させて、前記接合壁面の他方の面に成膜することを特徴とする請求項3に記載の磁気センサ積層体の成膜方法。 - 前記下地層、前記第2の磁性層および前記第1のキャッピング層は、前記ターゲットの下で、前記基板を一定の速度で直線的に移動させて、一方のフィールド領域に成膜し、

前記基板をその中央垂直軸を中心に180度回転させ、前記ターゲットの下で、前記基板を一定の速度で直線的に移動させて、他方のフィールド領域に成膜することを特徴とする請求項4に記載の磁気センサ積層体の成膜方法。 - 前記フィールド領域にハードバイアス積層体を成膜する手順の前に、絶縁層を成膜する手順を有することを特徴とする請求項1から5のいずれか1項に記載の磁気センサ積層体の成膜方法。

- 前記磁気抵抗素子および前記ハードバイアス積層体の表面を平坦化する手順の後に、第2のキャッピング層を成膜する手順を有することを特徴とする請求項1から6のいずれか1項に記載の磁気センサ積層体の成膜方法。

- 前記第2のキャッピング層を成膜する手順の後に、シールド層を成膜する手順を有することを特徴とする請求項7に記載の磁気センサ積層体の成膜方法。

- イオンビーム蒸着法により前記ハードバイアス積層体を成膜することを特徴とする請求項1から8のいずれか1項に記載の磁気センサ積層体の成膜方法。

- 前記基板上に複数の段形状の磁気抵抗素子が形成され、該複数の磁気抵抗素子の前記ハードバイアス積層体は同一の手順で積層することを特徴とする請求項1から9のいずれか1項に記載の磁気センサ積層体の成膜方法。

- 基板上に、少なくとも、反強磁性層上の一部に強磁性スタックを備える段形状の磁気抵抗素子を配置し、前記磁気抵抗素子の対向する2つの接合壁面の側方のフィールド領域に、前記磁気抵抗素子にバイアス磁界を与えるためのハードバイアス積層体を成膜する磁気センサ積層体の成膜制御プログラムであって、

前記磁気センサ積層体の成膜装置に、

前記基板の上に前記反強磁性層および前記強磁性スタックを成膜する手順と、

前記強磁性スタックの上にフォトレジストマスクのパターンを形成する手順と、

前記強磁性スタックの一部をエッチングする手順と、

前記フォトレジストマスクの幅をトリミングする手順と、

前記トリミングされたフォトレジストマスクを使用して、前記強磁性スタックおよび前記反強磁性層をエッチングして、前記対向する2つの接合壁面の両方に、前記反強磁性層と前記強磁性スタックとで形成される段形状部分を有する前記段形状の磁気抵抗素子を形成する手順と、

前記フィールド領域にハードバイアス積層体を成膜する手順と、

前記段形状の磁気抵抗素子およびハードバイアス積層体の表面を平坦化する手順と、

を実行させることを特徴とする磁気センサ積層体の成膜制御プログラム。 - 前記段形状の磁気抵抗素子は、前記接合壁面が対向する方向に沿った前記強磁性スタックの最上面の幅が、前記接合壁面が対向する方向に沿った前記反強磁性層の最上面の幅よりも小さく形成されていることを特徴とする請求項11に記載の磁気センサ積層体の成膜制御プログラム。

- 前記ハードバイアス積層体を成膜する手順は、

前記基板の法線から成膜角度θ1(θ1=0〜25度)で、下地層を成膜する手順と、

前記基板の法線から成膜角度θ2(θ2=50〜90度)で、第1の磁性層を成膜する手順と、

前記基板の法線から成膜角度θ3(θ3=0〜25度)で、第2の磁性層を成膜する手順と、

前記基板の法線から成膜角度θ4(θ4=0〜45度)で、第1のキャッピング層を成膜する手順と、

を有することを特徴とする請求項11または12に記載の磁気センサ積層体の成膜制御プログラム。 - 前記第1の磁性層は、前記磁気抵抗素子の接合壁面と平行な細長いターゲットの下で、前記基板を一定の速度で直線的に移動させて、前記磁気抵抗素子の接合壁面の一方の面に成膜し、

次いで、前記基板をその中央垂直軸を中心に180度回転させ、前記ターゲットの下で前記基板を一定の速度で直線的に移動させて、前記接合壁面の他方の面に成膜することを特徴とする請求項13に記載の磁気センサ積層体の成膜制御プログラム。 - 前記下地層、前記第2の磁性層および前記第1のキャッピング層は、前記ターゲットの下で、前記基板を一定の速度で直線的に移動させて、一方のフィールド領域に成膜し、

前記基板をその中央垂直軸を中心に180度回転させ、前記ターゲットの下で、前記基板を一定の速度で直線的に移動させて、他方のフィールド領域に成膜することを特徴とする請求項14に記載の磁気センサ積層体の成膜制御プログラム。 - 前記フィールド領域にハードバイアス積層体を成膜する手順の前に、絶縁層を成膜する手順を有することを特徴とする請求項11から15のいずれか1項に記載の磁気センサ積層体の成膜制御プログラム。

- 前記磁気抵抗素子およびハードバイアス積層体の表面を平坦化する手順の後に、第2のキャッピング層を成膜する手順を有することを特徴とする請求項11から16のいずれか1項に記載の磁気センサ積層体の成膜制御プログラム。

- 前記第2のキャッピング層を成膜する手順の後に、シールド層を成膜する手順を有することを特徴とする請求項17に記載の磁気センサ積層体の成膜制御プログラム。

- 請求項11から18のいずれか1項に記載の成膜制御プログラムを記録したことを特徴とするコンピュータで読み取り可能な記録媒体。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010149407A JP5529648B2 (ja) | 2009-08-04 | 2010-06-30 | 磁気センサ積層体、その成膜方法、成膜制御プログラムおよび記録媒体 |

| US12/849,907 US8810974B2 (en) | 2009-08-04 | 2010-08-04 | Magnetic sensor stack body, method of forming the same, film formation control program, and recording medium |

| CN201010250345.4A CN101989643B (zh) | 2009-08-04 | 2010-08-04 | 磁传感器层叠体、成膜方法、成膜控制程序以及记录介质 |

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009181479 | 2009-08-04 | ||

| JP2009181479 | 2009-08-04 | ||

| JP2009219943 | 2009-09-25 | ||

| JP2009219943 | 2009-09-25 | ||

| JP2010149407A JP5529648B2 (ja) | 2009-08-04 | 2010-06-30 | 磁気センサ積層体、その成膜方法、成膜制御プログラムおよび記録媒体 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011090759A JP2011090759A (ja) | 2011-05-06 |

| JP2011090759A5 JP2011090759A5 (ja) | 2013-07-25 |

| JP5529648B2 true JP5529648B2 (ja) | 2014-06-25 |

Family

ID=43534686

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010149407A Active JP5529648B2 (ja) | 2009-08-04 | 2010-06-30 | 磁気センサ積層体、その成膜方法、成膜制御プログラムおよび記録媒体 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8810974B2 (ja) |

| JP (1) | JP5529648B2 (ja) |

| CN (1) | CN101989643B (ja) |

Families Citing this family (98)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8507113B2 (en) * | 2009-06-09 | 2013-08-13 | Canon Anelva Corporation | Magnetic sensor stack body, method of forming the same, film formation control program, and recording medium |

| US8233248B1 (en) | 2009-09-16 | 2012-07-31 | Western Digital (Fremont), Llc | Method and system for providing a magnetic recording transducer using a line hard mask |

| US20120063034A1 (en) * | 2010-09-13 | 2012-03-15 | Hitachi Global Storage Technologies Netherlands B.V. | Current-perpendicular-to-the-plane (cpp) magnetoresistive (mr) sensor with improved insulating structure |

| US20120125884A1 (en) * | 2010-11-24 | 2012-05-24 | Hitachi Global Storage Technologies Netherlands B. V. | Method for manufacturing a narrow magnetic read width current perpendicular to plane magnetoresistive sensor |

| US8871102B2 (en) * | 2011-05-25 | 2014-10-28 | Western Digital (Fremont), Llc | Method and system for fabricating a narrow line structure in a magnetic recording head |

| US9036308B2 (en) | 2011-09-21 | 2015-05-19 | Seagate Technology Llc | Varyinig morphology in magnetic sensor sub-layers |

| JP5982795B2 (ja) | 2011-11-30 | 2016-08-31 | ソニー株式会社 | 記憶素子、記憶装置 |

| US8822046B2 (en) | 2012-04-30 | 2014-09-02 | Seagate Technology Llc | Stack with wide seed layer |

| US9490054B2 (en) * | 2012-10-11 | 2016-11-08 | Headway Technologies, Inc. | Seed layer for multilayer magnetic materials |

| US9053713B2 (en) | 2012-10-14 | 2015-06-09 | Headway Technologies, Inc. | High coercivity magnetic film for use as a hot seed in a magnetic write head and method to grow it |

| JP6053819B2 (ja) * | 2012-11-26 | 2016-12-27 | キヤノンアネルバ株式会社 | 磁気抵抗効果素子の製造方法 |

| US9123886B2 (en) | 2013-03-05 | 2015-09-01 | Headway Technologies, Inc. | High moment wrap-around shields for magnetic read head improvements |

| US9034564B1 (en) | 2013-07-26 | 2015-05-19 | Western Digital (Fremont), Llc | Reader fabrication method employing developable bottom anti-reflective coating |

| CN103424131B (zh) * | 2013-08-26 | 2015-08-05 | 电子科技大学 | 一种垂直偏置磁传感单元的制备方法 |

| US9263667B1 (en) * | 2014-07-25 | 2016-02-16 | Spin Transfer Technologies, Inc. | Method for manufacturing MTJ memory device |

| US9337412B2 (en) | 2014-09-22 | 2016-05-10 | Spin Transfer Technologies, Inc. | Magnetic tunnel junction structure for MRAM device |

| US9728712B2 (en) | 2015-04-21 | 2017-08-08 | Spin Transfer Technologies, Inc. | Spin transfer torque structure for MRAM devices having a spin current injection capping layer |

| US10468590B2 (en) | 2015-04-21 | 2019-11-05 | Spin Memory, Inc. | High annealing temperature perpendicular magnetic anisotropy structure for magnetic random access memory |

| US9922670B1 (en) * | 2015-04-30 | 2018-03-20 | Seagate Technology Llc | Method of manufacturing a recessed data reader pinning structure with vertical sidewall |

| US9853206B2 (en) | 2015-06-16 | 2017-12-26 | Spin Transfer Technologies, Inc. | Precessional spin current structure for MRAM |

| US9773974B2 (en) | 2015-07-30 | 2017-09-26 | Spin Transfer Technologies, Inc. | Polishing stop layer(s) for processing arrays of semiconductor elements |

| US10163479B2 (en) | 2015-08-14 | 2018-12-25 | Spin Transfer Technologies, Inc. | Method and apparatus for bipolar memory write-verify |

| US9741926B1 (en) | 2016-01-28 | 2017-08-22 | Spin Transfer Technologies, Inc. | Memory cell having magnetic tunnel junction and thermal stability enhancement layer |

| US10230042B2 (en) | 2016-03-03 | 2019-03-12 | Toshiba Memory Corporation | Magnetoresistive element and method of manufacturing the same |

| RU2633010C1 (ru) * | 2016-05-04 | 2017-10-11 | Акционерное общество "Научно-производственное объединение измерительной техники" | Магниторезистивный датчик |

| US10628316B2 (en) | 2016-09-27 | 2020-04-21 | Spin Memory, Inc. | Memory device with a plurality of memory banks where each memory bank is associated with a corresponding memory instruction pipeline and a dynamic redundancy register |

| US10437723B2 (en) | 2016-09-27 | 2019-10-08 | Spin Memory, Inc. | Method of flushing the contents of a dynamic redundancy register to a secure storage area during a power down in a memory device |

| US10818331B2 (en) | 2016-09-27 | 2020-10-27 | Spin Memory, Inc. | Multi-chip module for MRAM devices with levels of dynamic redundancy registers |

| US10546625B2 (en) | 2016-09-27 | 2020-01-28 | Spin Memory, Inc. | Method of optimizing write voltage based on error buffer occupancy |

| US10991410B2 (en) | 2016-09-27 | 2021-04-27 | Spin Memory, Inc. | Bi-polar write scheme |

| US10360964B2 (en) | 2016-09-27 | 2019-07-23 | Spin Memory, Inc. | Method of writing contents in memory during a power up sequence using a dynamic redundancy register in a memory device |

| US10446210B2 (en) | 2016-09-27 | 2019-10-15 | Spin Memory, Inc. | Memory instruction pipeline with a pre-read stage for a write operation for reducing power consumption in a memory device that uses dynamic redundancy registers |

| US10366774B2 (en) | 2016-09-27 | 2019-07-30 | Spin Memory, Inc. | Device with dynamic redundancy registers |

| US11119936B2 (en) | 2016-09-27 | 2021-09-14 | Spin Memory, Inc. | Error cache system with coarse and fine segments for power optimization |

| US11151042B2 (en) | 2016-09-27 | 2021-10-19 | Integrated Silicon Solution, (Cayman) Inc. | Error cache segmentation for power reduction |

| US10460781B2 (en) | 2016-09-27 | 2019-10-29 | Spin Memory, Inc. | Memory device with a dual Y-multiplexer structure for performing two simultaneous operations on the same row of a memory bank |

| US10437491B2 (en) | 2016-09-27 | 2019-10-08 | Spin Memory, Inc. | Method of processing incomplete memory operations in a memory device during a power up sequence and a power down sequence using a dynamic redundancy register |

| US11119910B2 (en) | 2016-09-27 | 2021-09-14 | Spin Memory, Inc. | Heuristics for selecting subsegments for entry in and entry out operations in an error cache system with coarse and fine grain segments |

| US9799357B1 (en) | 2016-11-08 | 2017-10-24 | Headway Technologies, Inc. | Magnetic reader sensor with shield spacing improvement and better pin flop robustness |

| US10665777B2 (en) | 2017-02-28 | 2020-05-26 | Spin Memory, Inc. | Precessional spin current structure with non-magnetic insertion layer for MRAM |

| US10672976B2 (en) | 2017-02-28 | 2020-06-02 | Spin Memory, Inc. | Precessional spin current structure with high in-plane magnetization for MRAM |

| US10032978B1 (en) | 2017-06-27 | 2018-07-24 | Spin Transfer Technologies, Inc. | MRAM with reduced stray magnetic fields |

| US10489245B2 (en) | 2017-10-24 | 2019-11-26 | Spin Memory, Inc. | Forcing stuck bits, waterfall bits, shunt bits and low TMR bits to short during testing and using on-the-fly bit failure detection and bit redundancy remapping techniques to correct them |

| US10656994B2 (en) | 2017-10-24 | 2020-05-19 | Spin Memory, Inc. | Over-voltage write operation of tunnel magnet-resistance (“TMR”) memory device and correcting failure bits therefrom by using on-the-fly bit failure detection and bit redundancy remapping techniques |

| US10481976B2 (en) | 2017-10-24 | 2019-11-19 | Spin Memory, Inc. | Forcing bits as bad to widen the window between the distributions of acceptable high and low resistive bits thereby lowering the margin and increasing the speed of the sense amplifiers |

| US10529439B2 (en) | 2017-10-24 | 2020-01-07 | Spin Memory, Inc. | On-the-fly bit failure detection and bit redundancy remapping techniques to correct for fixed bit defects |

| US10679685B2 (en) | 2017-12-27 | 2020-06-09 | Spin Memory, Inc. | Shared bit line array architecture for magnetoresistive memory |

| US10395712B2 (en) | 2017-12-28 | 2019-08-27 | Spin Memory, Inc. | Memory array with horizontal source line and sacrificial bitline per virtual source |

| US10516094B2 (en) | 2017-12-28 | 2019-12-24 | Spin Memory, Inc. | Process for creating dense pillars using multiple exposures for MRAM fabrication |

| US10360962B1 (en) | 2017-12-28 | 2019-07-23 | Spin Memory, Inc. | Memory array with individually trimmable sense amplifiers |

| US10811594B2 (en) | 2017-12-28 | 2020-10-20 | Spin Memory, Inc. | Process for hard mask development for MRAM pillar formation using photolithography |

| US10424726B2 (en) | 2017-12-28 | 2019-09-24 | Spin Memory, Inc. | Process for improving photoresist pillar adhesion during MRAM fabrication |

| US10395711B2 (en) | 2017-12-28 | 2019-08-27 | Spin Memory, Inc. | Perpendicular source and bit lines for an MRAM array |

| US10891997B2 (en) | 2017-12-28 | 2021-01-12 | Spin Memory, Inc. | Memory array with horizontal source line and a virtual source line |

| US10546624B2 (en) | 2017-12-29 | 2020-01-28 | Spin Memory, Inc. | Multi-port random access memory |

| US10270027B1 (en) | 2017-12-29 | 2019-04-23 | Spin Memory, Inc. | Self-generating AC current assist in orthogonal STT-MRAM |

| US10367139B2 (en) | 2017-12-29 | 2019-07-30 | Spin Memory, Inc. | Methods of manufacturing magnetic tunnel junction devices |

| US10840439B2 (en) | 2017-12-29 | 2020-11-17 | Spin Memory, Inc. | Magnetic tunnel junction (MTJ) fabrication methods and systems |

| US10840436B2 (en) | 2017-12-29 | 2020-11-17 | Spin Memory, Inc. | Perpendicular magnetic anisotropy interface tunnel junction devices and methods of manufacture |

| US10236047B1 (en) | 2017-12-29 | 2019-03-19 | Spin Memory, Inc. | Shared oscillator (STNO) for MRAM array write-assist in orthogonal STT-MRAM |

| US10199083B1 (en) | 2017-12-29 | 2019-02-05 | Spin Transfer Technologies, Inc. | Three-terminal MRAM with ac write-assist for low read disturb |

| US10886330B2 (en) | 2017-12-29 | 2021-01-05 | Spin Memory, Inc. | Memory device having overlapping magnetic tunnel junctions in compliance with a reference pitch |

| US10784439B2 (en) | 2017-12-29 | 2020-09-22 | Spin Memory, Inc. | Precessional spin current magnetic tunnel junction devices and methods of manufacture |

| US10360961B1 (en) | 2017-12-29 | 2019-07-23 | Spin Memory, Inc. | AC current pre-charge write-assist in orthogonal STT-MRAM |

| US10236048B1 (en) | 2017-12-29 | 2019-03-19 | Spin Memory, Inc. | AC current write-assist in orthogonal STT-MRAM |

| US10424723B2 (en) | 2017-12-29 | 2019-09-24 | Spin Memory, Inc. | Magnetic tunnel junction devices including an optimization layer |

| US10339993B1 (en) | 2017-12-30 | 2019-07-02 | Spin Memory, Inc. | Perpendicular magnetic tunnel junction device with skyrmionic assist layers for free layer switching |

| US10236439B1 (en) | 2017-12-30 | 2019-03-19 | Spin Memory, Inc. | Switching and stability control for perpendicular magnetic tunnel junction device |

| US10319900B1 (en) | 2017-12-30 | 2019-06-11 | Spin Memory, Inc. | Perpendicular magnetic tunnel junction device with precessional spin current layer having a modulated moment density |

| US10229724B1 (en) | 2017-12-30 | 2019-03-12 | Spin Memory, Inc. | Microwave write-assist in series-interconnected orthogonal STT-MRAM devices |

| US10255962B1 (en) | 2017-12-30 | 2019-04-09 | Spin Memory, Inc. | Microwave write-assist in orthogonal STT-MRAM |

| US10141499B1 (en) | 2017-12-30 | 2018-11-27 | Spin Transfer Technologies, Inc. | Perpendicular magnetic tunnel junction device with offset precessional spin current layer |

| US10468588B2 (en) | 2018-01-05 | 2019-11-05 | Spin Memory, Inc. | Perpendicular magnetic tunnel junction device with skyrmionic enhancement layers for the precessional spin current magnetic layer |

| US10438996B2 (en) | 2018-01-08 | 2019-10-08 | Spin Memory, Inc. | Methods of fabricating magnetic tunnel junctions integrated with selectors |

| US10438995B2 (en) | 2018-01-08 | 2019-10-08 | Spin Memory, Inc. | Devices including magnetic tunnel junctions integrated with selectors |

| US10388861B1 (en) | 2018-03-08 | 2019-08-20 | Spin Memory, Inc. | Magnetic tunnel junction wafer adaptor used in magnetic annealing furnace and method of using the same |

| US10446744B2 (en) | 2018-03-08 | 2019-10-15 | Spin Memory, Inc. | Magnetic tunnel junction wafer adaptor used in magnetic annealing furnace and method of using the same |

| US11107978B2 (en) | 2018-03-23 | 2021-08-31 | Spin Memory, Inc. | Methods of manufacturing three-dimensional arrays with MTJ devices including a free magnetic trench layer and a planar reference magnetic layer |

| US11107974B2 (en) | 2018-03-23 | 2021-08-31 | Spin Memory, Inc. | Magnetic tunnel junction devices including a free magnetic trench layer and a planar reference magnetic layer |

| US20190296228A1 (en) | 2018-03-23 | 2019-09-26 | Spin Transfer Technologies, Inc. | Three-Dimensional Arrays with Magnetic Tunnel Junction Devices Including an Annular Free Magnetic Layer and a Planar Reference Magnetic Layer |

| US10784437B2 (en) | 2018-03-23 | 2020-09-22 | Spin Memory, Inc. | Three-dimensional arrays with MTJ devices including a free magnetic trench layer and a planar reference magnetic layer |

| US10411185B1 (en) | 2018-05-30 | 2019-09-10 | Spin Memory, Inc. | Process for creating a high density magnetic tunnel junction array test platform |

| US10593396B2 (en) | 2018-07-06 | 2020-03-17 | Spin Memory, Inc. | Multi-bit cell read-out techniques for MRAM cells with mixed pinned magnetization orientations |

| US10692569B2 (en) | 2018-07-06 | 2020-06-23 | Spin Memory, Inc. | Read-out techniques for multi-bit cells |

| US10559338B2 (en) | 2018-07-06 | 2020-02-11 | Spin Memory, Inc. | Multi-bit cell read-out techniques |

| US10600478B2 (en) | 2018-07-06 | 2020-03-24 | Spin Memory, Inc. | Multi-bit cell read-out techniques for MRAM cells with mixed pinned magnetization orientations |

| US10650875B2 (en) | 2018-08-21 | 2020-05-12 | Spin Memory, Inc. | System for a wide temperature range nonvolatile memory |

| US10699761B2 (en) | 2018-09-18 | 2020-06-30 | Spin Memory, Inc. | Word line decoder memory architecture |

| US10971680B2 (en) | 2018-10-01 | 2021-04-06 | Spin Memory, Inc. | Multi terminal device stack formation methods |

| US11621293B2 (en) | 2018-10-01 | 2023-04-04 | Integrated Silicon Solution, (Cayman) Inc. | Multi terminal device stack systems and methods |

| US10580827B1 (en) | 2018-11-16 | 2020-03-03 | Spin Memory, Inc. | Adjustable stabilizer/polarizer method for MRAM with enhanced stability and efficient switching |

| US11107979B2 (en) | 2018-12-28 | 2021-08-31 | Spin Memory, Inc. | Patterned silicide structures and methods of manufacture |

| JP7455511B2 (ja) * | 2019-02-25 | 2024-03-26 | Tdk株式会社 | 磁気センサ及びその製造方法 |

| CN112310273B (zh) * | 2019-07-29 | 2023-04-07 | 中电海康集团有限公司 | 磁性隧道结及其制备方法 |

| TWI814942B (zh) * | 2019-11-11 | 2023-09-11 | 聯華電子股份有限公司 | 半導體元件及其製作方法 |

| US11423929B1 (en) | 2020-08-25 | 2022-08-23 | Seagate Technology Llc | Reader with wide synthetic antiferromagnetic structure optimized for high stability and low noise |

| CN116998015A (zh) * | 2021-03-26 | 2023-11-03 | 索尼半导体解决方案公司 | 图像传感器和摄像装置 |

| EP4362626A1 (en) * | 2022-10-31 | 2024-05-01 | Commissariat à l'énergie atomique et aux énergies alternatives | Magnetic device and corresponding method |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5739990A (en) * | 1996-11-13 | 1998-04-14 | Read-Rite Corporation | Spin-valve GMR sensor with inbound exchange stabilization |

| US6139906A (en) * | 1999-10-07 | 2000-10-31 | Veeco Instruments, Inc. | Methods of depositing multilayer thin films |

| JP3607850B2 (ja) * | 2000-04-06 | 2005-01-05 | アルプス電気株式会社 | 磁気抵抗効果型薄膜磁気素子及びその製造方法と、その磁気抵抗効果型薄膜磁気素子を備えた薄膜磁気ヘッド |

| US7115119B2 (en) * | 2000-06-24 | 2006-10-03 | Precimed S.A. | Dual reamer holder for surgical use |

| JP2002074621A (ja) * | 2000-08-30 | 2002-03-15 | Alps Electric Co Ltd | スピンバルブ型薄膜磁気素子及び薄膜磁気ヘッド及び浮上式磁気ヘッド並びにスピンバルブ型薄膜磁気素子の製造方法 |

| US6888706B2 (en) * | 2001-08-08 | 2005-05-03 | Alps Electric Co., Ltd. | Magnetic sensing element having hard bias layer formed on bias underlayer and process for manufacturing the same |

| JP3971140B2 (ja) * | 2001-08-14 | 2007-09-05 | Tdk株式会社 | 磁気抵抗効果素子並びにこれを用いた磁気ヘッド及びヘッドサスペンションアセンブリ |

| US6914760B2 (en) * | 2001-09-07 | 2005-07-05 | International Business Machines Corporation | Hard bias layer for read heads |

| US7123451B2 (en) * | 2002-09-25 | 2006-10-17 | Tdk Corporation | Thin-film magnetic head for reading magnetic information on a hard disk by utilizing a magnetoresistance effect |

| JP4284049B2 (ja) | 2002-09-25 | 2009-06-24 | 株式会社日立グローバルストレージテクノロジーズ | 磁気抵抗効果センサー及び磁気抵抗効果型ヘッド及びその製造方法 |

| US7061731B2 (en) * | 2003-11-17 | 2006-06-13 | Seagate Technology Llc | High magnetic anisotropy hard magnetic bias element |

| US7161763B2 (en) * | 2004-02-18 | 2007-01-09 | Hitachi Global Storage Technologies Netherlands B.V. | GMR sensor with oriented hard bias stabilization |

| US7360300B2 (en) * | 2005-03-31 | 2008-04-22 | Hitachi Global Storage Technologies Netherlands B.V. | Method for manufacturing a magnetic read sensor employing oblique etched underlayers for inducing uniaxial magnetic anisotropy in a hard magnetic pinning layer |

| JP2007141381A (ja) * | 2005-11-18 | 2007-06-07 | Alps Electric Co Ltd | Cpp型薄膜磁気ヘッド及びその製造方法 |

| JP2007287239A (ja) * | 2006-04-17 | 2007-11-01 | Hitachi Global Storage Technologies Netherlands Bv | 磁気ヘッドとその形成方法 |

| US7804668B2 (en) * | 2006-11-16 | 2010-09-28 | Headway Technologies, Inc. | Enhanced hard bias in thin film magnetoresistive sensors with perpendicular easy axis growth of hard bias and strong shield-hard bias coupling |

| JP2008192832A (ja) * | 2007-02-05 | 2008-08-21 | Hitachi Global Storage Technologies Netherlands Bv | 磁気検出素子及びその製造方法 |

| JP2009087474A (ja) | 2007-09-29 | 2009-04-23 | Hitachi Global Storage Technologies Netherlands Bv | Cpp磁気リード・ヘッド及びその製造方法 |

-

2010

- 2010-06-30 JP JP2010149407A patent/JP5529648B2/ja active Active

- 2010-08-04 US US12/849,907 patent/US8810974B2/en active Active

- 2010-08-04 CN CN201010250345.4A patent/CN101989643B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN101989643A (zh) | 2011-03-23 |

| US8810974B2 (en) | 2014-08-19 |

| JP2011090759A (ja) | 2011-05-06 |

| US20110032645A1 (en) | 2011-02-10 |

| CN101989643B (zh) | 2014-09-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5529648B2 (ja) | 磁気センサ積層体、その成膜方法、成膜制御プログラムおよび記録媒体 | |

| JP5336591B2 (ja) | 磁気センサ積層体、その成膜方法、成膜制御プログラムおよび記録媒体 | |

| US8734620B2 (en) | Method of making a thin seeded Co/Ni multilayer film with perpendicular anisotropy for read head sensor stabilization | |

| JP3890893B2 (ja) | スピントンネル磁気抵抗効果膜及び素子及びそれを用いた磁気抵抗センサー、及び磁気装置及びその製造方法 | |

| JP4284049B2 (ja) | 磁気抵抗効果センサー及び磁気抵抗効果型ヘッド及びその製造方法 | |

| US8873204B1 (en) | Current-perpendicular-to-the-plane (CPP) magnetoresistive (MR) sensor structure with multiple stacked sensors and center shield with CoFeB insertion layer | |

| JP6100990B2 (ja) | 磁気抵抗効果センサおよびその製造方法 | |

| US8077435B1 (en) | Current perpendicular-to-plane read sensor with back shield | |

| JP3965358B2 (ja) | 磁気ヘッド | |

| KR100372984B1 (ko) | 자기저항효과형자기헤드및자기기록재생장치 | |

| JP5815204B2 (ja) | Tmr素子およびその形成方法 | |

| US9437225B2 (en) | Reader designs of shield to shield spacing improvement | |

| US6735058B2 (en) | Current-perpendicular-to-plane read head with an amorphous magnetic bottom shield layer and an amorphous nonmagnetic bottom lead layer | |

| JP2011090759A5 (ja) | ||

| US9679589B2 (en) | Magnetoresistive sensor with enhanced uniaxial anisotropy | |

| US20140133052A1 (en) | Magnetoresistive sensor having reduced read gap and strong pinned layer stability | |

| US7443636B2 (en) | Magnetic head having layered film with tilted crystalline grain structure | |

| JP2007281087A (ja) | 積層体、その製造方法及び磁気抵抗効果ヘッド | |

| JP2003318462A (ja) | 磁気抵抗効果素子とこれを用いた磁気ヘッドおよび磁気メモリ | |

| JP2011123944A (ja) | Tmrリード・ヘッドの製造方法及びtmr積層体 | |

| JP3488652B2 (ja) | 磁気抵抗効果膜及びその製造方法並びにそれを用いた磁気ヘッド | |

| US12094499B1 (en) | Cap layer able to be reactive ion etched for RSB DFL read elements | |

| JP3939519B2 (ja) | 磁気検出素子及びその製造方法 | |

| JP2006338719A (ja) | 磁気ヘッド | |

| JP2008084480A (ja) | 磁気ヘッド及びそれを備えた磁気記録装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130607 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130607 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131126 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131210 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140130 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140325 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140417 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5529648 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |