JP5505922B2 - メモリシステム及びその読み出し方法 - Google Patents

メモリシステム及びその読み出し方法 Download PDFInfo

- Publication number

- JP5505922B2 JP5505922B2 JP2008198333A JP2008198333A JP5505922B2 JP 5505922 B2 JP5505922 B2 JP 5505922B2 JP 2008198333 A JP2008198333 A JP 2008198333A JP 2008198333 A JP2008198333 A JP 2008198333A JP 5505922 B2 JP5505922 B2 JP 5505922B2

- Authority

- JP

- Japan

- Prior art keywords

- memory

- flash memory

- data

- read

- block

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000015654 memory Effects 0.000 title claims description 191

- 238000000034 method Methods 0.000 title claims description 28

- 239000000872 buffer Substances 0.000 claims description 10

- 238000010586 diagram Methods 0.000 description 7

- 238000012937 correction Methods 0.000 description 5

- 238000012545 processing Methods 0.000 description 5

- 238000001514 detection method Methods 0.000 description 4

- 230000008439 repair process Effects 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- RMFAWIUWXUCNQL-UHFFFAOYSA-N 1-[2-[[2-hydroxy-3-(3-methoxyphenoxy)propyl]amino]ethylamino]-3-(3-methoxyphenoxy)propan-2-ol;dihydrochloride Chemical compound Cl.Cl.COC1=CC=CC(OCC(O)CNCCNCC(O)COC=2C=C(OC)C=CC=2)=C1 RMFAWIUWXUCNQL-UHFFFAOYSA-N 0.000 description 1

- 101100481702 Arabidopsis thaliana TMK1 gene Proteins 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 125000004122 cyclic group Chemical group 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000009957 hemming Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 238000013519 translation Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/349—Arrangements for evaluating degradation, retention or wearout, e.g. by counting erase cycles

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

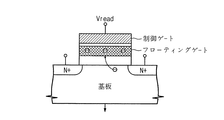

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3418—Disturbance prevention or evaluation; Refreshing of disturbed memory data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3418—Disturbance prevention or evaluation; Refreshing of disturbed memory data

- G11C16/3431—Circuits or methods to detect disturbed nonvolatile memory cells, e.g. which still read as programmed but with threshold less than the program verify threshold or read as erased but with threshold greater than the erase verify threshold, and to reverse the disturbance via a refreshing programming or erasing step

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Read Only Memory (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

Description

一実施形態において、前記読み出し回数の基準値はユーザによって設定されることを特徴とする。

一実施形態において、前記コピーバック動作を完了した後、前記回数をリセットすることを更に含む。

本発明の一実施形態において、前記フラッシュメモリ及び前記メモリコントローラはメモリカードに具現される。

一実施形態において、前記読み出し回数はラム内に格納される。

一実施形態において、前記メモリコントローラは、前記フラッシュメモリの電源がオフになる前に、前記ラムから前記フラッシュメモリ内に読み出し回数を格納する。

一実施形態において、前記メモリコントローラは、前記フラッシュメモリの電源がオンになる場合、前記フラッシュメモリから前記ラム内に読み出し回数を格納する。

本発明によるメモリシステム及びその読み出し方法は、メインページに対する反復的な読み出し動作によって他のページで発生するビットエラーによる読み出しエラーを防ぐ。

110 ホスト

120 メモリコントローラ

121 ホストインタフェース

122 フラッシュインタフェース

123 中央処理装置

124 ECC回路

125 ROM

126 RAM

130 フラッシュメモリ

131 第1ブロック

132 第2ブロック

133 カウントレコーダ

134 制御ユニット

Claims (10)

- フラッシュメモリを含むメモリシステムの読み出し方法であって、

前記メモリシステムは、該フラッシュメモリを制御するメモリコントローラを備え、

前記メモリコントローラは、前記フラッシュメモリの第1ブロック内の特定ページからデータを読み出し、

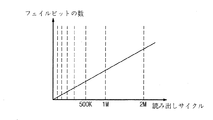

前記フラッシュメモリの前記特定ページ毎の読み出し回数を、前記特定ページからデータを読み出す毎に増加させ、

前記メモリコントローラは、バッファメモリから成り前記読み出し回数を格納する格納ユニットを含み、

前記読み出し回数が基準値より大きい場合、前記フラッシュメモリの第1ブロックから前記フラッシュメモリの第2ブロックにデータをコピーバックし、

前記第1ブロックからのデータは前記特定ページからのデータを含み、

前記メモリシステムの電源がオフになる前に、前記読み出し回数を前記フラッシュメモリ内の格納ユニットに格納し、

前記フラッシュメモリの電源がパワーオン(power on)時に前記データのコピーバックが行なわれることを特徴とする読み出し方法。 - 前記読み出し回数の基準値はユーザによって設定されることを特徴とする請求項1に記載の読み出し方法。

- 前記コピーバック動作を完了した後、前記回数をリセットすることを更に含むことを特徴とする請求項1に記載の読み出し方法。

- メモリシステムであって、

複数のページを有するフラッシュメモリと、

前記フラッシュメモリの動作を制御するためのメモリコントローラと、を備え、

前記メモリコントローラは、

前記フラッシュメモリの第1ブロック内の特定ページからデータを読み出し、前記フラッシュメモリの前記特定ページ毎の読み出し回数を、前記特定ページからデータを読み出す毎に増加させ、

前記メモリコントローラは、バッファメモリから成り前記読み出し回数を格納する格納ユニットを含み、

前記読み出し回数が基準値より大きい場合、前記フラッシュメモリの第1ブロックから前記フラッシュメモリの第2ブロック内にデータをコピーバックし、前記第1ブロックからのデータは前記特定ページのデータを含み、

前記メモリシステムの電源がオフになる前に、前記読み出し回数を前記フラッシュメモリ内の格納ユニットに格納し、

前記メモリコントローラは、前記フラッシュメモリの電源がパワーオン(power on)時にコピーバック動作を実行することを特徴とするメモリシステム。 - 前記読み出し回数の基準値はユーザによって設定されることを特徴とする請求項4に記載のメモリシステム。

- 前記メモリコントローラは、前記コピーバック動作を完了した後、前記ページの読み出し回数をリセットすることを特徴とする請求項4に記載のメモリシステム。

- 前記フラッシュメモリ及び前記メモリコントローラはメモリカードに具現されることを特徴とする請求項4に記載のメモリシステム。

- 前記読み出し回数はラム内に格納されることを特徴とする請求項4に記載のメモリシステム。

- 前記メモリコントローラは、前記フラッシュメモリの電源がオフになる前に、前記ラムから前記フラッシュメモリ内に読み出し回数を格納することを特徴とする請求項8に記載のメモリシステム。

- 前記メモリコントローラは、前記フラッシュメモリの電源がオンになる場合、前記フラッシュメモリから前記ラム内に読み出し回数を格納することを特徴とする請求項8に記載のメモリシステム。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2007-0078262 | 2007-08-03 | ||

| KR1020070078262A KR20090014036A (ko) | 2007-08-03 | 2007-08-03 | 읽기 디스터번스로 인한 에러를 방지하는 메모리 시스템 및그 방법 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009037619A JP2009037619A (ja) | 2009-02-19 |

| JP2009037619A5 JP2009037619A5 (ja) | 2011-09-15 |

| JP5505922B2 true JP5505922B2 (ja) | 2014-05-28 |

Family

ID=40337962

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008198333A Active JP5505922B2 (ja) | 2007-08-03 | 2008-07-31 | メモリシステム及びその読み出し方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US7751238B2 (ja) |

| JP (1) | JP5505922B2 (ja) |

| KR (1) | KR20090014036A (ja) |

Families Citing this family (41)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4776307B2 (ja) * | 2005-08-31 | 2011-09-21 | 株式会社日立製作所 | ストレージシステム、データ転送方法及びプログラム |

| KR100882841B1 (ko) * | 2007-06-19 | 2009-02-10 | 삼성전자주식회사 | 읽기 디스터번스로 인한 비트 에러를 검출할 수 있는메모리 시스템 및 그것의 읽기 방법 |

| US9471418B2 (en) * | 2007-06-19 | 2016-10-18 | Samsung Electronics Co., Ltd. | Memory system that detects bit errors due to read disturbance and methods thereof |

| KR20090014036A (ko) * | 2007-08-03 | 2009-02-06 | 삼성전자주식회사 | 읽기 디스터번스로 인한 에러를 방지하는 메모리 시스템 및그 방법 |

| EP2077559B1 (en) * | 2007-12-27 | 2012-11-07 | Hagiwara Solutions Co., Ltd. | Refresh method of a flash memory |

| US8031521B1 (en) * | 2008-05-20 | 2011-10-04 | Marvell International Ltd. | Reprogramming non-volatile memory devices for read disturbance mitigation |

| KR101609367B1 (ko) | 2009-06-29 | 2016-04-20 | 삼성전자주식회사 | 플래시 메모리 시스템 및 플래시 메모리의 프로그래밍 방법 |

| JP4703753B2 (ja) * | 2009-09-30 | 2011-06-15 | 株式会社東芝 | 情報処理装置、半導体記憶装置、及びプログラム |

| US9324440B2 (en) | 2010-02-09 | 2016-04-26 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, operating methods thereof and memory systems including the same |

| KR101691088B1 (ko) | 2010-02-17 | 2016-12-29 | 삼성전자주식회사 | 불휘발성 메모리 장치, 그것의 동작 방법, 그리고 그것을 포함하는 메모리 시스템 |

| KR101691092B1 (ko) | 2010-08-26 | 2016-12-30 | 삼성전자주식회사 | 불휘발성 메모리 장치, 그것의 동작 방법, 그리고 그것을 포함하는 메모리 시스템 |

| KR101658479B1 (ko) * | 2010-02-09 | 2016-09-21 | 삼성전자주식회사 | 불휘발성 메모리 장치, 그것의 동작 방법, 그리고 그것을 포함하는 메모리 시스템 |

| US9378831B2 (en) | 2010-02-09 | 2016-06-28 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, operating methods thereof and memory systems including the same |

| US8908431B2 (en) | 2010-02-17 | 2014-12-09 | Samsung Electronics Co., Ltd. | Control method of nonvolatile memory device |

| JP5788183B2 (ja) | 2010-02-17 | 2015-09-30 | 三星電子株式会社Samsung Electronics Co.,Ltd. | 不揮発性メモリ装置、それの動作方法、そしてそれを含むメモリシステム |

| US8923060B2 (en) | 2010-02-17 | 2014-12-30 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices and operating methods thereof |

| JP2011170956A (ja) | 2010-02-18 | 2011-09-01 | Samsung Electronics Co Ltd | 不揮発性メモリ装置およびそのプログラム方法と、それを含むメモリシステム |

| US8792282B2 (en) | 2010-03-04 | 2014-07-29 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, memory systems and computing systems |

| JP5523379B2 (ja) * | 2010-03-18 | 2014-06-18 | 京セラドキュメントソリューションズ株式会社 | 記憶制御装置、画像形成装置および記憶制御方法 |

| CN103065678B (zh) * | 2011-10-21 | 2016-01-13 | 点序科技股份有限公司 | 闪速存储器装置及其数据储存方法 |

| KR20130136343A (ko) * | 2012-06-04 | 2013-12-12 | 에스케이하이닉스 주식회사 | 반도체 장치 및 그 동작 방법 |

| KR102025263B1 (ko) | 2012-10-05 | 2019-09-25 | 삼성전자주식회사 | 메모리 시스템 및 그것의 읽기 교정 방법 |

| KR20140045168A (ko) | 2012-10-08 | 2014-04-16 | 삼성전자주식회사 | 불휘발성 메모리 장치, 메모리 시스템 및 불휘발성 메모리 장치의 동작방법 |

| KR101379883B1 (ko) * | 2012-11-06 | 2014-04-01 | 한국과학기술원 | 플래시 메모리의 소모 전력 감소 방법 및 그 장치 |

| KR102025193B1 (ko) * | 2013-02-19 | 2019-09-25 | 삼성전자주식회사 | 메모리 컨트롤러 및 그것의 동작 방법, 메모리 컨트롤러를 포함하는 메모리 시스템 |

| JP2016522513A (ja) * | 2013-06-25 | 2016-07-28 | マイクロン テクノロジー, インク. | オンデマンドブロック管理 |

| KR102164630B1 (ko) | 2013-06-28 | 2020-10-12 | 삼성전자주식회사 | 메모리 컨트롤러 및 상기 메모리 컨트롤러의 동작 방법 |

| TWI509624B (zh) | 2013-07-01 | 2015-11-21 | Asolid Technology Co Ltd | 快閃記憶體裝置、記憶體控制器及快閃記憶體的控制方法 |

| KR102242022B1 (ko) | 2013-09-16 | 2021-04-21 | 삼성전자주식회사 | 불휘발성 메모리 및 그것의 프로그램 방법 |

| US9230689B2 (en) | 2014-03-17 | 2016-01-05 | Sandisk Technologies Inc. | Finding read disturbs on non-volatile memories |

| KR102530905B1 (ko) | 2016-02-15 | 2023-05-11 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 그의 동작 방법 |

| KR102606490B1 (ko) | 2016-06-30 | 2023-11-30 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 컨트롤러를 포함하는 스토리지 장치 |

| US10204693B2 (en) * | 2016-12-31 | 2019-02-12 | Western Digital Technologies, Inc. | Retiring computer memory blocks |

| KR20190017550A (ko) | 2017-08-11 | 2019-02-20 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 메모리 시스템의 동작 방법 |

| JP6884675B2 (ja) * | 2017-09-20 | 2021-06-09 | 株式会社東芝 | ビデオサーバ、及び放送システム |

| KR102653843B1 (ko) | 2018-04-19 | 2024-04-02 | 에스케이하이닉스 주식회사 | 데이터 저장 장치 및 이의 리드 디스터번스 방지 방법, 이를 이용한 스토리지 시스템 |

| US10656995B2 (en) * | 2018-10-03 | 2020-05-19 | Micron Technology, Inc. | Copy-back operations in a memory device |

| US10592351B1 (en) * | 2018-10-16 | 2020-03-17 | EMC IP Holding Company LLC | Data restore process using a probability distribution model for efficient caching of data |

| KR20200043054A (ko) | 2018-10-17 | 2020-04-27 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 그것의 동작방법 |

| US11287998B2 (en) * | 2019-08-02 | 2022-03-29 | Micron Technology, Inc. | Read count scaling factor for data integrity scan |

| KR20210030599A (ko) * | 2019-09-10 | 2021-03-18 | 에스케이하이닉스 주식회사 | 데이터를 분산 리드할 수 있는 메모리 시스템 및 메모리 시스템의 동작방법 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8027194B2 (en) * | 1988-06-13 | 2011-09-27 | Samsung Electronics Co., Ltd. | Memory system and method of accessing a semiconductor memory device |

| JPH06110793A (ja) * | 1992-09-30 | 1994-04-22 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP3176019B2 (ja) * | 1995-04-05 | 2001-06-11 | 株式会社東芝 | 不揮発性半導体記憶部を含む記憶システム |

| US7318117B2 (en) * | 2004-02-26 | 2008-01-08 | Super Talent Electronics, Inc. | Managing flash memory including recycling obsolete sectors |

| JP2003007051A (ja) | 2001-06-27 | 2003-01-10 | Sanyo Electric Co Ltd | メモリおよびその動作方法 |

| JP4113423B2 (ja) | 2002-12-04 | 2008-07-09 | シャープ株式会社 | 半導体記憶装置及びリファレンスセルの補正方法 |

| JP2006113648A (ja) * | 2004-10-12 | 2006-04-27 | Hitachi Ltd | ディスクアレイ装置 |

| US8010764B2 (en) * | 2005-07-07 | 2011-08-30 | International Business Machines Corporation | Method and system for decreasing power consumption in memory arrays having usage-driven power management |

| JP2007048191A (ja) * | 2005-08-12 | 2007-02-22 | Renesas Technology Corp | メモリカード |

| JP4776307B2 (ja) * | 2005-08-31 | 2011-09-21 | 株式会社日立製作所 | ストレージシステム、データ転送方法及びプログラム |

| JP4597829B2 (ja) | 2005-09-27 | 2010-12-15 | パトレネラ キャピタル リミテッド, エルエルシー | メモリ |

| US20070115960A1 (en) * | 2005-11-04 | 2007-05-24 | Mediatek Inc. | De-interleaver for data decoding |

| TWI350448B (en) * | 2006-12-13 | 2011-10-11 | Compal Electronics Inc | Method for data preservation |

| KR20090014036A (ko) * | 2007-08-03 | 2009-02-06 | 삼성전자주식회사 | 읽기 디스터번스로 인한 에러를 방지하는 메모리 시스템 및그 방법 |

-

2007

- 2007-08-03 KR KR1020070078262A patent/KR20090014036A/ko not_active Application Discontinuation

-

2008

- 2008-07-29 US US12/181,408 patent/US7751238B2/en active Active

- 2008-07-31 JP JP2008198333A patent/JP5505922B2/ja active Active

-

2010

- 2010-06-01 US US12/791,077 patent/US8125825B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009037619A (ja) | 2009-02-19 |

| US20090034328A1 (en) | 2009-02-05 |

| US8125825B2 (en) | 2012-02-28 |

| KR20090014036A (ko) | 2009-02-06 |

| US20100241796A1 (en) | 2010-09-23 |

| US7751238B2 (en) | 2010-07-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5505922B2 (ja) | メモリシステム及びその読み出し方法 | |

| KR100882841B1 (ko) | 읽기 디스터번스로 인한 비트 에러를 검출할 수 있는메모리 시스템 및 그것의 읽기 방법 | |

| KR102065665B1 (ko) | 더미 워드라인을 포함하는 불휘발성 메모리 장치, 메모리 시스템 및 메모리 시스템의 동작방법 | |

| JP5138319B2 (ja) | メモリーシステム及び該動作方法。 | |

| KR101944793B1 (ko) | 플래시 메모리를 포함하는 플래시 메모리 시스템 및 그것의 비정상 워드 라인 검출 방법 | |

| US10643715B2 (en) | Semiconductor memory device and memory system configured to perform tracking read on first memory cells followed by shift read on second memory cells using read voltage correction value determined during the tracking read | |

| KR101491829B1 (ko) | 읽기 디스터번스를 방지하는 메모리 장치 및 그 방법 | |

| US9471418B2 (en) | Memory system that detects bit errors due to read disturbance and methods thereof | |

| KR101967368B1 (ko) | 반도체 메모리 장치 및 이의 동작 방법 | |

| KR20150046549A (ko) | 데이터 저장 시스템 및 그것의 동작 방법 | |

| US20120106247A1 (en) | Flash memory device including flag cells and method of programming the same | |

| KR20180027276A (ko) | 반도체 메모리 장치 및 그 동작 방법 | |

| US9152497B2 (en) | Data recovery from blocks with gate shorts | |

| KR101678888B1 (ko) | 비휘발성 메모리 장치의 데이터 판독 방법 | |

| KR20140079913A (ko) | 불휘발성 메모리 장치 및 이의 프로그램 방법 | |

| US11216208B1 (en) | Memory system, memory controller, and operation method of memory system | |

| US11061615B2 (en) | Memory system, memory controller and operating method thereof | |

| US10937511B2 (en) | Semiconductor memory device, memory system including controller, and method of operating controller | |

| KR20150029401A (ko) | 데이터 저장 시스템 및 그것의 동작 방법 | |

| US11307794B2 (en) | Memory system, memory controller, and operation method of memory system | |

| US20230195367A1 (en) | Memory system, memory controller, and operation method of memory system | |

| US11495319B2 (en) | Memory system, memory controller, and method for operating memory system performing integrity check operation on target code when voltage drop is detected |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110801 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110801 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130321 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130402 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130702 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130730 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131129 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20131218 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140218 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140312 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5505922 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |