JP5475665B2 - フラッシュメモリのクロスカップリング事後補正 - Google Patents

フラッシュメモリのクロスカップリング事後補正 Download PDFInfo

- Publication number

- JP5475665B2 JP5475665B2 JP2010526419A JP2010526419A JP5475665B2 JP 5475665 B2 JP5475665 B2 JP 5475665B2 JP 2010526419 A JP2010526419 A JP 2010526419A JP 2010526419 A JP2010526419 A JP 2010526419A JP 5475665 B2 JP5475665 B2 JP 5475665B2

- Authority

- JP

- Japan

- Prior art keywords

- cell

- cells

- data

- value

- reading

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000006880 cross-coupling reaction Methods 0.000 title description 77

- 238000012937 correction Methods 0.000 title description 12

- 238000000034 method Methods 0.000 claims description 47

- 238000004364 calculation method Methods 0.000 claims description 19

- 238000005259 measurement Methods 0.000 claims description 19

- 238000009826 distribution Methods 0.000 claims description 18

- 238000003860 storage Methods 0.000 claims description 11

- 230000007246 mechanism Effects 0.000 claims description 7

- 230000000704 physical effect Effects 0.000 claims description 5

- 238000007667 floating Methods 0.000 description 23

- 238000010168 coupling process Methods 0.000 description 11

- 238000005859 coupling reaction Methods 0.000 description 11

- 238000004891 communication Methods 0.000 description 10

- 230000008878 coupling Effects 0.000 description 10

- 238000004519 manufacturing process Methods 0.000 description 10

- 238000013461 design Methods 0.000 description 9

- 230000003044 adaptive effect Effects 0.000 description 8

- 238000007476 Maximum Likelihood Methods 0.000 description 7

- 238000010586 diagram Methods 0.000 description 6

- 238000005516 engineering process Methods 0.000 description 5

- 230000008859 change Effects 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- 230000003111 delayed effect Effects 0.000 description 2

- 238000001514 detection method Methods 0.000 description 2

- 238000005562 fading Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 238000012552 review Methods 0.000 description 2

- DEXFNLNNUZKHNO-UHFFFAOYSA-N 6-[3-[4-[2-(2,3-dihydro-1H-inden-2-ylamino)pyrimidin-5-yl]piperidin-1-yl]-3-oxopropyl]-3H-1,3-benzoxazol-2-one Chemical compound C1C(CC2=CC=CC=C12)NC1=NC=C(C=N1)C1CCN(CC1)C(CCC1=CC2=C(NC(O2)=O)C=C1)=O DEXFNLNNUZKHNO-UHFFFAOYSA-N 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical group [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000001808 coupling effect Effects 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 238000007726 management method Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000013598 vector Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5642—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3418—Disturbance prevention or evaluation; Refreshing of disturbed memory data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/563—Multilevel memory reading aspects

- G11C2211/5634—Reference cells

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Read Only Memory (AREA)

Description

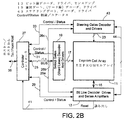

フラッシュメモリデバイスを制御するコマンドデータは、外部制御線へ接続されたコマンドインターフェイスへ入力される。外部制御線はコントローラ20に接続される。コマンドデータは要求された操作が何かをフラッシュメモリに伝える。入力コマンドは状態マシン8へ転送され、状態マシン8は、列制御回路2、行制御回路3、cソース制御回路4、c−pウェル制御回路5、およびデータ入出力回路6を制御する。READY/BUSY、PASS/FAIL等、状態マシン8はフラッシュメモリのステータスデータを出力できる。

フローティングゲート間結合の補償にあたっては数通りのアプローチが知られている。ChenとFongによるフラッシュメモリでは、フローティングゲートが結合しないようにセルが互いに物理的に隔離される。ChenとFongはまた、フローティングゲート間結合を補償するように比較基準電圧(例えば、図1BのV1、V2 )を調整する。あらゆる目的のためにあたかもその全体が本願明細書において参照により援用されている、Chen、Cernea、およびHemnikは米国特許第7,196,946号(特許文献5)で類似する方法を教示している。フラッシュメモリからのデータ読み出しにあたっては、蓄積されるデータのエラー補正符号化とその後に続く、読み出されたデータのエラー補正復号化によって不正確さを補償するのが一般的だが、これはフローティングゲート間結合の補償にもなる。

算出と同様、推定はMMSE、MAP、ML等の基準に基づく。

ここでは例証のみを目的として添付の図面を参照しながら本発明を説明する。

s0iの和は、ビットiが「0」ビットになっている状態sの和である。s1iの和は、残りの状態の和、すなわちビットiが「1」ビットになっている状態sの和である。例えば、図4のように状態がしきい値電圧に対応付けられる1セル当たり3ビットのフラッシュメモリで、左端のビットの場合、分子の和は右端の4つの状態の和であり、分母の和は左端の4つの状態の和であり、中間のビットの場合、分子の和は左から3番目と4番目の状態と右から1番目と2番目の状態の和であり、分母の和は左から1番目と2番目の状態と右から3番目と4番目の状態の和であり、右端のビットの場合、分子の和は左から2番目と4番目の状態と右から1番目と3番目の状態の和であり、分母の和は左から1番目と3番目の状態と右から2番目と4番目の状態の和である。

式11または式12を使って計算されるLi は、ビットiを含む符号語の推定にあたってECCデコーダへの入力として使用できる。

本発明のこの態様では、式(3)から(7)、(9)、および(10)の二次統計計算がLMMSEクロスカップリング推定であり、式(11)または式(12)におけるLiの計算がLMMSE等化である。

符号付きLMS (Simon Haykin, Adaptive Filter Theory, Third Edition, Prentice Hall,1996; R. D. Gitlin et al., An algorithm for the stable operation of a digitally implemented fractionally spaced adaptive equalizer, Proc. IEEE Int. Conf. Acoust. Speech Signal Process., May 1982, pp. 1379-1382(非特許文献3))

CMAアルゴリズム (R. Johnson, Jr., et al., Blind equalization using the constant modulus criterion: a review, Proc. IEEE vol. 86 no. 10 (1998) pp. 1927-1950(非特許文献4))

SATOアルゴリズム (Y. Sato, A method for self-recovering equalization for multilevel amplitude modulation system, IEEE Trans. Commun. vol. COM-23 (June 1975) pp.679-682 (非特許文献5))

Godardアルゴリズム (D. N. Godard, Self-recovering equalization and carrier tracking in two-dimensional data communication system, IEEE Trans. Commun. vol. COM-28 (Nov. 1980) pp. 1867-1875 (非特許文献6))

SUNUAアルゴリズム (Ching-Hsiang Tseng and Cheng-bin Lin, A stop-and-go dual-mode algorithm for blind equalization, GLOBECOM '96 (18-22 November 1996) vol. 2 pp. 1427-1431 (非特許文献7))

DMGSAアルゴリズム (V. Weerackody and S. A. Kassam, Dual-mode type algorithms for blind equalization, IEEE Trans. Commun. vol. 42 no. 1 (1994) pp. 22-28(非特許文献8))

RRSEアルゴリズム (Nigel C. McGinty and Rodney A. Kennedy, Reduced-state sequence estimator with reverse-time structure, IEEE Trans. Commun. vol. 45 no. 3 (1997) pp. 265-268(非特許文献10))

DDFSEアルゴリズム (Alexanra Duel-Hallen and Chris Heegard, Delayed decision-feedback sequence estimation, IEEE Trans. Commun. vol. 37 no. 5 (1989) pp. 428-436 (非特許文献11))

DFEアルゴリズム (Mikael Sternad et al., Robust decision feedback equalizers, IEEE Int. Conf. Acoustics, Speech and Signal Processing (April 27-30, 1993) vol. 3 pp. 555-558(非特許文献12))

なお、これらのMLアルゴリズムは非線形アルゴリズムである。

1.設計

2.製造

3.バックグラウンド

4.オンザフライ

クロスカップリング係数がかなり速やかに変化するためにバックグラウンドクロスカップリング推定では頼りにならない場合は、ワード線が読み出されるときに等化とともにクロスカップリング推定を行う。目標ワード線が読み出されるときには、近傍セルを含む全てのワード線(通常はもう1つのワード線のみ)も読み出されなければならないことに留意するべきである。

Claims (12)

- データを蓄積しかつ読み出す方法であって、

(a)複数のセル(151〜159)を含むメモリ(1;11;62)を提供するステップであって、データを表すセル(151〜159)の物理的特性の各値を設定することにより前記セル(151〜159)にデータを蓄積し、その後、各値の測定値を得るために各値を測定することにより前記セル(151〜159)を読み出すステップと、

(b)前記セルのいずれか1セル(151)と、前記1セル(151)の少なくとも1つの近傍セル(152〜159)とを読み出し、これにより前記1セル(151)と前記近傍セル(152〜159)の各測定値を得るステップと、

(c)各近傍セル(152〜159)が前記1セル(151)の読み出しを妨害するそれぞれの程度を算出するステップであって、前記算出するステップは前記妨害の線形または非線形モデルに基づくステップと、

(d)各測定値と、各近傍セル(152〜159)が前記1セル(151)の読み出しを妨害する前記算出されたそれぞれの程度とに基づき、データが前記1セル(151)に蓄積された時に設定された前記データの物理的特性の各値を推定するステップであって、前記推定するステップは各測定値の再設定を含まない計算であるステップと、

を含む方法。 - 請求項1記載の方法において、

前記セル(151〜159)は、フラッシュセル(151〜159)であり、

前記物理的特性は、前記フラッシュセル(151〜159)のしきい値電圧である方法。 - 請求項1記載の方法において、

前記算出するステップは、

前記推定するステップとは別に遂行されるか、あるいは

前記推定するステップとともに繰り返し遂行される方法。 - 請求項1記載の方法において、

(e)前記1セルと少なくとも1つの近傍セルとは別の少なくとも1つのさらなるセル(152〜159)を読み出し、これにより少なくとも1つのさらなる測定値を得るステップをさらに含み、

前記算出するステップは、前記少なくとも1つのさらなる測定値にも基づく方法。 - 請求項4記載の方法において、

前記メモリ(1;11;62)は、フラッシュメモリであり、

前記1セル(151)と少なくとも1つのさらなるセル(152〜159)は、前記メモリ(1;11;62)の同じ消去ブロックにある方法。 - 請求項5記載の方法において、

前記1セル(151)と少なくとも1つのさらなるセル(152〜159)は、前記メモリ(1;11;62)の同じワード線にある方法。 - 請求項1記載の方法において、

(e)前記1セル(151)と少なくとも1つの各近傍セル(152〜159)とにデータを蓄積するステップをさらに含む方法。 - 請求項7記載の方法において、

前記算出するステップは、

前記蓄積するステップの前に遂行されるか、

前記蓄積するステップの後に遂行されるか、あるいは

前記1セル(151)が読み出されるたびに遂行される方法。 - 請求項1記載の方法において、

前記推定するステップは、

少なくとも1つの近傍セル(152〜159)による妨害のために前記1セル(151)の各測定値を補正することと、

前記1セル(151)の各値の分布のパラメータの少なくとも1つの期待値を推定することと、

を含む方法。 - メモリデバイスであって、

(a)複数のセル(151〜159)を含むメモリ(1;11;62)と、

(b)回路(2〜8,20〜22;13,15,17,19,23,25,26a〜26c,27,29,31,33,35,41,43,44)であって、

(i)データを表すセル(151〜159)の物理的特性の各値を設定することにより前記セル(151〜159)にデータを蓄積し、かつ

(ii)その後、各値の測定値を得るために各値を測定することにより前記セル(151〜159)を読み出す回路と、

(c)前記セルのいずれか1セル(151)の各測定値と、前記1セル(151)の少なくとも1つの近傍セル(152〜159)の各測定値とに基づき、かつ各近傍セル(152〜159)が前記1セル(151)の読み出しを妨害するそれぞれの程度に基づき、データが前記1セル(151)に蓄積された時に設定された前記データの物理的特性の各値を、各測定値を再設定することなく、推定する機構であって、各近傍セル(152〜159)が前記1セル(151)の読み出しを妨害するそれぞれの程度を、前記妨害の線形または非線形モデルに基づき算出するように構成される機構と、

を備えるメモリデバイス。 - 請求項10記載のメモリデバイスにおいて、

前記推定する機構は、

前記セルのいずれか1セル(151)の各測定値と、前記1セルの少なくとも1つの近傍セル(152〜159)の各測定値とに基づき、かつ各近傍セル(152〜159)が前記1セル(151)の読み出しを妨害するそれぞれの程度に基づき、前記1セル(151)に蓄積されたデータを推定するコードを含む、前記メモリデバイスのためのドライバコードを蓄積する不揮発性メモリと、

前記コードを実行するプロセッサと、

を備えるメモリデバイス。 - 請求項1〜9のいずれか記載の方法によって規定されたプログラム命令を組み入れたコンピュータ可読蓄積媒体。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/860,553 US7751237B2 (en) | 2007-09-25 | 2007-09-25 | Post-facto correction for cross coupling in a flash memory |

| US11/860,553 | 2007-09-25 | ||

| PCT/IL2008/000855 WO2009040784A1 (en) | 2007-09-25 | 2008-06-23 | Post-facto correction for cross coupling in a flash memory |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010541119A JP2010541119A (ja) | 2010-12-24 |

| JP2010541119A5 JP2010541119A5 (ja) | 2011-08-11 |

| JP5475665B2 true JP5475665B2 (ja) | 2014-04-16 |

Family

ID=39828999

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010526419A Active JP5475665B2 (ja) | 2007-09-25 | 2008-06-23 | フラッシュメモリのクロスカップリング事後補正 |

Country Status (6)

| Country | Link |

|---|---|

| US (3) | US7751237B2 (ja) |

| EP (1) | EP2201572B1 (ja) |

| JP (1) | JP5475665B2 (ja) |

| KR (1) | KR101426063B1 (ja) |

| TW (1) | TWI463499B (ja) |

| WO (1) | WO2009040784A1 (ja) |

Families Citing this family (48)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20090097673A (ko) * | 2008-03-12 | 2009-09-16 | 삼성전자주식회사 | 연판정 값에 기반하여 메모리에 저장된 데이터를 검출하는장치 |

| US8185787B1 (en) * | 2008-04-09 | 2012-05-22 | Link—A—Media Devices Corporation | Blind and decision directed multi-level channel estimation |

| US8458563B2 (en) * | 2008-06-23 | 2013-06-04 | Ramot At Tel Aviv University Ltd. | Reading a flash memory by joint decoding and cell voltage distribution tracking |

| US8464131B2 (en) * | 2008-06-23 | 2013-06-11 | Ramot At Tel Aviv University Ltd. | Reading a flash memory by constrained decoding |

| US8406048B2 (en) | 2008-08-08 | 2013-03-26 | Marvell World Trade Ltd. | Accessing memory using fractional reference voltages |

| TW201019327A (en) * | 2008-09-30 | 2010-05-16 | Lsi Corp | Methods and apparatus for soft data generation for memory devices using reference cells |

| KR101484556B1 (ko) * | 2008-10-28 | 2015-01-20 | 삼성전자주식회사 | 독출 보상 회로 |

| US7995387B2 (en) * | 2009-01-30 | 2011-08-09 | Sandisk Il Ltd. | System and method to read data subject to a disturb condition |

| US8374026B2 (en) * | 2009-01-30 | 2013-02-12 | Sandisk Il Ltd. | System and method of reading data using a reliability measure |

| TWI412036B (zh) * | 2009-07-22 | 2013-10-11 | Silicon Motion Inc | 資料讀取的方法及資料儲存裝置 |

| KR101678909B1 (ko) * | 2009-09-17 | 2016-11-23 | 삼성전자주식회사 | 플래시 메모리 시스템 및 그것의 소거 리프레쉬 방법 |

| US7990767B2 (en) * | 2009-12-30 | 2011-08-02 | Sandisk Il Ltd. | Flash memory system having cross-coupling compensation during read operation |

| US8213255B2 (en) | 2010-02-19 | 2012-07-03 | Sandisk Technologies Inc. | Non-volatile storage with temperature compensation based on neighbor state information |

| KR101658619B1 (ko) * | 2010-04-27 | 2016-09-23 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치의 소거 방법 |

| TWI455132B (zh) * | 2010-06-23 | 2014-10-01 | Phison Electronics Corp | 資料讀取方法、控制電路與記憶體控制器 |

| US8531888B2 (en) | 2010-07-07 | 2013-09-10 | Marvell World Trade Ltd. | Determining optimal reference voltages for progressive reads in flash memory systems |

| US8627175B2 (en) | 2010-09-27 | 2014-01-07 | Seagate Technology Llc | Opportunistic decoding in memory systems |

| US8243511B2 (en) | 2010-09-27 | 2012-08-14 | Seagate Technology Llc | Reuse of information from memory read operations |

| US8879317B2 (en) | 2011-03-01 | 2014-11-04 | Sandisk Technologies Inc. | System and method of decoding data from memory based on sensing information and decoded data of neighboring storage elements |

| US9076547B2 (en) | 2012-04-05 | 2015-07-07 | Micron Technology, Inc. | Level compensation in multilevel memory |

| US9030870B2 (en) | 2011-08-26 | 2015-05-12 | Micron Technology, Inc. | Threshold voltage compensation in a multilevel memory |

| KR101919902B1 (ko) | 2011-10-18 | 2018-11-20 | 삼성전자 주식회사 | 메모리 장치의 데이터 독출 방법 |

| US8760932B2 (en) | 2011-10-18 | 2014-06-24 | Seagate Technology Llc | Determination of memory read reference and programming voltages |

| US8711619B2 (en) | 2011-10-18 | 2014-04-29 | Seagate Technology Llc | Categorizing bit errors of solid-state, non-volatile memory |

| US8737133B2 (en) | 2011-10-18 | 2014-05-27 | Seagate Technology Llc | Shifting cell voltage based on grouping of solid-state, non-volatile memory cells |

| US8693257B2 (en) | 2011-10-18 | 2014-04-08 | Seagate Technology Llc | Determining optimal read reference and programming voltages for non-volatile memory using mutual information |

| US8913437B2 (en) * | 2011-12-15 | 2014-12-16 | Marvell World Trade Ltd. | Inter-cell interference cancellation |

| US8811076B2 (en) | 2012-07-30 | 2014-08-19 | Sandisk Technologies Inc. | Systems and methods of updating read voltages |

| US8874992B2 (en) * | 2012-08-31 | 2014-10-28 | Sandisk Technologies Inc. | Systems and methods to initiate updating of reference voltages |

| WO2014113726A1 (en) * | 2013-01-17 | 2014-07-24 | University Of Hawaii | Estimation of memory data |

| KR102089532B1 (ko) | 2013-02-06 | 2020-03-16 | 삼성전자주식회사 | 메모리 컨트롤러, 메모리 시스템 및 메모리 시스템의 동작 방법 |

| US9129711B2 (en) | 2013-02-28 | 2015-09-08 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| US9135109B2 (en) | 2013-03-11 | 2015-09-15 | Seagate Technology Llc | Determination of optimum threshold voltage to read data values in memory cells |

| US9147490B2 (en) | 2013-03-15 | 2015-09-29 | Sandisk Technologies Inc. | System and method of determining reading voltages of a data storage device |

| KR102114230B1 (ko) * | 2013-10-07 | 2020-05-25 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 이의 동작 방법 |

| US9859925B2 (en) | 2013-12-13 | 2018-01-02 | Empire Technology Development Llc | Low-complexity flash memory data-encoding techniques using simplified belief propagation |

| US9934867B2 (en) | 2014-01-06 | 2018-04-03 | Seagate Technology Llc | Capacitance coupling parameter estimation in flash memories |

| KR102190241B1 (ko) | 2014-07-31 | 2020-12-14 | 삼성전자주식회사 | 메모리 컨트롤러의 동작 방법 및 불휘발성 메모리 시스템 |

| KR102318561B1 (ko) | 2014-08-19 | 2021-11-01 | 삼성전자주식회사 | 스토리지 장치, 스토리지 장치의 동작 방법 |

| US9406377B2 (en) | 2014-12-08 | 2016-08-02 | Sandisk Technologies Llc | Rewritable multibit non-volatile memory with soft decode optimization |

| US10204043B2 (en) | 2016-03-08 | 2019-02-12 | Toshiba Memory Corporation | Memory controller, method of controlling nonvolatile memory and memory system |

| US9761308B1 (en) | 2016-03-11 | 2017-09-12 | Western Digital Technologies, Inc. | Systems and methods for adaptive read level adjustment |

| WO2020170041A1 (en) * | 2019-02-20 | 2020-08-27 | Marvell Asia Pte, Ltd. | Decoding of high-density memory cells in a solid-state drive |

| US11557350B2 (en) * | 2020-10-16 | 2023-01-17 | Western Digital Technologies, Inc. | Dynamic read threshold calibration |

| US11393540B2 (en) | 2020-10-26 | 2022-07-19 | Western Digital Technologies, Inc. | Adjacent memory cell interference mitigation |

| US11342033B1 (en) | 2020-12-28 | 2022-05-24 | Sandisk Technologies Llc | Look neighbor ahead for data recovery |

| US11854631B2 (en) | 2021-08-19 | 2023-12-26 | Kioxia Corporation | System and method for dynamic compensation for multiple interference sources in non-volatile memory storage devices |

| US11513887B1 (en) | 2021-08-23 | 2022-11-29 | Apple Inc. | Cancelation of cross-coupling interference among memory cells |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5268870A (en) | 1988-06-08 | 1993-12-07 | Eliyahou Harari | Flash EEPROM system and intelligent programming and erasing methods therefor |

| US5867429A (en) * | 1997-11-19 | 1999-02-02 | Sandisk Corporation | High density non-volatile flash memory without adverse effects of electric field coupling between adjacent floating gates |

| US6295326B1 (en) | 1999-03-08 | 2001-09-25 | Bandspeed, Inc. | Kalman filter based equalization for digital multicarrier communications systems |

| US6522580B2 (en) | 2001-06-27 | 2003-02-18 | Sandisk Corporation | Operating techniques for reducing effects of coupling between storage elements of a non-volatile memory operated in multiple data states |

| US6751766B2 (en) | 2002-05-20 | 2004-06-15 | Sandisk Corporation | Increasing the effectiveness of error correction codes and operating multi-level memory systems by using information about the quality of the stored data |

| US6781877B2 (en) | 2002-09-06 | 2004-08-24 | Sandisk Corporation | Techniques for reducing effects of coupling between storage elements of adjacent rows of memory cells |

| US6829167B2 (en) | 2002-12-12 | 2004-12-07 | Sandisk Corporation | Error recovery for nonvolatile memory |

| US7372731B2 (en) | 2003-06-17 | 2008-05-13 | Sandisk Il Ltd. | Flash memories with adaptive reference voltages |

| US7012835B2 (en) | 2003-10-03 | 2006-03-14 | Sandisk Corporation | Flash memory data correction and scrub techniques |

| US7221008B2 (en) | 2003-10-06 | 2007-05-22 | Sandisk Corporation | Bitline direction shielding to avoid cross coupling between adjacent cells for NAND flash memory |

| US7817469B2 (en) * | 2004-07-26 | 2010-10-19 | Sandisk Il Ltd. | Drift compensation in a flash memory |

| US7348618B2 (en) | 2005-03-30 | 2008-03-25 | Intel Corporation | Flash memory cell having reduced floating gate to floating gate coupling |

| US7196946B2 (en) | 2005-04-05 | 2007-03-27 | Sandisk Corporation | Compensating for coupling in non-volatile storage |

| US7954037B2 (en) | 2005-10-25 | 2011-05-31 | Sandisk Il Ltd | Method for recovering from errors in flash memory |

| US7349258B2 (en) * | 2005-12-06 | 2008-03-25 | Sandisk Corporation | Reducing read disturb for non-volatile storage |

| US7262994B2 (en) * | 2005-12-06 | 2007-08-28 | Sandisk Corporation | System for reducing read disturb for non-volatile storage |

| CN103258572B (zh) | 2006-05-12 | 2016-12-07 | 苹果公司 | 存储设备中的失真估计和消除 |

| WO2008026203A2 (en) | 2006-08-27 | 2008-03-06 | Anobit Technologies | Estimation of non-linear distortion in memory devices |

| US7423912B2 (en) * | 2006-09-19 | 2008-09-09 | Atmel Corporation | SONOS memory array with improved read disturb characteristic |

| ITRM20070273A1 (it) * | 2007-05-16 | 2008-11-17 | Micron Technology Inc | Lettura di celle di memoria non volatile a livello mutiplo. |

| KR100877103B1 (ko) * | 2007-06-01 | 2009-01-07 | 주식회사 하이닉스반도체 | 리드 디스터브가 억제되도록 하는 플래시 메모리소자의리드 방법 |

| US8374026B2 (en) * | 2009-01-30 | 2013-02-12 | Sandisk Il Ltd. | System and method of reading data using a reliability measure |

| US8213255B2 (en) * | 2010-02-19 | 2012-07-03 | Sandisk Technologies Inc. | Non-volatile storage with temperature compensation based on neighbor state information |

-

2007

- 2007-09-25 US US11/860,553 patent/US7751237B2/en active Active

-

2008

- 2008-06-23 EP EP08763613.0A patent/EP2201572B1/en not_active Not-in-force

- 2008-06-23 KR KR1020107009032A patent/KR101426063B1/ko active IP Right Grant

- 2008-06-23 JP JP2010526419A patent/JP5475665B2/ja active Active

- 2008-06-23 WO PCT/IL2008/000855 patent/WO2009040784A1/en active Application Filing

- 2008-06-26 TW TW097123968A patent/TWI463499B/zh not_active IP Right Cessation

-

2010

- 2010-02-03 US US12/699,747 patent/US7990764B2/en active Active

-

2011

- 2011-07-14 US US13/183,341 patent/US8508989B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| WO2009040784A1 (en) | 2009-04-02 |

| TWI463499B (zh) | 2014-12-01 |

| US8508989B2 (en) | 2013-08-13 |

| KR101426063B1 (ko) | 2014-08-01 |

| US20090080259A1 (en) | 2009-03-26 |

| US7990764B2 (en) | 2011-08-02 |

| EP2201572B1 (en) | 2017-01-25 |

| EP2201572A1 (en) | 2010-06-30 |

| US20100135074A1 (en) | 2010-06-03 |

| JP2010541119A (ja) | 2010-12-24 |

| KR20100075958A (ko) | 2010-07-05 |

| TW200921684A (en) | 2009-05-16 |

| US20110305080A1 (en) | 2011-12-15 |

| US7751237B2 (en) | 2010-07-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5475665B2 (ja) | フラッシュメモリのクロスカップリング事後補正 | |

| US9377962B2 (en) | Determining bias information for offsetting operating variations in memory cells | |

| JP5443612B2 (ja) | エラーを管理するための書き込み後読み出しおよび適応再書き込みを伴う不揮発性メモリおよび方法 | |

| US9047955B2 (en) | Adjusting operating parameters for memory cells based on wordline address and cycle information | |

| KR101961975B1 (ko) | 비휘발성 저장소자에 대한 온 칩 다이내믹 판독 | |

| US9318223B2 (en) | Programming nonvolatile memory based on statistical analysis of charge level distributions of memory cells | |

| US7821839B2 (en) | Gain control for read operations in flash memory | |

| US8547740B2 (en) | Adaptive estimation of memory cell read thresholds | |

| KR101058568B1 (ko) | 메모리 셀에 대한 적응적 판독 및 기입 시스템과 방법 | |

| KR20090101160A (ko) | 플래시 메모리로부터 판독된 하드 비트 및 소프트 비트의 소프트 디코딩 | |

| KR20100021999A (ko) | 플래시 메모리의 적응형 동적 판독 | |

| KR20110061648A (ko) | 소프트 데이터 값 생성 방법 및 소프트 데이터 값 생성 시스템 | |

| TW201203273A (en) | Non-volatile storage with temperature compensation based on neighbor state information | |

| US8385116B2 (en) | Nonvolatile semiconductor storage device, controller and threshold adjustment method | |

| KR20140096796A (ko) | 멀티레벨 불휘발성 메모리 장치 및 프로그램 방법 | |

| Wang et al. | Histogram-based flash channel estimation | |

| US8605501B2 (en) | System and method for determining data dependent noise calculation for a flash channel | |

| Papandreou et al. | Enhancing the reliability of MLC NAND flash memory systems by read channel optimization | |

| KR101437103B1 (ko) | 메모리 장치 및 메모리 데이터 읽기 방법 | |

| KR20110082016A (ko) | 소프트 데이터 값 생성 방법 및 소프트 데이터 값 생성 시스템 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110623 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110623 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130122 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130419 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130426 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130517 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130524 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130620 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130627 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130722 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140114 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140206 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5475665 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |