JP5407976B2 - 通信装置、子局装置、通信システム及び通信方法 - Google Patents

通信装置、子局装置、通信システム及び通信方法 Download PDFInfo

- Publication number

- JP5407976B2 JP5407976B2 JP2010069760A JP2010069760A JP5407976B2 JP 5407976 B2 JP5407976 B2 JP 5407976B2 JP 2010069760 A JP2010069760 A JP 2010069760A JP 2010069760 A JP2010069760 A JP 2010069760A JP 5407976 B2 JP5407976 B2 JP 5407976B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- clock

- slave station

- control signal

- unit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Time-Division Multiplex Systems (AREA)

Description

本発明を実施する実施の形態1におけるPONシステムを図1ないし図8を用いて説明する。図1において、PONシステム1は上位装置4と加入者端末であるTE(Terminal Equipment)5の間に設けられ、上位装置4のネットワーク側に接続された通信装置であるOLT(Optical Line Terminal)2すなわち親局装置と、TE5a~5nに接続したONU(Optical Network Unit)3a~3nすなわち子局装置と、OLT2およびONU3a〜3nを接続する光ファイバ6と、光ファイバ6の途中に配置され、OLT2から送信された光信号を各ONU3a〜3n向けに分岐する光カプラ7とで構成されている。TE5としては、例えばHGW(Home Gate Way)、VoIP(Voice over Internet Protocol−Terminal Adapter)、PCなどがある。

ここではONU3がn台(nは整数)接続された場合を示しているが、1台以上であれば何台でも良く、各ONU3に接続するTE5も1台のみならず複数台であっても良い。また、PONシステム1では一般に、OLT2からONU3向きを下り方向、ONU3からOLT2向きを上り方向と呼ぶ。

なお、データ処理を行う各ブロックはソフトウェアで構成しても良い。

なお、低速光信号の出力P2は高速光信号の出力P1よりも小さく、例えば高速光信号の伝送速度が10GHz程度であれば駆動電流20mA程度の出力強度を要するのに対し、伝送速度が100MHz程度まで低速化すると駆動電流3mA程度の出力強度に抑えることができる。

まず、下り方向の通信について説明する。OLT2は、上位装置4からSNI−PHY24を介して入力されたデータはバッファ部251及び下りトラヒック監視部252に送られ、バッファ部251に一次蓄積されたデータはその後フレーム多重部254に送られる。下りトラヒック監視部252は下り方向のトラヒック量を監視し、その情報をパワーセーブ制御部26に伝達する。パワーセーブ制御部26は下りトラヒック監視部252から受取ったトラヒック情報、PON制御部253がPON制御を行う制御フレームのトラヒック情報、およびパワーセーブ制御部26自身が生成するパワーセーブの時間情報を格納したパワーセーブ制御フレームのトラヒック情報を合わせて有効データとし、この有効データの有無を判定して有効データが無い場合にパワーセーブ制御信号をLow出力する。

なお、ここではリンク維持やPON制御の詳細説明は省略するが、例えばGE−PONシステムと同様にプロトコルの一種であるMPCP(Multi−Point Control Protocol)を利用すれば、DiscoveryプロセスやGate/Reportプロセスで実現できる。

なお、1/Nクロック生成部27では常時低速クロックを出力し、セレクタ28にてパワーセーブ制御信号に対応した有効データと低速クロックデータの出力切り替えを行っても良い。

システムLSI20はパワーセーブ中であるか否かを判定し(S1)、パワーセーブ中で無い、すなわち通常運用状態であると判定すれば上位装置4から下りデータのトラヒックが有るか無いかを確認する(S2)。下りトラヒックが無い場合はパワーセーブ状態の開始時間及び継続時間を決定し(S3)、これらの時間情報を格納したパワーセーブ制御フレームを生成し(S4)、ONU3へ送信する(S8)。その後、パワーセーブ制御信号の出力タイミングに合わせてOLT2全体をパワーセーブ状態に遷移させ、PONシステム1に向けて低速の1/Nクロックデータを低出力で送信する(S5)。パワーセーブ状態にあるOLT2は定期的にパワーセーブ制御の継続時間が満了したか否かを確認し(S6)、継続時間満了であると判定するとS7にてパワーセーブ状態を解除し、S1の工程に戻る。なお、パワーセーブ状態の解除とは、通常運用状態で高速かつ高出力の光信号を送信することを意味する。

なお、図内の実線は通常運用状態を、破線はパワーセーブ状態であることを示している。

なお、ここでいう高速/低速および高出力/低出力とは2種類の光信号を比較した場合の速度および出力強度であり、具体的な基準によるものでは無い。

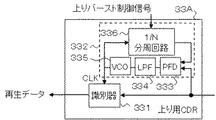

下り用CDR32に高速光信号の受信状態を示すパワーセーブ制御信号が入力されると、1/N分周回路336の分周率はN=1に設定され、低速光信号の受信状態を示すパワーセーブ制御信号が入力されると、1/N分周回路336の分周率はN=10に変更される。

また、ONU3はパワーセーブ制御信号に応じて、自身のPON処理部34の下り方向の機能をスリープさせて省電力化を図ることもできる。

システムLSI30はパワーセーブ中であるか否かを判定し(S11)、パワーセーブ中で無いと判定すればパワーセーブ制御フレームを受信しているか否かを確認する(S12)。パワーセーブ制御フレームを受信している場合はパワーセーブ状態の開始時間及び継続時間の情報を抽出し(S13)、これらの時間情報に合わせて自装置向けのパワーセーブ制御信号を出力すると共に、ONU3全体をパワーセーブ状態に遷移させる(S14)。S12にてパワーセーブ制御フレームを受信していないと判断した場合は予め定めた期間だけ待って(S17)、再度S12の工程を繰り返す。

なお、図内の実線は通常運用状態を、破線はパワーセーブ状態であることを示している。

ONU3は、TE5からユーザデータフレームを受信すると、UNI−PHY37を介してPON処理部34に取り込み、PON制御用の制御フレームと時間多重して上り用CDR33に出力する。

なお、10GHz程度の高速信号を伝送する場合、ONU3は送信信号の波形整形及びタイミング調整をするために上り用CDR33を用いる必要がある。上り方向のデータは各ONU3からバースト的に出力されるが、上り用CDR33の同期確立には数秒程度を要するため、有効データの不在時にはPON処理部34にてIDLEデータを補間し、システムLSI30と上り用CDR33の間は有効データの有無に関わらず連続的にデータ伝送する。

図8は下り方向のパワーセーブ制御シーケンスを示す図である。例えば(1)のように上位装置4からのデータが有る場合、OLT2の下りトラヒック監視部252はパワーセーブ制御部26にその情報を伝え、パワーセーブ制御部26はPON処理部25にデータを出力させる。ONU3はこのデータを受信すると、PON処理部34にて有効データとして処理する。

また、このようなOLT2及びONU3で構成されるPONシステム1も、有効データを損失すること無く消費電力を低減できる。

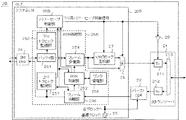

上記実施の形態1ではOLTのパワーセーブについて示したが、実施の形態2ではあわせてONUのパワーセーブも行う。本実施の形態に係るPONシステムを図9ないし図12を用いて説明する。なお、実施の形態1と同じ構成については同一符号を付して説明を省略する。

システムLSI30A上の各ブロックは下り用CDR32Aで抽出した再生クロックに同期して動作するが、フレーム多重部344は1/M分周回路327から出力される上り用クロックに同期して動く。

まず、下り方向の通信について説明する。OLT2は実施の形態1と同じため、説明を省略する。

一方、ONU3AはPONシステム1から光信号が入力されると、光トランシーバ31の光受信器311で受信する。光受信器311は光信号をパワーセーブ制御信号に基づいて所定レベルに増幅した後に電気信号にO/E変換し、下り用CDR32Aに出力する。

下り用CDR32Aに高速光信号の受信状態を示すパワーセーブ制御信号が入力されると、1/N分周回路336の分周率はN=1に設定され、低速光信号の受信状態を示すパワーセーブ制御信号が入力されると、1/N分周回路336の分周率はN=10に変更される。

また、ONU3AはOLT2が下り方向のパワーセーブを実行する時間に対応して下り用パワーセーブ制御信号を生成することにより、OLT2が速度及び強度の異なる光信号を送信しても常に有効データの処理速度と等しいクロックを再生でき、有効データを損なうこと無く受信できる。

また、ONU3Aはパワーセーブ制御信号に応じて、自身のPON処理部34Aの下り方向の機能をスリープさせて省電力化を図ることもできる。

また、実施の形態1と同様に、システムLSI30Aの下り方向通信に関する各機能をソフトウェアで構成することもできる。

ONU3Aは、TE5からユーザデータフレームを受信すると、UNI−PHY37を介してPON処理部34A内のバッファ部342に取り込む。バッファ部342はユーザデータを一時的に蓄積すると共に上りトラヒック監視部343に転送し、上りトラヒック監視部343は上りトラヒック量の情報をパワーセーブ制御部35に伝達する。

このようにして、上りバーストデータ不在時にフレーム多重部344と上り用CDR33A間を低速クロックで動作に切替えることにより、消費電力が大幅に低減できる。

まず、上り方向のパワーセーブ中であるか否かを判定し(S21)、パワーセーブ中で無い、すなわち通常運用状態であると判定すればTE5から上りデータのトラヒック送信要求が有るか無いかを確認する(S22)。上り送信要求が無い場合は下り用CDR32A及び光トランシーバ31へ上りバースト制御信号をLow出力し(S23)、上り方向のパワーセーブを実行するために下り用CDR32Aに上り用低速クロックを生成させ、システムLSI30Aと上り用CDR33A間を低速で信号伝送させ(S24)、フローを終了する。

なお、図内の実線は通常運用状態を、破線はパワーセーブ状態であることを示している。

なお、本実施の形態はONU3A内部の動作が実施の形態1と異なるのみで、PONシステム1のシステム動作は同じであるため説明を省略する。

また、このようなOLT2及びONU3Aで構成されるPONシステムも、有効データを損失すること無く実施の形態1に記載のPONシステム1よりもさらに消費電力を低減できる。

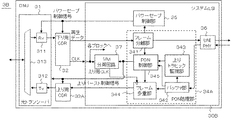

上記実施の形態2では、上りバーストデータが無い場合にONU3Aの下り用CDR32Aにて低速クロックを生成し、システムLSIと上り用CDR間の消費電力を低減している。本実施の形態では、下り用CDR32Aの代わりにシステムLSI上で上り用の低速クロックを生成する。また、OLTに接続するいずれのONUからも上りバーストデータを受信しない場合に上り方向の機能を休止させてOLTの更なるパワーセーブを図る。本実施の形態に係るPONシステム1を図13ないし図16を用いて説明する。なお、実施の形態1または実施の形態2と同じ構成については同一符号を付して説明を省略する。

OLT2Bは、図13に示すように、システムLSI20B以外は実施の形態1と同じ構成を有し、CMOS半導体等で形成されるシステムLSI20Bは、基準クロック23と、SNI−PHY24と、PON処理機能を有するPON処理部25Bすなわち下りデータ処理部兼上りデータ処理部と、実施の形態1に記載のパワーセーブ制御部26の機能に加えて上り方向のバーストデータ不在時に上りパワーセーブ制御信号すなわち第2の親局制御信号を生成するパワーセーブ制御部26Bと、1/Nクロック生成部27すなわち低速クロック生成部と、下り用パワーセーブ制御信号に基づいてPON処理部25Bから出力されるフレームと1/Nクロックを切替えるセレクタ28を備えている。

なお、OLT2B及びONU3Bのデータ処理を行う各ブロックはソフトウェアで構成しても良い。

下り方向の通信は実施の形態1と同じであるため省略し、上り方向の通信について説明する。

ONU3Bは、TE5からユーザデータフレームを受信すると、UNI−PHY37を介してPON処理部34A内のバッファ部342に取り込む。バッファ部342はユーザデータを一時的に蓄積すると共に上りトラヒック監視部343に転送し、上りトラヒック監視部343は上りトラヒック量の情報をパワーセーブ制御部35に伝達する。

このように、上りバーストデータ不在時にフレーム多重部344と上り用CDR33A間を低速クロックで動作に切替えることにより、実施の形態2と同様に消費電力を大幅に低減できる。

なお、システムLSI30Bの各機能をソフトウェアで構成した場合の動作は実施の形態2とほぼ同じで、上りバースト制御信号の出力先が下り用CDR32Aの代わりに1/M分周回路37になる点のみ異なる。

まず、上り方向のパワーセーブ中であるか否かを判定し(S31)、パワーセーブ中で無い、すなわち通常運用状態であると判定すれば、リンクしている各ONU3BについてID番号iを特定し(S32)、上りトラヒック送信要求が有るか無いかを確認する(S33)。上り送信要求が無い場合はS34にてID番号iに1加算し、S32に戻る。リンクしている全ONU3BについてS32〜S34を実行すると、上り方向のパワーセーブ時間を設定して上り通信に必要な各機能のパワーセーブを実行し(S35)、フローを終了する。

なお、図内の実線は通常運用状態を、破線はパワーセーブ状態であることを示している。

図16は上り方向のパワーセーブを行う場合の制御シーケンスを示す図である。ここでは、説明を簡潔にするためにONU3Bが1台の例を示している。

OLT2BはReportメッセージを受信すると、そのONU3Bに割当てる帯域を決定し、次のGateメッセージにONU3Bに許容する送信帯域及び送信タイミングの情報を格納して送信する。以降、OLT2BとONU3B間では同様の動作を繰り返す。

OLT2Bのパワーセーブ制御部26Bは、ONU3BからReportメッセージ#1を受信する前にパワーセーブ状態を解除し、Data#1受信後に再びパワーセーブを開始する。

OLT2Bのパワーセーブ制御部26Bは、ONU3BからReportメッセージ#2を受信する前にパワーセーブ状態を解除し、Reportメッセージ#2を受信するとパワーセーブ状態に戻る。

OLT2Bのパワーセーブ制御部26Bは、先ほどと同様に、ONU3BからReportメッセージ#3を受信する前にパワーセーブ状態を解除し、Reportメッセージ#3を受信するとパワーセーブ状態に戻る。

OLT2Bのパワーセーブ制御部26Bは、ONU3BからReportメッセージ#4を受信する前にパワーセーブ状態を解除し、Reportメッセージ#4及び自身がONU3Bに割当てたData#2の受信期間を待って再びパワーセーブ状態に戻る。

以降、同様の動作を繰り返す。

また、このようなOLT2B及びONU3Bで構成されるPONシステムは、有効データを損失すること無く消費電力を低減できる。

なお、本実施の形態に記載のONU3Bは実施の形態2に記載のONU3Aと低速クロックを生成する箇所が異なるのみであり、OLT2BにONU3Aを接続しても同様の効果が得られる。

2、2B OLT

3、3A、3B、3a〜3n ONU

21 光トランシーバ

23 基準クロック

25 PON処理部

252 下りトラヒック監視部

253 PON制御部

256 フレーム分離部

257 上りトラヒック監視部

26、26B パワーセーブ制御部

27 1/Nクロック生成部

28 セレクタ

29 駆動回路

31 光トランシーバ

32、32A 下り用CDR

322 PLL回路

326 1/N分周回路

327 1/M分周回路

33、33A 上り用CDR

336 1/N分周回路

34、34A PON処理部

343 上りトラヒック監視部

345 PON制御部

35 パワーセーブ制御部

37 1/M分周回路

Claims (18)

- 所定速度のクロックに同期して送信データを処理するデータ処理部と、

前記送信データのトラヒック有無を監視して制御信号を生成する制御部と、

前記クロックを整数倍に低速化する低速クロック生成部と、

前記制御信号に基づいて、前記送信データ又は前記低速クロックを異なる出力強度で送信

する送信部と、を備え、

前記送信部は、前記送信データを第1の出力強度で送信し、前記低速クロックを前記第1

の出力強度よりも小さな第2の出力強度で送信することを特徴とする通信装置。 - 所定速度のクロックに同期して送信データを処理する送信データ処理部と、

前記送信データのトラヒック有無を監視して第1の制御信号を生成する第1の制御部と、

前記クロックを整数倍に低速化する低速クロック生成部と、

前記第1の制御信号に基づいて、前記送信データ又は前記低速クロックを異なる出力強度

で送信する送信部と、

データを受信する受信部と、

前記受信データを前記所定速度のクロックに同期して処理する受信データ処理部と、

前記受信データから将来のデータ受信時間情報を抽出して第2の制御信号を生成する第2

の制御部と、を備え、

前記受信データ処理部は、前記第2の制御信号に基づいて受信データ処理機能を休止し、

前記送信部は、前記送信データを第1の出力強度で送信し、前記低速クロックを前記第1

の出力強度よりも小さな第2の出力強度で送信することを特徴とする通信装置。 - 前記制御部は、将来のデータ送信する時間情報を前記送信データとして生成することを特

徴とする請求項1または請求項2に記載の通信装置。 - 親局装置に同期して通信を行う子局装置において、

前記親局装置からデータを受信する受信部と、

前記受信データから前記親局装置が将来データ送信する時間情報を抽出して制御信号を生

成する制御部と、

前記制御信号に基づいて、前記受信データから前記親局装置と同期したクロックを再生す

るクロック再生部と、

を備え、

前記受信部は、前記制御信号に基づいて、強度の異なる前記受信データを同一のレベル強

度に増幅することを特徴とする子局装置。 - 前記クロック再生部は、前記制御信号に基づいて分周率が切り替わる可変分周器を備えた

ことを特徴とする請求項4に記載の子局装置。 - 親局装置に同期して通信する子局装置において、

前記親局装置からデータを受信する受信部と、

前記受信データから前記親局装置が将来データ送信する時間情報を抽出して第1の子局制

御信号を生成する第1の制御部と、

前記第1の子局制御信号に基づいて、前記受信データから前記親局装置と同期したクロッ

クを再生するクロック再生部と、

前記親局装置に送信するデータを生成する送信データ生成部と、

前記送信データを前記親局装置に送信する送信部と、

前記再生クロックに同期して前記送信データの有無情報を監視し、第2の子局制御信号を

生成する第2の制御部と、

前記送信データ生成部と前記送信部の間に設けられ、前記送信データの波形整形およびタ

イミング再生を行うCDRと、

前記再生クロックを分周する分周器と、を備え、

前記送信データ生成部と前記CDRの間は、前記第2の子局制御信号に基づいて前記分周

クロックで動作し、

前記受信部は、前記第1の子局制御信号に基づいて、強度の異なる前記受信データを同一のレベル強度に増幅することを特徴とする子局装置。 - 前記クロック再生部は、前記第1の子局制御信号に基づいて分周率が切り替わる可変分周

器を備えたことを特徴とする請求項6に記載の子局装置。 - 前記第2の制御部は、前記送信データに将来の前記送信データのトラヒック有無情報を格

納することを特徴とする請求項6または請求項7に記載の子局装置。 - 親局装置と子局装置が同期して通信する通信システムにおいて、

前記親局装置は、

所定速度のクロックに同期して前記子局装置へ送信するデータを処理するデータ処理部と

、

前記データの有無を監視して親局制御信号を生成すると共に、将来のデータ送信する時間

情報を前記データとして生成する親局制御部と、

前記クロックを整数倍に低速化する低速クロック生成部と、

前記親局制御信号に基づいて、前記データ又は前記低速クロックを異なる出力強度で送信

する送信部と、を備え、

前記送信部は、前記データを第1の出力強度で送信し、前記低速クロックを前記第1の出

力強度よりも小さな第2の出力強度で送信し、

前記子局装置は、

前記親局装置から前記データ及び前記低速クロックを受信する受信部と、

前記受信データから前記親局装置が将来データ送信する時間情報を抽出して子局制御信号

を生成する子局制御部と、

前記子局制御信号に基づいて、前記データ及び前記低速クロックから前記所定速度のクロ

ックを再生するクロック再生部と、

を備え、

前記受信部は、前記子局制御信号に基づいて、強度の異なる前記受信データを同一のレベ

ル強度に増幅することを特徴とする通信システム。 - 前記クロック再生部は、前記子局制御信号に基づいて分周率が切り替わる可変分周器を備

えたことを特徴とする請求項9に記載の通信システム。 - 親局装置と子局装置が同期して通信する通信システムにおいて、

前記親局装置は、

所定速度のクロックに同期して前記子局装置へ送信するデータを処理するデータ処理部と

、

前記データのトラヒック有無を監視してすると共に、将来のデータ送信する時間情報を前

記データとして生成する親局制御部と、

前記クロックを整数倍に低速化する低速クロック生成部と、

前記親局制御信号に基づいて、前記データ又は前記低速クロックを異なる出力強度で送信

する親局送信部と、を備え、

前記親局送信部は、前記データを第1の出力強度で送信し、前記低速クロックを前記第1

の出力強度よりも小さな第2の出力強度で送信し、

前記子局装置は、

前記親局装置からデータ及び前記低速クロックを受信する受信部と、

前記受信データから将来のデータ受信情報を抽出して第1の子局制御信号を生成する第1

の子局制御部と、

前記第1の子局制御信号に基づいて、前記受信データから前記所定速度のクロックを再生

するクロック再生部と、

前記親局装置に送信するデータを生成する送信データ生成部と、

前記送信データを前記親局装置に送信する子局送信部と、

前記再生クロックに同期して前記送信データの有無情報を監視し、第2の子局制御信号を

生成する第2の子局制御部と、

前記送信データ生成部と前記子局送信部の間に設けられ、前記送信データの波形整形およ

びタイミング再生を行うCDRと、

前記再生クロックを分周する分周器と、を備え、

前記送信データ生成部と前記CDRの間は、前記第2の子局制御信号に基づいて前記分周

クロックで動作し、

前記受信部は、前記第1の子局制御信号に基づいて、強度の異なる前記受信データを同一

のレベル強度に増幅することを特徴とする通信システム。 - 前記クロック再生部は、前記第1の子局制御信号に基づいて分周率が切り替わる可変分周

器を備えたことを特徴とする請求項11に記載の通信システム。 - 親局装置と子局装置が同期して通信する通信システムにおいて、

前記親局装置は、

所定速度のクロックに同期して前記子局装置へ送信する下りデータを処理する下りデータ

処理部と、

前記下りデータのトラヒック有無を監視して第1の親局制御信号を生成する第1の親局制

御部と、

前記クロックを整数倍に低速化する低速クロック生成部と、

前記第1の親局制御信号に基づいて、前記下りデータ又は前記低速クロックを異なる出力

強度で送信する親局送信部と、

上りデータを受信する親局受信部と、

前記上りデータを前記所定速度のクロックに同期して処理する上りデータ処理部と、

前記上りデータから将来の上りデータ受信時間情報を抽出して第2の親局制御信号を生成

する第2の親局制御部と、を備え、

前記親局送信部は、前記下りデータを第1の出力強度で送信し、前記低速クロックを前記

第1の出力強度よりも小さな第2の出力強度で送信し、

前記子局装置は、

前記親局装置から下りデータ及び前記低速クロックを受信する子局受信部と、

前記下りデータから前記親局装置が将来下りデータを送信する時間情報を抽出して第1の

子局制御信号を生成する第1の子局制御部と、

前記第1の子局制御信号に基づいて、前記下りデータから前記所定速度のクロックを再生

するクロック再生部と、

前記親局装置に送信する上りデータを生成する上りデータ生成部と、

前記上りデータを前記親局装置に送信する子局送信部と、

前記再生クロックに同期して前記上りデータの有無情報を監視し、第2の子局制御信号を

生成すると共に、前記上りデータに将来の前記上りデータのトラヒック有無情報を格納す

る第2の子局制御部と、

前記上りデータ生成部と前記子局送信部の間に設けられ、前記送信上りデータの波形整形

およびタイミング再生を行うCDRと、

前記再生クロックを分周する分周器と、を備え、

前記子局受信部は、前記第1の子局制御信号に基づいて、強度の異なる前記受信データを

同一のレベル強度に増幅し、

前記親局装置は、前記第2の親局制御信号に基づいて前記上りデータ処理部を休止し、

前記子局装置は、前記第2の子局制御信号に基づいて前記上りデータ生成部と前記CDR

の間を前記分周クロックで動作させることを特徴とする通信システム。 - 前記クロック再生部は、前記第1の子局制御信号に基づいて分周率が切り替わる可変分周

器を備えたことを特徴とする請求項13に記載の通信システム。 - 親局装置と子局装置が所定速度のクロックに同期して通信する通信システムにおいて、

前記親局装置が送信するデータのトラヒック有無を監視して将来データを送信する時間情

報を前記子局装置へ通知する工程と、

前記親局装置が前記時間情報に基づいて前記データ又は前記所定速度を整数倍に低速化し

た低速クロックのいずれか一方を異なる出力強度で前記子局装置に送信する工程と、

前記子局装置が前記時間情報に基づいて前記データ及び前記低速クロックから前記所定速

度のクロックを再生する工程と、を有し、

前記親局装置は、前記データを第1の出力強度で送信し、前記低速クロックを前記第1の出力強度よりも小さな第2の出力強度で送信することを特徴とする通信方法。 - 前記子局装置は、前記時間情報に基づいて自装置のデータ受信機能を休止することを特徴

とする請求項15に記載の通信方法。 - 前記子局装置は、送信するデータの波形整形およびタイミング再生を行うCDRを備え、

前記親局装置へ送信するデータのトラヒック有無を監視し、送信するデータが無い期間は

前記所定速度よりも低速で前記CDRへデータを入力することを特徴とする請求項15ま

たは請求項16に記載の通信方法。 - 前記子局装置は、前記親局装置へ送信するデータのトラヒック有無を監視し、将来データ

を送信する時間情報を前記親局装置へ通知する工程を有し、

前記親局装置は、前記時間情報に基づいて自装置のデータ受信機能を休止することを特徴

とする請求項17に記載の通信方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010069760A JP5407976B2 (ja) | 2010-03-25 | 2010-03-25 | 通信装置、子局装置、通信システム及び通信方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010069760A JP5407976B2 (ja) | 2010-03-25 | 2010-03-25 | 通信装置、子局装置、通信システム及び通信方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011205329A JP2011205329A (ja) | 2011-10-13 |

| JP5407976B2 true JP5407976B2 (ja) | 2014-02-05 |

Family

ID=44881514

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010069760A Expired - Fee Related JP5407976B2 (ja) | 2010-03-25 | 2010-03-25 | 通信装置、子局装置、通信システム及び通信方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5407976B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013126040A (ja) * | 2011-12-13 | 2013-06-24 | Nippon Telegr & Teleph Corp <Ntt> | 加入者側通信装置及びポイント・トゥ・マルチポイント型通信システム |

| KR102001414B1 (ko) | 2012-09-27 | 2019-07-18 | 삼성전자주식회사 | 데이터 트랜잭션에 따라 전력공급을 제어하는 시스템-온-칩 및 그 동작방법 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06311068A (ja) * | 1993-04-20 | 1994-11-04 | Hitachi Denshi Ltd | 無線機の送受信切換方式 |

| JPH07288507A (ja) * | 1994-04-15 | 1995-10-31 | Hitachi Ltd | マルチメディア多重化装置 |

| US6973123B2 (en) * | 2001-03-21 | 2005-12-06 | International Business Machines Corporation | System and method for controlling line driver power in digital subscriber line modems |

| JP4389949B2 (ja) * | 2007-02-28 | 2009-12-24 | 沖電気工業株式会社 | 通信タイミング制御装置、通信タイミング制御方法、ノード及び通信システム |

| JP2011188356A (ja) * | 2010-03-10 | 2011-09-22 | Mitsubishi Electric Corp | 子局およびponシステム |

-

2010

- 2010-03-25 JP JP2010069760A patent/JP5407976B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011205329A (ja) | 2011-10-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5283801B2 (ja) | 加入者側光通信装置、通信システム、制御装置および省電力制御方法 | |

| EP1520380B1 (en) | Synchronous data transfer system for time-sensitive data in packet-switched networks | |

| US20110211837A1 (en) | Method of Recovery From Sleep State of an Onu in a Pon System Capable of Power Saving | |

| CN101689947B (zh) | 电信网节点的相位同步 | |

| JP5407976B2 (ja) | 通信装置、子局装置、通信システム及び通信方法 | |

| JP2008199233A (ja) | 光受信装置及び方法並びに局側光終端装置 | |

| US9042737B2 (en) | Clock and data recovery unit and power control method therefor and PON system | |

| JP2007143160A (ja) | 受動光ネットワークの通信設備のための改善されたデータ伝送装置 | |

| JP2007243796A (ja) | マルチレートponシステムとこれに使用する端末装置 | |

| JP5718258B2 (ja) | 加入者側通信装置、加入者側ゲートウェイ装置及び宅内通信システム | |

| JP2007036712A (ja) | 通信システムおよび通信方法ならびにその親局装置および子局装置 | |

| JP2008160370A (ja) | データ伝送システム及び方法、データ送信装置並びにデータ受信装置 | |

| JP2010177906A (ja) | 変換装置 | |

| KR100688091B1 (ko) | 동기식 이더넷에서의 프레임 동기 방법 및 클럭 발생 장치 | |

| JP2012044671A (ja) | バーストモードクロック、データ復元装置、および方法 | |

| JP6127613B2 (ja) | 通信システム、宅側装置、通信制御方法および局側装置 | |

| JP5757190B2 (ja) | 光通信システム、光通信システムの制御方法および宅側装置 | |

| KR100900846B1 (ko) | 패킷 교환 네트워크에서의 시간에 민감한 데이터의 동기 데이터 전송 시스템 | |

| JP2013026712A (ja) | Ponシステムの宅側装置、信号処理回路及び同期維持方法 | |

| JP2012169815A (ja) | 光受信器および局舎装置 | |

| JP2007300445A (ja) | マルチレートponシステムに使用可能な局側装置及び端末装置、並びに、同システムにおける網同期方法 | |

| JP2013081065A (ja) | 省電力制御方法、局側装置および通信システム | |

| JP2011188356A (ja) | 子局およびponシステム | |

| JP5787684B2 (ja) | 時分割複信方式無線通信システム | |

| JP5787685B2 (ja) | 時分割複信方式無線通信システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120829 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130830 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130903 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130919 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131008 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131021 |

|

| LAPS | Cancellation because of no payment of annual fees |