JP5346520B2 - 画像表示装置 - Google Patents

画像表示装置 Download PDFInfo

- Publication number

- JP5346520B2 JP5346520B2 JP2008208614A JP2008208614A JP5346520B2 JP 5346520 B2 JP5346520 B2 JP 5346520B2 JP 2008208614 A JP2008208614 A JP 2008208614A JP 2008208614 A JP2008208614 A JP 2008208614A JP 5346520 B2 JP5346520 B2 JP 5346520B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- luminance

- waveform

- light emission

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000003990 capacitor Substances 0.000 claims description 7

- 239000011159 matrix material Substances 0.000 claims description 7

- 238000005401 electroluminescence Methods 0.000 description 106

- 239000010410 layer Substances 0.000 description 27

- 239000010409 thin film Substances 0.000 description 20

- 238000000034 method Methods 0.000 description 15

- 238000010586 diagram Methods 0.000 description 13

- 239000000463 material Substances 0.000 description 11

- 239000000758 substrate Substances 0.000 description 11

- 239000011521 glass Substances 0.000 description 10

- 239000010408 film Substances 0.000 description 9

- 239000002184 metal Substances 0.000 description 9

- 229910052751 metal Inorganic materials 0.000 description 9

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 8

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 6

- 230000015572 biosynthetic process Effects 0.000 description 6

- 229910000789 Aluminium-silicon alloy Inorganic materials 0.000 description 5

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 5

- 239000012788 optical film Substances 0.000 description 5

- 239000004065 semiconductor Substances 0.000 description 5

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- 238000002161 passivation Methods 0.000 description 4

- 229920005591 polysilicon Polymers 0.000 description 4

- 101100060179 Drosophila melanogaster Clk gene Proteins 0.000 description 3

- 229910001374 Invar Inorganic materials 0.000 description 3

- 101150038023 PEX1 gene Proteins 0.000 description 3

- 239000002274 desiccant Substances 0.000 description 3

- 229910052742 iron Inorganic materials 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 101150014555 pas-1 gene Proteins 0.000 description 3

- 229920006395 saturated elastomer Polymers 0.000 description 3

- 239000006096 absorbing agent Substances 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 239000012044 organic layer Substances 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 230000035939 shock Effects 0.000 description 2

- 229920001621 AMOLED Polymers 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 238000009125 cardiac resynchronization therapy Methods 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 239000005394 sealing glass Substances 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

- G09G3/3291—Details of drivers for data electrodes in which the data driver supplies a variable data voltage for setting the current through, or the voltage across, the light-emitting elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0814—Several active elements per pixel in active matrix panels used for selection purposes, e.g. logical AND for partial update

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0251—Precharge or discharge of pixel before applying new pixel voltage

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0259—Details of the generation of driving signals with use of an analog or digital ramp generator in the column driver or in the pixel circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0262—The addressing of the pixel, in a display other than an active matrix LCD, involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependent on signals of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0233—Improving the luminance or brightness uniformity across the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0271—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping

- G09G2320/0276—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping for the purpose of adaptation to the characteristics of a display device, i.e. gamma correction

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2014—Display of intermediate tones by modulation of the duration of a single pulse during which the logic level remains constant

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/30—Devices specially adapted for multicolour light emission

Description

有機EL表示装置は、例えば、下記特許文献1、特許文献2、特許文献3に記載されている。

前述の特許文献1には、発光期間内にPWM信号として三角波波形の信号を使用すること、および、この三角波波形信号は、様々な変更が可能であり、例えば、発光の時間軸重心が発光階調に依存しないように左右対象の三角波波形、非対称の三角波波形や、ガンマ特性変調に相当する非直線の三角波波形、複数の三角波波形などを用いてそれぞれ異なる視覚特性を得ることが記載されている。

また、前述の特許文献2には、判断回路の判断結果に基づいて、複数の輝度モードのうちの1つを選択する選択回路を備える電気光学装置が記載されている。この特許文献2では、低輝度部でつぶれを生じた場合などには、ガンマ補正電圧などの基準電位を調整してガンマカーブを適宜変更することにより、低輝度部で階調差を判別し易くすることができる。なお、このような処理は、例えば、ガンマ基準用電源回路を制御信号に応じて接続/非接続を切り替え可能な抵抗を組み込んでおくとともに、最大輝度を低下させる場合に主制御回路が先の制御信号を出力するようにプログラミングしておくことなどにより自動的に実施することができる、或いは、ユーザの入力操作に応じて先の処理が実施されるように構成してもよいと記載されている。

また一般に、アクティブ・マトリクス型有機EL表示装置(AM−OLED)に使用される赤、緑、青に発光する各有機EL素子は、発光特性(発光輝度、電圧−電流特性、電圧−発光輝度特性等)が、各色毎に異なっている。この赤、緑、青の各有機EL素子の発光特性のバラツキも、表示画面上では、前述したような微細なムラとなって見えることになる。

この赤、緑、青の各有機EL素子の発光特性のバラツキによる表示不均一を抑制するために、例えば、前述の特許文献3には、赤、緑、青の各有機EL素子に供給するR・G・Bのそれぞれの映像信号に対して、ガンマ補正するメモリを設け、R・G・B毎にガンマ補正値を変更する手法が記載されている。

また、引用文献2、引用文献3では、ガンマ補正するために、A/D変換器と、D/A変換器と、補正メモリとを必要とし、構成が複雑でコストがかかるという問題点がある。その上、引用文献3では、各画素間の輝度バラツキなどの局所的な特性のバラツキについては考慮されておらず、この引用文献3では、各画素間の輝度バラツキなどの局所的な特性のバラツキを解消することは不可能である。

本発明は、前記従来技術の問題点を解決するためになされたものであり、本発明の目的は、EL素子のような電流駆動型発光素子を有する画像表示装置において、従来よりも駆動回路の構成が簡単で、しかも、発光輝度のバランスをとりつつ高輝度から低輝度まで広範囲に亘る赤、緑、青の各画素の発光輝度を制御することが可能となる技術を提供することにある。

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

(3)(1)において、前記画像信号生成回路と前記画素駆動信号生成回路とは、同一の回路で共用する。

(4)(1)において、前記第一の輝度表示モードでは前記駆動トランジスタが飽和領域で前記自発光素子を発光させ、前記第二の輝度表示モードでは前記駆動トランジスタは非飽和領域で前記自発光素子を発光させる。

(5)(1)において、前記第二の輝度表示モードにおける前記画素駆動信号波形は、複数の変極点を有する多角形である。

(6)(5)において、前記第二の輝度表示モードにおける前記画素駆動信号波形は、複数の変極点を有する放物線波形である。

(7)(1)において、前記第二の輝度表示モードにおける前記画素駆動信号波形は、概略放物線波形である。

(9)(1)において、前記第一の輝度表示モードにおける前記画素駆動信号波形は、矩形波である。

(10)(1)において、前記第一の輝度表示モードにおける前記画素駆動信号波形は、台形波である。

(11)(1)において、前記輝度表示モードには、前記発光期間における前記画素駆動信号波形が変動電圧波形であり、前記変動電圧波形の形状が異なる複数の輝度表示モードを有する。

(12)(1)において、前記輝度表示モードには、前記発光期間における前記画素駆動信号波形が変動電圧波形であり、前記変動電圧波形の周期が異なる複数の輝度表示モードを有する。

(13)(1)において、前記輝度表示モードは、外光の明るさを検出して自動的に選択可能である。

本発明によれば、EL素子のような電流駆動型発光素子を有する画像表示装置において、従来よりも駆動回路の構成が簡単で、しかも、発光輝度のバランスをとりつつ高輝度から低輝度まで広範囲に亘る赤、緑、青の各画素の発光輝度を制御することが可能となる。

なお、実施例を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

[本発明の前提となる有機EL表示装置の概要]

図1は、本発明の前提となる有機EL表示装置の概略構成を示すブロック図である。

図1において、ARは表示部、21は信号線駆動回路、22は走査線駆動回路、100は輝度モード制御部、110は陽極電源部、111は電源制御部、130は表示制御部である。

131は外部から入力される映像デジタル信号である映像データ信号であり、画像の各画素の濃淡値を表す信号である。132は垂直同期信号(VSYNC)であり、表示一画面周期(1フレーム)の信号で映像データ信号の1フレーム分の始まりを示す信号である。

133は水平同期信号(HSYNC)であり、一水平周期の信号で表示データデジタル信号の1水平ライン分の始まりを示す信号である。134はデータイネーブル信号であり、映像データ信号が有効である期間を示す信号である。

映像データ信号131、垂直同期信号132、水平同期信号133、データイネーブル信号134は全てデータ同期クロック135に同期して入力される。

本実施例では、映像データ信号131は、一画面分が左上端の画素から順次ラスタスキャン形式で転送されるものとして以下説明する。

信号線駆動回路21は、信号線駆動回路制御信号137によって制御され、信号線を介して表示部内の各画素にアナログ信号で画像信号を書き込む。

走査線駆動回路22は、走査線駆動回路制御信号138によって制御され、リセット線15と点灯スイッチ線19とを介して表示部ARに書き込み選択信号を送る。

陽極電源部110は有機EL素子の陽極側の電源である。陽極電源部110は、有機EL素子7が発光するために必要な電力を表示部ARに供給する。

輝度モード制御部100は、外部から設定され、輝度モード制御部100は、電圧制御信号101を電源制御部111に、発光期間制御信号102を信号線駆動回路21に出力する。

電源制御部111は各種の輝度表示モードに応じて、予め規定した有機EL素子の駆動電圧を表示部ARに供給する。なお、輝度モード制御部100は、外光の明るさに応じて、自動的に2つ以上の輝度表示モードの中の所定の輝度表示モードを選択するようにしてもよい。

信号線駆動回路21は、有機EL表示装置に入力される画像信号の階調に対する実際の表示輝度(即ち、階調特性)を制御する。陰極電源部120は表示部内の各画素の有機EL素子の陰極側に陰極電源線121を介して接続されている。

画素10には、信号線17、リセット線15、点灯スイッチ線19、および電源線18がそれぞれ入力される。リセット線15、および、点灯スイッチ線19は、走査線駆動回路22に接続される。

信号線17には、信号線駆動回路21から、画像信号とPWM信号が入力される。

また、実際には画素10は、有機EL表示パネルの表示領域内に多数個配置されるが、図面の簡略化のために図1では、4画素のみを記載してある。

各画素10には、発光素子としての有機エレクトロルミネッセンス素子(以下、有機EL素子という。)7が設けられており、有機EL素子7のカソード電極は陰極電源線121に接続される。

また、アノード電極は、n型薄膜トランジスタで構成される点灯スイッチ素子9と、p型薄膜トランジスタ(以下、駆動TFTという。)4を介して電源線18に接続される。

また、駆動TFT4のゲート電極とソース電極との間には、容量素子2が接続され、駆動TFT4のドレイン電極とゲート電極との間には、薄膜トランジスタで構成されるリセットスイッチ素子5が設けられる。

なお、リセットスイッチ素子5のゲート電極は、リセット線15に接続される。また、点灯スイッチ素子9のゲート電極は、点灯スイッチ線19に接続される。

画素10、走査線駆動回路22、信号線駆動回路21等の各回路は全て、半導体層として、一般に良く知られている低温多結晶シリコン層を有する低温多結晶シリコン薄膜トランジスタを用いて構成され、これらの薄膜トランジスタは、ガラス基板上に形成される。

また、低温多結晶シリコン薄膜トランジスタ、あるいは、有機EL素子7の製造方法などに関しては、一般に報告されているものと大きな相違はないため、ここではその説明は省略する。

図3に示すように、本実施例の前提となる有機EL表示装置では、各画素は、1フレーム期間内に、書込期間(図3のAの期間)と発光期間(図3のBの期間)とを有し、書込期間に各画素10に画像信号を書き込み、発光期間に点灯して表示を行う。

画像信号の書き込みは、1表示ライン単位、即ち、リセット線15毎に行なわれる。ここで、本実施例の有機EL表示装置の表示部ARの画素数は、640×480×3画素となっているため、リセット線15は、垂直方向に第1リセット線から第480リセット線まで480本並び、信号線17は、R・G・Bの各画素毎に、水平方向に第1信号線、第2信号線から、第640信号線まで640本並んでいるものとして、以下説明する。

さらに、電源線18は、R・G・Bの各画素毎に、水平方向に第1電源線、第2電源線から、第640電源線まで640本並んでいるものとして、以下説明する。

以下、本実施例の有機EL表示装置の前提となる駆動方法の各期間の動作について説明する。

書込期間においては、図3のCに示すように、走査線駆動回路22が、1表示ライン単位に各行の複数の画素10を順次走査し、これと同期して、信号線駆動回路21から画像信号を信号線17に書き込む。

以下、走査線駆動回路22によって選択された、任意の表示ラインの画素10の「書込み期間」における動作について説明する。

書込み期間内に、信号線駆動回路21から信号線17に、画像電圧が供給される。

始めに、リセット線15と点灯スイッチ線19とがHighレベル(以下、Hレベル)となるので、リセットスイッチ素子5と点灯スイッチ素子9とがオンとなり、これにより、駆動TFT4はゲート電極とドレイン電極とが接続されたダイオード接続になる。

次に、点灯スイッチ線19がLowレベル(以下、Lレベル)となり、点灯スイッチ素子9がオフすると、駆動TFT4と有機EL素子7とは強制的に電流オフ状態になるが、このとき、駆動TFT4のゲート電極とドレイン電極はリセットスイッチ素子5で短絡されているため、容量素子2の一端でもある、駆動TFT4のゲート電極の電圧は、電源線18の電圧(Vdd)よりしきい値電圧(Vth)だけ低い電圧(Vdd−Vth)に自動的にリセットされる。なお、このとき、前述したように、容量素子2の他端には、信号線17から画像信号が入力されている。

即ち、図4に示すように、駆動TFT4と有機EL素子7とで構成される駆動インバータ(INV)の入出力が短絡されることとなり、各々の画素の駆動インバータ(INV)を構成する駆動TFT4の特性に従った基準電圧(Vref)が設定され、この基準電圧を基準として、信号線17からの映像電圧を容量素子2に蓄積する。

駆動インバータ(INV)は、書込期間後の発光期間に入力される三角波波形のPWM信号が、容量素子2に蓄積された画像電圧より高いときは、有機EL素子7をオフ状態とし、書込期間後の発光期間に入力される三角波波形のPWM信号が、容量素子2に蓄積された画像電圧より低いときは有機EL素子7をオン状態とすることによって、画像電圧に従った有機EL素子7の発光時間制御を行う。

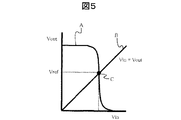

図5において、Aは駆動インバータ(INV)の入出力特性を、またBは入出力短絡条件を示し、Aに示す曲線とBに示す直線の交叉点Cは駆動インバータ(INV)の画像電圧書込み基準電位(Vref)である。

駆動TFT4は、画像信号の書き込み時に入出力が短絡されるため、入力、出力の電位は、入出力特性と、Vin=Voutの直線で示す入出力短絡条件の交点Cである画像電圧書込み基準電位(Vref)となる。画像電圧の書き込みはこの信号電圧書込み基準電圧(Vref)を基準として行われる。

発光期間においては、走査線駆動回路22は停止し、リセット線15がLレベル、点灯スイッチ線19がHレベルとなるので、全画素のリセットスイッチ素子5がオフ、点灯スイッチ素子9が一斉にオンとなる。

このとき、信号線17には、信号線駆動回路21から、図3のDに示す三角波波形のPWM信号が入力される。

そして、三角波波形のPWM信号が、容量素子2に蓄積された画像電圧より高いときは、有機EL素子7がオフ状態となり、三角波波形のPWM信号が、容量素子2に蓄積された画像電圧より低いときは有機EL素子7をオン状態となる。

なお、本実施例では、駆動TFT4と有機EL素子7が点灯スイッチ素子9を介して接続されていたが、点灯スイッチ素子9がなくても同様の効果は得られる。

また、走査線駆動回路22、信号線駆動回路21等からなる周辺駆動回路は、低温多結晶シリコン(ポリシリコン)薄膜トランジスタ回路で構成しているが、これらの周辺駆動回路あるいはその一部分を単結晶LSI(Large Scale Integrated circuit)回路で構成して実装するようにしてもよい。その場合に、駆動TFT4、リセットスイッチ素子5、および、点灯スイッチ素子9等は、それぞれ半導体層にアモルファスシリコンを用いるアモルファスシリコン薄膜トランジスタを用いてガラス基板上に構成するようにしてもよい。

図6において、データシフト手段31は、データクロックCK2に従い、一ライン分の表示入力シリアルデータData(図1の表示データ136)を、データスタート信号STを取り込み開始の基準として一水平期間中に取り込み、シフトデータとして出力する。

1ラインラッチ手段32は、シフトデータを1ライン分ラッチし、水平ラッチクロックCK1に同期して1ラインラッチデータとして出力する。

なお、データクロックCK2、データスタート信号ST、および、水平ラッチクロックCK1は、図1に示す信号線駆動回路制御信号137に含まれる信号である。また、一ライン分の表示入力シリアルデータDataは、図1の表示データ136に相当する。

階調電圧選択手段33は、1ラインラッチデータに従って256レベルの階調電圧のうちの1レベルを選択し、1ライン分の画像信号として出力する。

三角波生成手段35は、発光期間制御信号102と帰線期間信号38に従って、発光期間中に入力表示データと無関係な三角波波形のPWM信号36を生成し、出力するとともに、三角波波形のPWM信号36を信号線17に出力する期間を示す三角波切替信号37を生成する。

階調電圧−三角波切替手段34は、三角波切替信号37に従って、1ライン分の画像信号と三角波波形のPWM信号を切り替え、信号線17に出力する。

基準クロック生成手段51は、三角波波形のPWM信号を生成するための基準クロック52を生成する。

アップダウンカウント手段53は、発光期間制御信号102と帰線期間信号38の制御の元に、基準クロック52に同期して、初期値からカウントダウン、“0”となった後再び初期値に戻るまでカウントアップを行い、カウント出力54を出力する。

デジタル/アナログ変換手段55は、デジタルデータであるカウント出力54を、アナログ信号変換し、三角波波形のPWM信号36として出力する。

図7に示す回路では、アップダウンカウント手段53は、8ビットのカウンタであることとし、カウント開始の初期値は“255”、デジタル/アナログ変換手段55も8ビットデジタルデータに対応するものとする。

三角波切替信号生成手段56は、帰線期間信号38に基づき三角波切替信号37を生成する。

図8において、基準クロック52は、人力表示データ終了タイミングから人力表示データ開始タイミングまでの三角波期間(図8の帰線期間信号38の間のAの期間)の期間中に、最低限、アップダウンカウント手段53が、初期値“255”から“0”までカウントダウンし、その後再び“255”までカウントアッブするために必要なサイクル数を有するクロックとなる。

アップダウンカウント手段53から出力されるカウント出力54は、基準クロック52に従って、初期値“255”からカウントダウンを開始し、“0”となった後、再び初期値である“255”までカウントアップした値となる出力である。

デジタル/アナログ変換手段55から出力される三角波波形のPWM信号36は、“0”から“255”までを示す8ビットデジタルデータであるカウント出力54を、“0”のときを最低、“255”のときを最高レベルとするアナログ値に変換した信号である。

本発明では、輝度モード制御部100より、複数の輝度表示モードに切り換えるが、このとき、それぞれの輝度表示モードに応じて、最適の波形のPWM信号を使用するようにしたものである。

図9Aは、本実施例の有機EL表示装置の標準輝度モードにおけるPWM信号を説明するための図である。なお、図9A〜図9Dにおいて、書込み期間は、1表示ライン毎(あるいは、2表示ライン毎)に各画素に画像信号を書込む期間である。

本実施例の標準輝度モードでは、図9Aに示すように、発光期間に三角波波形(例えば、図3のCに示す波形)のPWM信号に代えて、A1〜A5の変曲点を有する放物線波形に近い波形のPWM信号を用いる。なお、本発明では、この変曲点とは、この変曲点を境に直線の傾きが異なる点を意味している。

本実施例では、変曲点を有する放物線波形に近い波形のPWM信号を用い、それぞれの輝度表示モードに応じて最適の変曲点を設定することにより、それぞれの輝度表示モードに応じて最適な輝度制御を行うことが可能となる。また、本実施例において、例えば、R・G・Bの各画素毎に、PWM信号の変曲点を設定することにより、赤、緑、青の各画素の発光輝度のバランスを調整することが可能となる。さらに、本実施例では、PWM信号の変曲点を適宜設定することにより、ガンマ調整も行うことが可能となる。但し、これらの場合には、赤、緑、青の各画素毎にそれぞれ異なるPWM信号を供給する必要があるので、赤、緑、青の各画素毎にPWM信号を供給する信号線17をそれぞれ分離する必要がある。

なお、図9Aに示すようなPWM信号を生成するには、例えば、図7に示す基準クロック生成手段51に、それぞれ周期の異なる複数のクロック生成回路を容易しておき、カウント数に応じて適宜切り換えて、図7に示す基準クロック生成手段51から出力することにより容易に実現可能である。

ここで、クロック生成回路51−1から出力されるクロックを用いて、16カウント数でアップダウン繰り返す場合、図10(b)のBに示すような、三角波波形のPWM信号が得られる。

また、1から4のカウント数の時に、クロック生成回路51−2から出力されるクロック、5から6のカウント数の時に、クロック生成回路51−1から出力されるクロック、7から10のカウント数の時に、クロック生成回路51−3ら出力されるクロック、11から12のカウント数の時に、クロック生成回路51−1から出力されるクロック、13から16のカウント数の時に、クロック生成回路51−2から出力されるクロックを用いて、16カウント数でアップダウン繰り返す場合、図10(b)のCに示すような、A1〜A5の変曲点を有する放物線波形に近い波形のPWM信号を得ることできる。

図9Bに示すように、本実施例の低輝度表示モードのPWM信号は、図9Aに示すPWM信号と同様に、A1〜A5の変曲点を有する放物線波形に近い波形のPWM信号であるが、図9Aに示すPWM信号に比して、周期が、図9Aに示すPWM信号の周期の約半分となっている。このようなPWMを信号を用いることにより、画像信号の書込から発光までの期間が短くなるので低輝度制御に最適な波形となっている。

なお、図9Bに示すようなPWM信号を生成するには、例えば、図10(a)に示すクロック生成回路51−1、クロック生成回路51−2、およびクロック生成回路51−3において、周期(T)を短くする(あるいは、クロック生成回路51−1で生成されるクロックの周波数を高かい周波数とする)ことで容易に実現可能である。

図9Cに示すように、本実施例の高輝度表示モードのPWM信号は、A1〜A4の変曲点を有し、矩形波に近い波形のPWM信号である。また、この高輝度表示モードでは、駆動TFT4を飽和領域で動作させる。

前述したように、Vddを電源線18の電圧、Vdataを画像信号の電圧、Vdsを駆動TFT4のソースードレイン間の電圧とするとき、下記(1)式を満足する場合、駆動TFT4は飽和領域で動作する。

(Vdd−Vdata)≦Vds ・・・・・・・・・・・・・・ (1)

駆動TFT4が飽和領域で動作する場合、ドレイン電流(ID)は、ゲート・ソース間電圧の2乗に比例するので、ガンマ調整が容易となる。なお、図11に、ガンマ値が1.0、1.8、2.0、2.2の時の、画像信号の信号レベルと輝度レベルのグラフを示す。

なお、図9Cに示すようなPWM信号を生成するには、発光期間制御信号102に基づき、アップダウンカウント手段53のダウン動作開始時と、アップ動作時に、アップダウンカウント手段53のダウン動作を制御するアップダウン制御信号を入力するようにすればよい。

図9Dに示すように、本実施例の最大輝度表示モードのPWM信号は、A1、A2の変曲点を有し、図9Cに示すPWM信号よりも、より矩形波に近い台形波波形のPWM信号である。また、この最大輝度表示モードでも、駆動TFT4を飽和領域で動作させる。

図9Dに示すように、この最大輝度表示モードでは、例えば、インタレース駆動により、画像信号の書込期間が、図9Cに示す高輝度表示モードの画像信号の書込期間の半分期間となっている。これにより、図9Cに示す高輝度表示モードに比して、より高輝度の画像を表示することが可能となる。

このインタレース駆動では、奇数番号の表示ライン上の画素に対する画像信号の書き込みと、偶数番号の表示ライン上の画素に対する画像信号の書き込みとが、1フレーム毎に交互に繰り返される。

例えば、奇数フレームでは、奇数番号の表示ライン上の画素に対する画像信号の書き込み行われ、偶数番号では、偶数番号の表示ライン上の画素に対する画像信号の書き込みが行われる。

「有機EL表示パネル」とは、サブ画素を構成する有機EL素子を備えた基板のことをいう。ここで、ドライバICが実装(実装方法は、チップオンガラス(COG)、テープキャリアパッケージ(TCP)、チップオンフィルム(COF)等)されている構造、半導体層がポリシリコンで構成される薄膜トランジスタによって基板上にドライバが内蔵されている構造、封止基板で封止された構造も含む。

「有機EL表示装置」は、有機EL表示パネルの他、この有機EL表示パネルのドライバを制御するタイミング制御回路や、電源回路などのインターフェ一スを含めた構造のことをいうものとする。

図12に、有機EL表示装置の外観を示す。

図12に示す有機EL表示装置は、有機EL表示パネル(以下、単にパネルとも称する。)の表示部ARが露出する開口を備えた前面フレーム(FF)と、有機EL表示パネルの裏面全体を覆い、前面フレーム(FF)とスナップフィットにより固定されている裏面フレーム(RF)と、裏面フレーム(RF)のさらに裏面に配置された回路基板(SUB)と有機EL表示パネルとの間に取り付けられたフレキシブル回路基板(FPC)を備えた構造である。

なお、回路基板(SUB)は、裏面フレーム(RF)に対して、接着剤や面面テープで固定してもよいし、さらに外部に設けた電子装置のフレームにねじ等で固定してもよい。

図13は、表示面斜上方から見た有機EL表示パネルの分解図である。図14は、図13に示す有機ELパネルの断面構造を示す断面図であり、同図(a)は、図13のA−A’切断線に沿った断面構造を示す断面図、同図(b)は図13のB−B’切断線に沿った断面構造を示す断面図である。

前面フレーム(FF)の側から、光学フィルム(OF)、有機EL表示パネル(PEL)、熱拡散シート&衝撃吸収剤(ADF)、裏面フレーム(RF)の順に積層されている。

前面フレーム(FF)と裏面フレーム(RF)は、鉄とニッケルを主成分とする金属で構成され、アンバーやインバーと呼ばれる鉄を約36%含有する材料で構成された合金で構成された金属フレームである。

なお、この金属は、インバーにニッケルを含有させたスーパーインバーと呼ばれる合金で構成された金属フレームでもよい。また、ステンレスや鉄を用いた場合、廉価で容易に製造できる。前面フレーム(FF)は、裏面フレーム(RF)に向かって折り曲げられた形状をしている。

半導体層がポリシコンから薄膜トランジスタの製造プロセスにより、ガラス基板(GLAS1)上にチャネル(FG)、ゲート絶縁膜(材料:P−TEOS)(GI)、ゲート配線(材料:MoW)(SG)、CONT絶縁膜(材料:P−TEOS)(PAS1)、SD配線(材料:金属/AlSi/金属)(AL)、パシベーション層(材料:P−SiN)(PAS2)からなる薄膜トランジスタ(TFT)を形成する。

薄膜トランジスタ(TFT)の形成については、nMOS単テャネルプロセスにカウンタードープpMOSプロセスを加えたCMOSプロセスで作製する。

薄膜トランジスタ(TFT)形成後に、有機EL素子7の下部電極の陽極(ITO)を形成する。ボトムエミッション型の有機EL表示パネル(PEL)は、光の取り出し方向を薄膜トランジスタ(TFT)基板側とするため、下部電極の陽極が透明電極であるITOとなっている。

陽極(ITO)の形成後に電極端部での陽極−陰極間のショートを防ぐためのSiNバンク(SiL2)(BANK)を形成する。

次に、有機EL素子工程(OLED工程)にてR・G・Bを打ち分けるため精密マスクを用いて有機EL層(ELS)を形成し、表示領域全体を覆う形で上部電極の陰極(AI)を形成する。陰極AIは反射層を兼ねている。

最後に有機EL素子の劣化要因となる水分の浸入を防ぐため乾燥剤(KZA)を貼り付けた封止ガラス(GLAS2)を、N2環境下で封止して有機EL表示パネル(PEL)パネルの完成となる。

半導体層がポリシコンから薄膜トランジスタの製造プロセスにより、ガラス基板(GLAS1)上にチャネル(FG)、ゲート絶縁膜(材料:P−TEOS)(GI)、ゲート配線(材料:MoW)(SG)、CONT絶縁膜(材料:P−TEOS)(PAS1)、SD配線(材料:金属/AlSi/金属)(AL)、パシベーション層(材料:P−SiN)(PAS2)からなる薄膜トランジスタ(TFT)を形成する。形成工程は、ボトムエミッション型の有機EL表示パネル(PEL)と同一である。

その後、パッシベーション層(PAS2)の上に薄膜トランジスタ(TFT)の形成によって生じた段差を平坦化するための有機層(平坦化層)(OC)を形成する。

トップエミッション型の有機EL表示パネル(PEL)は、光の取り出し方向が薄膜トランジスタ(TFT)基板の上側になるため、平坦化層(OC)を挿入すると画素回路に制限されることなく画素開口を配置することができる。このため、トップエミッション型の有機EL表示パネル(PEL)は高精細化が可能となる。

平坦化層(OC)には、窒化シリコンなどの無機膜やアクリル樹脂、ポリイミド樹脂などの有機膜が適用可能である。これは、ボトムエミッション型の有機EL表示パネル(PEL)でも同様である。

反射層にはAlSi(Si:1.0wt%以下)を用いるが、平坦化層(OC)は金属との密着性が悪いことから、MoW(Mo:80wt%,W:20wt‰)を下地として追加し,AlSi/MoWの2層構造とした。

SD配線(AL)と陽極(ITO)との電気的接続に関しては反射層(AM)を介して陽極(ITO)に接続する方法と、反射層(AM)を介さずに直接SD配線(AL)と陽極(ITO)を接続する方法が考えられるが、AlSiとITOはオーミック接続とならないため、直接SD配線(AL)と陽極(ITO)を接続することとした。

SD配線(AL)は、従来から陽極(ITO)との接続を考慮してキャップ金属を用いており、陽極(ITO)との接続については問題ない。

陽極(ITO)の形成後に、電極端部での陽極−陰極間ショートを防ぐためのSiNバンク(SiL2)(BANK)を形成する。

有機EL素子工程(OLED工程)にてR・G・Bを打ち分けるため精密マスクを用いて有機EL層(ELS)を形成し、表示領域全体を覆う形で上部電極の透明陰極(IZO)を形成する。

光学干渉のため透明陰極(IZO)は薄膜化する必要があり、透明陰極(IZO)の抵抗が問題となる。そこで画素と画素の間に補助電極(HSD)を形成する。

最後に有機EL素子の劣化要因となる水分の浸入を防ぐため乾燥剤(図示せず)を貼り付けたガラス基板(GLAS2)を、N2環境下で封止して有機EL表示パネル(PEL)パネルの完成となる。

なお、ELディスプレイには、パソコン用ディスプレイ、TV放送受信用ディスプレイ、広告表示用ディスプレイ等の全ての情報表示用ディスプレイが含まれる。また、その他にも様々な電子装置の表示部として本発明の有機EL表示装置を用いることができる。その様な電子装置としては、ビデオカメラ、デジタルカメラ、カーナビゲーションシステム、カーオーディオ、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置などが挙げられる。

特に、斜め方向から見ることの多い携帯情報端末は視野角の広さが重要視されるため、有機EL表示装置を用いることが望ましい。それら電子装置の具体例を以下に示す。

図17は、携帯電話であり、本実施例の有機EL表示装置は表示部に用いることができる。なお、表示部は黒色の背景に白色の文字を表示することで携帯電話の消費電力を抑えることができる。図18は、デジタルステルカメラであり、本実施例の有機EL表示装置は表示部に用いることができる。また、有機EL表示装置は発光している部分が電力を消費するため、発光部分が極力少なくなるように情報を表示することが望ましい。

図19は、デジタルビデオカメラであり、本実施例の有機EL表示装置は表示部に用いることができる。図20はカーナビゲーションシステムであり、本実施例の有機EL表示装置は表示部に用いることができる。

以上の様に、本実施例の有機EL表示装置の適用範囲は極めて広く、あらゆる分野の電子装置に用いることが可能である。

本実施例の有機EL表示装置において、複数の発光輝度設定(例えば、最大表示輝度:500cd/m2、輝度表示モード:RGB各50ステップ(各ステップ内で256階調):輝度ステップ≦10cd/m2)が必要な場合、電源制御部111での電圧制御により変動した階調特性をPWM信号の変曲点を所定の階調特性に合わせて規定することにより、高コントラストかつ正確な階調性能を得ることができる。

また、高輝度表示モード時に、PWM信号を飽和領域駆動に切り替えることで、所定の輝度を得ることができ屋外視認性が向上する。さらに、飽和駆動に切り替えることで、非飽和領域駆動に対して、配線抵抗による電圧降下に起因する面内輝度むら(シェーディング)や焼付き発生時間を大幅に低減することもできる。

また、RGB各色の陽極電源部110が共通であっても、RGBの各画素を独立で階調制御が可能となり、高品位な表示装置の提供が可能となる。

さらに、本実施例においては、各画素のガンマ調整を行うことにより、適宜制御された発光輝度で発光するEL素子を有する有機EL表示装置が作製される。

以上、本発明者によってなされた発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

4 p型薄膜トランジスタ(駆動TFT)

5 リセットスイッチ素子

7 有機エレクトロルミネッセンス素子(有機EL素子)

9 点灯スイッチ素子

10 画素

17 信号線

15 リセット線

19 点灯スイッチ線

18 電源線

21 信号線駆動回路

22 走査線駆動回路

31 データシフト手段

32 1ラインラッチ手段

33 階調電圧選択手段

34 階調電圧−三角波切替手段

35 三角波生成手段

51 基準クロック生成手段

51−1,51−2,51−3 クロック生成回路

53 アップダウンカウント手段

55 デジタル/アナログ変換手段

56 三角波切替信号生成手段

100 輝度モード制御部

110 陽極電源部

111 電源制御部

120 陰極電源部

121 陰極電源線

130 表示制御部

AR 表示部

INV 駆動インバータ

FF 前面フレーム

RF 裏面フレーム

SUB 回路基板

FPC フレキシブル回路基板

OF 光学フィルム

PEL 有機EL表示パネル

ADF 熱拡散シート&衝撃吸収剤

GLAS1,GLAS2 ガラス基板

FG チャネル

GI ゲート絶縁膜

SG ゲート配線

PAS1 CONT絶縁膜

AL SD配線

PAS2 パシベーション層

TFT 薄膜トランジスタ

OC 有機層(平坦化層)

ITO 陽極

BANK SiNバンク

ELS 有機EL層

AI 陰極

KAZ 乾燥剤

AM 反射層

HSD 補助電極

Claims (7)

- 自発光素子を有する画素をマトリクス状に設けた表示領域と、

前記自発光素子の陽極である第一電極に供給される第一電源電圧を生成する陽極電源部と、

前記自発光素子の陰極である第二電極に供給される第二電圧を生成する陰極電源部と、

リセット線が接続する走査線駆動回路と、

画像信号と、発光時間の制御を行う信号を供給する信号線駆動回路とを有し、

画素容量の第一電極がゲート電極に接続され、前記第一電源電圧がソース電極に入力され、前記自発光素子の第一電極がドレイン電極に接続された駆動トランジスタと、

前記駆動トランジスタのゲート電極とドレイン電極間に、ソース電極とドレイン電極が接続されたリセットスイッチ素子を有し、

前記自発光素子の第二電極には前記第二電圧が入力され、

前記リセットスイッチ素子のゲート電極には前記リセット線が接続され、

1フレーム期間内に前記各画素に前記画像信号を書込む書込み期間と、前記自発光素子を発光させる発光期間とを有し、

前記書込み期間に、前記画像信号を前記画素容量の第二電極に入力し、前記発光期間に、前記全画素の前記リセットスイッチ素子をオフとして、前記発光時間の制御を行う信号を前記画素容量の第二電極に入力する画像表示装置であって、

輝度モード制御回路で制御される2つ以上の輝度表示モードを有し、

前記輝度表示モードには、前記発光期間における前記発光時間の制御を行う信号の波形を台形波形として高輝度で表示する第一の輝度表示モードと、前記発光期間における前記発光時間の制御を行う信号の波形を前記第一の輝度表示モードよりも放物線波形に近い波形として低輝度で表示する第二の輝度表示モードを有することを特徴とする画像表示装置。 - 前記第一の輝度表示モードでは前記駆動トランジスタが飽和領域で前記自発光素子を発光させ、前記第二の輝度表示モードでは前記駆動トランジスタは非飽和領域で前記自発光素子を発光させることを特徴とする請求項1に記載の画像表示装置。

- 前記第二の輝度表示モードにおける前記発光時間の制御を行う信号の波形は、複数の変極点を有する多角形であることを特徴とする請求項1に記載の画像表示装置。

- 前記第二の輝度表示モードにおける前記発光時間の制御を行う信号の波形は、複数の変極点を有する放物線波形であることを特徴とする請求項3に記載の画像表示装置。

- 前記発光時間の制御を行う信号の波形は、各画素における前記自発光素子の発光色によって波形が異なることを特徴とする請求項1に記載の画像表示装置。

- 前記輝度表示モードには、前記発光期間における前記発光時間の制御を行う信号の波形の形状が異なる複数の輝度表示モードを有することを特徴とする請求項1に記載の画像表示装置。

- 前記輝度表示モードは、外光の明るさを検出して自動的に選択可能であることを特徴とする請求項1に記載の画像表示装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008208614A JP5346520B2 (ja) | 2008-08-13 | 2008-08-13 | 画像表示装置 |

| US12/538,963 US8248333B2 (en) | 2008-08-13 | 2009-08-11 | Display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008208614A JP5346520B2 (ja) | 2008-08-13 | 2008-08-13 | 画像表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010044250A JP2010044250A (ja) | 2010-02-25 |

| JP2010044250A5 JP2010044250A5 (ja) | 2011-08-25 |

| JP5346520B2 true JP5346520B2 (ja) | 2013-11-20 |

Family

ID=41681047

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008208614A Active JP5346520B2 (ja) | 2008-08-13 | 2008-08-13 | 画像表示装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8248333B2 (ja) |

| JP (1) | JP5346520B2 (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010145709A (ja) * | 2008-12-18 | 2010-07-01 | Hitachi Displays Ltd | 画像表示装置 |

| JP2012093434A (ja) * | 2010-10-25 | 2012-05-17 | Canon Inc | 表示装置の駆動方法 |

| KR20140058283A (ko) * | 2012-11-06 | 2014-05-14 | 삼성디스플레이 주식회사 | 표시 장치 및 표시 장치의 구동 방법 |

| KR102109166B1 (ko) | 2013-01-15 | 2020-05-12 | 삼성디스플레이 주식회사 | 박막 트랜지스터 및 이를 구비하는 표시 기판 |

| US9881554B2 (en) | 2015-02-11 | 2018-01-30 | Boe Technology Group Co., Ltd. | Driving method of pixel circuit and driving device thereof |

| CN104599637A (zh) * | 2015-02-11 | 2015-05-06 | 京东方科技集团股份有限公司 | 一种像素电路的驱动方法及其驱动装置 |

| JP2016212239A (ja) * | 2015-05-08 | 2016-12-15 | ソニー株式会社 | 表示装置、表示方法、および電子機器 |

| CN105070248B (zh) * | 2015-09-08 | 2017-05-31 | 深圳市华星光电技术有限公司 | 提高画面对比度的oled驱动系统及驱动方法 |

| US11328655B2 (en) | 2017-03-06 | 2022-05-10 | Sony Semiconductor Solutions Corporation | Drive device and display apparatus |

| JP7335066B2 (ja) * | 2017-11-02 | 2023-08-29 | シナプティクス インコーポレイテッド | 表示ドライバ、表示装置及び輝度制御方法 |

| TWI683434B (zh) * | 2018-09-21 | 2020-01-21 | 友達光電股份有限公司 | 畫素結構 |

| CN112750397B (zh) * | 2019-10-31 | 2022-04-12 | 京东方科技集团股份有限公司 | 显示面板及其驱动方法、显示装置 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001092413A (ja) | 1999-09-24 | 2001-04-06 | Semiconductor Energy Lab Co Ltd | El表示装置および電子装置 |

| JP2003005703A (ja) | 2001-06-22 | 2003-01-08 | Pioneer Electronic Corp | パネル駆動装置 |

| JP2004341144A (ja) * | 2003-05-15 | 2004-12-02 | Hitachi Ltd | 画像表示装置 |

| JP4804711B2 (ja) * | 2003-11-21 | 2011-11-02 | 株式会社 日立ディスプレイズ | 画像表示装置 |

| JP4203656B2 (ja) * | 2004-01-16 | 2009-01-07 | カシオ計算機株式会社 | 表示装置及び表示パネルの駆動方法 |

| JP2005316110A (ja) | 2004-04-28 | 2005-11-10 | Toshiba Matsushita Display Technology Co Ltd | 有機el表示装置及び電子機器 |

| US8115705B2 (en) * | 2004-05-17 | 2012-02-14 | Global Oled Technology Llc | Display device |

| US8681077B2 (en) * | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| US7652646B2 (en) * | 2006-04-14 | 2010-01-26 | Tpo Displays Corp. | Systems for displaying images involving reduced mura |

| JP2009047778A (ja) * | 2007-08-15 | 2009-03-05 | Hitachi Displays Ltd | 画像表示装置 |

-

2008

- 2008-08-13 JP JP2008208614A patent/JP5346520B2/ja active Active

-

2009

- 2009-08-11 US US12/538,963 patent/US8248333B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010044250A (ja) | 2010-02-25 |

| US20100039454A1 (en) | 2010-02-18 |

| US8248333B2 (en) | 2012-08-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5346520B2 (ja) | 画像表示装置 | |

| US10923030B2 (en) | EL display apparatus | |

| JP4146421B2 (ja) | El表示装置およびel表示装置の駆動方法 | |

| KR102207190B1 (ko) | 영상 처리 방법 및 영상 처리 회로와, 그를 이용한 표시 장치 | |

| US20100060554A1 (en) | Display apparatus and method of driving the same | |

| KR20070057020A (ko) | 화상 표시 장치 | |

| US20180061320A1 (en) | Organic light emitting diode display device and driving method thereof | |

| US8847999B2 (en) | Display device, method for driving the same, and electronic unit | |

| US11854495B2 (en) | Display device and display driving method | |

| US11830443B2 (en) | Display device, display panel, and display driving method having operation at a low driving frequency | |

| JP2011118301A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| US11450265B2 (en) | Display device and driving method of the same | |

| JP2008052289A (ja) | 発光装置及び電子機器 | |

| JP2011013340A (ja) | 発光素子表示装置及び表示方法 | |

| US11935475B2 (en) | Display device, driving circuit and display driving method | |

| US20110109817A1 (en) | Display device, method of driving the same, and electronic unit | |

| KR20140075352A (ko) | 유기발광소자표시장치 및 그 구동방법 | |

| JP2006030289A (ja) | El表示装置 | |

| JP6119185B2 (ja) | 画像データ処理回路及び電子機器 | |

| US11830442B2 (en) | Gamma voltage generating circuit for use in display device having first and second pixel areas, and display device including the same | |

| TWI764413B (zh) | 具自校正功能的顯示驅動電路及利用其之平面顯示器和資訊處理裝置 | |

| JP2011118125A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| KR20230018822A (ko) | 디스플레이 장치 및 그 구동 방법 | |

| KR20230099113A (ko) | 표시장치 및 표시장치의 구동 방법 | |

| KR20230081043A (ko) | 디스플레이 장치 및 그 구동 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20110218 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20110218 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110706 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110706 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120926 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130212 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130411 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130430 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130628 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130723 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130819 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5346520 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |