JP5255801B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP5255801B2 JP5255801B2 JP2007232503A JP2007232503A JP5255801B2 JP 5255801 B2 JP5255801 B2 JP 5255801B2 JP 2007232503 A JP2007232503 A JP 2007232503A JP 2007232503 A JP2007232503 A JP 2007232503A JP 5255801 B2 JP5255801 B2 JP 5255801B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor film

- semiconductor

- film

- substrate

- tray

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 635

- 238000000034 method Methods 0.000 title claims description 84

- 238000004519 manufacturing process Methods 0.000 title claims description 70

- 239000000758 substrate Substances 0.000 claims description 304

- 238000005192 partition Methods 0.000 claims description 48

- 239000013078 crystal Substances 0.000 claims description 39

- 150000002500 ions Chemical class 0.000 claims description 30

- 238000005530 etching Methods 0.000 claims description 28

- 238000003776 cleavage reaction Methods 0.000 claims description 10

- 230000007017 scission Effects 0.000 claims description 10

- 239000010408 film Substances 0.000 description 686

- 239000002585 base Substances 0.000 description 83

- 239000010410 layer Substances 0.000 description 76

- 239000007789 gas Substances 0.000 description 50

- 239000012535 impurity Substances 0.000 description 47

- 239000001257 hydrogen Substances 0.000 description 37

- 229910052739 hydrogen Inorganic materials 0.000 description 37

- 230000007547 defect Effects 0.000 description 32

- -1 fluorine or chlorine Chemical class 0.000 description 31

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 25

- 229910052581 Si3N4 Inorganic materials 0.000 description 21

- 229920005989 resin Polymers 0.000 description 21

- 239000011347 resin Substances 0.000 description 21

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 21

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 19

- 238000010438 heat treatment Methods 0.000 description 19

- 229910052710 silicon Inorganic materials 0.000 description 19

- 239000010703 silicon Substances 0.000 description 19

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 17

- 229910052782 aluminium Inorganic materials 0.000 description 17

- 229910052814 silicon oxide Inorganic materials 0.000 description 16

- 239000010936 titanium Substances 0.000 description 16

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 15

- 239000000463 material Substances 0.000 description 12

- 229910052751 metal Inorganic materials 0.000 description 12

- 239000002184 metal Substances 0.000 description 12

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 11

- CSDREXVUYHZDNP-UHFFFAOYSA-N alumanylidynesilicon Chemical compound [Al].[Si] CSDREXVUYHZDNP-UHFFFAOYSA-N 0.000 description 11

- 239000000969 carrier Substances 0.000 description 11

- 239000011521 glass Substances 0.000 description 11

- 239000000203 mixture Substances 0.000 description 11

- 238000012545 processing Methods 0.000 description 11

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 10

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 10

- 229920001940 conductive polymer Polymers 0.000 description 10

- 239000004973 liquid crystal related substance Substances 0.000 description 10

- 229910000077 silane Inorganic materials 0.000 description 10

- 238000003860 storage Methods 0.000 description 10

- 229910052719 titanium Inorganic materials 0.000 description 10

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 9

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 9

- 230000001133 acceleration Effects 0.000 description 9

- 230000004888 barrier function Effects 0.000 description 9

- 239000001301 oxygen Substances 0.000 description 9

- 229910052760 oxygen Inorganic materials 0.000 description 9

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 9

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 8

- 230000001070 adhesive effect Effects 0.000 description 8

- 238000000137 annealing Methods 0.000 description 8

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 8

- 230000015572 biosynthetic process Effects 0.000 description 8

- 239000000701 coagulant Substances 0.000 description 8

- 230000006870 function Effects 0.000 description 8

- 238000002513 implantation Methods 0.000 description 8

- 238000005468 ion implantation Methods 0.000 description 8

- 229910052750 molybdenum Inorganic materials 0.000 description 8

- 239000011733 molybdenum Substances 0.000 description 8

- 238000009832 plasma treatment Methods 0.000 description 8

- 229910052721 tungsten Inorganic materials 0.000 description 8

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 7

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 7

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 7

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 7

- 238000006243 chemical reaction Methods 0.000 description 7

- 239000000460 chlorine Substances 0.000 description 7

- 229910052801 chlorine Inorganic materials 0.000 description 7

- 150000001875 compounds Chemical class 0.000 description 7

- 229910052731 fluorine Inorganic materials 0.000 description 7

- 239000011737 fluorine Substances 0.000 description 7

- 229910052736 halogen Inorganic materials 0.000 description 7

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 7

- 238000005498 polishing Methods 0.000 description 7

- 239000011148 porous material Substances 0.000 description 7

- 238000007789 sealing Methods 0.000 description 7

- 239000002356 single layer Substances 0.000 description 7

- 239000002904 solvent Substances 0.000 description 7

- 239000010937 tungsten Substances 0.000 description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 239000010949 copper Substances 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 6

- 230000005684 electric field Effects 0.000 description 6

- 229910052734 helium Inorganic materials 0.000 description 6

- 238000005984 hydrogenation reaction Methods 0.000 description 6

- 150000002894 organic compounds Chemical class 0.000 description 6

- 229920001721 polyimide Polymers 0.000 description 6

- 238000000926 separation method Methods 0.000 description 6

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 6

- 239000004642 Polyimide Substances 0.000 description 5

- 229910021529 ammonia Inorganic materials 0.000 description 5

- 239000012298 atmosphere Substances 0.000 description 5

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 239000011651 chromium Substances 0.000 description 5

- 150000002367 halogens Chemical class 0.000 description 5

- 239000001307 helium Substances 0.000 description 5

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- 229910021332 silicide Inorganic materials 0.000 description 5

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- 229910052715 tantalum Inorganic materials 0.000 description 5

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 5

- 238000012546 transfer Methods 0.000 description 5

- 238000007740 vapor deposition Methods 0.000 description 5

- WZJUBBHODHNQPW-UHFFFAOYSA-N 2,4,6,8-tetramethyl-1,3,5,7,2$l^{3},4$l^{3},6$l^{3},8$l^{3}-tetraoxatetrasilocane Chemical compound C[Si]1O[Si](C)O[Si](C)O[Si](C)O1 WZJUBBHODHNQPW-UHFFFAOYSA-N 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 4

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 4

- 239000000853 adhesive Substances 0.000 description 4

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 4

- 150000001342 alkaline earth metals Chemical class 0.000 description 4

- 125000004429 atom Chemical group 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 238000000576 coating method Methods 0.000 description 4

- 239000004020 conductor Substances 0.000 description 4

- 230000005281 excited state Effects 0.000 description 4

- 239000000945 filler Substances 0.000 description 4

- 229910052732 germanium Inorganic materials 0.000 description 4

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 4

- 230000005283 ground state Effects 0.000 description 4

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 4

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 230000001678 irradiating effect Effects 0.000 description 4

- HMMGMWAXVFQUOA-UHFFFAOYSA-N octamethylcyclotetrasiloxane Chemical compound C[Si]1(C)O[Si](C)(C)O[Si](C)(C)O[Si](C)(C)O1 HMMGMWAXVFQUOA-UHFFFAOYSA-N 0.000 description 4

- 239000011368 organic material Substances 0.000 description 4

- 230000001590 oxidative effect Effects 0.000 description 4

- 229910052698 phosphorus Inorganic materials 0.000 description 4

- 239000011574 phosphorus Substances 0.000 description 4

- CZDYPVPMEAXLPK-UHFFFAOYSA-N tetramethylsilane Chemical compound C[Si](C)(C)C CZDYPVPMEAXLPK-UHFFFAOYSA-N 0.000 description 4

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 3

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 3

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 3

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 3

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 3

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 3

- OKKJLVBELUTLKV-UHFFFAOYSA-N Methanol Chemical compound OC OKKJLVBELUTLKV-UHFFFAOYSA-N 0.000 description 3

- ZMXDDKWLCZADIW-UHFFFAOYSA-N N,N-Dimethylformamide Chemical compound CN(C)C=O ZMXDDKWLCZADIW-UHFFFAOYSA-N 0.000 description 3

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 3

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 3

- 239000002253 acid Substances 0.000 description 3

- 229910052783 alkali metal Inorganic materials 0.000 description 3

- 150000001340 alkali metals Chemical class 0.000 description 3

- 238000004458 analytical method Methods 0.000 description 3

- 229910052799 carbon Inorganic materials 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 210000002858 crystal cell Anatomy 0.000 description 3

- 239000002019 doping agent Substances 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- 229910010272 inorganic material Inorganic materials 0.000 description 3

- 238000005499 laser crystallization Methods 0.000 description 3

- 239000010955 niobium Substances 0.000 description 3

- 238000005121 nitriding Methods 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 229920001707 polybutylene terephthalate Polymers 0.000 description 3

- 229920000139 polyethylene terephthalate Polymers 0.000 description 3

- 239000005020 polyethylene terephthalate Substances 0.000 description 3

- 238000002360 preparation method Methods 0.000 description 3

- 239000000565 sealant Substances 0.000 description 3

- 230000008054 signal transmission Effects 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 229920001187 thermosetting polymer Polymers 0.000 description 3

- QENGPZGAWFQWCZ-UHFFFAOYSA-N 3-Methylthiophene Chemical compound CC=1C=CSC=1 QENGPZGAWFQWCZ-UHFFFAOYSA-N 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- LSNNMFCWUKXFEE-UHFFFAOYSA-M Bisulfite Chemical compound OS([O-])=O LSNNMFCWUKXFEE-UHFFFAOYSA-M 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- 239000002841 Lewis acid Substances 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 239000004696 Poly ether ether ketone Substances 0.000 description 2

- 239000004697 Polyetherimide Substances 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 125000000217 alkyl group Chemical group 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 2

- 238000001505 atmospheric-pressure chemical vapour deposition Methods 0.000 description 2

- ILAHWRKJUDSMFH-UHFFFAOYSA-N boron tribromide Chemical compound BrB(Br)Br ILAHWRKJUDSMFH-UHFFFAOYSA-N 0.000 description 2

- WTEOIRVLGSZEPR-UHFFFAOYSA-N boron trifluoride Chemical compound FB(F)F WTEOIRVLGSZEPR-UHFFFAOYSA-N 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 150000001732 carboxylic acid derivatives Chemical class 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 238000003486 chemical etching Methods 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 229920001577 copolymer Polymers 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- JHIVVAPYMSGYDF-UHFFFAOYSA-N cyclohexanone Chemical compound O=C1CCCCC1 JHIVVAPYMSGYDF-UHFFFAOYSA-N 0.000 description 2

- 230000005674 electromagnetic induction Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 230000005284 excitation Effects 0.000 description 2

- 239000002360 explosive Substances 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 150000002366 halogen compounds Chemical class 0.000 description 2

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 2

- 230000005525 hole transport Effects 0.000 description 2

- 150000002431 hydrogen Chemical class 0.000 description 2

- 238000009616 inductively coupled plasma Methods 0.000 description 2

- 150000002484 inorganic compounds Chemical class 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 150000007517 lewis acids Chemical class 0.000 description 2

- 238000004020 luminiscence type Methods 0.000 description 2

- 239000011572 manganese Substances 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 2

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 2

- 229910021334 nickel silicide Inorganic materials 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- RNVCVTLRINQCPJ-UHFFFAOYSA-N o-toluidine Chemical compound CC1=CC=CC=C1N RNVCVTLRINQCPJ-UHFFFAOYSA-N 0.000 description 2

- 150000001282 organosilanes Chemical class 0.000 description 2

- 230000010355 oscillation Effects 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- VLTRZXGMWDSKGL-UHFFFAOYSA-N perchloric acid Chemical compound OCl(=O)(=O)=O VLTRZXGMWDSKGL-UHFFFAOYSA-N 0.000 description 2

- 229920002492 poly(sulfone) Polymers 0.000 description 2

- 229920000767 polyaniline Polymers 0.000 description 2

- 229920001230 polyarylate Polymers 0.000 description 2

- 229920002530 polyetherether ketone Polymers 0.000 description 2

- 229920001601 polyetherimide Polymers 0.000 description 2

- 239000011112 polyethylene naphthalate Substances 0.000 description 2

- 229920000128 polypyrrole Polymers 0.000 description 2

- 229920000123 polythiophene Polymers 0.000 description 2

- 239000011118 polyvinyl acetate Substances 0.000 description 2

- 229920002689 polyvinyl acetate Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 150000003254 radicals Chemical class 0.000 description 2

- 239000010979 ruby Substances 0.000 description 2

- 229910001750 ruby Inorganic materials 0.000 description 2

- 239000002210 silicon-based material Substances 0.000 description 2

- 238000003746 solid phase reaction Methods 0.000 description 2

- 241000894007 species Species 0.000 description 2

- 239000010935 stainless steel Substances 0.000 description 2

- 229910001220 stainless steel Inorganic materials 0.000 description 2

- 125000001424 substituent group Chemical group 0.000 description 2

- 229920003002 synthetic resin Polymers 0.000 description 2

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 2

- VZGDMQKNWNREIO-UHFFFAOYSA-N tetrachloromethane Chemical compound ClC(Cl)(Cl)Cl VZGDMQKNWNREIO-UHFFFAOYSA-N 0.000 description 2

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 2

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 2

- QQQSFSZALRVCSZ-UHFFFAOYSA-N triethoxysilane Chemical compound CCO[SiH](OCC)OCC QQQSFSZALRVCSZ-UHFFFAOYSA-N 0.000 description 2

- 238000001947 vapour-phase growth Methods 0.000 description 2

- 239000011800 void material Substances 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- ZPOROQKDAPEMOL-UHFFFAOYSA-N 1h-pyrrol-3-ol Chemical compound OC=1C=CNC=1 ZPOROQKDAPEMOL-UHFFFAOYSA-N 0.000 description 1

- UCDCWSBXWOGCKR-UHFFFAOYSA-N 2-(2-methylpropyl)aniline Chemical compound CC(C)CC1=CC=CC=C1N UCDCWSBXWOGCKR-UHFFFAOYSA-N 0.000 description 1

- ZMCHBSMFKQYNKA-UHFFFAOYSA-N 2-aminobenzenesulfonic acid Chemical compound NC1=CC=CC=C1S(O)(=O)=O ZMCHBSMFKQYNKA-UHFFFAOYSA-N 0.000 description 1

- RUUWTSREEUTULQ-UHFFFAOYSA-N 2-octylaniline Chemical compound CCCCCCCCC1=CC=CC=C1N RUUWTSREEUTULQ-UHFFFAOYSA-N 0.000 description 1

- LGPVKMIWERPYIJ-UHFFFAOYSA-N 3,4-dibutyl-1h-pyrrole Chemical compound CCCCC1=CNC=C1CCCC LGPVKMIWERPYIJ-UHFFFAOYSA-N 0.000 description 1

- OJFOWGWQOFZNNJ-UHFFFAOYSA-N 3,4-dimethyl-1h-pyrrole Chemical compound CC1=CNC=C1C OJFOWGWQOFZNNJ-UHFFFAOYSA-N 0.000 description 1

- JSOMPMRZESLPSM-UHFFFAOYSA-N 3-(2-methylpropyl)aniline Chemical compound CC(C)CC1=CC=CC(N)=C1 JSOMPMRZESLPSM-UHFFFAOYSA-N 0.000 description 1

- ZAJAQTYSTDTMCU-UHFFFAOYSA-N 3-aminobenzenesulfonic acid Chemical compound NC1=CC=CC(S(O)(=O)=O)=C1 ZAJAQTYSTDTMCU-UHFFFAOYSA-N 0.000 description 1

- ATWNFFKGYPYZPJ-UHFFFAOYSA-N 3-butyl-1h-pyrrole Chemical compound CCCCC=1C=CNC=1 ATWNFFKGYPYZPJ-UHFFFAOYSA-N 0.000 description 1

- KPOCSQCZXMATFR-UHFFFAOYSA-N 3-butylthiophene Chemical compound CCCCC=1C=CSC=1 KPOCSQCZXMATFR-UHFFFAOYSA-N 0.000 description 1

- FFRZVVFLHHGORC-UHFFFAOYSA-N 3-decyl-1h-pyrrole Chemical compound CCCCCCCCCCC=1C=CNC=1 FFRZVVFLHHGORC-UHFFFAOYSA-N 0.000 description 1

- JAYBIBLZTQMCAY-UHFFFAOYSA-N 3-decylthiophene Chemical compound CCCCCCCCCCC=1C=CSC=1 JAYBIBLZTQMCAY-UHFFFAOYSA-N 0.000 description 1

- RFKWIEFTBMACPZ-UHFFFAOYSA-N 3-dodecylthiophene Chemical compound CCCCCCCCCCCCC=1C=CSC=1 RFKWIEFTBMACPZ-UHFFFAOYSA-N 0.000 description 1

- KEAYXGHOGPUYPB-UHFFFAOYSA-N 3-ethoxy-1h-pyrrole Chemical compound CCOC=1C=CNC=1 KEAYXGHOGPUYPB-UHFFFAOYSA-N 0.000 description 1

- OTODBDQJLMYYKQ-UHFFFAOYSA-N 3-methoxy-1h-pyrrole Chemical compound COC=1C=CNC=1 OTODBDQJLMYYKQ-UHFFFAOYSA-N 0.000 description 1

- FEKWWZCCJDUWLY-UHFFFAOYSA-N 3-methyl-1h-pyrrole Chemical compound CC=1C=CNC=1 FEKWWZCCJDUWLY-UHFFFAOYSA-N 0.000 description 1

- YIRWZHZOCIDDAH-UHFFFAOYSA-N 3-octoxy-1h-pyrrole Chemical compound CCCCCCCCOC=1C=CNC=1 YIRWZHZOCIDDAH-UHFFFAOYSA-N 0.000 description 1

- AUVZKIJQGLYISA-UHFFFAOYSA-N 3-octoxythiophene Chemical compound CCCCCCCCOC=1C=CSC=1 AUVZKIJQGLYISA-UHFFFAOYSA-N 0.000 description 1

- WFHVTZRAIPYMMO-UHFFFAOYSA-N 3-octyl-1h-pyrrole Chemical compound CCCCCCCCC=1C=CNC=1 WFHVTZRAIPYMMO-UHFFFAOYSA-N 0.000 description 1

- PRPLKAUMELMCKP-UHFFFAOYSA-N 4-methyl-1h-pyrrol-3-ol Chemical compound CC1=CNC=C1O PRPLKAUMELMCKP-UHFFFAOYSA-N 0.000 description 1

- FXPOCCDGHHTZAO-UHFFFAOYSA-N 4-methyl-1h-pyrrole-3-carboxylic acid Chemical compound CC1=CNC=C1C(O)=O FXPOCCDGHHTZAO-UHFFFAOYSA-N 0.000 description 1

- LRFIHWGUGBXFEC-UHFFFAOYSA-N 4-methylthiophene-3-carboxylic acid Chemical compound CC1=CSC=C1C(O)=O LRFIHWGUGBXFEC-UHFFFAOYSA-N 0.000 description 1

- 241001270131 Agaricus moelleri Species 0.000 description 1

- 229910021630 Antimony pentafluoride Inorganic materials 0.000 description 1

- 229910015900 BF3 Inorganic materials 0.000 description 1

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 description 1

- 239000004215 Carbon black (E152) Substances 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- 229910052691 Erbium Inorganic materials 0.000 description 1

- QZRGKCOWNLSUDK-UHFFFAOYSA-N Iodochlorine Chemical compound ICl QZRGKCOWNLSUDK-UHFFFAOYSA-N 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- 229920000877 Melamine resin Polymers 0.000 description 1

- NTIZESTWPVYFNL-UHFFFAOYSA-N Methyl isobutyl ketone Chemical compound CC(C)CC(C)=O NTIZESTWPVYFNL-UHFFFAOYSA-N 0.000 description 1

- UIHCLUNTQKBZGK-UHFFFAOYSA-N Methyl isobutyl ketone Natural products CCC(C)C(C)=O UIHCLUNTQKBZGK-UHFFFAOYSA-N 0.000 description 1

- FXHOOIRPVKKKFG-UHFFFAOYSA-N N,N-Dimethylacetamide Chemical compound CN(C)C(C)=O FXHOOIRPVKKKFG-UHFFFAOYSA-N 0.000 description 1

- SECXISVLQFMRJM-UHFFFAOYSA-N N-Methylpyrrolidone Chemical compound CN1CCCC1=O SECXISVLQFMRJM-UHFFFAOYSA-N 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 229920000571 Nylon 11 Polymers 0.000 description 1

- 229920000299 Nylon 12 Polymers 0.000 description 1

- 229920002292 Nylon 6 Polymers 0.000 description 1

- 229920002302 Nylon 6,6 Polymers 0.000 description 1

- CTQNGGLPUBDAKN-UHFFFAOYSA-N O-Xylene Chemical compound CC1=CC=CC=C1C CTQNGGLPUBDAKN-UHFFFAOYSA-N 0.000 description 1

- 239000002033 PVDF binder Substances 0.000 description 1

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 1

- 229920000280 Poly(3-octylthiophene) Polymers 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004962 Polyamide-imide Substances 0.000 description 1

- 239000004743 Polypropylene Substances 0.000 description 1

- 229920002396 Polyurea Polymers 0.000 description 1

- 239000004372 Polyvinyl alcohol Substances 0.000 description 1

- 229910004283 SiO 4 Inorganic materials 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- 238000005411 Van der Waals force Methods 0.000 description 1

- 229910052769 Ytterbium Inorganic materials 0.000 description 1

- XECAHXYUAAWDEL-UHFFFAOYSA-N acrylonitrile butadiene styrene Chemical compound C=CC=C.C=CC#N.C=CC1=CC=CC=C1 XECAHXYUAAWDEL-UHFFFAOYSA-N 0.000 description 1

- 239000004676 acrylonitrile butadiene styrene Substances 0.000 description 1

- 229920000122 acrylonitrile butadiene styrene Polymers 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 239000005354 aluminosilicate glass Substances 0.000 description 1

- VBVBHWZYQGJZLR-UHFFFAOYSA-I antimony pentafluoride Chemical compound F[Sb](F)(F)(F)F VBVBHWZYQGJZLR-UHFFFAOYSA-I 0.000 description 1

- 239000004760 aramid Substances 0.000 description 1

- 229920003235 aromatic polyamide Polymers 0.000 description 1

- 239000003849 aromatic solvent Substances 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- YBGKQGSCGDNZIB-UHFFFAOYSA-N arsenic pentafluoride Chemical compound F[As](F)(F)(F)F YBGKQGSCGDNZIB-UHFFFAOYSA-N 0.000 description 1

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- 239000005380 borophosphosilicate glass Substances 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 description 1

- 229910052794 bromium Inorganic materials 0.000 description 1

- 229910052792 caesium Inorganic materials 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 125000004093 cyano group Chemical group *C#N 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 229920006332 epoxy adhesive Polymers 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- JBTWLSYIZRCDFO-UHFFFAOYSA-N ethyl methyl carbonate Chemical compound CCOC(=O)OC JBTWLSYIZRCDFO-UHFFFAOYSA-N 0.000 description 1

- 229910052839 forsterite Inorganic materials 0.000 description 1

- 230000008014 freezing Effects 0.000 description 1

- 238000007710 freezing Methods 0.000 description 1

- 230000005484 gravity Effects 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 1

- 229910000449 hafnium oxide Inorganic materials 0.000 description 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 1

- LNEPOXFFQSENCJ-UHFFFAOYSA-N haloperidol Chemical compound C1CC(O)(C=2C=CC(Cl)=CC=2)CCN1CCCC(=O)C1=CC=C(F)C=C1 LNEPOXFFQSENCJ-UHFFFAOYSA-N 0.000 description 1

- 229930195733 hydrocarbon Natural products 0.000 description 1

- 150000002430 hydrocarbons Chemical class 0.000 description 1

- GPRLSGONYQIRFK-UHFFFAOYSA-N hydron Chemical compound [H+] GPRLSGONYQIRFK-UHFFFAOYSA-N 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- PNDPGZBMCMUPRI-UHFFFAOYSA-N iodine Chemical compound II PNDPGZBMCMUPRI-UHFFFAOYSA-N 0.000 description 1

- CBEQRNSPHCCXSH-UHFFFAOYSA-N iodine monobromide Chemical compound IBr CBEQRNSPHCCXSH-UHFFFAOYSA-N 0.000 description 1

- PDJAZCSYYQODQF-UHFFFAOYSA-N iodine monofluoride Chemical compound IF PDJAZCSYYQODQF-UHFFFAOYSA-N 0.000 description 1

- 150000002576 ketones Chemical class 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- HCWCAKKEBCNQJP-UHFFFAOYSA-N magnesium orthosilicate Chemical compound [Mg+2].[Mg+2].[O-][Si]([O-])([O-])[O-] HCWCAKKEBCNQJP-UHFFFAOYSA-N 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 150000007522 mineralic acids Chemical class 0.000 description 1

- 239000012046 mixed solvent Substances 0.000 description 1

- 150000002751 molybdenum Chemical class 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 150000002831 nitrogen free-radicals Chemical class 0.000 description 1

- GVGCUCJTUSOZKP-UHFFFAOYSA-N nitrogen trifluoride Chemical compound FN(F)F GVGCUCJTUSOZKP-UHFFFAOYSA-N 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 150000007524 organic acids Chemical class 0.000 description 1

- 235000005985 organic acids Nutrition 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- 150000002902 organometallic compounds Chemical class 0.000 description 1

- YWXLYZIZWVOMML-UHFFFAOYSA-N oxirane-2,2,3,3-tetracarbonitrile Chemical compound N#CC1(C#N)OC1(C#N)C#N YWXLYZIZWVOMML-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 239000012071 phase Substances 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- OBCUTHMOOONNBS-UHFFFAOYSA-N phosphorus pentafluoride Chemical compound FP(F)(F)(F)F OBCUTHMOOONNBS-UHFFFAOYSA-N 0.000 description 1

- 229920002849 poly(3-ethoxythiophene) polymer Polymers 0.000 description 1

- 229920002850 poly(3-methoxythiophene) polymer Polymers 0.000 description 1

- 229920002493 poly(chlorotrifluoroethylene) Polymers 0.000 description 1

- 229920003207 poly(ethylene-2,6-naphthalate) Polymers 0.000 description 1

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920006122 polyamide resin Polymers 0.000 description 1

- 229920002312 polyamide-imide Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 239000005023 polychlorotrifluoroethylene (PCTFE) polymer Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 229920006267 polyester film Polymers 0.000 description 1

- 229920001225 polyester resin Polymers 0.000 description 1

- 239000004645 polyester resin Substances 0.000 description 1

- 229920000570 polyether Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 239000002952 polymeric resin Substances 0.000 description 1

- 229920001155 polypropylene Polymers 0.000 description 1

- 229920005749 polyurethane resin Polymers 0.000 description 1

- 229920002451 polyvinyl alcohol Polymers 0.000 description 1

- 229920001289 polyvinyl ether Polymers 0.000 description 1

- 229920002620 polyvinyl fluoride Polymers 0.000 description 1

- 229920002981 polyvinylidene fluoride Polymers 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- RUOJZAUFBMNUDX-UHFFFAOYSA-N propylene carbonate Chemical compound CC1COC(=O)O1 RUOJZAUFBMNUDX-UHFFFAOYSA-N 0.000 description 1

- DOYOPBSXEIZLRE-UHFFFAOYSA-N pyrrole-3-carboxylic acid Chemical compound OC(=O)C=1C=CNC=1 DOYOPBSXEIZLRE-UHFFFAOYSA-N 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000008439 repair process Effects 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 239000003566 sealing material Substances 0.000 description 1

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 1

- FDNAPBUWERUEDA-UHFFFAOYSA-N silicon tetrachloride Chemical compound Cl[Si](Cl)(Cl)Cl FDNAPBUWERUEDA-UHFFFAOYSA-N 0.000 description 1

- 239000013464 silicone adhesive Substances 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000010944 silver (metal) Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 229910052712 strontium Inorganic materials 0.000 description 1

- 238000000859 sublimation Methods 0.000 description 1

- 230000008022 sublimation Effects 0.000 description 1

- SFZCNBIFKDRMGX-UHFFFAOYSA-N sulfur hexafluoride Chemical compound FS(F)(F)(F)(F)F SFZCNBIFKDRMGX-UHFFFAOYSA-N 0.000 description 1

- 229960000909 sulfur hexafluoride Drugs 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- NLDYACGHTUPAQU-UHFFFAOYSA-N tetracyanoethylene Chemical group N#CC(C#N)=C(C#N)C#N NLDYACGHTUPAQU-UHFFFAOYSA-N 0.000 description 1

- PCCVSPMFGIFTHU-UHFFFAOYSA-N tetracyanoquinodimethane Chemical compound N#CC(C#N)=C1C=CC(=C(C#N)C#N)C=C1 PCCVSPMFGIFTHU-UHFFFAOYSA-N 0.000 description 1

- TXEYQDLBPFQVAA-UHFFFAOYSA-N tetrafluoromethane Chemical compound FC(F)(F)F TXEYQDLBPFQVAA-UHFFFAOYSA-N 0.000 description 1

- 238000007725 thermal activation Methods 0.000 description 1

- 229920005992 thermoplastic resin Polymers 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- YNVOMSDITJMNET-UHFFFAOYSA-N thiophene-3-carboxylic acid Chemical compound OC(=O)C=1C=CSC=1 YNVOMSDITJMNET-UHFFFAOYSA-N 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 1

- 125000000391 vinyl group Chemical group [H]C([*])=C([H])[H] 0.000 description 1

- 229920002554 vinyl polymer Polymers 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- 239000008096 xylene Substances 0.000 description 1

- ZVWKZXLXHLZXLS-UHFFFAOYSA-N zirconium nitride Chemical compound [Zr]#N ZVWKZXLXHLZXLS-UHFFFAOYSA-N 0.000 description 1

Images

Landscapes

- Liquid Crystal (AREA)

- Element Separation (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

- Electroluminescent Light Sources (AREA)

Description

本実施の形態では、本発明の半導体装置の作製方法の一つについて説明する。

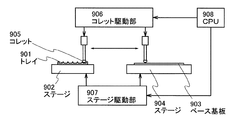

本実施の形態では、本発明の作製方法に用いられる製造装置の構成について説明する。

本実施の形態では、実施の形態1に示した作製方法において、エッチングにより半導体膜を分離するのではなく、ドーピングを用いて半導体膜を分離する、本発明の半導体装置の作製方法の一つについて説明する。

101 絶縁膜

102 欠陥層

103 凸部

104 マスク

105 コレット

106 半導体膜

107 ベース基板

108 半導体膜

109 半導体膜

110 半導体膜

111 トランジスタ

114 絶縁膜

120 トレイ

121 収容部

122 隔壁

130 画素部

131 信号線駆動回路

132 走査線駆動回路

200 ボンド基板

201 絶縁膜

202 欠陥層

206 半導体膜

210 マスク

211 欠陥層

220 トレイ

221 収容部

222 隔壁

400 画素部

410 走査線駆動回路

420 信号線駆動回路

421 シフトレジスタ

422 ラッチ

423 ラッチ

424 DA変換回路

500 RFタグ

501 アンテナ

502 集積回路

503 電源回路

504 復調回路

505 変調回路

506 レギュレータ

507 制御回路

509 メモリ

601 ベース基板

602 絶縁膜

603 半導体膜

604 半導体膜

606 ゲート絶縁膜

607 電極

608 不純物領域

609 不純物領域

610 サイドウォール

611 高濃度不純物領域

612 低濃度不純物領域

613 チャネル形成領域

614 高濃度不純物領域

615 低濃度不純物領域

616 チャネル形成領域

617 トランジスタ

618 トランジスタ

619 絶縁膜

620 絶縁膜

621 導電膜

622 導電膜

630 絶縁膜

631 絶縁膜

800 基板

801 演算回路

802 演算回路用制御部

803 命令解析部

804 制御部

805 タイミング制御部

806 レジスタ

807 レジスタ制御部

808 バスインターフェース

809 メモリ

820 メモリ用インターフェース

901 トレイ

901a トレイ

901b トレイ

901c トレイ

902 ステージ

902a ステージ

902b ステージ

902c ステージ

903 ベース基板

904 ステージ

905 コレット

906 コレット駆動部

907 ステージ駆動部

907a ステージ駆動部

907b ステージ駆動部

908 CPU

106a 半導体膜

106b 半導体膜

106c 半導体膜

1600 素子基板

1601 トランジスタ

1602 トランジスタ

1603 スイッチング用トランジスタ

1604 駆動用トランジスタ

1605 発光素子

1606 画素電極

1607 電界発光層

1608 対向電極

1610 素子基板

1611 トランジスタ

1612 トランジスタ

1613 トランジスタ

1614 対向基板

1615 液晶セル

1616 画素電極

1617 対向電極

1618 液晶

1620 収容部

1621 収容部

1622 収容部

1801 半導体膜

1802 半導体膜

1803 走査線

1804 信号線

1805 画素

1811 半導体膜

1812 半導体膜

1813 走査線

1814 信号線

1815 画素

1821 半導体膜

1822 半導体膜

1823 走査線

1824 信号線

1825 画素

1831 半導体膜

1832 半導体膜

1833 走査線

1834 信号線

1835 画素

2001 トランジスタ

2002 トランジスタ

2003 配線

2004 配線

2005 配線

2006 配線

2007 配線

2008 半導体膜

2010 半導体膜

2030 半導体膜

2031 半導体膜

3001 トランジスタ

3002 トランジスタ

3003 トランジスタ

3004 トランジスタ

3005 半導体膜

3006 半導体膜

3007 配線

3008 配線

3009 配線

3010 配線

3011 配線

3012 配線

3030 半導体膜

3031 半導体膜

4001 ベース基板

4002 画素部

4003 信号線駆動回路

4004 走査線駆動回路

4006 封止用基板

4007 充填材

4008 トランジスタ

4009 駆動用トランジスタ

4010 スイッチング用トランジスタ

4011 発光素子

4012 対向電極

4013 電界発光層

4014 配線

4015 配線

4016 接続端子

4017 配線

4018 FPC

4019 異方性導電膜

4020 シール材

5001 筐体

5002 表示部

5003 スピーカー部

5201 本体

5202 筐体

5203 表示部

5204 キーボード

5205 マウス

5401 本体

5402 筐体

5403 表示部

5404 部

5405 操作キー

5406 スピーカー部

6000 トレイ

6001 半導体膜

6002 収容部

6003 隔壁

6004 開口部

6005 凸部

6100 破線

6101 トレイ

6102 トレイ

6103 トレイ

6104 トレイ

6105 領域

6106 領域

6107 領域

6120 収容部

6121 収容部

6122 収容部

6123 半導体膜

6124 半導体膜

6125 半導体膜

6126 隔壁

6127 隔壁

6200 半導体膜

6201 トレイ

6202 収容部

6203 支持体

6204 隔壁

6205 絶縁膜

6206 コレット

6300 半導体膜

6301 トレイ

6302 収容部

6303 トレイ

6304 隔壁

6305 絶縁膜

6306 コレット

6310 収容部

6311 隔壁

6312 気孔

Claims (6)

- ボンド基板の下に第1の容器を配置した後、

前記ボンド基板を劈開させることで前記ボンド基板から形成される複数の第1の半導体膜を、前記第1の容器に載置し、

前記第1の容器の上に第2の容器を配置した後、前記第1の容器及び前記第2の容器を反転させることで、前記複数の第1の半導体膜を前記第2の容器に載置し、

前記複数の第1の半導体膜を前記第2の容器から拾い上げて、前記複数の第1の半導体膜どうしが離隔するように、なおかつ前記劈開により露出した面がベース基板側を向くように、前記複数の第1の半導体膜を前記ベース基板に貼り、

前記複数の第1の半導体膜をエッチングすることで、複数の第2の半導体膜を形成し、

前記第2の半導体膜から半導体素子を形成することを特徴とする半導体装置の作製方法。 - 第1の結晶面方位を有する第1のボンド基板の下に第1の容器を配置した後、

前記第1のボンド基板を劈開させることで前記第1のボンド基板から形成される複数の第1の半導体膜を、前記第1の容器に載置し、

前記第1の容器の上に第2の容器を配置した後、前記第1の容器及び前記第2の容器を反転させることで、前記複数の第1の半導体膜を前記第2の容器に載置し、

第2の結晶面方位を有する第2のボンド基板の下に第3の容器を配置した後、

前記第2のボンド基板を劈開させることで前記第2のボンド基板から形成される複数の第2の半導体膜を、前記第3の容器に載置し、

前記第3の容器の上に第4の容器を配置した後、前記第3の容器及び前記第4の容器を反転させることで、前記複数の第2の半導体膜を前記第4の容器に載置し、

前記複数の第1の半導体膜を前記第2の容器から拾い上げて、前記複数の第1の半導体膜どうしが離隔するように、なおかつ前記劈開により露出した面がベース基板側を向くように、前記複数の第1の半導体膜を前記ベース基板に貼り、

前記複数の第2の半導体膜を前記第4の容器から拾い上げて、前記複数の第2の半導体膜どうしが離隔するように、なおかつ前記複数の第1の半導体膜と前記複数の第2の半導体膜とが離隔するように、さらに前記劈開により露出した面が前記ベース基板側を向くように、前記複数の第2の半導体膜を前記ベース基板に貼り、

前記複数の第1の半導体膜及び前記複数の第2の半導体膜をエッチングすることで、複数の第3の半導体膜及び複数の第4の半導体膜を形成し、

前記第3の半導体膜及び前記第4の半導体膜から半導体素子を形成することを特徴とする半導体装置の作製方法。 - 請求項1において、

前記第1の容器は、第1の隔壁を有し、

前記第2の容器は、第2の隔壁を有し、

前記複数の第1の半導体膜は、それぞれ前記第1の隔壁及び第2の隔壁で隔てられることを特徴とする半導体装置の作製方法。 - 請求項2において、

前記第1の容器は、第1の隔壁を有し、

前記第2の容器は、第2の隔壁を有し、

前記第3の容器は、第3の隔壁を有し、

前記第4の容器は、第4の隔壁を有し、

前記複数の第1の半導体膜は、それぞれ前記第1の隔壁及び前記第2の隔壁で隔てられ、

前記複数の第2の半導体膜は、それぞれ前記第3の隔壁及び前記第4の隔壁で隔てられることを特徴とする半導体装置の作製方法。 - 請求項2または4において、前記第1の結晶面方位は{100}であり、前記第2の結晶面方位は{110}面であり前記第3の半導体膜からnチャネル型の素子が形成され、前記第4の半導体膜からpチャネル型の素子が形成されることを特徴とする半導体装置の作製方法。

- 請求項2、4または5において、前記第1のボンド基板及び前記第2のボンド基板にH3 +イオンを有するソースガスをイオンドーピングして劈開面を形成することを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007232503A JP5255801B2 (ja) | 2007-09-07 | 2007-09-07 | 半導体装置の作製方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007232503A JP5255801B2 (ja) | 2007-09-07 | 2007-09-07 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009065015A JP2009065015A (ja) | 2009-03-26 |

| JP2009065015A5 JP2009065015A5 (ja) | 2010-09-30 |

| JP5255801B2 true JP5255801B2 (ja) | 2013-08-07 |

Family

ID=40559327

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007232503A Expired - Fee Related JP5255801B2 (ja) | 2007-09-07 | 2007-09-07 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5255801B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB0819449D0 (en) * | 2008-10-23 | 2008-12-03 | Cambridge Display Tech Ltd | Display drivers |

| KR101651206B1 (ko) * | 2009-05-26 | 2016-08-25 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | Soi 기판의 제작 방법 |

| JP5981424B2 (ja) * | 2010-06-11 | 2016-08-31 | クロスバー, インコーポレイテッドCrossbar, Inc. | メモリー素子に関する柱状構造及び方法 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000012864A (ja) * | 1998-06-22 | 2000-01-14 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| EP1039513A3 (en) * | 1999-03-26 | 2008-11-26 | Canon Kabushiki Kaisha | Method of producing a SOI wafer |

| JP3771084B2 (ja) * | 1999-04-30 | 2006-04-26 | Necエレクトロニクス株式会社 | 半導体集積回路装置用トレイ |

| JP4378672B2 (ja) * | 2002-09-03 | 2009-12-09 | セイコーエプソン株式会社 | 回路基板の製造方法 |

| JP4163478B2 (ja) * | 2002-09-25 | 2008-10-08 | トッパン・フォームズ株式会社 | チップ反転装置 |

| JP4299721B2 (ja) * | 2003-12-09 | 2009-07-22 | 株式会社ルネサステクノロジ | 半導体装置の搬送方法および半導体装置の製造方法 |

| JP4838504B2 (ja) * | 2004-09-08 | 2011-12-14 | キヤノン株式会社 | 半導体装置の製造方法 |

| JP4687366B2 (ja) * | 2005-10-12 | 2011-05-25 | セイコーエプソン株式会社 | 半導体チップ収容トレイ及び半導体チップの搬送方法 |

| US7696574B2 (en) * | 2005-10-26 | 2010-04-13 | International Business Machines Corporation | Semiconductor substrate with multiple crystallographic orientations |

-

2007

- 2007-09-07 JP JP2007232503A patent/JP5255801B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009065015A (ja) | 2009-03-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5460984B2 (ja) | 半導体装置の作製方法 | |

| JP5268305B2 (ja) | 半導体装置の作製方法 | |

| JP5205012B2 (ja) | 表示装置及び当該表示装置を具備する電子機器 | |

| JP5294724B2 (ja) | 半導体装置の作製方法 | |

| JP5507063B2 (ja) | 半導体装置の作製方法 | |

| US7781306B2 (en) | Semiconductor substrate and method for manufacturing the same | |

| JP5728049B2 (ja) | 半導体装置 | |

| JP5250228B2 (ja) | 半導体装置の作製方法 | |

| JP5619474B2 (ja) | Soi基板の作製方法 | |

| JP2009111375A (ja) | 半導体装置の作製方法 | |

| JP5255801B2 (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100816 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100816 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121204 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121218 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130416 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130422 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160426 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |