図1は、本発明に係るスイッチングレギュレータの一実施形態を示す回路ブロック図である。本図に示すように、本実施形態のスイッチングレギュレータは、スイッチングレギュレータIC100と、これに外部接続されるダイオード(ショットキーダイオード)D1、インダクタL1、抵抗R1〜R4、並びに、キャパシタC1及びC2を有して成る。

スイッチングレギュレータIC100は、内部電圧生成部1と、参照電圧生成部2と、ソフトスタート電圧生成部3と、誤差増幅器4と、PWM[Pulse Width Modulation]コンパレータ5と、スロープ電圧生成部6と、発振器7と、論理和演算器8と、リセット優先型のRSフリップフロップ9と、プリドライバ10と、Pチャネル型MOS[Metal Oxide Semiconductor]電界効果トランジスタ11と、センス抵抗12(抵抗値R)と、コンパレータ13と、直流電圧源14(起電圧Vth1)と、遅延回路15と、ラッチ回路16と、タイマ回路17と、定電流源18と、Nチャネル型MOS電界効果トランジスタ19及び20と、ダイオード列21と、Pチャネル型MOS電界効果トランジスタ22と、抵抗23と、低電圧ドライバ24と、コンパレータ25と、直流電圧源26(起電圧Vth2)と、を集積化して成り、スイッチング素子(トランジスタ11)のオン/オフ制御を行うスイッチ駆動装置である。なお、本実施形態では、スイッチングレギュレータIC100にトランジスタ11を内蔵した構成を例示して説明を行うが、本発明の構成はこれに限定されるものではなく、トランジスタ11を外付けする構成としても構わない。

内部電圧生成部1は、入力電圧Vinから所定の内部電圧Vregを生成し、これをスイッチングレギュレータIC100の各部(参照電圧生成部2など)へ供給する手段である。なお、内部電圧生成部1の回路構成や動作については、後ほど詳述する。

参照電圧生成部2は、内部電圧Vregから所定の参照電圧Vrefを生成し、これを誤差増幅器4の第1非反転入力端(+)に出力する手段である。

ソフトスタート電圧生成部3は、スイッチングレギュレータIC100の起動時から緩やかに上昇するソフトスタート電圧Vssを生成し、これを誤差増幅器4の第2非反転入力端(+)に出力する手段である。

誤差増幅器4は、第1非反転入力端(+)に印加される参照電圧Vref、及び、第2非反転入力端(+)に印加されるソフトスタート電圧Vssのいずれか低い方と、反転入力端(−)に印加される帰還電圧Vfb(抵抗R1と抵抗R2との接続ノードから引き出される出力電圧Voutの分圧電圧)との差分を増幅して誤差電圧ERRを生成し、これをPWMコンパレータ5の反転入力端(−)に出力する手段である。すなわち、スイッチングレギュレータIC100が起動してから、ソフトスタート電圧Vssが参照電圧Vrefに達するまでは、ソフトスタート電圧Vssと帰還電圧Vfbとの差分が増幅されることになり、ソフトスタート電圧Vssが参照電圧Vrefに達して以後は、参照電圧Vrefと帰還電圧Vfbとの差分が増幅されることになる。なお、誤差増幅器4の出力端には、位相補償用の抵抗R3とキャパシタC2が外部接続されている。

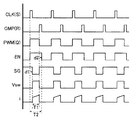

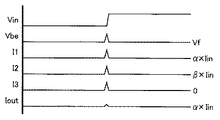

PWMコンパレータ5は、非反転入力端(+)に印加されるスロープ電圧SLと、反転入力端(−)に印加される誤差電圧ERRを比較して比較信号CMPを生成し、これを論理和演算器8の第1入力端に出力する手段である。図2は、トランジスタ11のオン/オフ制御に用いられるパルス信号PWMの生成動作を説明するためのタイミングチャートである。なお、図2では、上から順に、誤差電圧ERR、スロープ電圧SL、比較信号CMP(RSフリップフロップ9のリセット信号R)、クロック信号CLK(RSフリップフロップ9のセット信号S)、及び、パルス信号PWM(RSフリップフロップ9の出力信号Q)が描写されている。図2に示す通り、スロープ電圧SLが誤差電圧ERRよりも高いときには、比較信号CMPがハイレベルとされ、スロープ電圧SLが誤差電圧ERRよりも低いときには、比較信号CMPがローレベルとされる。

スロープ電圧生成部6は、クロック信号CLKに基づいて、図2に示すスロープ電圧SLを生成し、これをPWMコンパレータ5の非反転入力端(+)に出力する手段である。なお、図2では、三角波状のスロープ電圧SLを生成する構成を例に挙げたが、本発明の構成はこれに限定されるものではなく、鋸波状のスロープ電圧SLを生成する構成としても構わない。

発振器7は、矩形波状のクロック信号CLKを生成し、これをスロープ電圧生成部6とRSフリップフロップ9のセット端(S)に各々出力する手段である。なお、クロック信号CLKの発振周波数は、抵抗R4の抵抗値に応じて任意に調整することができる。

論理和演算器8は、第1入力端に印加される比較信号CMPと、第2入力端に印加される過電流保護信号S3との論理和演算信号ORを生成し、これをRSフリップフロップ9のリセット端(R)に出力する手段である。具体的に述べると、過電流保護信号S3がローレベルであるときには、比較信号CMPが論理和演算器8をスルーされる形となり、RSフリップフロップ9のリセット端(R)には、比較信号CMPと同じ論理レベルの論理和演算信号ORが入力される。一方、過電流保護信号S3がハイレベルであるときには、比較信号CMPが論理和演算器8によってマスクされる形となり、RSフリップフロップ9のリセット端(R)には、比較信号CMPに依ることなく、常にハイレベルの論理和演算信号ORが入力されることになる。

RSフリップフロップ9は、図2に示すように、セット端(S)に入力されるクロック信号CLKの立上がりエッジをトリガとして、出力端(Q)から出力するパルス信号PWMをハイレベルにセットし、リセット端(R)に入力される論理和演算信号OR(過電流未検出時には比較信号CMPに相当)の立上がりエッジをトリガとして、出力端(Q)から出力するパルス信号PWMをローレベルにリセットする手段である。なお、軽負荷時や無負荷時において、出力電圧Voutが目標電圧値の近傍に維持されている場合には、図2に示すように、誤差電圧ERRがスロープ電圧SLの下限値を常に下回る状態となり、パルス信号PWMは、連続発振状態から間欠発振状態に自動的にシフトされる。

プリドライバ10は、パルス信号PWMの駆動能力を高めてゲート信号SGを生成し、これをトランジスタ11のゲートに供給する手段であり、本実施形態では、プリドライバ10として、上側駆動電圧VH(=入力電圧Vin)と下側駆動電圧VLとの間で、ゲート信号SGをパルス駆動するインバータが用いられている。すなわち、パルス信号PWMとゲート信号SGとは、互いに論理反転された信号となっている。

トランジスタ11は、ゲート信号SG(延いてはパルス信号PWM)に応じてオン/オフ制御されるスイッチング素子(パワートランジスタ)である。トランジスタ11のソースは、センス抵抗12を介して入力電圧Vinの印加端に接続されている。トランジスタ11のドレインは、ダイオードD1のカソードとインダクタL1の一端にそれぞれ接続されている。ダイオードD1のアノードは、接地端に接続されている。インダクタL1の他端は、出力電圧Voutの引出端として負荷(図示せず)に接続される一方、キャパシタC1を介する経路、及び、抵抗R1、R2を介する経路で、接地端にも接続されている。

なお、トランジスタ11のソースから引き出される矩形波状のスイッチ電圧Vswは、ダイオードD1、インダクタL1、及び、キャパシタC1によって整流・平滑され、出力電圧Voutとして負荷(不図示)に供給される。また、出力電圧Voutは、抵抗R1と抵抗R2から成る抵抗分割回路によって分圧され、先述の帰還電圧Vfbとして誤差増幅器4に出力される。このようなフィードバック制御により、本実施形態のスイッチングレギュレータでは、入力電圧Vinを降圧して所望の出力電圧Voutが生成される。

センス抵抗12は、トランジスタ11に流れる電流iを電圧信号として検出する手段であり、入力電圧Vinの印加端とトランジスタ11のソースとの間に接続されている。

コンパレータ13の非反転入力端(+)は直流電圧源14の負極端に接続されている。直流電圧源14の正極端は、入力電圧Vinの印加端(センス抵抗12の高電位端)に接続されている。コンパレータ13の反転入力端(−)は、トランジスタ11のソース(センス抵抗12の低電位端)に接続されている。すなわち、コンパレータ13は、非反転入力端(+)に印加される閾値電圧(=Vin−Vth1)と、反転入力端(−)に印加されるセンス抵抗12の一端電圧(=Vin−i×R)を比較して過電流検出信号S1を生成し、これをラッチ回路16に出力する過電流検出手段(過電流保護回路の一回路要素)として機能する。なお、センス抵抗12での電圧降下分(i×R)が直流電圧源14の起電圧Vth1よりも小さい間は、過電流検出信号S1がローレベルに維持されるが、センス抵抗12での電圧降下分(i×R)が直流電圧源14の起電圧Vth1よりも大きくなると、過電流検出信号S1がハイレベルに遷移される。

直流電圧源14は、過電流検出用の閾値電圧(=Vin−Vth1)を設定する手段であり、入力電圧Vinの印加端とコンパレータ13の非反転入力端(+)との間に接続されている。

遅延回路15は、パルス信号PWMがローレベルとされるタイミングに遅延を与えて、コンパレータ13のイネーブル信号ENを生成する手段である。なお、遅延回路15の動作については後述する。

ラッチ回路16は、コンパレータ13から入力される過電流検出信号S1の立上がりエッジをトリガとして、過電流保護信号S3をハイレベルにセットし、タイマ回路17から入力されるタイマ信号S2の立上がりエッジをトリガとして、過電流保護信号S3をローレベルにリセットする手段である。なお、ラッチ回路16の動作については後述する。

タイマ回路17は、コンパレータ13から入力される過電流検出信号S1の立上がりエッジをトリガとして、保護動作期間Toffのカウントを開始し、そのカウント動作が終了した時点で、タイマ信号S2をローレベルからハイレベルにセットする手段である。なお、タイマ回路17の動作については後述する。

定電流源18、Nチャネル型MOS電界効果トランジスタ19及び20、ダイオード列21、Pチャネル型MOS電界効果トランジスタ22、及び、抵抗23は、トランジスタ11のゲート・ソース間電圧(入力電圧Vinとゲート信号SGとの電圧差)を所定値以下に維持するように、入力電圧Vinに応じて下側駆動電圧VLを制御しつつ、プリドライバ10の駆動電流を引き込む耐圧保護回路である。定電流源18の一端は、内部電圧Vregの印加端に接続されている。定電流源18の他端(定電流出力端)は、トランジスタ19のドレインに接続されている。トランジスタ19のソースは、接地端に接続されている。トランジスタ19のゲートは、トランジスタ20のゲートに接続される一方、トランジスタ19のドレインにも接続されている。トランジスタ20のソースは、接地端に接続されている。トランジスタ20のドレインは、ダイオード列21のアノード端と、トランジスタ22のゲートにそれぞれ接続されている。ダイオード列21のカソード端は、入力電圧Vinの印加端に接続されている。トランジスタ22のドレインは、抵抗23を介して接地端に接続されている。トランジスタ22のソースは、下側駆動電圧VLの印加端に接続されている。なお、ダイオード列21を形成するダイオードの個数については、1以上の任意の整数とすればよい。また、上記構成から成る耐圧保護回路の動作については後ほど詳細に説明する。

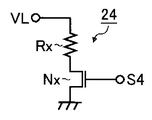

低電圧ドライバ24は、コンパレータ25から入力される低電圧検出信号S4に基づいて、プリドライバ10の下側駆動電圧VLを通常時よりも引き下げて、プリドライバ10の駆動電流を引き込むか否かを制御する手段である。なお、低電圧ドライバ24の回路構成及び動作については後述する。

コンパレータ25は、非反転入力端(+)に印加される直流電圧源26の起電圧(閾値電圧Vth2)と、反転入力端(−)に印加される入力電圧Vinを比較して低電圧検出信号S4を生成し、これを低電圧ドライバ24に出力する低電圧検出回路である。すなわち、入力電圧Vinが閾値電圧Vth2よりも高いときには、低電圧検出信号S4がローレベルに維持されるが、入力電圧Vinが閾値電圧Vth2よりも低くなると、低電圧検出信号S4がハイレベルに遷移される。

直流電圧源26は、低電圧検出用の閾値電圧(=Vth2)を設定する手段であり、コンパレータ25の非反転入力端(+)と接地端との間に接続されている。

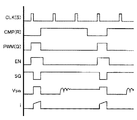

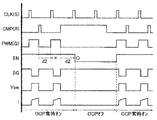

次に、過電流保護回路の消費電流低減機能について、図3〜図5を参照しながら詳細な説明を行う。図3〜図5は、いずれも、過電流保護回路の消費電流低減機能を説明するためのタイミングチャートであり、それぞれ、上から順に、クロック信号CLK(RSフリップフロップ9のセット信号S)、比較信号CMP(RSフリップフロップ9のリセット信号R)、パルス信号PWM(RSフリップフロップ9の出力信号Q)、イネーブル信号EN、ゲート信号SG、スイッチ電圧Vsw、及び、電流iが描写されている。なお、図3には、パルス信号PWMが連続発振されているときの様子が示されており、図4には、パルス信号PWMが間欠発振されているときの様子が示されている。また、図5には、後述する遅延時間d2を長く設定した場合の様子が示されている。

まず、図3及び図4について説明する。先述したように、RSフリップフロップ9の出力端(Q)から出力されるパルス信号PWMは、セット端(S)に入力されるクロック信号CLKの立上がりエッジでハイレベルにセットされ、リセット端(R)に入力される比較信号CMPの立上がりエッジでローレベルにリセットされる。

遅延回路15は、上記のパルス信号PWMを過電流保護回路のイネーブル信号ENとして流用すべく、パルス信号PWMがローレベルとされるタイミングに遅延を与えて、コンパレータ13のイネーブル信号ENを生成する。すなわち、イネーブル信号ENは、パルス信号PWMの立上がりエッジと同じタイミングでハイレベルとされ、パルス信号PWMの立下がりエッジから遅延時間d2だけ遅れたタイミングでローレベルとされる。

一方、プリドライバ10は、パルス信号PWMの駆動能力を高めるとともに、その論理を反転することでゲート信号SGを生成する。このとき、ゲート信号SGがローレベルとされるタイミングは、プリドライバ10のスルーレートやトランジスタ11のゲート容量などに応じて、パルス信号PWMがハイレベルとされるタイミングよりも遅延時間d1だけ遅れる。すなわち、ゲート信号SGは、パルス信号PWMの立上がりエッジから遅延時間d1だけ遅れたタイミングでローレベルとされ、パルス信号PWMの立下がりエッジと同じタイミングでハイレベルとされる。

従って、コンパレータ13が動作状態とされる期間T2は、トランジスタ11がオンされる期間T1よりも長くなる。別の言い方をすれば、コンパレータ13は、トランジスタ11がオンされる前に動作状態とされ、かつ、トランジスタ11がオフされた後に非動作状態とされる。

上記で説明した通り、本実施形態のスイッチングレギュレータIC100は、トランジスタ11に流れる電流iをモニタして過電流保護を行う過電流保護回路(コンパレータ13を含む)と、トランジスタ11のオン時に過電流保護回路を動作状態とし、トランジスタ11のオフ時に過電流保護回路を非動作状態とするイネーブル制御回路(本実施形態では、遅延回路15)と、を有して成る構成とされている。

このような構成とすることにより、電流iをモニタすべきとき(すなわち、トランジスタ11をオンとし、トランジスタ11を介した電流経路が導通されているとき)にのみ、過電流保護回路を動作状態とし、その余の場合には過電流保護回路を非動作状態とすることができるので、過電流保護回路の消費電流を低減することが可能となる。特に、図4に示すように、パルス信号PWMが間欠発振状態となる軽負荷時や無負荷時においては、スイッチングレギュレータ全体の消費電流に占める過電流保護回路の消費電流の割合が大きくなるため、本発明による消費電流の低減効果が顕著となる。

なお、本実施形態のスイッチングレギュレータIC100において、イネーブル制御回路(遅延回路15)は、トランジスタ11のオン/オフ制御に用いられるパルス信号PWMを過電流保護回路のイネーブル信号ENとして流用する構成とされている。このような構成であれば、トランジスタ11のオン/オフ制御タイミングと過電流保護回路のオン/オフ制御タイミングのマッチングを容易に実現することが可能となる。ただし、本発明の構成はこれに限定されるものではなく、その他の手段によって過電流保護回路のイネーブル信号ENを生成しても構わない。例えば、トランジスタ11のゲート信号SGからイネーブル信号ENを生成する構成としてもよいし、或いは、トランジスタ11のオン/オフ状態を直接モニタしてイネーブル信号ENを生成する構成としてもよい。

また、先から述べている通り、本実施形態のスイッチングレギュレータIC100は、イネーブル制御回路として、パルス信号PWMがローレベルとされるタイミングに遅延を与えてイネーブル信号ENを生成する遅延回路15を用いている。このような構成とすることにより、コンパレータ13が動作状態とされる期間T2をトランジスタ11がオンされる期間T1よりも長くすることができるので、トランジスタ11がオンされているときには、過電流保護回路を確実に起動しておくことが可能となる。

次に、図5について説明する。図5の例では、遅延回路15でパルス信号PWMに与える遅延時間d2が図3や図4の例よりも長く設定されている。より具体的に述べると、遅延回路15では、パルス信号PWMが連続発振されているときには、過電流保護回路が常に動作状態に維持され、パルス信号PWMが間欠発振されているときにのみ、過電流保護回路が非動作状態とされるように、その遅延時間d2が設定されている。

図5の例に即して説明すると、パルス信号PWMが連続発振されているときには、パルス信号PWMの立下がりエッジから遅延時間d2が経過する前に、パルス信号PWMの次の立上がりエッジが到来するので、イネーブル信号ENは常にハイレベルとなり、過電流保護回路が常に動作状態に維持される。一方、パルス信号PWMが間欠発振されているときには、パルス信号PWMの立下がりエッジから遅延時間d2が経過しても、パルス信号PWMの次の立上がりエッジは到来しないので、イネーブル信号ENは、上記の遅延時間d2が経過した時点でローレベルとなり、過電流保護回路が非動作状態とされる。

このような構成とすることにより、パルス信号PWMが連続発振されているときには、安全性の向上を優先して、過電流保護回路を常に動作状態に維持する一方、パルス信号PWMが間欠発振されているときには、消費電流の低減を優先して、過電流保護回路を非動作状態とすることが可能となる。

なお、上記実施形態では、本発明をスイッチングレギュレータIC100に適用した構成を例に挙げて説明を行ったが、本発明の適用対象はこれに限定されるものではなく、過電流保護回路を備えたスイッチ駆動装置全般(例えば、モータドライバの出力段を形成するスイッチング素子のオン/オフ制御を行うスイッチ駆動装置)に広く適用することが可能である。

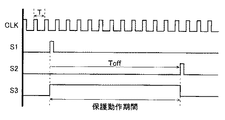

次に、過電流保護回路の自己復帰機能について、先出の図1とともに、図6を参照しながら詳述する。図6は過電流保護回路の自己復帰機能を説明するためのタイミングチャートであり、上から順番に、クロック信号CLK、過電流検出信号S1、タイマ信号S2、及び、過電流保護信号S3が各々描写されている。

先に述べた通り、タイマ回路17は、過電流検出信号S1の立上がりエッジをトリガとして、保護動作期間Toffのカウントを開始し、そのカウント動作が終了した時点で、タイマ信号S2をローレベルからハイレベルにセットする。また、ラッチ回路16は、過電流検出信号S1の立上がりエッジをトリガとして、過電流保護信号S3をハイレベルにセットし、タイマ信号S2の立上がりエッジをトリガとして、過電流保護信号S3をローレベルにリセットする。このようにして生成された過電流保護信号S3は、論理和演算器8の第2入力端に印加され、比較信号CMPのマスク処理に用いられる。具体的には、過電流保護信号S3がローレベルであるときには、比較信号CMPが論理和演算器8をスルーされ、過電流保護信号S3がハイレベルであるときには、比較信号CMPが論理和演算器8によってマスクされる。

上記のように、本実施形態のスイッチングレギュレータIC100において、過電流保護回路は、過電流が検出されたときに所定の保護動作期間Toffを計時し始め、前記過電流が検出されてから保護動作期間Toffが経過するまで、トランジスタ11の駆動を継続的に停止させた後、トランジスタ11の駆動を再開させる構成とされている。

このような構成であれば、パルス信号PWMの一周期毎(クロック信号CLKのパルス周期毎)に過電流保護回路を自己復帰させる従来構成と異なり、連続的に過電流が流れ続ける異常状態(出力ショートなど)に陥った場合でも、パルス信号PWMの一周期毎に過電流保護回路が自己復帰されて過大な電流iが断続的に流れ続けることはないので、スイッチングレギュレータIC100や外付け部品(コイルL1、ショットキーダイオードD1)の発熱を抑えることが可能となる。

なお、タイマ回路17としては、RC時定数回路などのアナログタイマを用いてもよいし、クロック信号CLKのパルス数をカウントするデジタルタイマを用いても構わない。また、上記の保護動作期間Toffは、クロック信号CLKのパルス周期Tより十分長く設定することが望ましく、例えば、パルス周期Tが数[μs]である場合、保護動作期間Toffは、数十[μs]に設定すればよい。

また、先出の図1では、過電流保護回路の自己復帰機能部として、ラッチ回路16とタイマ回路17を各々独立の回路ブロックで描写したが、本発明の構成はこれに限定されるものではなく、ラッチ回路16、並びに、タイマ回路17を形成する回路要素としては、図7に示すように、キャパシタCAと、キャパシタCAの充電電流を生成する定電流源IAと、過電流が検出されたときにキャパシタCAを放電する放電部(図7では過電流検出信号S1がハイレベルであるときにオンとなるNチャネル型MOS電界効果トランジスタNA)と、キャパシタCAの充電電圧VCが所定の閾値電圧よりも高いか低いかに応じて過電流保護信号S3の出力論理を変遷する比較部(図7ではインバータINV)と、を有して成る構成としてもよい。

図8は、上記構成から成る自己復帰機能部の動作を説明するためのタイミングチャートであり、上から順に、過電流検出信号S1、キャパシタCAの充電電圧VC、及び、過電流保護信号S3が描写されている。

図8に示すように、過電流検出信号S1がハイレベルに立ち上がると、トランジスタNAがオンとなり、キャパシタCAが放電されて、充電電圧VCがゼロ値(ローレベル)となる。従って、インバータINVの出力信号である過電流保護信号S3は、ハイレベルに立ち上がり、トランジスタ11の駆動が継続的に停止される。トランジスタ11の駆動が停止されると、過電流検出信号S1はローレベルに立ち下がり、トランジスタNAはオフとなる。その結果、キャパシタCAの充電が再開され、充電電圧VCが上昇し始める。そして、充電電圧VCがインバータINVの論理反転閾値(図8中の一点鎖線を参照)に達すると、過電流保護信号S3がハイレベルからローレベルに遷移され、トランジスタ11の駆動が再開される。

このように、上記構成から成る自己復帰機能部であれば、簡易なアナログ回路により、所望の過電流保護信号S3を生成することが可能となる。なお、保護動作期間Toffの長さは、定電流源IAで生成する電流量に応じて適宜調整することが可能である。

また、上記実施形態では、キャパシタCAの充電電圧VCが所定の閾値電圧よりも高いか低いかに応じて過電流保護信号S3の出力論理を変遷する比較部として、インバータINVを用いた構成を例に挙げて説明を行ったが、本発明の構成はこれに限定されるものではなく、バッファやコンパレータを用いても構わない。

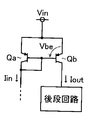

次に、内部電圧生成部1の回路構成及び動作について詳細に説明する。図9は、内部電圧生成部1の一構成例を示す回路図である。図9に示すように、本構成例の内部電圧生成部1は、pnp型バイポーラトランジスタQa、Qb、Qcと、npn型バイポーラトランジスタQd、Qeと、抵抗Ra、Rb、Rc、Rdと、キャパシタCaと、オペアンプAMPと、直流電圧源Eaと、を有して成る。

トランジスタQa、Qb、Qcのエミッタは、いずれも入力電圧Vinの印加端に接続されている。トランジスタQa、Qb、Qcのベースは、いずれもトランジスタQaのコレクタに接続されている。トランジスタQaのコレクタは、入力電流Iinの入力端に接続されている。トランジスタQbのコレクタは、オペアンプAMPの電源端に接続される一方、抵抗Raを介してトランジスタQdのコレクタにも接続されている。トランジスタQcのコレクタは、抵抗Rbを介して接地端に接続される一方、トランジスタQdのベースにも接続されている。トランジスタQdのエミッタは、接地端に接続されている。トランジスタQeのコレクタは、入力電圧Vinの印加端に接続されている。トランジスタQeのベースは、オペアンプAMPの出力端に接続されている。トランジスタQeのエミッタは、抵抗Rc及び抵抗Rdを介して接地端に接続される一方、内部電圧Vregの出力端にも接続されている。オペアンプAMPの非反転入力端(+)は、第1電圧V1の印加端(直流電圧源Eaの正極端)に接続されている。オペアンプAMPの反転入力端(−)は、第2電圧V2の印加端(抵抗Rcと抵抗Rdとの接続ノード)に接続されている。

上記構成から成る内部電圧生成部1は、オペアンプAMPを用いて、第1電圧V1と第2電圧V2が一致するように、トランジスタQeの開放度を制御することにより、入力電圧Vinから所望の内部電圧Vregを生成するシリーズレギュレータである。

また、上記構成から成る内部電圧生成部1において、トランジスタQa、Qbは、入力電流Iinから所望の出力電流Iout(=α×Iin)を生成し、これをオペアンプAMPに供給するカレントミラー回路を形成している。

このカレントミラー回路には、トランジスタQa、Qbから成る第1カレントミラー段のほか、入力電圧Vinの急変に際して、出力電流Ioutの変動を抑えるためのピーク電流防止回路X(トランジスタQc、Qd、抵抗Ra、Rb、及び、キャパシタCa)が組み込まれている。

図10は、ピーク電流防止動作を説明するための波形図であり、上から順に、入力電圧Vin、トランジスタQbのベース・エミッタ間電圧Vbe、第1ミラー電流I1、第2ミラー電流I2、補正電流I3、及び、出力電流Ioutが示されている。

図10に示すように、入力電圧Vinが一定に保たれている場合、トランジスタQbのベース・エミッタ間電圧Vbeは、トランジスタQbのベース・エミッタ間における順方向降下電圧Vfに維持され、第1ミラー電流I1、及び、第2ミラー電流I2は、それぞれα×Iin、β×Iinに維持される。また、第2ミラー電流I2が上記の電流値に維持されている間、トランジスタQdはオフとなり、トランジスタQbのコレクタから抵抗Ra及びトランジスタQdを介して接地端に至る電流経路が遮断されるため、この電流経路に流れる補正電流I3はゼロ値となる。その結果、出力電流Ioutは、第1ミラー電流I1と同じ電流値(α×Iin)となる。なお、上記の第2ミラー定数βは、消費電流削減の観点から、第1ミラー定数αよりも十分に小さい値(例えば数十分の一)に設定しておくことが望ましい。

一方、入力電圧Vinに急変動が生じると、トランジスタQbのベース・エミッタ間電圧Vbeは大きくなるが、入力電圧VinとトランジスタQbのベースとの間には、キャパシタCaが接続されているため、その増大量は、従来構成(図12や図13を参照)に比べて、非常に小さく抑えられている。

また、ピーク電流防止回路Xには、上記キャパシタCaに加えて、第1ミラー電流I1の増加分を吸収するピーク電流吸収回路Y(トランジスタQc、Qd、及び、抵抗Ra、Rb)が設けられており、入力電圧Vinの急変時に生じるピーク電流のさらなる抑制が図られている。

ピーク電流吸収回路Yの動作について、図9及び図10を参照しながら詳述する。入力電圧Vinに急変動が生じて第1ミラー電流I1にピーク電流が生じた場合、これと同様の挙動で第2ミラー電流I2にもピーク電流が生じる。このとき、第2ミラー電流I2が所定値に達すると、トランジスタQdのベース電位(第2ミラー電流I2が流れる抵抗Rbの一端電圧)がトランジスタQdのオンスレッショルド電圧まで引き上げられて、トランジスタQdがオンとなり、トランジスタQbのコレクタから抵抗Ra及びトランジスタQdを介して接地端に至る電流経路が導通される。その結果、トランジスタQbのコレクタからは、第2ミラー電流I2に応じた補正電流I3が引き抜かれるので、出力電流Ioutは、第1ミラー電流I1から補正電流I3を差し引いた電流値(第1ミラー電流I1の増加分が吸収された電流値)となる。

上記で説明した通り、本発明に係るカレントミラー回路は、入力電流Iinをミラーして第1ミラー電流I1を生成する第1カレントミラー段(トランジスタQa、Qb)と、電源急変時に生じる第1ミラー電流I1の増加分に応じた補正電流I3を生成し、これを第1カレントミラー段の出力端から引き込むピーク電流吸収回路Y(トランジスタQc、Qd、抵抗Ra、Rb)と、を有して成り、第1ミラー電流i1から補正電流I3を差し引いて得られる差分電流(=I1−I3)を出力電流Ioutとして後段回路(オペアンプAMP)に出力する構成とされている。

より具体的に述べると、上記のピーク電流吸収回路Yは、入力電流Iinをミラーして第2ミラー電流I2を生成する第2カレントミラー段(トランジスタQa、Qc)と、第2ミラー電流I2に応じて補正電流I3の引き込み量を制御する補正電流生成回路Z(トランジスタQd、抵抗Ra、Rb)と、を有して成る構成とされている。

さらに詳しく述べると、上記の補正電流生成回路Zは、第2ミラー電流I2を電圧信号に変換する抵抗Rbと、第1カレントミラー段の出力端(トランジスタQbのコレクタ)と接地端との間に接続され、上記の電圧信号に応じて導通度が制御されるトランジスタQdと、を有して成る構成とされている。

このような構成とすることにより、入力電圧Vinが急変しても、カレントミラー回路の出力電流Ioutには大きなピーク電流が生じないので、後段回路の誤動作を防ぐことが可能となり、延いては、スイッチングレギュレータの安定性向上に貢献することができる。特に、入力電圧Vinとしてバッテリの出力電圧が直接印加される場合には、入力電圧Vinの急変動が生じやすいため、本発明によるピーク電流の低減効果が顕著となる。

なお、上記実施形態では、オペアンプAMPの駆動電流生成手段として、本発明に係るカレントミラー回路を用いた構成を例に挙げて説明を行ったが、本発明の適用対象はこれに限定されるものではなく、入力電流をミラーして所望の出力電流を生成するカレントミラー回路全般に広く適用することが可能である。

次に、トランジスタ11の耐圧保護機能、及び、低電圧モードへの切換機能について、先出の図1を参照しながら詳述する。

先述したように、本実施形態のスイッチングレギュレータIC100には、トランジスタ11のゲート・ソース間電圧(入力電圧Vinとゲート信号SGとの電圧差)を所定値以下に維持するように、入力電圧Vinに応じてプリドライバ10の下側駆動電圧VLを制御しつつ、プリドライバ10の駆動電流を引き込む耐圧保護回路が設けられている。

なお、上記の耐圧保護回路は、図1に示す通り、カソード端が入力電圧Vinの印加端に接続されたダイオード列21と、ダイオード列21に定電流を流す定電流源(18〜20)と、ソースが下側駆動電圧VLの印加端に接続され、ゲートがダイオード列21のアノード端に接続されたPチャネル型電界効果トランジスタ22と、を有して成る。

確かに、上記構成から成る耐圧保護回路であれば、プリドライバ10の下側駆動電圧VLをVin−VA+VthB(ただし、VAはダイオード列21の順方向降下電圧、VthBはトランジスタ22のオンスレッショルド電圧)に維持することができるので、トランジスタ11のゲート・ソース間電圧は、所定値(VA−VthB)までしか開かなくなる。従って、トランジスタ11を高い入力電圧Vinで動作させる場合でも、トランジスタ11のゲート・ソース間電圧がその耐圧を超えることはなく、装置の破壊や異常発熱などを防止することが可能である。

ただし、上記の耐圧保護回路のみを備えた場合には、従来技術の項でも述べた通り、プリドライバ10を正常に動作させるために、VthA+VthB+Vds以上(ただし、VthAはトランジスタ11のオンスレッショルド電圧、Vdsはトランジスタ20のドレイン・ソース間降下電圧)の入力電圧Vinを供給する必要がある。また、入力電圧Vinが低くなると、トランジスタ11のゲート・ソース間電圧が小さくなるため、トランジスタ11のオン抵抗が大きくなり、電力効率が低下してしまう。

そこで、本実施形態のスイッチングレギュレータIC100は、入力電圧Vinが閾値電圧Vth2を下回っているか否かを検出する低電圧検出回路(コンパレータ25)と、低電圧検出回路において入力電圧Vinの低電圧状態が検出されたときにのみ、プリドライバ10の下側駆動電圧VLを通常時よりも引き下げて、プリドライバ10の駆動電流を引き込む低電圧ドライバ24と、を有して成る。

なお、低電圧ドライバ24は、図11に示すように、抵抗RxとNチャネル型電界効果トランジスタNxを有して成る。トランジスタNxのドレインは、抵抗Rxを介して下側駆動電圧VLの印加端に接続されている。トランジスタNxのソースは接地端に接続されている。トランジスタNxのゲートは、低電圧検出信号S4の印加端に接続されている。

上記構成から成るスイッチングレギュレータIC100において、入力電圧Vinが閾値電圧Vth2を下回ったときには、低電圧ドライバ24の働きによって、プリドライバ10の下側駆動電圧VLが通常時よりも引き下げられ、かつ、トランジスタ22を介する電流経路のみならず、トランジスタNxを介する電流経路でもプリドライバ10の駆動電流が引き込まれることになる。すなわち、入力電圧Vinの低電圧状態が検出されたときには、プリドライバ10の駆動モードが通常モードから低電圧モードに切り換えられる。

このような構成とすることにより、入力電圧Vinが高電圧範囲から低電圧範囲まで幅広く変化される場合であっても、安全かつ安定にスイッチングレギュレータを動作させることが可能となる。また、入力電圧Vinが低電圧状態となった場合でも、トランジスタ11のゲート・ソース間電圧を確保して、トランジスタ11のオン抵抗を小さく維持することができるので、電力効率の低下を招くことがなくなる。

なお、本発明の構成は、上記実施形態のほか、発明の主旨を逸脱しない範囲で種々の変更を加えることが可能である。