JP5188545B2 - 化合物半導体基板 - Google Patents

化合物半導体基板 Download PDFInfo

- Publication number

- JP5188545B2 JP5188545B2 JP2010153634A JP2010153634A JP5188545B2 JP 5188545 B2 JP5188545 B2 JP 5188545B2 JP 2010153634 A JP2010153634 A JP 2010153634A JP 2010153634 A JP2010153634 A JP 2010153634A JP 5188545 B2 JP5188545 B2 JP 5188545B2

- Authority

- JP

- Japan

- Prior art keywords

- single crystal

- layer

- crystal layer

- carbon

- atoms

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000000758 substrate Substances 0.000 title claims description 87

- 239000004065 semiconductor Substances 0.000 title claims description 63

- 150000001875 compounds Chemical class 0.000 title claims description 47

- 239000013078 crystal Substances 0.000 claims description 140

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 80

- 229910052799 carbon Inorganic materials 0.000 claims description 80

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 claims description 18

- 229910052796 boron Inorganic materials 0.000 claims description 18

- 150000004767 nitrides Chemical class 0.000 claims description 18

- 238000009826 distribution Methods 0.000 claims description 4

- 239000010410 layer Substances 0.000 description 229

- 239000007789 gas Substances 0.000 description 18

- 238000000034 method Methods 0.000 description 17

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 15

- 238000011156 evaluation Methods 0.000 description 13

- 230000015556 catabolic process Effects 0.000 description 12

- 230000008569 process Effects 0.000 description 11

- 238000004519 manufacturing process Methods 0.000 description 10

- 239000000203 mixture Substances 0.000 description 10

- 230000007423 decrease Effects 0.000 description 6

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 6

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 5

- JLTRXTDYQLMHGR-UHFFFAOYSA-N trimethylaluminium Chemical compound C[Al](C)C JLTRXTDYQLMHGR-UHFFFAOYSA-N 0.000 description 5

- 229910002601 GaN Inorganic materials 0.000 description 4

- 239000000969 carrier Substances 0.000 description 4

- 238000001947 vapour-phase growth Methods 0.000 description 4

- 229910002704 AlGaN Inorganic materials 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000001451 molecular beam epitaxy Methods 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- ATUOYWHBWRKTHZ-UHFFFAOYSA-N Propane Chemical compound CCC ATUOYWHBWRKTHZ-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 238000001741 metal-organic molecular beam epitaxy Methods 0.000 description 2

- -1 nitride compound Chemical class 0.000 description 2

- 230000000704 physical effect Effects 0.000 description 2

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 2

- 239000002994 raw material Substances 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- XCZXGTMEAKBVPV-UHFFFAOYSA-N trimethylgallium Chemical compound C[Ga](C)C XCZXGTMEAKBVPV-UHFFFAOYSA-N 0.000 description 2

- 238000001771 vacuum deposition Methods 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 1

- OTMSDBZUPAUEDD-UHFFFAOYSA-N Ethane Chemical compound CC OTMSDBZUPAUEDD-UHFFFAOYSA-N 0.000 description 1

- 230000005355 Hall effect Effects 0.000 description 1

- HSFWRNGVRCDJHI-UHFFFAOYSA-N alpha-acetylene Natural products C#C HSFWRNGVRCDJHI-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 125000002534 ethynyl group Chemical group [H]C#C* 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 238000007429 general method Methods 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 239000001294 propane Substances 0.000 description 1

- 239000000700 radioactive tracer Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 1

- 230000001568 sexual effect Effects 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 230000008719 thickening Effects 0.000 description 1

- 238000004627 transmission electron microscopy Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02538—Group 13/15 materials

- H01L21/0254—Nitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02439—Materials

- H01L21/02455—Group 13/15 materials

- H01L21/02458—Nitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02494—Structure

- H01L21/02496—Layer structure

- H01L21/02505—Layer structure consisting of more than two layers

- H01L21/02507—Alternating layers, e.g. superlattice

Description

このような多層バッファ層を設けることにより、窒化物活性層でのクラックの発生および基板の反りを抑制することができ、かつ、この基板を用いたデバイスのノーマリオフ化と高耐圧化を図ることができる。

炭素含有濃度が高いAlxGa1-xN単結晶層は、その直上のAlyGa1-yN単結晶層の結晶との格子定数差が大きくなり、強い圧縮応力を生じ得る。

上記濃度範囲のホウ素を含むことにより、前記AlxGa1-xN単結晶層および前記AlyGa1-yN単結晶層の炭素含有濃度が増加し、耐圧をより向上させることができる。

デバイスの高速性向上の観点からは、前記電子走行層中のAl濃度はできるだけ低いことが好ましい。

さらに、本発明に係る化合物半導体基板は、これを用いてデバイス作製することにより、耐電圧の向上を図ることができるため、高耐圧デバイス、特に、ノーマリオフ型スイッチングデバイスに好適に適用することができる。

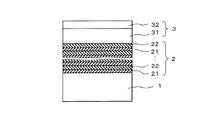

図1に、本発明に係る化合物半導体基板の層構造の概略を示す。図1に示す化合物半導体基板は、Si単結晶基板1上に、多層バッファ層2、電子走行層31と電子供給層32からなる窒化物活性層3が、順次積層された構成を備えているものである。

前記多層バッファ層2は、AlxGa1-xN単結晶層(0.6≦x≦1.0)21およびAlyGa1-yN単結晶層(0≦y≦0.5)22が、この順にSi基板1側から交互に繰り返し積層された多層構造からなる。

そして、前記AlxGa1-xN単結晶層(0.6≦x≦1.0)21には、炭素が1×1018atoms/cm3以上1×1021atoms/cm3以下含まれており、前記AlyGa1-yN単結晶層(0≦y≦0.5)22には、炭素が1×1017atoms/cm3以上1×1021atoms/cm3以下含まれている。

このような多層バッファ層2を設けることにより、窒化物活性層3でのクラックの発生および基板全体の反りを抑制することができる。しかも、この基板を用いたデバイスの高耐圧化を図ることができるという効果が得られる。

このようなキャリアを抑制するためには、多層バッファ層中に炭素を含有していることが効果的である。

本発明においては、炭素を意図的に上記のような濃度範囲となるように添加することにより、デバイスの耐電圧を向上させることができる。

x<0.6、また、y>0.5の場合は、AlxGa1-xN単結晶層とAlyGa1-yN単結晶層の結晶格子定数の差が小さいため、圧縮応力が発生しにくくなる。

一方、y<0.1の場合は、AlyGa1-yN層のAl組成が低すぎて、従来並みの低耐圧デバイスまたは従来のノーマリオン型デバイスしか得られない。

基板1側は、高い炭素含有濃度のため、残留キャリアが低減して高耐圧となる。物理的には、フェルミ準位が伝導帯から離れる。

そして、活性層3側を低い炭素含有濃度とすることにより、ゲート電圧が印加されない場合、キャリアが誘起されない状態となる。物理的には、フェルミ準位が伝導帯に近づくが、デバイスにおけるオフ・オン制御が、ゲートにおける数V程度の正電圧で可能となる、すなわち、ノーマリオフとなる。

したがって、単に、基板1側から活性層3側に向かって、全体的に一定割合で炭素含有濃度が減少するような構成では、ノーマリオフ化は達成されない。上記のような本発明に係る炭素含有濃度の変化および層構成が、良好なノーマリオフの高耐圧デバイスを実現する上で重要である。

炭素含有濃度が高いAlxGa1-xN単結晶層21は、結晶が柔らかいため、転位が発生しやすくなり、結晶が緩和する。緩和した結晶は、その直上のAlyGa1-yN単結晶層22の結晶との格子定数差が大きいため、強い圧縮応力が発生する。

上記濃度範囲のホウ素を含むことにより、AlxGa1-xN単結晶層21およびAlyGa1-yN単結晶層22の炭素含有濃度を、より増加させることができ、耐圧の向上が図られる。

AlxGa1-xN単結晶層21およびAlyGa1-yN単結晶層22の結晶格子において、Gaの格子位置にホウ素が入ることにより、格子間の隙間が増大し、格子への炭素の取込みが増したためと考えられる。

一方、前記ホウ素濃度が1×1019atoms/cm3を超える場合、炭素含有濃度が上記において規定した上限値を超えて、結晶性が悪化する。

多層バッファ層2を構成する2種のAlGaN系単結晶層について、上記のように膜厚に差をつけて形成することにより、基板と窒化物半導体による多層バッファ層との間で生じる応力の制御性が向上し、例えば、4インチ径の基板において、反りを30μm以下に抑制することができる。

一方、前記AlxGa1-xN単結晶層21の厚さが50nmを超える場合、あるいはまた、AlyGa1-yN単結晶層22の厚さが500nm未満である場合、製造コストが高くなり、また、それに見合った効果が得られない。

積層組数が少なすぎると、膜成長過程において、多層バッファ層による応力緩和が十分でなく、クラックや反りの抑制効果が十分に得られない。

一方、積層組数が多すぎる場合、コスト高となり、製造効率の点でも劣り、好ましくない。

電子走行層31中に炭素が存在すると、電子が散乱されて移動度が低下するため、デバイスの高速性が低下することから、炭素含有濃度は低い方が好ましいが、前記炭素含有濃度が5×1017atoms/cm3以下であれば、デバイスの高速性の差が小さい。

なお、二次イオン質量分析(SIMS)法による測定では、現在の技術水準では、炭素濃度の検出下限は5×1016atoms/cm3であり、5×1017atoms/cm3を超えた場合に、デバイスの高速性の著しい低下が確認された。

電子走行層31中にアルミニウム(Al)が存在すると、電子が散乱されて移動度が低下するため、この場合も、デバイスの高速性が低下する。このため、Al濃度は低いほどよいが、電子走行層31の形成時において、炉内の残留Alの混入を考慮すると、z=0とすることは実際上困難であるため、意図的に含有させる濃度以下として、z≦0.01であることが好ましい。

より好ましくは、z=0、すなわち、前記電子走行層31はGaN層がよい。このように、電子走行層31をGaN層とし、前記多層バッファ層2とAl濃度の差をつけることは、物理的には、フェルミ準位が伝導帯から離れることなり、ノーマリオフ化の観点からも好ましい。

ノーマリオフ型とは、ゲート電極と呼ばれる制電電極に電圧を印加しない場合(電圧ゼロ)、停止(オフ)状態となり、プラス電圧を印加すると、動作(オン)状態となるものである。

これに対して、ノーマリオン型とは、ゲート電極(制電電極)に電圧を印加しなくても(電圧ゼロ)、動作(オン)状態となり、マイナス電圧を印加すると、停止(オフ)状態となるものである。

回路の安全性等の観点から、スイッチングデバイスとしては、ノーマリオン型よりもノーマリオフ型の方が望まれており、本発明に係る化合物半導体基板は、デバイス形成に、非常に有用である。

窒化物半導体をSi単結晶基板上にエピタキシャル成長させることにより、従来のSi半導体製造プロセスにおいて用いられている装置および技術を利用することができ、大口径かつ低コストでの製造が可能となる。

SiとGaは非常に反応性が高く、成長初期においてSi基板表面にGaが付着した場合、メルトバックエッチング反応により、Si単結晶基板表面に荒れが生じる。

このため、前記初期バッファは、多層バッファ層を形成する前のSi単結晶基板表面の保護および下地として有効である。

また、各層をエピタキシャル成長させる際に用いられる原料も、下記実施例で用いられているものに限定されるものではなく、例えば、炭素を含有させるための原料ガスは、メタン以外に、アセチレン、エタン、プロパン、トリメチルアルミニウム、トリメチルガリウムであってもよい。

下記に示すような各条件にて化合物半導体基板の試料を作製し、以下のようにして、各基板およびそれを用いて作製したデバイスの評価を行った。

各化合物半導体基板試料について、電子走行層31として用いられるAlzGa1-zN単結晶層における転位密度を、透過型電子顕微鏡により評価した。また、反りおよびクラックの発生についても、レーザ変位計および光学顕微鏡により評価した。

各化合物半導体基板試料に、リセスゲート領域および素子分離領域の溝をドライエッチングにより形成し、活性層側にゲート電極としてAu電極を、ソースおよびドレイン電極としてAl電極を、また、Si基板の裏面側に裏面電極としてAl電極を、それぞれ真空蒸着により形成し、化合物半導体デバイスを作製した。

続いて、ゲート電極にピンチオフ電圧を印加しつつ、ソース−ドレイン電極間に電圧を印加した際の電流−電圧特性を測定し、耐電圧特性を求めた。

なお、デバイスの測定の際、ソース電極と裏面電極を電気的にショートさせた。

[試料1](標準試料)

図1に示すような層構造を備えた化合物半導体基板を、以下の工程により作製した。

まず、直径4インチのSi単結晶基板1をMOCVD装置にセットし、原料ガスとしてトリメチルアルミニウム(TMA)ガス、NH3ガス、メタンガスおよびジボランガスを用い、1000℃での気相成長により、炭素を1×1020atoms/cm3含む厚さ20nmのAlN単結晶層(AlxGa1-xN単結晶層(x=1))21を形成し、さらにその上に、原料ガスとして、トリメチルガリウム(TMG)ガス、TMAガス、NH3ガス、メタンガスおよびジボランガスを用い、1000℃での気相成長により、炭素を5×1019atoms/cm3含む厚さ80nmのGaN単結晶層(AlyGa1-yN単結晶層(y=0.2))22を積層させ、これらを同様の工程にて、炭素含有濃度が、いずれも、それぞれ、前記基板側から前記活性層側に向かって減少するように、交互に繰り返し、各10層、合計20層積層させ、多層バッファ層2を形成した。

前記多層バッファ層2上に、原料ガスとして、TMGガス、TMAガス、NH3ガスおよびメタンガスを用い、1000℃での気相成長により、炭素を5×1017atoms/cm3含む厚さ1000nmのAl0.02Ga0.98N単結晶層(AlzGa1-zN層(z=0.02))を電子走行層31として積層させ、さらに、厚さ30nmのAl0.25Ga0.75N単結晶による電子供給層32を積層させ、窒化物活性層3を形成して化合物半導体基板を得た。

なお、気相成長により形成した各層の厚さの調整は、ガス流量および供給時間の調整により行った。

試料1において、電子走行層31であるAlzGa1-zN層をGaN層(z=0)、厚さ500nmとし、また、AlyGa1-yN単結晶層22をAl0.2Ga0.8N単結晶層(y=0.2)とし、AlxGa1-xN単結晶層21のxの数値を変化させ、Al0.5Ga0.5N(x=0.5)(試料2)、Al0.6Ga 0.4 N(x=0.6)(試料3)、AlN(x=1)(試料4)とした。それ以外は、試料1と同様の工程にて、化合物半導体基板を作製した。

試料4において、AlyGa1-yN単結晶層22のyの数値を変化させ、GaN(y=0)(試料5)Al0.1Ga0.9N(y=0.1)(試料6)、Al0.5Ga0.5N(y=0.5)(試料7)、Al0.6Ga 0.4 N(y=0.6)(試料8)とした。それ以外は、試料1と同様の工程にて、化合物半導体基板を作製した。

なお、試料1を他の試料と比較する際の標準試料とする。表1において、リーク電流は、試料1を1としたときの相対指数で表す。以下の評価結果においても、同様とする。

試料2および8以外の試料については、ノーマリオフ特性に優れ、デバイスの高速性が向上することが認められた。

試料4において、AlxGa1-xN単結晶層21の炭素含有濃度を下記表2の試料9〜11に示すように変化させた。それ以外は、試料1と同様の工程にて、化合物半導体基板を作製した。

試料4において、AlyGa1-yN単結晶層22の炭素含有濃度を下記表2の試料12〜15に示すように変化させた。それ以外は、試料1と同様の工程にて、化合物半導体基板を作製した。

Si単結晶基板1上に、AlN単結晶層21とAl0.2Ga0.8N単結晶層22を積層させた後、10層目のAlN単結晶層21の炭素含有濃度が3×1020atoms/cm3、10層目のAlN0.2Ga0.8N単結晶層22の炭素含有濃度が2×1020atoms/cm3となるように、いずれの炭素含有濃度も、前記基板側から前記活性層側に向かって一定の割合で増加するように、交互に繰り返し、各10層、合計20層積層させ、多層バッファ層2を形成した。それ以外は、試料1と同様の工程にて、化合物半導体基板を作製した。

また、AlxGa1-xN単結晶層21の炭素含有濃度が1×1021atoms/cm3超(試料11)、AlyGa1-yN単結晶層22の炭素含有濃度が1×1021atoms/cm3超(試料15)の場合は、基板の転位密度が1×1010cm-2超以上であり、結晶性に劣り、デバイスとして好ましくなく、デバイスのリーク電流も大きかった。

また、AlxGa1-xN単結晶層21およびAlyGa1-yN単結晶層22の炭素含有濃度を増加するように傾斜させて積層した場合(試料16)は、基板の転位密度が高く、反りも大きく、クラックが発生した。

試料10,13および14は、応力の制御特性およびノーマリオフ特性に優れ、また、デバイスの高速性が向上することが認められた。

試料4において、AlxGa1-xN単結晶層21およびAlyGa1-yN単結晶層22にホウ素を添加し、試料4を基準として、ホウ素含有濃度を下記表3の試料17〜20に示すように変化させた。それ以外は、試料1と同様の工程にて、化合物半導体基板を作製した。

試料18において、AlxGa1-xN単結晶層21、AlyGa1-yN単結晶層22および電子走行層31であるAlzGa1-zN層の各パラメータを下記表4の試料21〜27に示すように変化させた。それ以外は、試料1と同様の工程にて、化合物半導体基板を作製した。

試料18において、Si単結晶基板1上に、AlN単結晶層21とAl0.2Ga0.8N単結晶層22を交互に繰り返し、それぞれ7層目まで、合計14層積層させた。そして、8層目のAlN単結晶層21の炭素含有濃度を9×1019atoms/cm3、8層目のAlN0.2Ga0.8N単結晶層22の炭素含有濃度を4×1019atoms/cm3として、炭素含有濃度が、いずれも、前記基板側から前記活性層側に向かってわずかに減少するように、交互に繰り返し、それぞれ9層目まで積層した。さらに、10層目のAlN単結晶層21の炭素含有濃度を6×1019atoms/cm3、10層目のAlN0.2Ga0.8N単結晶層22の炭素含有濃度を2×1019atoms/cm3として、炭素含有濃度が減少する割合を変化させ、それぞれ10層目まで、合計20層積層させ、多層バッファ層2を形成した。それ以外は、試料1と同様の工程にて、化合物半導体基板を作製した。

試料28において、10層目のAlN単結晶層21およびAlN0.2Ga0.8N単結晶層22の炭素含有濃度が、それぞれ、下記表5の試料29〜31に示すような数値となるように、いずれも、前記基板側から前記活性層側に向かって一定の割合で減少するように、交互に繰り返し、各10層、合計20層積層させ、多層バッファ層2を形成し、それ以外は、試料1と同様の工程にて、化合物半導体基板を作製した。

試料28において、10層目のAlN単結晶層21の炭素含有濃度が3×1020atoms/cm3、10層目のAlN0.2Ga0.8N単結晶層22の炭素含有濃度が2×1020atoms/cm3となるように、いずれの炭素含有濃度も、前記基板側から前記活性層側に向かって増加するように、交互に繰り返し、各10層、合計20層積層させ、多層バッファ層2を形成し、それ以外は、試料1と同様の工程にて、化合物半導体基板を作製した。

また、試料28〜32の評価結果をまとめて表5に示す。

2 多層バッファ層

21 AlxGa1-xN単結晶層

22 AlyGa1-yN単結晶層

3 窒化物活性層

31 電子走行層

32 電子供給層

Claims (6)

- Si単結晶基板上に、炭素を1×1018atoms/cm3以上1×1021atoms/cm3以下含むAlxGa1-xN単結晶層(0.6≦x≦1.0)と、炭素を1×1017atoms/cm3以上1×1021atoms/cm3以下含むAlyGa1-yN単結晶層(0≦y≦0.5)とが順に交互に繰り返し積層された多層バッファ層と、炭素含有濃度が5×1017atoms/cm3以下である電子走行層と電子供給層からなる窒化物活性層とが順次堆積された構成を備え、

前記AlxGa1-xN単結晶層の炭素含有濃度分布は、前記基板側のAl x Ga 1-x N単結晶層よりも前記活性層側のAl x Ga 1-x N単結晶層の方が炭素含有濃度が低く、

前記AlyGa1-yN単結晶層の炭素含有濃度分布は、前記基板側のAl y Ga 1-y N単結晶層よりも前記活性層側のAl y Ga 1-y N単結晶層の方が炭素含有濃度が低いことを特徴とする化合物半導体基板。 - 前記AlyGa1-yN単結晶層が0.1≦y≦0.5であることを特徴とする請求項1記載の化合物半導体基板。

- 前記AlxGa1-xN単結晶層の炭素含有濃度が、その直上のAlyGa1-yN単結晶層の炭素含有濃度よりも高いことを特徴とする請求項1または2記載の化合物半導体基板。

- 前記多層バッファ層が、ホウ素を5×1016atoms/cm3以上1×1019atoms/cm3以下含んでいることを特徴とする請求項1〜3のいずれかに記載の化合物半導体基板。

- 前記電子走行層がAlzGa1-zN単結晶層(0≦z≦0.01)であることを特徴とする請求項1〜4のいずれかに記載の化合物半導体基板。

- 前記電子走行層の厚さが1nm以上500nm以下であり、ノーマリオフ型スイッチングデバイスに用いられることを特徴とする請求項1〜5のいずれかに記載の化合物半導体基板。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010153634A JP5188545B2 (ja) | 2009-09-14 | 2010-07-06 | 化合物半導体基板 |

| US12/879,035 US8212288B2 (en) | 2009-09-14 | 2010-09-10 | Compound semiconductor substrate comprising a multilayer buffer layer |

| DE102010045196A DE102010045196A1 (de) | 2009-09-14 | 2010-09-13 | Verbindungshalbleitersubstrat |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009211189 | 2009-09-14 | ||

| JP2009211189 | 2009-09-14 | ||

| JP2010153634A JP5188545B2 (ja) | 2009-09-14 | 2010-07-06 | 化合物半導体基板 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011082494A JP2011082494A (ja) | 2011-04-21 |

| JP2011082494A5 JP2011082494A5 (ja) | 2012-10-18 |

| JP5188545B2 true JP5188545B2 (ja) | 2013-04-24 |

Family

ID=43603673

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010153634A Active JP5188545B2 (ja) | 2009-09-14 | 2010-07-06 | 化合物半導体基板 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8212288B2 (ja) |

| JP (1) | JP5188545B2 (ja) |

| DE (1) | DE102010045196A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP3364463A2 (en) | 2017-02-20 | 2018-08-22 | CoorsTek KK | Nitride semiconductor substrate and method for manufactuing the same |

Families Citing this family (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5707767B2 (ja) * | 2010-07-29 | 2015-04-30 | 住友電気工業株式会社 | 半導体装置 |

| JP5649112B2 (ja) * | 2010-07-30 | 2015-01-07 | パナソニック株式会社 | 電界効果トランジスタ |

| JP5810293B2 (ja) * | 2010-11-19 | 2015-11-11 | パナソニックIpマネジメント株式会社 | 窒化物半導体装置 |

| JP5624940B2 (ja) * | 2011-05-17 | 2014-11-12 | 古河電気工業株式会社 | 半導体素子及びその製造方法 |

| JP2012243886A (ja) * | 2011-05-18 | 2012-12-10 | Sharp Corp | 半導体装置 |

| US8796738B2 (en) * | 2011-09-21 | 2014-08-05 | International Rectifier Corporation | Group III-V device structure having a selectively reduced impurity concentration |

| JP5912383B2 (ja) * | 2011-10-03 | 2016-04-27 | クアーズテック株式会社 | 窒化物半導体基板 |

| US9165766B2 (en) * | 2012-02-03 | 2015-10-20 | Transphorm Inc. | Buffer layer structures suited for III-nitride devices with foreign substrates |

| JP6151487B2 (ja) | 2012-07-10 | 2017-06-21 | 富士通株式会社 | 化合物半導体装置及びその製造方法 |

| JP6002508B2 (ja) | 2012-09-03 | 2016-10-05 | 住友化学株式会社 | 窒化物半導体ウェハ |

| JP2014072429A (ja) * | 2012-09-28 | 2014-04-21 | Fujitsu Ltd | 半導体装置 |

| JPWO2014108946A1 (ja) | 2013-01-10 | 2017-01-19 | パナソニックIpマネジメント株式会社 | 電界効果トランジスタ |

| EP2767620A1 (en) * | 2013-02-15 | 2014-08-20 | Azzurro Semiconductors AG | P-doping of group-III-nitride buffer layer structure on a heterosubstrate |

| US9245993B2 (en) * | 2013-03-15 | 2016-01-26 | Transphorm Inc. | Carbon doping semiconductor devices |

| JP2014220407A (ja) * | 2013-05-09 | 2014-11-20 | ローム株式会社 | 窒化物半導体素子 |

| JP2015053328A (ja) * | 2013-09-05 | 2015-03-19 | 富士通株式会社 | 半導体装置 |

| JP2015060987A (ja) * | 2013-09-19 | 2015-03-30 | 富士通株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP2015070064A (ja) * | 2013-09-27 | 2015-04-13 | 富士通株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP6175009B2 (ja) * | 2014-02-06 | 2017-08-02 | 住友化学株式会社 | 高耐圧窒化ガリウム系半導体デバイス及びその製造方法 |

| JP6249868B2 (ja) * | 2014-04-18 | 2017-12-20 | サンケン電気株式会社 | 半導体基板及び半導体素子 |

| JP2016004948A (ja) * | 2014-06-18 | 2016-01-12 | 株式会社東芝 | 半導体装置 |

| US9876143B2 (en) | 2014-10-01 | 2018-01-23 | Rayvio Corporation | Ultraviolet light emitting device doped with boron |

| US9608103B2 (en) * | 2014-10-02 | 2017-03-28 | Toshiba Corporation | High electron mobility transistor with periodically carbon doped gallium nitride |

| TWI657578B (zh) * | 2014-11-07 | 2019-04-21 | 日商住友化學股份有限公司 | 半導體基板及半導體基板的檢查方法 |

| FR3028670B1 (fr) * | 2014-11-18 | 2017-12-22 | Commissariat Energie Atomique | Structure semi-conductrice a couche de semi-conducteur du groupe iii-v ou ii-vi comprenant une structure cristalline a mailles cubiques ou hexagonales |

| JP6473017B2 (ja) | 2015-03-09 | 2019-02-20 | エア・ウォーター株式会社 | 化合物半導体基板 |

| TW201637078A (zh) * | 2015-04-01 | 2016-10-16 | 環球晶圓股份有限公司 | 半導體元件 |

| JP2017163050A (ja) * | 2016-03-10 | 2017-09-14 | 株式会社東芝 | 半導体装置 |

| JP6233476B2 (ja) * | 2016-09-07 | 2017-11-22 | 富士通株式会社 | 化合物半導体装置 |

| JP7179706B2 (ja) * | 2018-12-12 | 2022-11-29 | クアーズテック株式会社 | 窒化物半導体基板 |

| US10825895B2 (en) | 2018-12-12 | 2020-11-03 | Coorstek Kk | Nitride semiconductor substrate |

| US20220029007A1 (en) * | 2020-07-24 | 2022-01-27 | Vanguard International Semiconductor Corporation | Semiconductor structure and semiconductor device |

| US20240112909A1 (en) * | 2021-02-22 | 2024-04-04 | Panasonic Intellectual Property Management Co., Ltd. | Nitride semiconductor epitaxial substrate, method for producing same, and nitride semiconductor device |

| JP7388422B2 (ja) | 2021-12-23 | 2023-11-29 | 信越半導体株式会社 | 窒化物半導体基板の製造方法 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10290051A (ja) * | 1997-04-16 | 1998-10-27 | Furukawa Electric Co Ltd:The | 半導体装置とその製造方法 |

| JP3648386B2 (ja) * | 1998-07-08 | 2005-05-18 | 株式会社東芝 | 半導体素子およびウェーハならびにそれらの製造方法 |

| JP2002100837A (ja) * | 2000-09-25 | 2002-04-05 | Sharp Corp | 窒化物半導体発光素子およびその製造方法 |

| JP2003059948A (ja) * | 2001-08-20 | 2003-02-28 | Sanken Electric Co Ltd | 半導体装置及びその製造方法 |

| JP4514584B2 (ja) * | 2004-11-16 | 2010-07-28 | 富士通株式会社 | 化合物半導体装置及びその製造方法 |

| JP4792814B2 (ja) * | 2005-05-26 | 2011-10-12 | 住友電気工業株式会社 | 高電子移動度トランジスタ、電界効果トランジスタ、エピタキシャル基板、エピタキシャル基板を作製する方法およびiii族窒化物系トランジスタを作製する方法 |

| JP2007067077A (ja) | 2005-08-30 | 2007-03-15 | Nippon Telegr & Teleph Corp <Ntt> | 窒化物半導体素子およびその製造方法 |

| JP5064824B2 (ja) * | 2006-02-20 | 2012-10-31 | 古河電気工業株式会社 | 半導体素子 |

| JP5224311B2 (ja) | 2007-01-05 | 2013-07-03 | 古河電気工業株式会社 | 半導体電子デバイス |

| JP2010239034A (ja) * | 2009-03-31 | 2010-10-21 | Furukawa Electric Co Ltd:The | 半導体装置の製造方法および半導体装置 |

-

2010

- 2010-07-06 JP JP2010153634A patent/JP5188545B2/ja active Active

- 2010-09-10 US US12/879,035 patent/US8212288B2/en active Active

- 2010-09-13 DE DE102010045196A patent/DE102010045196A1/de not_active Ceased

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP3364463A2 (en) | 2017-02-20 | 2018-08-22 | CoorsTek KK | Nitride semiconductor substrate and method for manufactuing the same |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011082494A (ja) | 2011-04-21 |

| US20110062556A1 (en) | 2011-03-17 |

| DE102010045196A1 (de) | 2011-03-24 |

| US8212288B2 (en) | 2012-07-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5188545B2 (ja) | 化合物半導体基板 | |

| US9685323B2 (en) | Buffer layer structures suited for III-nitride devices with foreign substrates | |

| US8426893B2 (en) | Epitaxial substrate for electronic device and method of producing the same | |

| JP5836158B2 (ja) | 歪吸収中間層遷移モジュールを有するiii族窒化物半導体構造 | |

| JP5787417B2 (ja) | 窒化物半導体基板 | |

| US10991577B2 (en) | Method for forming a semiconductor structure for a gallium nitride channel device | |

| US20150349064A1 (en) | Nucleation and buffer layers for group iii-nitride based semiconductor devices | |

| US10818491B2 (en) | Formation of a III-N semiconductor structure | |

| US8994032B2 (en) | III-N material grown on ErAIN buffer on Si substrate | |

| WO2018092689A1 (ja) | 化合物半導体基板の製造方法および化合物半導体基板 | |

| JP6108609B2 (ja) | 窒化物半導体基板 | |

| JP2020113693A (ja) | 化合物半導体基板 | |

| WO2022014592A1 (ja) | 化合物半導体基板および化合物半導体基板の製造方法 | |

| CN210073765U (zh) | 一种AlGaN双异质结高阻缓冲层外延结构 | |

| CN212209534U (zh) | 一种氮化镓外延芯片 | |

| TWI728498B (zh) | 氮化物半導體基板 | |

| JP2006216576A (ja) | 化合物半導体デバイス | |

| CN111682093A (zh) | 一种氮化镓外延芯片及其制备方法 | |

| CN111628061A (zh) | 一种氮化镓外延芯片及其制备方法 | |

| CN115832013A (zh) | AlN缓冲复合层及其制备方法和应用、氮化镓功率器件的外延结构及其制备方法 | |

| JP2019125672A (ja) | 化合物半導体基板 | |

| KR20130142415A (ko) | 질화갈륨계 반도체 소자 및 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120830 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120830 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20120830 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20121024 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121029 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121115 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130121 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130122 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160201 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5188545 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |