JP5085902B2 - 表示装置の製造方法 - Google Patents

表示装置の製造方法 Download PDFInfo

- Publication number

- JP5085902B2 JP5085902B2 JP2006227265A JP2006227265A JP5085902B2 JP 5085902 B2 JP5085902 B2 JP 5085902B2 JP 2006227265 A JP2006227265 A JP 2006227265A JP 2006227265 A JP2006227265 A JP 2006227265A JP 5085902 B2 JP5085902 B2 JP 5085902B2

- Authority

- JP

- Japan

- Prior art keywords

- continuous wave

- wave laser

- region

- manufacturing

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 89

- 229910021417 amorphous silicon Inorganic materials 0.000 claims description 111

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 101

- 239000000758 substrate Substances 0.000 claims description 99

- 238000000034 method Methods 0.000 claims description 83

- 239000004065 semiconductor Substances 0.000 claims description 51

- 239000013078 crystal Substances 0.000 claims description 36

- 239000004973 liquid crystal related substance Substances 0.000 claims description 30

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 25

- 229910052710 silicon Inorganic materials 0.000 claims description 25

- 239000010703 silicon Substances 0.000 claims description 25

- 230000001678 irradiating effect Effects 0.000 claims description 24

- 238000006356 dehydrogenation reaction Methods 0.000 claims description 19

- 239000000463 material Substances 0.000 claims description 10

- 230000002093 peripheral effect Effects 0.000 claims description 8

- 238000002844 melting Methods 0.000 claims description 7

- 230000008018 melting Effects 0.000 claims description 7

- 229910021424 microcrystalline silicon Inorganic materials 0.000 claims 1

- 239000011521 glass Substances 0.000 description 37

- 238000010586 diagram Methods 0.000 description 20

- 230000003287 optical effect Effects 0.000 description 19

- 238000009826 distribution Methods 0.000 description 18

- 230000004048 modification Effects 0.000 description 11

- 238000012986 modification Methods 0.000 description 11

- 238000002425 crystallisation Methods 0.000 description 9

- 230000008025 crystallization Effects 0.000 description 9

- 230000010355 oscillation Effects 0.000 description 9

- 239000011159 matrix material Substances 0.000 description 6

- 238000000137 annealing Methods 0.000 description 5

- 230000007423 decrease Effects 0.000 description 5

- 230000000694 effects Effects 0.000 description 4

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 229910052739 hydrogen Inorganic materials 0.000 description 3

- 239000000155 melt Substances 0.000 description 3

- 239000013081 microcrystal Substances 0.000 description 3

- 239000003566 sealing material Substances 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000008014 freezing Effects 0.000 description 1

- 238000007710 freezing Methods 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02532—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02675—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth using laser beams

- H01L21/02683—Continuous wave laser beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02664—Aftertreatments

- H01L21/02667—Crystallisation or recrystallisation of non-monocrystalline semiconductor materials, e.g. regrowth

- H01L21/02691—Scanning of a beam

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

- H10D86/021—Manufacture or treatment of multiple TFTs

- H10D86/0221—Manufacture or treatment of multiple TFTs comprising manufacture, treatment or patterning of TFT semiconductor bodies

- H10D86/0223—Manufacture or treatment of multiple TFTs comprising manufacture, treatment or patterning of TFT semiconductor bodies comprising crystallisation of amorphous, microcrystalline or polycrystalline semiconductor materials

- H10D86/0229—Manufacture or treatment of multiple TFTs comprising manufacture, treatment or patterning of TFT semiconductor bodies comprising crystallisation of amorphous, microcrystalline or polycrystalline semiconductor materials characterised by control of the annealing or irradiation parameters

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Optics & Photonics (AREA)

- Recrystallisation Techniques (AREA)

- Thin Film Transistor (AREA)

Description

なお、実施例を説明するための全図において、同一機能を有するものは、同一符号を付け、その繰り返しの説明は省略する。

図4(a)は、アモルファスシリコン膜を成膜した直後のマザーガラスの模式平面図である。図4(b)は、図4(a)のB−B’線における模式断面図である。図5(a)は、アモルファスシリコン膜の一部を多結晶シリコン化した直後のマザーガラスの模式平面図である。図5(b)は、図5(a)のC−C’線における模式断面図である。図6は、多結晶シリコン化した領域およびその周辺領域を拡大して示した模式平面図である。

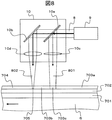

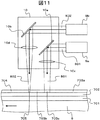

図7は、実施例1の製造方法における連続発振レーザの照射方法を説明するための模式斜視図である。図8は、図7の連続発振レーザが照射されている領域をx方向と平行な面でみた模式断面図である。図9は、照射する連続発振レーザのエネルギー分布とエネルギー密度の関係を示す模式グラフ図である。なお、図9のエネルギー分布は、連続発振レーザの走査方向(移動方向)と平行な面でみた分布である。

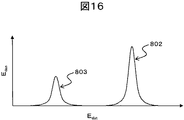

図15は、実施例2の製造方法における連続発振レーザの照射方法を説明するための模式断面図である。図16は、照射する連続発振レーザのエネルギー分布とエネルギー密度の関係を示す模式グラフ図である。なお、図16は、脱水素化されたアモルファスシリコンを溶融させる第2の連続発振レーザと、多結晶シリコン化された領域に照射する第3の連続発振レーザのエネルギー分布とエネルギー密度の関係を示しており、横軸がエネルギー分布Edistであり、縦軸がエネルギー密度Edenである。また、図16のエネルギー分布Edistは、連続発振レーザの走査方向(移動方向)と平行な面でみた分布である。

2…対向基板

3…液晶材料

4…シール材

5a,5b…偏光板

6…マザーガラス

701…シリコン窒化膜(SiN膜)

702…シリコン酸化膜(SiO膜)

703a…水素化したアモルファスシリコン(膜)

703b…脱水素化されたアモルファスシリコン(膜)

704,704a,704b…多結晶シリコン

704p…帯状結晶

704w…帯状結晶(擬似単結晶)

705…溶融したシリコン

801…第1の連続発振レーザ

802…第2の連続発振レーザ

803…第3の連続発振レーザ

9…レーザ発振器

9a…第1のレーザ発振器

9b…第2のレーザ発振器

10…光学系

10a…ハーフミラー

10b…全反射ミラー(第2の全反射ミラー)

10c…第1のレンズ

10d…第2のレンズ

10e…第1の全反射ミラー

10f…第3のレンズ

GL,GLm,GLm+1…走査信号線

DL,DLn,GLn+1…走査信号線

PX…画素電極

CT…共通電極

DA…表示領域

DRV1…第1の駆動回路

DRV2…第2の駆動回路

Claims (16)

- 基板の上に水素化したアモルファスシリコン膜を成膜する第1の工程と、

前記水素化したアモルファスシリコン膜のあらかじめ定められた領域を脱水素化した後、前記脱水素化された領域のアモルファスシリコンを溶融、結晶化して多結晶シリコンにする第2の工程とを有し、

前記基板の表示領域にアモルファスシリコンを用いたTFT素子を有する複数の画素を形成するとともに、該表示領域の外側に、多結晶シリコンを用いた複数個の半導体素子を有する駆動回路を形成する表示装置の製造方法であって、

前記第2の工程は、前記基板の前記表示領域の外側にある前記駆動回路を形成する領域およびその周辺領域のみを第1の連続発振レーザを照射して脱水素化した後、前記脱水素化された領域のみに第2の連続発振レーザを照射して前記アモルファスシリコンを前記多結晶シリコンにし、

前記第1の連続発振レーザを照射する領域は、前記第2の連続発振レーザを照射する領域よりも広いことを特徴とする表示装置の製造方法。 - 前記第1の連続発振レーザおよび前記第2の連続発振レーザは、前記基板の上を走査しながら照射し、

前記第1の連続発振レーザのエネルギー密度は、前記第2の連続発振レーザのエネルギー密度よりも低く、

前記第1の連続発振レーザおよび前記第2の連続発振レーザが照射する領域の各点は、前記第1の連続発振レーザが照射されている時間が、前記第2の連続発振レーザが照射されている時間よりも長いことを特徴とする請求項1に記載の表示装置の製造方法。 - 前記第1の連続発振レーザの走査方向のビーム幅が、前記第2の連続発振レーザの前記走査方向のビーム幅よりも広いことを特徴とする請求項2に記載の表示装置の製造方法。

- 前記第1の連続発振レーザの走査速度と、前記第2の連続発振レーザの走査速度とが異なることを特徴とする請求項2に記載の表示装置の製造方法。

- 前記第1の連続発振レーザの走査速度が、前記第2の連続発振レーザの走査速度よりも遅いことを特徴とする請求項4に記載の表示装置の製造方法。

- 前記第2の工程は、前記基板の上のある帯状領域を第1の方向に走査する間に前記第1の連続発振レーザおよび前記第2の連続発振レーザを照射することを特徴とする請求項1乃至請求項5のいずれか1項に記載の表示装置の製造方法。

- 前記第2の工程は、前記基板の上のある帯状領域を第1の方向に走査した後、前記基板の上の前記ある帯状領域とは別の帯状領域を前記第1の方向と反対の方向に走査することを特徴とする請求項6に記載の表示装置の製造方法。

- 前記第2の工程は、前記第2の連続発振レーザを照射して前記多結晶シリコン化された領域に、第3の連続発振レーザを照射することを特徴とする請求項1乃至請求項7のいずれか1項に記載の表示装置の製造方法。

- 前記第2の工程は、前記基板の上のある帯状領域を第1の方向に走査する間に前記第1の連続発振レーザ、前記第2の連続発振レーザ、および前記第3の連続発振レーザを照射することを特徴とする請求項8に記載の表示装置の製造方法。

- 前記第2の工程は、前記基板の上のある帯状領域を第1の方向に走査した後、前記ある帯状領域とは別の帯状領域を前記第1の方向と反対の方向に走査し、

前記別の帯状領域を走査するときは、前記第3の連続発振レーザを照射して前記水素化したアモルファスシリコン膜を脱水素化し、前記第3の連続発振レーザによって脱水素化されたアモルファスシリコンに前記第2の連続発振レーザを照射して多結晶シリコン化し、前記第2の連続発振レーザを照射して前記多結晶シリコン化された領域に前記第1の連続発振レーザを照射することを特徴とする請求項8または請求項9に記載の表示装置の製造方法。 - 前記基板の上を前記第1の方向に走査するときと、前記第1の方向と反対の方向に走査するときで、前記第1の連続発振レーザの焦点と前記第3の連続発振レーザの焦点を相互に切り替えることを特徴とする請求項10に記載の表示装置の製造方法。

- 基板の上にTFT素子が設けられたTFT基板を形成する工程と、対向基板を形成する工程と、前記TFT基板と前記対向基板との間に液晶材料を封入して液晶表示パネルを形成する工程とを有する表示装置の製造方法であって、

前記TFT基板を形成する工程は、前記基板の上に水素化したアモルファスシリコン膜を成膜する第1の工程と、

前記水素化したアモルファスシリコン膜のあらかじめ定められた領域を脱水素化した後、前記脱水素化された領域のアモルファスシリコンを溶融、結晶化する第2の工程とを有し、

前記基板の表示領域にアモルファスシリコンを用いたTFT素子を有する複数の画素を形成するとともに、該表示領域の外側に前記第2の工程で結晶化されたシリコンを用いた複数のTFT素子を有する駆動回路を形成し、

前記第2の工程は、前記基板の前記表示領域の外側にある前記駆動回路を形成する領域およびその周辺領域のみを第1の連続発振レーザを照射して脱水素化した後、前記脱水素化された領域のみに第2の連続発振レーザを照射して前記アモルファスシリコンを溶融、結晶化し、

前記第1の連続発振レーザを照射する領域は、前記第2の連続発振レーザを照射する領域よりも広いことを特徴とする表示装置の製造方法。 - 前記第1の連続発振レーザおよび前記第2の連続発振レーザは、前記基板の上を走査しながら照射し、

前記第1の連続発振レーザのエネルギー密度は、前記第2の連続発振レーザのエネルギー密度よりも低く、

前記第1の連続発振レーザおよび前記第2の連続発振レーザが照射する領域の各点は、前記第1の連続発振レーザが照射されている時間が、前記第2の連続発振レーザが照射されている時間よりも長いことを特徴とする請求項12に記載の表示装置の製造方法。 - 前記第1の連続発振レーザの走査方向のビーム幅が、前記第2の連続発振レーザの前記走査方向のビーム幅よりも広いことを特徴とする請求項13に記載の表示装置の製造方法。

- 前記第2の工程は、前記アモルファスシリコンを溶融、結晶化させて多結晶シリコンに改質することを特徴とする請求項12乃至請求項14のいずれか1項に記載の表示装置の製造方法。

- 前記第2の工程は、前記アモルファスシリコンを溶融、結晶化させて帯状結晶シリコン、粒状結晶シリコン、微結晶シリコンのいずれかに改質することを特徴とする請求項12乃至請求項14のいずれか1項に記載の表示装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006227265A JP5085902B2 (ja) | 2006-08-24 | 2006-08-24 | 表示装置の製造方法 |

| US11/882,828 US7732268B2 (en) | 2006-08-24 | 2007-08-06 | Manufacturing method of display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006227265A JP5085902B2 (ja) | 2006-08-24 | 2006-08-24 | 表示装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008053394A JP2008053394A (ja) | 2008-03-06 |

| JP2008053394A5 JP2008053394A5 (ja) | 2009-07-09 |

| JP5085902B2 true JP5085902B2 (ja) | 2012-11-28 |

Family

ID=39197202

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006227265A Expired - Fee Related JP5085902B2 (ja) | 2006-08-24 | 2006-08-24 | 表示装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7732268B2 (ja) |

| JP (1) | JP5085902B2 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5068972B2 (ja) * | 2006-09-12 | 2012-11-07 | 富士フイルム株式会社 | レーザアニール装置、半導体膜基板、素子基板、及び電気光学装置 |

| RU2476954C2 (ru) | 2008-09-18 | 2013-02-27 | Шарп Кабусики Кайся | Базовая плата, способ производства базовой платы и подложка устройства |

| JP2010108957A (ja) * | 2008-10-28 | 2010-05-13 | Hitachi Displays Ltd | 表示装置およびその製造方法 |

| US9111803B2 (en) * | 2011-10-03 | 2015-08-18 | Joled Inc. | Thin-film device, thin-film device array, and method of manufacturing thin-film device |

| KR102014167B1 (ko) * | 2012-12-06 | 2019-10-22 | 삼성디스플레이 주식회사 | 다결정 실리콘층의 제조 방법, 상기 다결정 실리콘층의 제조 방법을 포함하는 유기 발광 표시 장치의 제조 방법, 및 그 제조 방법에 의해 제조된 유기 발광 표시 장치 |

| WO2016068713A1 (en) * | 2014-10-30 | 2016-05-06 | Technische Universiteit Delft | Low-temperature formation of thin-film structures |

| NL2013715B1 (en) * | 2014-10-30 | 2016-10-04 | Univ Delft Tech | Low-temperature formation of thin-film structures. |

| JP7203417B2 (ja) | 2019-01-31 | 2023-01-13 | 株式会社ブイ・テクノロジー | レーザアニール方法、レーザアニール装置、およびtft基板 |

| WO2022181029A1 (ja) * | 2021-02-26 | 2022-09-01 | 株式会社ブイ・テクノロジー | レーザアニール装置およびレーザアニール方法 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62160781A (ja) * | 1986-01-09 | 1987-07-16 | Agency Of Ind Science & Technol | レ−ザ光照射装置 |

| JP3026520B2 (ja) * | 1991-08-23 | 2000-03-27 | 東京エレクトロン株式会社 | 液晶表示装置の製造装置 |

| JPH0661172A (ja) * | 1992-08-07 | 1994-03-04 | Fuji Xerox Co Ltd | エキシマレ−ザアニ−ル装置 |

| JP3196132B2 (ja) * | 1992-11-16 | 2001-08-06 | 東京エレクトロン株式会社 | 液晶ディスプレイ基板の製造方法、半導体結晶の評価方法、半導体結晶薄膜の製造方法及び半導体結晶薄膜の製造装置 |

| SG46344A1 (en) * | 1992-11-16 | 1998-02-20 | Tokyo Electron Ltd | Method and apparatus for manufacturing a liquid crystal display substrate and apparatus and method for evaluating semiconductor crystals |

| JPH0883765A (ja) * | 1994-07-14 | 1996-03-26 | Sanyo Electric Co Ltd | 多結晶半導体膜の製造方法 |

| TW457553B (en) * | 1999-01-08 | 2001-10-01 | Sony Corp | Process for producing thin film semiconductor device and laser irradiation apparatus |

| US20030017658A1 (en) * | 2000-02-15 | 2003-01-23 | Hikaru Nishitani | Non-single crystal film, substrate with non-single crystal film, method and apparatus for producing the same, method and apparatus for inspecting the same, thin film trasistor, thin film transistor array and image display using it |

| JP2002064060A (ja) * | 2000-08-22 | 2002-02-28 | Matsushita Electric Ind Co Ltd | 非結晶薄膜のレーザーアニール方法とその装置 |

| US6737672B2 (en) * | 2000-08-25 | 2004-05-18 | Fujitsu Limited | Semiconductor device, manufacturing method thereof, and semiconductor manufacturing apparatus |

| JP2002158173A (ja) | 2000-09-05 | 2002-05-31 | Sony Corp | 薄膜の製造方法、半導体薄膜、半導体装置、半導体薄膜の製造方法、及び半導体薄膜製造装置 |

| US20020072252A1 (en) * | 2000-09-05 | 2002-06-13 | Hideharu Nakajima | Process for production of thin film semiconductor thin film, semiconductor device, process for production of semiconductor thin film, and apparatus for production of semiconductor thin film |

-

2006

- 2006-08-24 JP JP2006227265A patent/JP5085902B2/ja not_active Expired - Fee Related

-

2007

- 2007-08-06 US US11/882,828 patent/US7732268B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008053394A (ja) | 2008-03-06 |

| US20080050893A1 (en) | 2008-02-28 |

| US7732268B2 (en) | 2010-06-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5085902B2 (ja) | 表示装置の製造方法 | |

| US8598588B2 (en) | Systems and methods for processing a film, and thin films | |

| US7507645B2 (en) | Method of forming polycrystalline semiconductor layer and thin film transistor using the same | |

| US7943936B2 (en) | Crystallizing method, thin-film transistor manufacturing method, thin-film transistor, and display device | |

| KR100740124B1 (ko) | 다결정 실리콘 박막 트랜지스터 및 그 제조방법 | |

| WO2002031871A1 (en) | Method and apparatus for producing polysilicon film, semiconductor device, and method of manufacture thereof | |

| JP2011101022A (ja) | 半導体装置の作製方法 | |

| US7033434B2 (en) | Mask for crystallizing, method of crystallizing amorphous silicon and method of manufacturing array substrate using the same | |

| US20080070386A1 (en) | Device for irradiating a laser beam | |

| KR20140018081A (ko) | 박막 반도체 장치의 제조 방법, 박막 반도체 어레이 기판의 제조 방법, 결정성 실리콘 박막의 형성 방법, 및 결정성 실리콘 박막의 형성 장치 | |

| US20030148566A1 (en) | Production method for flat panel display | |

| JP4169073B2 (ja) | 薄膜半導体装置および薄膜半導体装置の製造方法 | |

| JP2005197658A (ja) | 多結晶シリコン膜の形成方法 | |

| US7651931B2 (en) | Laser beam projection mask, and laser beam machining method and laser beam machine using same | |

| US7541615B2 (en) | Display device including thin film transistors | |

| KR20120048239A (ko) | 연속측면고상화(Sequential Lateral Solidification:SLS)를 이용한 결정화 장치 | |

| JP4769491B2 (ja) | 結晶化方法、薄膜トランジスタの製造方法、薄膜トランジスタおよび表示装置 | |

| US7696449B2 (en) | Silicon crystallizing device | |

| JP2006086447A (ja) | 半導体薄膜の製造方法および半導体薄膜の製造装置 | |

| JPH0945632A (ja) | レーザーアニール方法及び半導体膜の溶融結晶化方法 | |

| JP2008053528A (ja) | 表示装置の製造方法 | |

| KR100781440B1 (ko) | 다결정실리콘막 형성방법 | |

| JP2008053396A (ja) | 表示装置の製造方法 | |

| JP2010056433A (ja) | 平面表示装置の製造方法 | |

| KR20050121548A (ko) | 실리콘 결정화 방법과 이를 이용한 박막트랜지스터 기판의제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090527 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090527 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20110218 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20110218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120426 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120508 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120515 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120904 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120906 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5085902 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150914 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |