JP5020051B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP5020051B2 JP5020051B2 JP2007322824A JP2007322824A JP5020051B2 JP 5020051 B2 JP5020051 B2 JP 5020051B2 JP 2007322824 A JP2007322824 A JP 2007322824A JP 2007322824 A JP2007322824 A JP 2007322824A JP 5020051 B2 JP5020051 B2 JP 5020051B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor device

- substrate

- bump

- protruding electrode

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

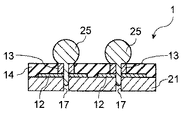

12 電極パット

13 突起電極

14 保護層

16 ボイド

17 貫通孔部

21 半導体基板(基板部)

25 半田ボール(バンプ部)

25a 半田ペースト

Claims (12)

- 基板部と、

前記基板部の表面を被覆する保護層と、

前記基板部上に前記保護層から露出して設けられ、前記基板部と電気的に接続された突起電極と、

前記突起電極と電気的に接続されたバンプ部と、

前記基板部及び前記突起電極を貫通する貫通孔部とを備え、

前記バンプ部は、平面的に見た場合に、前記貫通孔部と少なくとも一部が重なるように配されており、

前記基板部は、一方の表面に集積回路部を含むシリコン基板であり、

前記バンプ部は、半田ボールであり、

前記突起電極の表面が前記保護層の表面と面一であることを特徴とする半導体装置。 - 前記基板部の一主面上に配線部が形成され、

前記突起電極は、前記基板部の前記配線部上に設けられるとともに、前記配線部と電気的に接続され、

前記貫通孔部は、前記基板部の厚さ方向に、前記基板部と前記突起電極と前記配線部とを連続して貫通することを特徴とする請求項1に記載の半導体装置。 - 前記突起電極は、前記配線部と前記バンプ部との間に形成され、

前記バンプ部は、前記突起電極を介して、前記配線部と電気的に接続されていることを特徴とする請求項2に記載の半導体装置。 - 前記配線部は、Cuで形成されていることを特徴とする請求項2又は請求項3に記載の半導体装置。

- 前記基板部と電気的に接続された電極パッドをさらに備え、

前記基板部は、半導体チップであり、

前記突起電極は、前記電極パッド上に形成され、

前記貫通孔部は、さらに前記電極パッドを貫通し、

前記貫通孔部上に前記バンプ部を有することを特徴とする請求項1に記載の半導体装置。 - 前記電極パッドは前記半導体チップ上に形成され、

前記貫通孔部は、断面視において、前記半導体チップと前記電極パッドと前記突起電極とを貫通し、

断面視において、前記貫通孔部上に前記バンプ部を有することを特徴とする請求項5に記載の半導体装置。 - 断面視において、前記貫通孔部に前記バンプ部の一部が入り込んでいることを特徴とする請求項5又は請求項6に記載の半導体装置。

- 前記電極パッドは、Cuで形成されていることを特徴とする請求項5〜請求項7のいずれかに記載の半導体装置。

- 前記電極パッドは、前記半導体チップの一主面上に形成された配線部の一部であることを特徴とする請求項5〜請求項8のいずれかに記載の半導体装置。

- 前記突起電極は、前記バンプ部と濡れ性が良好な材料で形成されていることを特徴とする請求項1〜請求項9のいずれかに記載の半導体装置。

- 前記突起電極は、Cuで形成されていることを特徴とする請求項1〜請求項10のいずれかに記載の半導体装置。

- 前記貫通孔部内において、前記バンプ部の一部によって挟まれたボイドを有することを特徴とする請求項1〜請求項11のいずれかに記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007322824A JP5020051B2 (ja) | 2007-12-14 | 2007-12-14 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007322824A JP5020051B2 (ja) | 2007-12-14 | 2007-12-14 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009147106A JP2009147106A (ja) | 2009-07-02 |

| JP2009147106A5 JP2009147106A5 (ja) | 2010-12-16 |

| JP5020051B2 true JP5020051B2 (ja) | 2012-09-05 |

Family

ID=40917380

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007322824A Expired - Fee Related JP5020051B2 (ja) | 2007-12-14 | 2007-12-14 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5020051B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20120298406A1 (en) * | 2011-05-23 | 2012-11-29 | International Business Machines Corporation | Reduced stress gull wing solder joints for printed wiring board connections |

| WO2015082951A1 (en) * | 2013-12-06 | 2015-06-11 | Commissariat à l'énergie atomique et aux énergies alternatives | Method of hermetically sealing a hole with a fuse material |

| US10497846B2 (en) * | 2017-07-11 | 2019-12-03 | Lg Innotek Co., Ltd. | Light emitting device package |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04258127A (ja) * | 1991-02-13 | 1992-09-14 | Fujitsu Ltd | バンプ接合パッド構造 |

| KR100216839B1 (ko) * | 1996-04-01 | 1999-09-01 | 김규현 | Bga 반도체 패키지의 솔더 볼 랜드 메탈 구조 |

| JP2001223293A (ja) * | 2000-02-09 | 2001-08-17 | Nec Corp | 半導体装置及びその製造方法 |

| JP2002270718A (ja) * | 2001-03-07 | 2002-09-20 | Seiko Epson Corp | 配線基板及びその製造方法、半導体装置及びその製造方法、回路基板並びに電子機器 |

-

2007

- 2007-12-14 JP JP2007322824A patent/JP5020051B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009147106A (ja) | 2009-07-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2007287712A (ja) | 半導体装置、半導体装置の実装構造、及びそれらの製造方法 | |

| JP2017152646A (ja) | 電子部品、電子装置及び電子機器 | |

| JP2006339596A (ja) | インタポーザおよび半導体装置 | |

| WO2012035688A1 (ja) | 半導体装置、半導体装置ユニット、および半導体装置の製造方法 | |

| KR20090126762A (ko) | 반도체칩이 실장된 인쇄회로기판 및 그 제조방법 | |

| JP2006202969A (ja) | 半導体装置およびその実装体 | |

| JP2008218629A (ja) | 半導体パッケージおよび電子部品 | |

| US20080042279A1 (en) | Mounting structure of semiconductor device having flux and under fill resin layer and method of mounting semiconductor device | |

| JP2009164607A (ja) | ボンディングパッド構造物及びその製造方法、並びにボンディングパッド構造物を有する半導体パッケージ | |

| JP2009004454A (ja) | 電極構造体及びその形成方法と電子部品及び実装基板 | |

| JP5020051B2 (ja) | 半導体装置 | |

| JP4509673B2 (ja) | 電子部品及びその製造方法、並びに電子装置 | |

| JP2009111307A (ja) | 部品内蔵配線板 | |

| JP2008305931A (ja) | 半導体装置及びその製造方法 | |

| JP5437553B2 (ja) | 半導体素子及び半導体装置 | |

| JP2004128290A (ja) | 半導体装置 | |

| JP2009049115A (ja) | 半導体装置及びその製造方法 | |

| JP2008218759A (ja) | 半導体チップの電極構造、並びにその半導体チップがフリップチップ実装された半導体装置及びその製造方法 | |

| JP4728079B2 (ja) | 半導体装置用基板および半導体装置 | |

| JP2013211497A (ja) | 部品接合構造 | |

| JP2005183868A (ja) | 半導体装置およびその実装構造 | |

| JP4322903B2 (ja) | 半導体装置、および半導体装置の製造方法 | |

| KR20100097845A (ko) | 범프 구조물 및 이를 갖는 반도체 패키지 | |

| JP2007258354A (ja) | 半導体装置の製造方法 | |

| JP2006120716A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101028 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101210 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120213 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120221 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120416 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120515 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120612 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5020051 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150622 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D03 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |