JP4931329B2 - コンデンサ、配線基板、デカップリング回路及び高周波回路 - Google Patents

コンデンサ、配線基板、デカップリング回路及び高周波回路 Download PDFInfo

- Publication number

- JP4931329B2 JP4931329B2 JP2003335812A JP2003335812A JP4931329B2 JP 4931329 B2 JP4931329 B2 JP 4931329B2 JP 2003335812 A JP2003335812 A JP 2003335812A JP 2003335812 A JP2003335812 A JP 2003335812A JP 4931329 B2 JP4931329 B2 JP 4931329B2

- Authority

- JP

- Japan

- Prior art keywords

- conductor

- capacitor

- layer

- conductors

- conductor layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

近年のMPUの高速、高周波化に伴って、低ESL化が求められている。

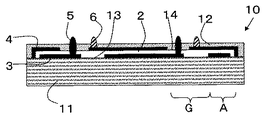

積層体51が構成されている。そして、ここでは、第1及び第2貫通導体55、56が、積層体51の一方の最表面に露出し、夫々第1及び第2接続端子57、58に接続され、積層コンデンサ50が構成されている。さらに、第1及び第2導体層53、54内に、第2及び第1貫通導体56、55とは夫々接続しない第1及び第2非導体形成領域63、64が形成されている。

2つの前記第1貫通導体及び2つの前記第2貫通導体が格子状に配置されて格子の縦横の方向に隣接する前記第1貫通導体の前記第1非導体形成領域と前記第2貫通導体の前記第2非導体形成領域とが積層方向に重なり合った貫通導体群を複数形成しているとともに、複数の前記貫通導体群が互いに一様な距離をもって配置され、前記第1導体層及び前記第2導体層の周縁部と前記貫通導体群との間に、前記格子の縦横の方向に隣接する前記第1貫通導体と前記第2貫通導体との中心間の間隔以上の幅で、前記第1導体層及び前記第2導体層が存在していることを特徴とするものである。

1 積層体

2 誘電体層

3 第1の導体層(内部電極層)

4 第2の導体層(内部電極層)

5 第1の貫通導体(ビアホール導体)

6 第2の貫通導体(ビアホール導体)

13 第1の非導体形成領域

14 第2の非導体形成領域

A 静電容量領域

G 貫通導体群

20 MPU

21 配線基板

22 キャビティ

23 電源側導体層

24 グランド側導体層

40 MPUチップ

37、38 MPUチップの端子

31 マザーボード

Claims (6)

- 誘電体層の一方主面に第1導体層が、前記誘電体層の他方主面に第2導体層が配設されるとともに、前記誘電体層の厚み方向に、前記第2導体層と第1非導体形成領域によって隔てられ、且つ前記第1導体層に接続される複数の第1貫通導体と、前記第1導体層と第2非導体形成領域によって隔てられ、且つ前記第2導体層に接続される複数の第2貫通導体とが形成されてなるコンデンサにおいて、

2つの前記第1貫通導体及び2つの前記第2貫通導体が格子状に配置されて格子の縦横の方向に隣接する前記第1貫通導体の前記第1非導体形成領域と前記第2貫通導体の前記第2非導体形成領域とが積層方向に重なり合った貫通導体群を複数形成しているとともに、複数の前記貫通導体群が互いに一様な距離をもって配置され、前記第1導体層及び前記第2導体層の周縁部と前記貫通導体群との間に、前記格子の縦横の方向に隣接する前記第1貫通導体と前記第2貫通導体との中心間の間隔以上の幅で、前記第1導体層及び前記第2導体層が存在していることを特徴とするコンデンサ。 - 前記貫通導体群が、前記第1貫通導体及び前記第2貫通導体並びに前記第1導体層及び前記第2導体層を流れる電流によって誘起される磁界を互いに相殺するように配置されていることを特徴とする請求項1記載のコンデンサ。

- 前記貫通導体群内において、前記第1貫通導体及び前記第2貫通導体が、実質的に正方形の各頂点に位置する分布状態をもって互いに隣り合うように配置されていることを特徴とする請求項1又は2記載のコンデンサ。

- 請求項1乃至3のうちいずれかに記載のコンデンサを備えたことを特徴とする配線基板。

- 請求項1乃至3のうちいずれかに記載のコンデンサを備えたことを特徴とするデカップリング回路。

- 請求項1乃至3のうちいずれかに記載のコンデンサを備えたことを特徴とする高周波回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003335812A JP4931329B2 (ja) | 2002-09-27 | 2003-09-26 | コンデンサ、配線基板、デカップリング回路及び高周波回路 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002284379 | 2002-09-27 | ||

| JP2002284379 | 2002-09-27 | ||

| JP2003335812A JP4931329B2 (ja) | 2002-09-27 | 2003-09-26 | コンデンサ、配線基板、デカップリング回路及び高周波回路 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006076660A Division JP2006222441A (ja) | 2002-09-27 | 2006-03-20 | コンデンサ、配線基板、デカップリング回路及び高周波回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004140351A JP2004140351A (ja) | 2004-05-13 |

| JP2004140351A5 JP2004140351A5 (ja) | 2006-05-11 |

| JP4931329B2 true JP4931329B2 (ja) | 2012-05-16 |

Family

ID=32473225

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003335812A Expired - Fee Related JP4931329B2 (ja) | 2002-09-27 | 2003-09-26 | コンデンサ、配線基板、デカップリング回路及び高周波回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4931329B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5404312B2 (ja) * | 2009-07-29 | 2014-01-29 | 京セラ株式会社 | 電子装置 |

| CN106796844B (zh) * | 2014-10-30 | 2018-09-21 | 日立汽车系统株式会社 | 叠层电容器及车载控制装置 |

-

2003

- 2003-09-26 JP JP2003335812A patent/JP4931329B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004140351A (ja) | 2004-05-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8410887B2 (en) | Built-in-coil substrate | |

| JP2020057754A (ja) | 積層セラミック電子部品 | |

| KR101504015B1 (ko) | 적층 세라믹 커패시터 및 그 실장 기판 | |

| KR20150018140A (ko) | 기판 내장용 적층 세라믹 전자부품 및 적층 세라믹 전자부품 내장형 인쇄회로기판 | |

| KR20170087665A (ko) | 적층 세라믹 커패시터 및 그 실장 기판 | |

| KR102097324B1 (ko) | 적층 세라믹 커패시터 및 그 실장 기판 | |

| KR20140081360A (ko) | 적층 세라믹 커패시터, 그 제조방법 및 적층 세라믹 커패시터가 실장된 회로기판 | |

| JP2015076600A (ja) | 基板内蔵用積層セラミック電子部品及び積層セラミック電子部品内蔵型印刷回路基板 | |

| JPH04220004A (ja) | 電圧制御発振器 | |

| KR101832611B1 (ko) | 적층형 커패시터 및 그 실장 기판 | |

| KR101489815B1 (ko) | 적층 세라믹 커패시터 | |

| JP2006222441A (ja) | コンデンサ、配線基板、デカップリング回路及び高周波回路 | |

| JP2004296936A (ja) | セラミック電子部品 | |

| JP2016086150A (ja) | 積層セラミックキャパシタ | |

| JP4458812B2 (ja) | コンデンサ、コンデンサの製造方法、配線基板、デカップリング回路及び高周波回路 | |

| KR20150018137A (ko) | 기판 내장용 적층 세라믹 전자부품 및 적층 세라믹 전자부품 내장형 인쇄회로기판 | |

| JP2021097202A (ja) | 積層型キャパシタ及びその実装基板 | |

| KR102037268B1 (ko) | 적층 세라믹 커패시터 및 그 실장 기판 | |

| JP2017120876A (ja) | 積層電子部品及びその製造方法 | |

| JP4931329B2 (ja) | コンデンサ、配線基板、デカップリング回路及び高周波回路 | |

| KR102449360B1 (ko) | 적층 세라믹 커패시터 및 그 실장 기판 | |

| JP2004140350A (ja) | コンデンサ、配線基板、デカップリング回路及び高周波回路 | |

| JP2005203623A (ja) | コンデンサ、コンデンサの製造方法、配線基板、デカップリング回路及び高周波回路 | |

| JPH0817675A (ja) | チップ型積層セラミックコンデンサ | |

| JP2006222442A (ja) | コンデンサ、及び配線基板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060320 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060912 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090120 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090319 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20091201 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111217 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120214 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150224 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |