JP4896286B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4896286B2 JP4896286B2 JP2000002019A JP2000002019A JP4896286B2 JP 4896286 B2 JP4896286 B2 JP 4896286B2 JP 2000002019 A JP2000002019 A JP 2000002019A JP 2000002019 A JP2000002019 A JP 2000002019A JP 4896286 B2 JP4896286 B2 JP 4896286B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- semiconductor film

- substrate

- amorphous semiconductor

- amorphous

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Liquid Crystal (AREA)

- Recrystallisation Techniques (AREA)

- Formation Of Insulating Films (AREA)

- Thin Film Transistor (AREA)

Description

【発明の属する技術分野】

本願発明は絶縁表面を有する基板上に薄膜トランジスタ(以下、TFTという)で構成された回路を有する半導体装置およびその作製方法に関する。とくに本発明は、画素回路とその周辺に設けられる制御回路を同一基板上に設けた液晶表示装置に代表される電気光学装置、および電気光学装置を搭載した電子機器に関する。

【0002】

【従来の技術】

薄膜トランジスタ(以下、TFTと記す)は、基板上に形成した半導体膜を用いて作製することができる。TFTは能動素子として各種集積回路を形成することが可能である。特にアクティブマトリクス型の液晶表示装置の画素部に設けるスイッチング素子や、或いは画素部の周辺に設けられる駆動回路を形成する素子として利用することができる。

【0003】

半導体膜として非晶質シリコン膜を用いたTFTはプロセス温度が低く生産が容易であるが、電気的特性が低いという欠点がある。そのために各画素に設けるスイッチング素子としては利用できるが、駆動回路まで形成することは出来なかった。しかし、結晶構造を有する半導体膜(以下、結晶質半導体膜と記す)でTFTを形成すると電気的特性を高めることができることが知られている。結晶質半導体膜の代表例として結晶構造を有するシリコン膜は多結晶シリコン膜、ポリシリコン膜、微結晶シリコン膜などとしても知られているが、TFTの技術分野では非晶質シリコン膜を光や熱エネルギーによって結晶化させた結晶質シリコン膜が多くの場合用いられている。

【0004】

しかし、熱エネルギーを用いる熱結晶法は600℃以上の温度で熱処理する必要があり、処理時間も10時間程度を要するものである。従って、生産性を低下させてしまう問題がある。一方、光エネルギーを用いる結晶化技術はエキシマレーザー光やYAGレーザー光を用いたレーザー結晶化法が知られているが、熱結晶化法で作製したTFTと比較して電気的特性が劣るという問題がある。

【0005】

また、結晶質半導体膜を、触媒元素を用いた熱結晶化法により形成する技術が知られている。例えば、特開平7−130652号公報、特開平8−78329号公報などで開示された技術を用いることができる。触媒元素を用いた熱結晶化法によれば非晶質シリコン膜にニッケルなどの触媒元素を導入し、550℃、4時間の熱処理により結晶質シリコン膜を形成することができる。

【0006】

【発明が解決しようとする課題】

ガラスなどの基板上に酸化シリコン、窒化シリコン、酸化窒化シリコンなどから成る下地膜を形成し、その上に堆積した非晶質半導体膜を熱結晶化法やレーザー結晶化法で結晶化して得られる結晶質半導体膜は、下地膜と半導体膜との界面エネルギーの大小関係の兼ね合いで<111>に優先的に配向し、その他の方向にもランダムな方位を持った結晶粒が多数存在してしまうことが電子線回折の解析から知られている。一方、ニッケルなどの触媒元素を用いた熱結晶化法で作製される結晶質半導体膜は、その結晶粒の大部分は<110>に配向している。しかしながら前述のように下地膜と半導体膜との界面エネルギーとの兼ね合いで<111>などのその他の配向が若干混在してしまう。

【0007】

複数の結晶粒から成る結晶質半導体膜において配向性が低いと結晶粒界で不対結合手が多く形成され、結晶質半導体膜中のキャリア(電子・ホール)の輸送特性を低下させる。即ち、キャリアが散乱されたりトラップされたりするため、このような結晶質半導体膜でTFTを作製しても高い電界効果移動度を有するTFTを作製することができない。また、結晶粒界はランダムに存在するため、個々のTFTの電気的特性のバラツキの要因ともなる。

【0008】

本発明はこのような問題点を解決する手段を提供することを目的とし、非晶質半導体膜を熱結晶化法やレーザー結晶化法を用いて作製される結晶質半導体膜の配向性を高めることを目的とする。さらに、そのような結晶質半導体膜を用いることでTFTの特性を向上させ、特性バラツキを低減させることを目的とする。

【0009】

【課題を解決するための手段】

本発明は、基板の表面をハロゲン元素を含むプラズマ雰囲気に晒す第1の工程と、前記基板上に非晶質半導体膜を形成する第2の工程と、前記非晶質半導体膜上に該非晶質半導体膜の結晶化を助長する触媒元素が含有する層を形成する第3の工程と、前記非晶質半導体膜を第1の加熱処理により結晶質半導体膜を形成する第4の工程と、前記結晶質半導体膜を選択的に除去して島状の結晶質半導体膜を形成する第5の工程と、前記島状の結晶質半導体膜上にゲート絶縁膜を形成する第6の工程と、前記第6の工程の後にハロゲンを含む酸化雰囲気中で第2の加熱処理を行う第7の工程とを有することを特徴とする。

【0010】

また、基板の表面をハロゲン元素を含むプラズマ雰囲気に晒す第1の工程と、前記基板上に非晶質半導体膜を形成する第2の工程と、前記非晶質半導体膜上に選択的に第1の絶縁膜を形成する第3の工程と、前記非晶質半導体膜上に該非晶質半導体膜の結晶化を助長する触媒元素を含有する層を形成する第4の工程と、前記非晶質半導体膜を第1の加熱処理により結晶質半導体膜を形成する第5の工程と、前記第1の絶縁膜を除去する第6の工程と、前記結晶質半導体膜を選択的に除去して島状の結晶質半導体膜を形成する第7の工程と、前記島状の結晶質半導体膜上にゲート絶縁膜を形成する第8の工程と、前記第8の工程の後にハロゲンを含む酸化雰囲気中で第2の加熱処理を行う第9の工程とを有することを特徴とする。

【0011】

【発明の実施の形態】

[実施形態1]

図11(A)で示すように、石英基板1101上もしくはその表面に形成された下地膜に、ハロゲン原子を含む(本実施形態ではフッ素)プラズマ1103を晒し基板の表面をフッ素化する。具体的には、フッ素またはフッ素ラジカルの雰囲気中に表面を晒し、表面をフッ素でコーティングする。ハロゲン元素としてはその他に塩素や臭素などを用いることも可能である。

【0012】

例えば、四フッ化珪素(SiF4)または三フッ化窒素(NF3)を導入しプラズマ化してフッ素原子またはフッ素ラジカルを生成させる。その手段として、例えばプラズマCVD装置を適用することができる。プラズマCVD装置には、容量結合型または誘導結合型のものをはじめ、ECR(電子サイクロトン共鳴)プラズマCVD装置やマイクロ波CVD装置などいずれの形式の装置を適用しても良い。特に、ECRプラズマやマイクロ波プラズマはガスの分解効率が高いので、フッ素ラジカルを効率良く生成することができる。

【0013】

フッ素化を行った基板表面1102に、20〜100nm(好ましくは40〜80nm)の厚さの非晶質構造を含む半導体膜1104を減圧熱CVD法、プラズマCVD法またはスパッタ法で形成する(図11(B))。非晶質構造を含む半導体膜としては、非晶質半導体膜、微結晶半導体膜があり、さらに非晶質シリコンゲルマニウム膜などの非晶質構造を含む化合物半導体膜も含まれる。例えば、プラズマCVD法でSiH4またはSiH4とH2から作製される非晶質シリコン膜を55nmの厚さで形成する。或いは、減圧CVD法でSi2H6から非晶質シリコン膜を55nmの厚さで形成しても良い。さらに、基板上に下地膜と非晶質シリコン膜とを大気解放しないで連続的に形成することも有効である。

【0014】

そして図11(C)で示すように、重量換算で10ppmの触媒元素を含む水溶液をスピナーで基板を回転させて塗布するスピンコート法で触媒元素を含有する層1105を形成する。触媒元素にはニッケル(Ni)、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)などである。この触媒元素を含有する層1104は、スピンコート法の他に印刷法やスプレー法、バーコーター法、或いはスパッタ法や真空蒸着法によって上記触媒元素の層を1〜5nmの厚さに形成しても良い。

【0015】

図11(D)で示す結晶化の工程では、まず400〜500℃で1時間程度の熱処理を行い、非晶質シリコン膜の含有水素量を5atom%以下にする。非晶質シリコン膜の含有水素量が成膜後において最初からこの値である場合にはこの熱処理は必ずしも必要でない。そして、ファーネスアニール炉を用い、窒素雰囲気中で550〜600℃で1〜8時間の熱結晶化を行う。好適には、550℃で4時間の熱処理を行う。こうして結晶質シリコン膜から成る結晶質半導体膜1106を得ることができる。

【0016】

このようにして作製された結晶質半導体膜1106の所定の領域をエッチングして島状半導体膜1107を形成する。そして、その上にゲート絶縁膜1108をシリコンを成分とする絶縁膜で20〜200nmの厚さに形成する。例えば、プラズマCVD法でSiH4とN2Oとの混合ガスから酸化窒化シリコン膜を70nmの厚さに形成する。

【0017】

そして、ハロゲン(代表的には塩素)を含む酸化雰囲気中で700〜1100℃の熱処理を0.1〜8時間行う。この熱処理により、ゲート絶縁膜1108と島状半導体膜1107との界面で新な酸化膜が形成され、ゲート絶縁膜1108の厚さは120nmとなる。また、ハロゲン雰囲気での酸化の過程でゲート絶縁膜1108や島状半導体膜1107に含まれる金属不純物元素などはハロゲンと化合物を形成し、気相中に除去することができる。さらにゲート絶縁膜1108は絶縁耐圧が高く、また島状半導体膜との界面準位密度を低減させることができる(図11(E))。

【0018】

[実施形態2]

実施形態1に従って作製された島状半導体膜とゲート絶縁膜を用いてTFTを作製した一例を示す。図12は基板301上に形成されたnチャネル型及びpチャネル型TFTの断面構造を示している。nチャネル型TFT及びpチャネル型TFTのゲート電極は、ゲート絶縁膜310に接して設けられた第1の導電層311、313と、前記第1の導電層に接して設けられた312、314とから成っている。

【0019】

第1の導電層311、313は、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、タングステン(W)など元素か、これらの元素を成分とする材料で形成する。また、第2の導電層312、314は抵抗率の低いアルミニウム(Al)や銅(Cu)を用いれば良い。用途によっては、第1の導電層のみで形成しても良いし、第2の導電層の上にさらに他の導電層を積層しても良い。

【0020】

pチャネル型TFTの半導体層は、ソース領域303と、ドレイン領域304とから成っている。

【0021】

チャネル形成領域302には、あらかじめボロンを添加しても良い。このボロンはしきい値電圧を制御するために添加するものであり、同様の効果が得られるものであれば他の元素で代用することもできる。

【0022】

こうしてnチャネル型TFTおよびpチャネル型TFTが完成したら、第1の層間絶縁膜315、第2層間絶縁膜316で覆い、ソース領域303、309、ドレイン領域304、308と接触するソース配線317、319とドレイン配線318とを設ける。図12の構造では、これらを設けた後でパッシベーション膜320として窒化シリコン膜を設けている。さらに樹脂材料でなる第3の層間絶縁膜321を設ける。第3の層間絶縁膜は、樹脂材料に限定される必要はないが、例えば、液晶表示装置に応用する場合には、表面の平坦性を確保するために樹脂材料を用いることが好ましい。

【0023】

[実施形態3]

実施形態1と同様に石英基板1201上もしくは基板表面に形成された下地膜表面をフッ素を含むプラズマ1202によって処理(図13(A))した後、その処理した表面1203上に非晶質半導体膜1204を30〜100nm、好ましくは50〜60nmの厚さで形成する。例えば、プラズマCVD法でSiH4またはSiH4とH2から作製される非晶質シリコン膜を55nmの厚さで形成する(図13(B))。或いは、減圧CVD法でSi2H6から非晶質シリコン膜を55nmの厚さで形成しても良い。非晶質半導体膜1204上に珪素(シリコン)を含む絶縁膜でなるマスク膜1205を150nmの厚さで形成し、パターニングによって開口部1206を形成する(図13(C))。

【0024】

非晶質構造を含む半導体膜の表面に触媒元素を保持させた層を形成し、加熱処理を行う。本実施形態では、触媒元素としてニッケルを用い、570℃で14時間の熱処理を行う。その結果、開口部1206を起点として概略基板と平行な方向(矢印で示した方向)に結晶化が進行し、巨視的な結晶成長方向が揃った結晶構造を含む半導体膜(本実施例では結晶質シリコン膜)が形成される。(図13(D))

【0025】

次に、結晶化の工程で用いたニッケルを結晶質シリコン膜から除去するゲッタリング工程を行う。先ほど形成したマスク膜1205をそのままマスクとして用い、15族に属する元素(本実施例ではリン)を添加する工程を行い、開口部1206で露出した結晶質シリコン膜に1×1019〜1×1020atoms/cm3の濃度でリンを含むリン添加領域(以下、ゲッタリング領域という)1207を形成する。

【0026】

次に、窒素雰囲気中で450〜650℃(好ましくは500〜550℃)、4〜24時間(好ましくは6〜12時間)の熱処理工程を行う。この熱処理工程により結晶質シリコン膜中のニッケルは矢印の方向に移動し、リンのゲッタリング作用によってゲッタリング領域107に捕獲される。即ち、結晶質シリコン膜中からニッケルが除去されるため、ゲッタリング後の結晶質シリコン膜に含まれるニッケル濃度は、1×1017atms/cm3以下、好ましくは1×1016atms/cm3にまで低減することができる(図13(E))。

【0027】

その後、マスク1205を除去し、得られた結晶質半導体膜から実施例1と同様にして島状半導体膜1208を形成する。さらに、ゲート絶縁膜を形成し、ハロゲンを含む酸化雰囲気中で熱処理することにより実施形態1と同様に絶縁耐圧が高いゲート絶縁膜を形成することができ、また島状半導体膜との界面準位密度を低減させることができる。そして、実施形態2に示すTFTを形成することができる。

【0028】

[実施形態4]

実施形態1と3では非晶質構造を有する半導体膜をプラズマCVD法または減圧CVD法でSiH4やSi2H6から作製する方法について示した。本実施形態では他のガスを用いて作製する場合について示す。

【0029】

本実施形態の作製方法の特徴は、非晶質構造を有する半導体膜はハロゲン元素と水素を含む反応ガスで形成することにある。具体的には、非晶質構造を有する半導体膜として例えば非晶質シリコン膜を作製する時にハロゲン元素と水素とを混合させる。ハロゲン元素としては特にフッ素を用いると良く、フッ素はシリコンに対しエッチングする作用があり、膜の堆積過程において結合の弱い部分を優先的にエッチングすることができる。また、水素を供給することにより膜中に残存してしまうフッ素濃度を低減させることができる。そして、フッ素と水素の作用を利用してボイドや空孔の少ない緻密な非晶質シリコン膜を作製することができる。このような効果は非晶質シリコン膜の他に非晶質シリコン・ゲルマニウム(a−SiGe)膜、非晶質炭化シリコン(a−SiC)膜,非晶質シリコン・スズ(a−SiSn)膜などにも適用することができる。

【0030】

フッ素と水素の供給方法は、非晶質半導体膜として非晶質シリコン膜を作製する場合には、反応ガスとして四フッ化珪素(SiF4)と水素(H2)、またはSiF4とSiH4、またはSiF4とSiH4とH2の組み合わせを選択することができる。SiF4の代わりにトリフロロシラン(SiHF3)、ジフロロシラン(SiH2F2)、モノフロロシラン(SiH3F)を適用することもできる。また、SiH4とF2を直接反応させても良い。さらに、非晶質シリコン・ゲルマニウム膜を作製する場合にはゲルマン(GeH4)や四フッ化ゲルマニウム(GeF4)を、非晶質炭化シリコンを作製する場合にはメタン(CH4)や四フッ化メタン(CF4)などを、非晶質シリコン・スズ膜を形成する場合には水素化スズ(SnH4)を適宣添加すれば良い。

【0031】

非晶質構造を有する半導体膜の厚さは25〜100nmの厚さで形成する。膜の堆積初期の段階ではフッ素の効果により下地の表面をフッ素化することができる。

【0032】

このようにフッ素と水素とを含む反応ガスで作製された非晶質構造を有する半導体膜1103には、成膜時の基板温度にも依存するが、膜中に水素が0.1〜20atomic%、フッ素が0.1〜10atomic%含有するように形成する。膜中に残存するフッ素や水素はその後の熱結晶化の工程で膜中から放出されて膜中に残存する濃度はさらに低下するが、緻密化した非晶質半導体膜と、最表面をフッ素で終端した下地膜との相互作用により<110>の配向性をより高めることができる。

【0033】

[実施形態5]

下地の表面または下地と非晶質半導体膜との界面をフッ素化する方法として、図11や図13で示すように石英基板上にそのまま非晶質半導体膜を形成した後で非晶質半導体膜の表面からフッ素を注入しても良い。その手法としてイオンドープ法やイオン注入法を用いる。

【0034】

イオンドープ法ではイオン原としてSiF4やヘリウム(He)希釈のF2を用いイオン化して非晶質半導体膜の表面から注入する。加速電圧は高めに設定して、非晶質半導体膜1103と下地膜1102との界面またはその近傍に注入されたフッ素の濃度分布のピークが存在するようにする。その場合、ピーク濃度は1×1019〜1×1021atoms/cm3となるようにする。イオンドープ法では質量分離されないのでフッ素以外の元素も同時に注入されてしまうが、液晶表示装置などの大面積基板を処理するのに適している。また、イオン注入法でも同様な濃度でフッ素を非晶質半導体膜と下地との界面またはその近傍に注入することができる。また、フッ素イオンを非晶質半導体膜の表面から注入することで、非晶質半導体膜中に存在し得る微結晶核を破壊する作用が同時に得られ、熱結晶化における核生成密度を低減させることができる。

【0035】

このようにフッ素を注入した状態で実施形態1と同様にして非晶質半導体膜1103に接して触媒元素を含有する層を設けて結晶化させると同様の効果を得ることができる。

【0036】

[実施形態6]

本実施例で示すようにして作製された結晶質半導体膜は、石英基板とその上に形成したシリコンとの界面エネルギーが低いため、石英基板上に形成した非晶質シリコン膜を熱結晶化法で結晶化させると<111>に優先的に配向し、その他にランダムな方位を持った結晶粒が多数存在することが電子線回折の解析から知られている。一方、ニッケルなどの触媒元素を用いた熱結晶化法で作製される結晶質シリコン膜は、微視的に見れば複数の針状または棒状の結晶が集合した構造を有している。しかし、隣接する結晶粒の連続性が高く不対結合手(ダングリングボンド)が殆ど形成されないことが見込まれている。また、その結晶粒の大部分は<110>に配向している。その理由の一つとして、ニッケルなどの触媒元素を用いた場合の結晶成長過程は、触媒元素のシリサイド化物が関与しているものと考えられ、半導体膜の膜厚が25〜100nmと薄いのでその初期核のうち(111)面が基板表面とほぼ垂直なものが優先的に成長するため実質的に<110>の配向性が高くなると考えられる。しかしながら前述のように石英基板とシリコンとの界面エネルギーが低いので<111>晶帯に含まれる他の面方位をとることも可能となる。従って、その他の配向が若干混在してしまう。

【0037】

しかし、触媒元素を用いた熱結晶化法において、石英基板の表面をフッ素化しておくことにより、石英基板との界面の影響を低減させることができ、実質的にその影響を無視することができる。その結果、結晶の配向性は表面エネルギーのみに影響されることになるが、触媒元素を用いた結晶成長では<110>の配向性が高まる。このような効果は通常の熱結晶化法やレーザー結晶化法などでも実現することができるが、触媒元素を用いた熱結晶化法においてより顕著に得ることができる。このようにして作製された結晶質半導体膜は、実施形態2で示したようにTFTを作製するための半導体膜として好適に用いることができる。

【0038】

【実施例】

[実施例1]

本発明の実施例について図1〜図4を用いて説明する。ここでは、同一基板上に画素回路とその画素回路を制御するための制御回路とを同時に作製する方法について説明する。但し、説明を簡単にするために、制御回路では、シフトレジスタ回路、バッファ回路等の基本回路であるCMOS回路と、サンプリング回路を形成するnチャネル型TFTとを図示することとする。

【0039】

基板には、石英基板やシリコン基板を使用することが望ましい。本実施例では石英基板を用いた。その他にも金属基板またはステンレス基板の表面に絶縁膜を形成したものを基板としても良い。本実施例の場合、800℃以上の温度に耐えうる耐熱性を要求されるので、それを満たす基板であればどのような基板を用いても構わない。

【0040】

そして、基板のTFTが形成される表面をプラズマで処理し、その処理された基板表面に、20〜100nm(好ましくは40〜80nm)の厚さの非晶質構造を含む半導体膜を減圧熱CVD法、プラズマCVD法またはスパッタ法で形成する。なお、本実施例では60nm厚の非晶質シリコン膜を形成するが、後に熱酸化工程があるのでこの膜厚が最終的なTFTの活性層の膜厚になるわけではない)

【0041】

また、非晶質構造を含む半導体膜としては、非晶質半導体膜、微結晶半導体膜があり、さらに非晶質シリコンゲルマニウム膜などの非晶質構造を含む化合物半導体膜も含まれる。さらに、基板上に下地膜と非晶質シリコン膜とを大気解放しないで連続的に形成することも有効である。そうすることにより基板表面の汚染が非晶質シリコン膜に影響を与えないようにすることが可能となり、作製されるTFTの特性バラツキを低減させることができる。

【0042】

次に、非晶質シリコン膜上に珪素(シリコン)を含む絶縁膜でなるマスク膜を形成し、パターニングによって開口部を形成する。この開口部は、次の結晶化工程の際に結晶化を助長する触媒元素を添加するための添加領域となる。

【0043】

なお、珪素を含む絶縁膜としては、酸化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜を用いることができる。窒化酸化シリコン膜は、珪素、窒素及び酸素を所定の量で含む絶縁膜であり、SiOxNyで表される絶縁膜である。窒化酸化シリコン膜はSiH4、N2O及びNH3を原料ガスとして作製することが可能であり、含有する窒素濃度が25atomic%以上50atomic%未満とすると良い。

【0044】

また、このマスク膜のパターニングを行うと同時に、後のパターニング工程の基準となるマーカーパターンを形成しておく。マスク膜をエッチングする際に非晶質シリコン膜も僅かにエッチングされるが、この段差が後にマスク合わせの時にマーカーパターンとして用いることができるのである。

【0045】

次に、特開平10−247735号公報(米国出願番号09/034,041に対応)に記載された技術に従って、結晶構造を含む半導体膜を形成する。同公報記載の技術は、非晶質構造を含む半導体膜の結晶化に際して、結晶化を助長する触媒元素(ニッケル、コバルト、ゲルマニウム、錫、鉛、パラジウム、鉄、銅から選ばれた一種または複数種の元素)を用いる結晶化手段である。

【0046】

具体的には、非晶質構造を含む半導体膜の表面に触媒元素を保持させた状態で加熱処理を行い、非晶質構造を含む半導体膜を、結晶構造を含む半導体膜に変化させるものである。なお、結晶化手段としては、特開平7−130652号公報の実施例1に記載された技術を用いても良い。また、結晶質構造を含む半導体膜には、いわゆる単結晶半導体膜も多結晶半導体膜も含まれるが、同公報で形成される結晶構造を含む半導体膜は結晶粒界を有している。

【0047】

なお、同公報では触媒元素を含む層をマスク膜上に形成する際にスピンコート法を用いているが、触媒元素を含む薄膜をスパッタ法や蒸着法といった気相法を用いて成膜する手段をとっても良い。

【0048】

また、非晶質シリコン膜は含有水素量にもよるが、好ましくは400〜550℃で1時間程度の加熱処理を行い、水素を十分に脱離させてから結晶化させることが望ましい。その場合、含有水素量を5atom%以下とすることが好ましい。

【0049】

結晶化工程は、まず400〜500℃で1時間程度の熱処理工程を行い、水素を膜中から脱離させた後、500〜650℃(好ましくは550〜600℃)で6〜16時間(好ましくは8〜14時間)の熱処理を行う。

【0050】

本実施例では、触媒元素としてニッケルを用い、570℃で14時間の熱処理を行う。その結果、開口部を起点として概略基板と平行な方向(矢印で示した方向)に結晶化が進行し、巨視的な結晶成長方向が揃った結晶構造を含む半導体膜(本実施例では結晶質シリコン膜)が形成される。

【0051】

次に、結晶化の工程で用いたニッケルを結晶質シリコン膜から除去するゲッタリング工程を行う。本実施例では、先ほど形成したマスク膜をそのままマスクとして15族に属する元素(本実施例ではリン)を添加する工程を行い、開口部で露出した結晶質シリコン膜に1×1019〜1×1020atoms/cm3の濃度でリンを含むリン添加領域(以下、ゲッタリング領域という)を形成する。

【0052】

次に、窒素雰囲気中で450〜650℃(好ましくは500〜550℃)、4〜24時間(好ましくは6〜12時間)の熱処理工程を行う。この熱処理工程により結晶質シリコン膜中のニッケルは矢印の方向に移動し、リンのゲッタリング作用によってゲッタリング領域に捕獲される。即ち、結晶質シリコン膜中からニッケルが除去されるため、ゲッタリング後の結晶質シリコン膜に含まれるニッケル濃度は、1×1017atms/cm3以下、好ましくは1×1016atms/cm3にまで低減することができる。

【0053】

次に、マスク膜を除去し、結晶質シリコン膜上に後の不純物添加時のために保護膜を形成する。保護膜は100〜200nm(好ましくは130〜170nm)の厚さの窒化酸化シリコン膜または酸化シリコン膜を用いると良い。この保護膜は不純物添加時に結晶質シリコン膜が直接プラズマに曝されないようにするためと、微妙な濃度制御を可能にするための意味がある。

【0054】

そして、その上にレジストマスクを形成し、保護膜を介してp型を付与する不純物元素(以下、p型不純物元素という)を添加する。p型不純物元素としては、代表的には13族に属する元素、典型的にはボロンまたはガリウムを用いることができる。この工程(チャネルドープ工程という)はTFTのしきい値電圧を制御するための工程である。なお、ここではジボラン(B2H6)を質量分離しないでプラズマ励起したイオンドープ法でボロンを添加する。勿論、質量分離を行うイオンインプランテーション法を用いても良い。

【0055】

この工程により1×1015〜1×1018atoms/cm3(代表的には5×1016〜5×1017atoms/cm3)の濃度でp型不純物元素(本実施例ではボロン)を含む不純物領域を形成する。なお、本明細書中では上記濃度範囲でp型不純物元素を含む不純物領域(但し、リンは含まれていない領域)をp型不純物領域(b)と定義する。

【0056】

次に、レジストマスクを除去し、結晶質シリコン膜をパターニングして島状の半導体層(以下、活性層という)を形成する。なお、活性層は、ニッケルを選択的に添加して結晶化することによって、非常に結晶性の良い結晶質シリコン膜で形成されている。具体的には、棒状または柱状の結晶が、特定の方向性を持って並んだ結晶構造を有している。また、結晶化後、ニッケルをリンのゲッタリング作用により除去又は低減しており、活性層中に残存する触媒元素の濃度は、1×1017atms/cm3以下、好ましくは1×1016atms/cm3である。

【0057】

また、pチャネル型TFTの活性層は意図的に添加された不純物元素を含まない領域であり、nチャネル型TFTの活性層はp型不純物領域(b)となっている。本明細書中では、この状態の活性層は全て真性または実質的に真性であると定義する。即ち、TFTの動作に支障をきたさない程度に不純物元素が意図的に添加されている領域が実質的に真性な領域と考えて良い。

【0058】

次に、プラズマCVD法またはスパッタ法により10〜100nm厚の珪素を含む絶縁膜を形成する。本実施例では、30nm厚の窒化酸化シリコン膜を形成する。この珪素を含む絶縁膜は、他の珪素を含む絶縁膜を単層または積層で用いても構わない。

【0059】

次に、800〜1150℃(好ましくは900〜1000℃)の温度で15分〜8時間(好ましくは30分〜2時間)の熱処理工程を、酸化性雰囲気下で行う(熱酸化工程)。本実施例では酸素雰囲気中に3体積%の塩化水素を添加した雰囲気中で950℃80分の熱処理工程を行う。なお、前の工程で添加されたボロンはこの熱酸化工程の間に活性化される。

【0060】

なお、酸化性雰囲気としては、ドライ酸素雰囲気でもウェット酸素雰囲気でも良いが、半導体層中の結晶欠陥の低減にはドライ酸素雰囲気が適している。また、本実施例では酸素雰囲気中にハロゲン元素を含ませた雰囲気としたが、100%酸素雰囲気で行っても構わない。

【0061】

この熱酸化工程の間、珪素を含む絶縁膜とその下の活性層との界面においても酸化反応が進行する。本願発明ではそれを考慮して最終的に形成されるゲート絶縁膜の膜厚が50〜200nm(好ましくは100〜150nm)となるように調節する。本実施例の熱酸化工程では、60nm厚の活性層のうち25nmが酸化されて活性層の膜厚は45nmとなる。また、30nm厚の珪素を含む絶縁膜に対して50nm厚の熱酸化膜が加わるので、最終的なゲート絶縁膜の膜厚は110nmとなる。

【0062】

次に、新たにレジストマスクを形成する。そして、n型を付与する不純物元素(以下、n型不純物元素という)を添加してn型を呈する不純物領域を形成する。なお、n型不純物元素としては、代表的には15族に属する元素、典型的にはリンまたは砒素を用いることができる。

【0063】

この不純物領域は、後にCMOS回路およびサンプリング回路のnチャネル型TFTにおいて、LDD領域として機能させるための不純物領域である。なお、ここで形成された不純物領域にはn型不純物元素が2×1016〜5×1019atoms/cm3(代表的には5×1017〜5×1018atoms/cm3)の濃度で含まれている。本明細書中では上記濃度範囲でn型不純物元素を含む不純物領域をn型不純物領域(b)と定義する。

【0064】

なお、ここではフォスフィン(PH3)を質量分離しないでプラズマ励起したイオンドープ法でリンを1×1018atoms/cm3の濃度で添加する。勿論、質量分離を行うイオンインプランテーション法を用いても良い。この工程では、ゲート膜を介して結晶質シリコン膜にリンを添加する。

【0065】

次に、600〜1000℃(好ましくは700〜800℃)の不活性雰囲気中で熱処理を行い、前の工程で添加されたリンを活性化する。本実施例では800℃1時間の熱処理を窒素雰囲気中で行う。

【0066】

この時、同時にリンの添加時に損傷した活性層及び活性層とゲート絶縁膜との界面を修復することが可能である。この活性化工程は電熱炉を用いたファーネスアニールが好ましいが、ランプアニールやレーザーアニールといった光アニールを併用しても良い。

【0067】

この工程によりn型不純物領域(b)の境界部、即ち、n型不純物領域(b)の周囲に存在する真性又は実質的に真性な領域(勿論、p型不純物領域(b)も含む)との接合部が明確になる。このことは、後にTFTが完成した時点において、LDD領域とチャネル形成領域とが非常に良好な接合部を形成しうることを意味する。

【0068】

次に、ゲート配線となる導電膜を形成する。なお、ゲート配線は単層の導電膜で形成しても良いが、必要に応じて二層、三層といった積層膜とすることが好ましい。本実施例では、第1導電膜と第2導電膜とでなる積層膜を形成する。

【0069】

ここで第1導電膜、第2導電膜としては、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、クロム(Cr)、シリコン(Si)から選ばれた元素、または前記元素を主成分とする導電膜(代表的には窒化タンタル膜、窒化タングステン膜、窒化チタン膜)、または前記元素を組み合わせた合金膜(代表的にはMo−W合金膜、Mo−Ta合金膜、タングステンシリサイド膜等)を用いることができる。

【0070】

なお、第1導電膜は10〜50nm(好ましくは20〜30nm)とし、第2導電膜は200〜400nm(好ましくは250〜350nm)とすれば良い。本実施例では、第1導電膜として、50nm厚の窒化タングステン(WN)膜を、第2導電膜として、350nm厚のタングステン膜を用いる。なお、図示しないが、第1導電膜の下にシリコン膜を2〜20nm程度の厚さで形成しておくことは有効である。これによりその上に形成される導電膜の密着性の向上と、酸化防止を図ることができる。

【0071】

また、第1導電膜として窒化タンタル膜、第2導電膜としてタンタル膜を用いることも有効である。

【0072】

次に、第1導電膜と第2導電膜とを一括でエッチングして400nm厚のゲート配線を形成する。この時、制御回路に形成されるゲート配線はn型不純物領域(b)の一部とゲート絶縁膜を介して重なるように形成する。この重なった部分が後にLov領域となる。なお、ゲート配線は断面では二つに見えるが実際は連続的に繋がった一つのパターンから形成されている。

【0073】

次に、レジストマスク129を形成し、p型不純物元素(本実施例ではボロン)を添加して高濃度にボロンを含む不純物領域130、131を形成する。本実施例ではジボラン(B2H6)を用いたイオンドープ法(勿論、イオンインプランテーション法でも良い)により3×1020〜3×1021atoms/cm3(代表的には5×1020〜1×1021atoms/cm3)濃度でボロンを添加する。なお、本明細書中では上記濃度範囲でp型不純物元素を含む不純物領域をp型不純物領域(a)と定義する。(図1(A))

【0074】

次に、レジストマスク129を除去し、ゲート配線及びpチャネル型TFTとなる領域を覆う形でレジストマスク132〜134を形成する。そして、n型不純物元素(本実施例ではリン)を添加して高濃度にリンを含む不純物領域135〜141を形成する。ここでも、フォスフィン(PH3)を用いたイオンドープ法(勿論、イオンインプランテーション法でも良い)で行い、この領域のリンの濃度は1×1020〜1×1021atoms/cm3(代表的には2×1020〜5×1021atoms/cm3)とする。(図1(B))

【0075】

なお、本明細書中では上記濃度範囲でn型不純物元素を含む不純物領域をn型不純物領域(a)と定義する。また、不純物領域135〜141が形成された領域には既に前工程で添加されたリンまたはボロンが含まれるが、十分に高い濃度でリンが添加されることになるので、前工程で添加されたリンまたはボロンの影響は考えなくて良い。従って、本明細書中では不純物領域135〜141はn型不純物領域(a)と言い換えても構わない。

【0076】

次に、レジストマスク132〜134を除去し、ゲート配線をマスクとして自己整合的にn型不純物元素(本実施例ではリン)を添加する。こうして形成された不純物領域142〜147には前記n型不純物領域(b)の1/2〜1/10(代表的には1/3〜1/4)の濃度(但し、前述のチャネルドープ工程で添加されたボロン濃度よりも5〜10倍高い濃度、代表的には1×1016〜5×1018atoms/cm3、典型的には3×1017〜3×1018atoms/cm3、)でリンが添加されるように調節する。なお、本明細書中では上記濃度範囲でn型不純物元素を含む不純物領域(但し、p型不純物領域(a)を除く)をn型不純物領域(c)と定義する。(図1(C))

【0077】

なお、この工程ではゲート配線で隠された部分を除いて全ての不純物領域にも1×1016〜5×1018atoms/cm3の濃度でリンが添加されているが、非常に低濃度であるため各不純物領域の機能には影響を与えない。また、n型不純物領域(b)142〜147には既にチャネルドープ工程で1×1015〜1×1018atoms/cm3の濃度のボロンが添加されているが、この工程ではp型不純物領域(b)に含まれるボロンの5〜10倍の濃度でリンが添加されるので、この場合もボロンはn型不純物領域(b)の機能には影響を与えないと考えて良い。

【0078】

次に、第1層間絶縁膜148を形成する。第1層間絶縁膜148としては、珪素を含む絶縁膜、具体的には窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜またはそれらを組み合わせた積層膜で形成すれば良い。また、膜厚は100〜400nmとすれば良い。本実施例では、プラズマCVD法でSiH4、N2O、NH3を原料ガスとし、200nm厚の窒化酸化シリコン膜(但し窒素濃度が25〜50atomic%)を用いる。

【0079】

その後、それぞれの濃度で添加されたn型またはp型不純物元素を活性化するために熱処理工程を行った。この工程はファーネスアニール法、レーザーアニール法、ランプアニール法またはそれらを併用して行うことができる。ファーネスアニール法で行う場合は、不活性雰囲気中において500〜800℃、好ましくは550〜600℃で行えば良い。本実施例では600℃、4時間の熱処理を行い、不純物元素を活性化する。(図1(D))

【0080】

本実施例ではタングステンを配線材料として用いているが、タングステン膜は非常に酸化に弱いことが知られている。即ち、保護膜で覆って酸化してもピンホールが保護膜に存在すればただちに酸化されてしまう。ところが、本実施例では酸化防止膜としては非常に有効な窒化シリコン膜を用い、且つ、窒化シリコン膜に対して窒化酸化シリコン膜を積層しているため、窒化シリコン膜のピンホールの問題を気にせずに高い温度で活性化工程を行うことが可能である。

【0081】

次に、活性化工程の後、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜4時間の熱処理を行い、活性層の水素化を行う。この工程は熱的に励起された水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。

【0082】

活性化工程を終えたら、第1層間絶縁膜148の上に500nm〜1.5μm厚の第2層間絶縁膜149を形成する。本実施例では第2層間絶縁膜149として800nm厚の酸化シリコン膜をプラズマCVD法により形成する。こうして第1層間絶縁膜(窒化酸化シリコン膜)148と第2層間絶縁膜(酸化シリコン膜)149との積層膜でなる1μm厚の層間絶縁膜を形成する。

【0083】

なお、後の工程で耐熱性が許せば、第2層間絶縁膜149として、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等の有機樹脂膜を用いることも可能である。

【0084】

その後、それぞれのTFTのソース領域またはドレイン領域に達するコンタクトホールが形成され、ソース配線150〜153と、ドレイン配線154〜156を形成する。なお、CMOS回路を形成するためにドレイン配線154はpチャネル型TFTとnチャネル型TFTとの間で共通化されている。また、図示していないが、本実施例ではこの配線を、Ti膜を200nm、Tiを含むアルミニウム膜500nm、Ti膜100nmをスパッタ法で連続して形成した3層構造の積層膜とする。(図3(A))

【0085】

次に、パッシベーション膜157として、窒化シリコン膜、酸化シリコン膜、または窒化酸化シリコン膜で50〜500nm(代表的には200〜300nm)の厚さで形成する。この時、本実施例では膜の形成に先立ってH2、NH3等水素を含むガスを用いてプラズマ処理を行い、成膜後に熱処理を行う。この前処理により励起された水素が第1、第2層間絶縁膜中に供給される。この状態で熱処理を行うことで、パッシベーション膜157の膜質を改善するとともに、第1、第2層間絶縁膜中に添加された水素が下層側に拡散するため、効果的に活性層を水素化することができる。

【0086】

また、パッシベーション膜157を形成した後に、さらに水素化工程を行っても良い。例えば、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られる。なお、水素化工程後に画素電極とドレイン配線を接続するためのコンタクトホールを形成する位置において、パッシベーション膜157に開口部(図示せず)を形成しておいても良い。

【0087】

その後、有機樹脂からなる第3層間絶縁膜158を約1μmの厚さに形成する。有機樹脂としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等を使用することができる。有機樹脂膜を用いることの利点は、成膜方法が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点などが上げられる。なお上述した以外の有機樹脂膜や有機系SiO化合物などを用いることもできる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300℃で焼成して形成する。

【0088】

次に、画素回路となる領域において、第3層間絶縁膜158上に遮蔽膜159を形成する。なお、本明細書中では光と電磁波を遮るという意味で遮蔽膜という文言を用いる。遮蔽膜159はアルミニウム(Al)、チタン(Ti)、タンタル(Ta)から選ばれた元素でなる膜またはいずれかの元素を主成分とする膜で100〜300nmの厚さに形成する。本実施例では1wt%のチタンを含有させたアルミニウム膜を125nmの厚さに形成する。

【0089】

なお、第3層間絶縁膜158上に酸化シリコン膜等の絶縁膜を5〜50nm形成しておくと、この上に形成する遮蔽膜の密着性を高めることができる。また、有機樹脂で形成した第3層間絶縁膜158の表面にCF4ガスを用いたプラズマ処理を施すと、表面改質により膜上に形成する遮蔽膜の密着性を向上させることができる。

【0090】

また、このチタンを含有させたアルミニウム膜を用いて、遮蔽膜だけでなく他の接続配線を形成することも可能である。例えば、制御回路内で回路間をつなぐ接続配線を形成できる。但し、その場合は遮蔽膜または接続配線を形成する材料を成膜する前に、予め第3層間絶縁膜にコンタクトホールを形成しておく必要がある。

【0091】

次に、遮蔽膜159の表面に陽極酸化法またはプラズマ酸化法(本実施例では陽極酸化法)により20〜100nm(好ましくは30〜50nm)の厚さの酸化物160を形成する。本実施例では遮蔽膜159としてアルミニウムを主成分とする膜を用いたため、陽極酸化物160として酸化アルミニウム膜(アルミナ膜)が形成される。

【0092】

この陽極酸化処理に際して、まず十分にアルカリイオン濃度の小さい酒石酸エチレングリコール溶液を作製する。これは15%の酒石酸アンモニウム水溶液とエチレングリコールとを2:8で混合した溶液であり、これにアンモニア水を加え、pHが7±0.5となるように調節する。そして、この溶液中に陰極となる白金電極を設け、遮蔽膜159が形成されている基板を溶液に浸し、遮蔽膜159を陽極として、一定(数mA〜数十mA)の直流電流を流す。

【0093】

溶液中の陰極と陽極との間の電圧は陽極酸化物の成長に従い時間と共に変化するが、定電流のまま100V/minの昇圧レートで電圧を上昇させて、到達電圧45Vに達したところで陽極酸化処理を終了させる。このようにして遮蔽膜159の表面には厚さ約50nmの陽極酸化物160を形成することができる。また、その結果、遮蔽膜159の膜厚は90nmとなる。なお、ここで示した陽極酸化法に係わる数値は一例にすぎず、作製する素子の大きさ等によって当然最適値は変化しうるものである。

【0094】

また、ここでは陽極酸化法を用いて遮蔽膜表面のみに絶縁膜を設ける構成としたが、絶縁膜をプラズマCVD法、熱CVD法またはスパッタ法などの気相法によって形成しても良い。その場合も膜厚は20〜100nm(好ましくは30〜50nm)とすることが好ましい。また、酸化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、DLC(Diamond like carbon)膜、酸化タンタル膜または有機樹脂膜を用いても良い。さらに、これらを組み合わせた積層膜を用いても良い。

【0095】

次に、第3層間絶縁膜158、パッシベーション膜157にドレイン配線156に達するコンタクトホールを形成し、画素電極161を形成する。なお、画素電極162は隣接する別の画素の画素電極である。画素電極161、162は、透過型液晶表示装置とする場合には透明導電膜を用い、反射型の液晶表示装置とする場合には金属膜を用いれば良い。ここでは透過型の液晶表示装置とするために、酸化インジウム・スズ(ITO)膜を110nmの厚さにスパッタ法で形成する。

【0096】

また、この時、画素電極161と遮蔽膜159とが陽極酸化物160を介して重なり、保持容量(キャパシタンス・ストレージ)163を形成する。なお、この場合、遮蔽膜159をフローティング状態(電気的に孤立した状態)か固定電位、好ましくはコモン電位(データとして送られる画像信号の中間電位)に設定しておくことが望ましい。

【0097】

こうして同一基板上に、制御回路と画素回路とを有したアクティブマトリクス基板が完成した。なお、図3(B)においては、制御回路にはpチャネル型TFT1301、nチャネル型TFT1302、1303が形成され、画素回路にはnチャネル型TFTでなる画素TFT1304が形成される。

【0098】

制御回路のpチャネル型TFT1301には、チャネル形成領域201、ソース領域202、ドレイン領域203がそれぞれp型不純物領域(a)で形成される。但し、厳密にはソース202領域及びドレイン領域203に1×1016〜5×1018atoms/cm3の濃度でリンを含んでいる。

【0099】

また、nチャネル型TFT1302には、チャネル形成領域204、ソース領域205、ドレイン領域206、そしてチャネル形成領域とドレイン領域との間に、ゲート絶縁膜を介してゲート配線と重なった領域(本明細書中ではこのような領域をLov領域という。なお、ovはoverlapの意味で付した。)207が形成される。この時、Lov領域207は2×1016〜5×1019atoms/cm3の濃度でリンを含み、且つ、ゲート配線と全部重なるように形成される。

【0100】

また、nチャネル型TFT1303には、チャネル形成領域208、ソース領域209、ドレイン領域210、そしてチャネル形成領域を挟むようにしてLDD領域211、212が形成される。即ち、ソース領域とチャネル形成領域との間及びドレイン領域とチャネル形成領域との間にLDD領域が形成される。

【0101】

なお、この構造ではLDD領域211、212の一部がゲート配線と重なるように配置されたために、ゲート絶縁膜を介してゲート配線と重なった領域(Lov領域)とゲート配線と重ならない領域(本明細書中ではこのような領域をLoff領域という。なお、offはoffsetの意味で付した。)が実現されている。

【0102】

LDD領域211はさらにLov領域211a、Loff領域211bに区別できる。また、前述のLov領域211aには2×1016〜5×1019atoms/cm3の濃度でリンが含まれるが、Loff領域211bはその1〜2倍(代表的には1.2〜1.5倍)の濃度でリンが含まれる。

【0103】

また、画素TFT1304には、チャネル形成領域213、214、ソース領域215、ドレイン領域216、Loff領域217〜220、Loff領域218、219に接したn型不純物領域(a)221が形成される。この時、ソース領域215、ドレイン領域216はそれぞれn型不純物領域(a)で形成され、Loff領域217〜220はn型不純物領域(c)で形成される。

【0104】

本実施例では、画素回路および制御回路が要求する回路仕様に応じて各回路を形成するTFTの構造を最適化し、半導体装置の動作性能および信頼性を向上させることができる。具体的には、nチャネル型TFTは回路仕様に応じてLDD領域の配置を異ならせ、Lov領域またはLoff領域を使い分けることによって、同一基板上に高速動作またはホットキャリア対策を重視したTFT構造と、低オフ電流動作を重視したTFT構造とを実現できる。

【0105】

例えば、アクティブマトリクス型液晶表示装置の場合、nチャネル型TFT1302は高速動作を重視するシフトレジスタ回路、分周波回路、信号分割回路、レベルシフタ回路、バッファ回路などの制御回路に適している。即ち、チャネル形成領域とドレイン領域との間のみにLov領域を形成することで、できるだけ抵抗成分を低減させつつホットキャリア対策を重視した構造となっている。これは上記回路群の場合、ソース領域とドレイン領域の機能が変わらず、キャリア(電子)の移動する方向が一定だからである。

【0106】

但し、必要に応じてチャネル形成領域を挟んでLov領域を形成することもできる。即ち、ソース領域とチャネル形成領域の間、及びドレイン領域とチャネル形成領域との間に形成することも可能である。

【0107】

また、nチャネル型TFT1303はホットキャリア対策と低オフ電流動作の双方を重視するサンプリング回路(サンプルホールド回路)に適している。即ち、Lov領域を形成することでホットキャリア対策とし、さらにLoff領域を形成することで低オフ電流動作を実現する。また、サンプリング回路はソース領域とドレイン領域の機能が反転してキャリアの移動方向が180°変わるため、ゲート配線を中心に線対称となるような構造としなければならない。なお、場合によってはLov領域のみとすることもありうる。

【0108】

また、nチャネル型TFT1304は低オフ電流動作を重視した画素回路、サンプリング回路(サンプルホールド回路)に適している。即ち、オフ電流値を増加させる要因となりうるLov領域を配置せず、Loff領域とオフセット領域を配置することで低オフ電流動作を実現している。また、制御回路のLDD領域よりも低い濃度のLDD領域をLoff領域として用いることで、多少オン電流値が低下しても徹底的にオフ電流値を低減する対策を打っている。さらに、n型不純物領域(a)221はオフ電流値を低減する上で非常に有効であることが確認されている。

【0109】

また、チャネル長3〜7μmに対してnチャネル型TFT1302のLov領域207の長さ(幅)は0.3〜3.0μm、代表的には0.5〜1.5μmとすれば良い。また、nチャネル型TFT303のLov領域211a、212aの長さ(幅)は0.3〜3.0μm、代表的には0,5〜1.5μm、Loff領域211b、212bの長さ(幅)は1.0〜3.5μm、代表的には1.5〜2.0μmとすれば良い。また、画素TFT1304に設けられるLoff領域217〜220の長さ(幅)は0.5〜3.5μm、代表的には2.0〜2.5μmとすれば良い。

【0110】

さらに、pチャネル型TFT1301は自己整合(セルフアライン)的に形成され、nチャネル型TFT1302〜1304は非自己整合(ノンセルフアライン)的に形成されている点も本発明の特徴の一つである。

【0111】

また、本実施例では保持容量の誘電体として比誘電率が7〜9と高いアルミナ膜を用いたことで、必要な容量を形成するために必要な保持容量の占有面積を少なくすることができる。さらに、本実施例のように画素TFT上に形成される遮蔽膜を保持容量の一方の電極とすることで、アクティブマトリクス型液晶表示装置の画像表示部の開口率を向上させることができる。

【0112】

なお、本発明は本実施例に示した保持容量の構造に限定される必要はない。例えば、本出願人による特願平9−316567号出願、特願平9−273444号出願または特願平10−254097号出願に記載された構造の保持容量を用いることもできる。

【0113】

ここでアクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を説明する。図4に示すように、図3(B)の状態の基板に対し、配向膜501を形成する。本実施例では配向膜としてポリイミド膜を用いる。また、対向基板502には、透明導電膜503と、配向膜504とを形成する。なお、対向基板には必要に応じてカラーフィルターや遮蔽膜を形成しても良い。

【0114】

次に、配向膜を形成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するように調節する。そして、画素回路と、制御回路が形成されたアクティブマトリクス基板と対向基板とを、公知のセル組み工程によってシール材やスペーサ(共に図示せず)などを介して貼りあわせる。その後、両基板の間に液晶505を注入し、封止剤(図示せず)によって完全に封止する。液晶には公知の液晶材料を用いれば良い。このようにして図4に示すアクティブマトリクス型液晶表示装置が完成する。

【0115】

[実施例2]

【0116】

ここでは画素部の画素TFTと、画素部の周辺に設けられる駆動回路(ソース信号線駆動回路、ゲート信号線駆動回路等)の回路TFTを同一基板上に作製する方法について工程に従って詳細に説明する。但し、説明を簡単にするために、CMOS回路と、nチャネル型TFTとを図示することにする。

【0117】

図5(A)において、6000は耐熱性を有する基板であり、石英基板、シリコン基板、セラミックス基板、金属基板(代表的にはステンレス基板)を用いれば良い。どの基板を用いる場合においても、必要に応じて下地膜(好ましくは珪素を主成分とする絶縁膜)を設けても構わない。

【0118】

次に基板表面をフッ素を含むプラズマ6001aで処理した後、その処理した表面6001b上に20〜6050nm(好ましくは30〜80nm)の厚さで非晶質構造を有する半導体膜を、プラズマCVD法やスパッタ法などの公知の方法で形成する。本実施例では、プラズマCVD法で非晶質シリコン膜を53nmの厚さに形成した。非晶質構造を有する半導体膜としては、非晶質半導体膜や微結晶半導体膜があり、非晶質シリコンゲルマニウム膜などの非晶質構造を有する化合物半導体膜を適用しても良い。また、下地膜を形成する場合、下地膜と非晶質シリコン膜とは同じ成膜法で形成することが可能であるので、両者を連続形成しても良い。下地膜を形成した後、一旦大気雰囲気に晒さないことでその表面の汚染を防ぐことが可能となり、作製するTFTの特性バラツキやしきい値電圧の変動を低減させることができる。

【0119】

そして、公知の結晶化技術を使用して非晶質シリコン膜から結晶質シリコン膜6002を形成する。例えば、レーザー結晶化法や熱結晶化法(固相成長法)を適用すれば良いが、ここでは、特開平7−6030652号公報で開示された技術に従って、触媒元素を用いる結晶化法で結晶質シリコン膜6002を形成した。

【0120】

なお、非晶質珪素膜の結晶化を助長する触媒元素としてニッケル(Ni)を含有した溶液をスピンコート法により塗布し、Ni含有層を形成した。また、触媒元素としてはニッケル以外にも、コバルト(Co)、鉄(Fe)、パラジウム(Pd)、白金(Pt)、銅(Cu)、金(Au)等を用いることができる。

【0121】

また、上記触媒元素の添加工程は、レジストマスクを利用したイオン注入法またはプラズマドーピング法を用いることもできる。この場合、添加領域の占有面積の低減、横成長領域の成長距離の制御が容易となるので、微細化した回路を構成する際に有効な技術となる。

【0122】

また結晶化の工程に先立って、非晶質シリコン膜の含有水素量にもよるが、400〜500℃で1時間程度の熱処理を行い、含有水素量を5atom%以下にしてから結晶化させることが望ましい。触媒元素の添加工程が終了したら、450℃で1時間程度の水素出しの後、不活性雰囲気、水素雰囲気または酸素雰囲気中において500〜700℃(代表的には550〜650℃)の温度で4〜24時間の加熱処理を加えて非晶質シリコン膜の結晶化を行う。本実施例では窒素雰囲気で600℃、12時間の加熱処理を行い非晶質シリコン膜の結晶化を行った。

【0123】

非晶質シリコン膜を結晶化させると原子の再配列が起こり緻密化するので、作製される結晶質シリコン膜の厚さは当初の非晶質シリコン膜の厚さ(本実施例では53nm)よりも1〜15%程度減少した。(図5(B))。

【0124】

そして結晶質シリコン膜6002上に酸化珪素膜からなる130nmの厚さの保護酸化膜6003を形成した。そして結晶質シリコン膜6002にゲッタリング領域を形成するために、保護酸化膜6003に開口部6004を形成した。(図5(C))

【0125】

そしてレジストマスク6005を除去した後に、結晶質シリコン膜6002中のニッケルを除去するために、リンをドーピングする。すると、開口部6004から結晶質シリコン膜6002にリンがドーピングされ、ゲッタリング領域6007が形成される。このとき、ドーピングの加速電圧と、酸化膜で成る保護酸化膜6003の厚さを最適化し、リンが保護酸化膜6003を実質的に突き抜けないようにする。

【0126】

ドーピングはリン(P)の濃度が1×1020〜1×1021atoms/cm3程度になるように調節した。本実施例では、リン(P)の濃度が5×1020atoms/cm3となるように、イオンドーピング装置を用いて行った。

【0127】

なお、イオンドープの際の加速電圧は10kevとした。10kevの加速電圧であれば、リンは保護酸化膜6007の厚さを100nm以上とするとほとんど通過することができない。

【0128】

その後、600℃の窒素雰囲気にて1〜12時間(本実施例では12時間)熱アニールし、ニッケル元素のゲッタリングを行った。加熱によりニッケルがリンに吸い寄せられることになる。600℃の温度のもとでは、リン原子は膜中をほとんど動かないが、ニッケル原子は数100μm程度またはそれ以上の距離を移動することができる。このことからリンがニッケルのゲッタリングに最も適した元素の1つであることが理解できる。(図5(D))

【0129】

次に保護酸化膜6003をマスクとしてエッチングし、ゲッタリング領域6007を除去する。(図5(E))

【0130】

そして保護酸化膜6003を除去した後に(図6(A))、非晶質シリコン膜6002を覆うように基板6001上に酸化珪素膜からなる酸化膜6008aを形成した。本実施例では20nmの厚さで形成した。(図6(B))

【0131】

次に結晶質シリコン膜6002を酸化性気体の雰囲気下でアッシングすることにより、結晶質シリコン膜6002のシリコンの密度を上げ、膜を緻密にした。本実施例では、950℃で酸素雰囲気下で熱酸化し、結晶質シリコン膜6002の膜厚を15nm程度減少させた。(図6(C))

【0132】

そして熱酸化により厚さが大きくなった熱処理後酸化膜6008bを除去し(図6(D))、パターニングすることによって、半導体膜6010、6011、6012を形成した。(図7(A))

【0133】

そして、半導体膜6010、6011、6012を覆って第1ゲート絶縁膜6013が形成される。代表的には、酸化珪素膜又は窒化珪素膜からなる第1ゲート絶縁膜6013を、その膜厚が5〜200nm(好ましくは100〜150nm)となるように形成すれば良い。本実施例では酸化珪素膜または酸化珪素を主成分とする膜からなる第1ゲート絶縁膜6013の膜厚を40nmとした。(図7(B))

【0134】

次にレジストマスク6014を利用して第1ゲート絶縁膜6013の一部をエッチングすることにより、半導体膜6012の一部を露出させた。そしてリンをドーピングすることによって、Csの一部となる不純物領域(Cs領域)6015を形成した。ドーピングは加速電圧10keV程度で行い、リン(P)の濃度が1×1019〜1×1020atoms/cm3程度になるように調節した。本実施例では、リン(P)の濃度が5×1019atoms/cm3となるように、イオンドーピング装置を用いて行った。(図7(C))

【0135】

レジストマスク6014を除去した後、第2ゲート絶縁膜6016を形成した。代表的には、第2ゲート絶縁膜6016の膜厚は5〜200nm(好ましくは100〜150nm)とすれば良い。本実施例では窒化珪素膜からなる第2ゲート絶縁膜6016を、その膜厚が20nmとなるように形成した。(図7(D))

【0136】

そして第1導電膜6017及び第2導電膜6018を順に形成した。本実施例ではゲート電極を多層構造とするが、ゲート電極を単層で形成していてもよい。

【0137】

そして開口部6004及び結晶質シリコン膜6002のpチャネル型TFTが形成される部分を覆ってレジストマスク6005を形成した。そして結晶質シリコン膜6002のnチャネル型TFTが形成される部分にしきい値電圧を制御する目的で、p型を付与する不純物としてボロン(B)をドーピングした。ドーピングは加速電圧30keV程度で行い、ボロン(B)の濃度が5×1017〜5×1018atoms/cm3程度になるように調節した。本実施例では、ボロン(B)の濃度が1×1018atoms/cm3となるようにした。ボロン(B)の添加はイオンドープ法で実施しても良いし、非晶質シリコン膜を成膜するときに同時に添加しておくこともできる。そして結晶質シリコン膜6002の特性によっては、しきい値電圧を制御するためにボロン(B)ではなくリン(P)を添加しても良い。ここでのボロン(B)添加は必ずしも必要でないが、結晶質シリコン膜6002のボロン(B)を添加した部分(チャネルドープ部)6006はnチャネル型TFTのしきい値電圧を所定の範囲内に収めるために形成することが好ましかった。(図8(A))

【0138】

第1導電膜6017はn型の不純物を有する結晶質シリコン膜であり、CVD法を用いて150nmの膜厚で形成されている。また第2導電膜6018はタングステンシリサイドであり、スパッタリングにより150nmの膜厚で形成されている。(図8(B))この場合、金属膜を用いるよりも若干抵抗が上がるが、金属シリサイド膜と珪素膜との積層構造は耐熱性も高く、酸化にも強いので有効な構造である。なお第1導電膜6017は窒化タンタル(TaN)、窒化タングステン(WN)、窒化チタン(TiN)膜、窒化モリブデン(MoN)、タングステンシリサイド、チタンシリサイドまたはモリブデンシリサイドで形成しても良く、第2導電膜6018はタンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)から選ばれた元素、または前記元素を主成分とする合金か、前記元素を組み合わせた合金膜(代表的にはMo−W合金膜、Mo−Ta合金膜)で形成しても良い。

【0139】

次に第1導電膜6017及び第2導電膜6018をパターニングし、pチャネル型TFTのゲート電極6020、nチャネル型のTFTのゲート電極6021、6022、Cs電極6023を形成した。(図8(C))

【0140】

そしてゲート電極6020、6021、6022、Cs電極6023をマスクとして利用し、半導体膜6010、6011及び半導体膜6012の一部にn型を付与する不純物をドーピングし、不純物領域6024〜6029を形成した。n型を付与する不純物としては、リン(P)や砒素(As)を用いれば良く、ここではリン(P)を添加すべく、フォスフィン(PH3)を用いたイオンドープ法を適用した。ドーピングは加速電圧40keV程度で行い、リン(P)の濃度が5×1017〜5×1018atoms/cm3程度になるように調節した。本実施例では、不純物領域6024〜6029のリン(P)の濃度が1×1018atoms/cm3となるように、イオンドーピング装置を用いて行った。本明細書中では、ここで形成された不純物領域6024〜6029に含まれるn型を付与する不純物の濃度を(n-)と表す。(図8(D))

【0141】

次にpチャネル型TFTとなる半導体膜6010と、nチャネル型TFTとなる半導体膜6011、6012の一部を覆うようにレジストマスク6030、6031、6032を形成した。そしてレジストマスク6030、6031、6032を利用して半導体膜6011、6012の一部にn型を付与する不純物をドーピングし、不純物領域6033〜6036を形成した。

【0142】

不純物領域6033〜6036の形成は、フォスフィン(PH3)を用いたイオンドープ法で行い、ドーピングは加速電圧40keV程度で行い、リン(P)の濃度が5×1019〜5×1020atoms/cm3程度になるように調節した。本実施例では、不純物領域6033〜6036のリン(P)の濃度が1×1020atoms/cm3となるようにした。本明細書中では、ここで形成された不純物領域6033〜6036に含まれるn型を付与する不純物の濃度を(n+)と表す。(図9(A))

【0143】

レジストマスク6030〜6032を除去し、nチャネル型TFTとなる部分及びCsとなる部分をレジストマスク6039で覆った。そして半導体膜6010にp型を付与する不純物をドーピングした。本実施例では、ジボラン(B2H6)を用いたイオンドープ法で不純物領域6037、6038を形成した。ドーピングは加速電圧40keV程度で行い、ボロン(B)の濃度が5×1019〜5×1020atoms/cm3程度になるように調節した。本実施例では、不純物領域6037、6038のボロン(B)の濃度が1×1020atoms/cm3となるようにした。本明細書中では、ここで形成された不純物領域6037、6038に含まれるp型を付与する不純物元素の濃度を(p+)と表す。 不純物領域6037、6038には、既に前工程で添加されたリン(P)またはボロン(B)が含まれているが、それに比して十分に高い濃度でボロン(B)が添加されるので、p型の導電性が確保され、TFTの特性に何ら影響を与えることはない。(図9(B))

【0144】

レジストマスク6039を除去した後、絶縁膜6040を形成した。絶縁膜6040は窒化珪素膜からなり、CVD法によって膜厚70nmに形成された。(図9(C))

【0145】

次に窒素雰囲気下、850℃で30分の条件で加熱することにより、不純物領域に含まれる不純物が半導体膜6010〜6012内で拡散してゲート電極6020〜6022の下部にまで広がる。ゲート電極6020〜6022の下部に位置する不純物領域6041〜6046をLov領域と称する。またゲート電極6020〜6022の下部に位置しておらず、不純物領域(ソース領域またはドレイン領域)6033〜6036に接している不純物領域6047〜6050をLof領域と称する。不純物領域6033〜6038、6041〜6050は上記熱処理によって活性化される。(図10(A))

【0146】

次に酸化シリコン又は酸化窒化シリコンからなる第1の層間絶縁膜6052を500〜60500nmの厚さで形成する。本実施例では、窒化珪素を用い1000nmの厚さで形成した。その後、ソース領域またはドレイン領域6033〜6038に達するコンタクトホールを形成し、ソース配線6053、6055、6057と、ドレイン配線6054、6056、6058を形成する。なお、図示していないが、本実施例ではこのソース配線、ドレイン配線を、Ti膜60nm、窒素を含むTi膜40nm、Siを含むアルミニウム膜300nm、Ti膜100nmをスパッタ法で連続して形成した4層構造の積層膜とした。(図10(B))

【0147】

次にソース配線6053、6055、6057と、ドレイン配線6054、6056、6058を覆うように第1層間絶縁膜6052上に窒化珪素膜からなるパッシベーション膜6060を220nmの厚さで形成する。(図10(C))そしてパッシベーション膜6060を覆うようにして第2層間絶縁膜が形成される。この第2層間絶縁膜はアクリル膜からなり、厚さが800nmに形成される。

【0148】

アクリル膜からなる第2層間絶縁膜を150℃、0.3hrの条件で加熱した後、第2層間絶縁膜の上にTi膜またはTiを主成分とする厚さが100nmの遮光膜を形成する。

【0149】

そして、遮光膜を覆うように第2層間絶縁膜上に第3層間絶縁膜を形成した。第3層間絶縁膜はアクリル膜からなり、その厚さは500nm〜1000nmで形成される。本実施例では第3層間絶縁膜の厚さを800nmとした。

【0150】

第3層間絶縁膜にはコンタクトホールが形成され、その後、画素電極が形成される。本実施例では画素電極の厚さを2.8μmとした。画素電極はコンタクトホールを介してドレイン配線と電気的に接続される。画素電極は透明導電膜を用いれば良い。

【0151】

以上のように、本発明の半導体装置はドライバー回路および画素マトリクス回路に様々な特徴を有しており、これらの相乗効果によって明るく高精細な画像が得られ、動作性能および信頼性の高い電気光学装置を得る。そして、そのような電気光学装置を部品として搭載した高性能な電子機器を得る。

【0152】

[実施例3]

本願発明を実施して形成されたCMOS回路や画素部は様々な電気光学装置(アクティブマトリクス型液晶ディスプレイ、アクティブマトリクス型ELディスプレイ、アクティブマトリクス型ECディスプレイ)に用いることができる。即ち、それら電気光学装置を表示部に組み込んだ電子機器全てに本願発明を実施できる。

【0153】

その様な電子機器としては、ビデオカメラ、デジタルカメラ、プロジェクター(リア型またはフロント型)、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、カーステレオ、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図14、図15及び図16に示す。

【0154】

図14(A)はパーソナルコンピュータであり、本体2001、画像入力部2002、表示部2003、キーボード2004等を含む。本発明を画像入力部2002、表示部2003やその他の信号制御回路に適用することができる。

【0155】

図14(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106等を含む。本発明を表示部2102やその他の信号制御回路に適用することができる。

【0156】

図14(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示部2205等を含む。本発明は表示部2205やその他の信号制御回路に適用できる。

【0157】

図14(D)はゴーグル型ディスプレイであり、本体2301、表示部2302、アーム部2303等を含む。本発明は表示部2302やその他の信号制御回路に適用することができる。

【0158】

図14(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体2401、表示部2402、スピーカ部2403、記録媒体2404、操作スイッチ2405等を含む。なお、このプレーヤーは記録媒体としてDVD(Digtial Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示部2402やその他の信号制御回路に適用することができる。

【0159】

図14(F)はデジタルカメラであり、本体2501、表示部2502、接眼部2503、操作スイッチ2504、受像部(図示しない)等を含む。本願発明を表示部2502やその他の信号制御回路に適用することができる。

【0160】

図15(A)はフロント型プロジェクターであり、投射装置2601、スクリーン2602等を含む。本発明は投射装置2601の一部を構成する液晶表示装置2808やその他の信号制御回路に適用することができる。

【0161】

図15(B)はリア型プロジェクターであり、本体2701、投射装置2702、ミラー2703、スクリーン2704等を含む。本発明は投射装置2702の一部を構成する液晶表示装置2808やその他の信号制御回路に適用することができる。

【0162】

なお、図15(C)は、図15(A)及び図15(B)中における投射装置2601、2702の構造の一例を示した図である。投射装置2601、2702は、光源光学系2801、ミラー2802、2804〜2806、ダイクロイックミラー2803、プリズム2807、液晶表示装置2808、位相差板2809、投射光学系2810で構成される。投射光学系2810は、投射レンズを含む光学系で構成される。本実施例は三板式の例を示したが、特に限定されず、例えば単板式であってもよい。また、図15(C)中において矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するためのフィルム、IRフィルム等の光学系を設けてもよい。

【0163】

また、図15(D)は、図15(C)中における光源光学系2801の構造の一例を示した図である。本実施例では、光源光学系2801は、リフレクター2811、光源2812、レンズアレイ2813、2814、偏光変換素子2815、集光レンズ2816で構成される。なお、図15(D)に示した光源光学系は一例であって特に限定されない。例えば、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するフィルム、IRフィルム等の光学系を設けてもよい。

【0164】

ただし、図15に示したプロジェクターにおいては、透過型の電気光学装置を用いた場合を示しており、反射型の電気光学装置及びEL表示装置での適用例は図示していない。

【0165】

図16(A)は携帯電話であり、本体2901、音声出力部2902、音声入力部2903、表示部2904、操作スイッチ2905、アンテナ2906等を含む。本願発明を音声出力部2902、音声入力部2903、表示部2904やその他の信号制御回路に適用することができる。

【0166】

図16(B)は携帯書籍(電子書籍)であり、本体3001、表示部3002、3003、記憶媒体3004、操作スイッチ3005、アンテナ3006等を含む。本発明は表示部3002、3003やその他の信号回路に適用することができる。

【0167】

図16(C)はディスプレイであり、本体3101、支持台3102、表示部3103等を含む。本発明は表示部3103に適用することができる。本発明のディスプレイは特に大画面化した場合において有利であり、対角10インチ以上(特に30インチ以上)のディスプレイには有利である。

【0168】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。また、本実施例の電子機器は実施例1、2のどのような組み合わせからなる構成を用いても実現することができる。

【0169】

[実施例4]

本実施例では、本願発明を用いてEL(エレクトロルミネッセンス)表示装置を作製した例について説明する。

【0170】

図17(A)は本願発明を用いたEL表示装置の上面図である。図117(A)において、4010は基板、4011は画素部、4012はソース側駆動回路、4013はゲート側駆動回路であり、それぞれの駆動回路は配線4014〜4016を経てFPC4017に至り、外部機器へと接続される。

【0171】

このとき、少なくとも画素部、好ましくは駆動回路及び画素部を囲むようにしてカバー材6000、シーリング材(ハウジング材ともいう)7000、密封材(第2のシーリング材)7001が設けられている。

【0172】

また、図17(B)は本実施例のEL表示装置の断面構造であり、基板4010、下地膜4021の上に駆動回路用TFT(但し、ここではnチャネル型TFTとpチャネル型TFTを組み合わせたCMOS回路を図示している。)4022及び画素部用TFT4023(但し、ここではEL素子への電流を制御するTFTだけ図示している。)が形成されている。これらのTFTは公知の構造(トップゲート構造またはボトムゲート構造)を用いれば良い。

【0173】

本願発明は、駆動回路用TFT4022、画素部用TFT4023に際して用いることができる。

【0174】

本願発明を用いて駆動回路用TFT4022、画素部用TFT4023が完成したら、樹脂材料でなる層間絶縁膜(平坦化膜)4026の上に画素部用TFT4023のドレインと電気的に接続する透明導電膜でなる画素電極4027を形成する。透明導電膜としては、酸化インジウムと酸化スズとの化合物(ITOと呼ばれる)または酸化インジウムと酸化亜鉛との化合物を用いることができる。そして、画素電極4027を形成したら、絶縁膜4028を形成し、画素電極4027上に開口部を形成する。

【0175】

次に、EL層4029を形成する。EL層4029は公知のEL材料(正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層)を自由に組み合わせて積層構造または単層構造とすれば良い。どのような構造とするかは公知の技術を用いれば良い。また、EL材料には低分子系材料と高分子系(ポリマー系)材料がある。低分子系材料を用いる場合は蒸着法を用いるが、高分子系材料を用いる場合には、スピンコート法、印刷法またはインクジェット法等の簡易な方法を用いることが可能である。

【0176】

本実施例では、シャドーマスクを用いて蒸着法によりEL層を形成する。シャドーマスクを用いて画素毎に波長の異なる発光が可能な発光層(赤色発光層、緑色発光層及び青色発光層)を形成することで、カラー表示が可能となる。その他にも、色変換層(CCM)とカラーフィルターを組み合わせた方式、白色発光層とカラーフィルターを組み合わせた方式があるがいずれの方法を用いても良い。勿論、単色発光のEL表示装置とすることもできる。

【0177】

EL層4029を形成したら、その上に陰極4030を形成する。陰極4030とEL層4029の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、真空中でEL層4029と陰極4030を連続成膜するか、EL層4029を不活性雰囲気で形成し、大気解放しないで陰極4030を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。

【0178】

なお、本実施例では陰極4030として、LiF(フッ化リチウム)膜とAl(アルミニウム)膜の積層構造を用いる。具体的にはEL層4029上に蒸着法で1nm厚のLiF(フッ化リチウム)膜を形成し、その上に300nm厚のアルミニウム膜を形成する。勿論、公知の陰極材料であるMgAg電極を用いても良い。そして陰極4030は4031で示される領域において配線4016に接続される。配線4016は陰極4030に所定の電圧を与えるための電源供給線であり、導電性ペースト材料4032を介してFPC4017に接続される。

【0179】

4031に示された領域において陰極4030と配線4016とを電気的に接続するために、層間絶縁膜4026及び絶縁膜4028にコンタクトホールを形成する必要がある。これらは層間絶縁膜4026のエッチング時(画素電極用コンタクトホールの形成時)や絶縁膜4028のエッチング時(EL層形成前の開口部の形成時)に形成しておけば良い。また、絶縁膜4028をエッチングする際に、層間絶縁膜4026まで一括でエッチングしても良い。この場合、層間絶縁膜4026と絶縁膜4028が同じ樹脂材料であれば、コンタクトホールの形状を良好なものとすることができる。

【0180】

このようにして形成されたEL素子の表面を覆って、パッシベーション膜6003、充填材6004、カバー材6000が形成される。

【0181】

さらに、EL素子部を囲むようにして、カバー材6000と基板4010の内側にシーリング材が設けられ、さらにシーリング材7000の外側には密封材(第2のシーリング材)7001が形成される。

【0182】

このとき、この充填材6004は、カバー材6000を接着するための接着剤としても機能する。充填材6004としては、PVC(ポリビニルクロライド)、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。この充填材6004の内部に乾燥剤を設けておくと、吸湿効果を保持できるので好ましい。

【0183】

また、充填材6004の中にスペーサーを含有させてもよい。このとき、スペーサーをBaOなどからなる粒状物質とし、スペーサー自体に吸湿性をもたせてもよい。

【0184】

スペーサーを設けた場合、パッシベーション膜6003はスペーサー圧を緩和することができる。また、パッシベーション膜とは別に、スペーサー圧を緩和する樹脂膜などを設けてもよい。

【0185】

また、カバー材6000としては、ガラス板、アルミニウム板、ステンレス板、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリルフィルムを用いることができる。なお、充填材6004としてPVBやEVAを用いる場合、数十μmのアルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることが好ましい。

【0186】

但し、EL素子からの発光方向(光の放射方向)によっては、カバー材6000が透光性を有する必要がある。

【0187】

また、配線4016はシーリング材7000および密封材7001と基板4010との隙間を通ってFPC4017に電気的に接続される。なお、ここでは配線4016について説明したが、他の配線4014、4015も同様にしてシーリング材7000および密封材7001の下を通ってFPC4017に電気的に接続される。

【0188】

[実施例5]

本実施例では、本願発明を用いて実施例4とは異なる形態のEL表示装置を作製した例について、図18(A)、(B)を用いて説明する。図17(A)、(B)と同じ番号のものは同じ部分を指しているので説明は省略する。

【0189】

図18(A)は本実施例のEL表示装置の上面図であり、図18(A)をA-A'で切断した断面図を図18(B)に示す。

【0190】

実施例4に従って、EL素子の表面を覆ってパッシベーション膜6003までを形成する。

【0191】

さらに、EL素子を覆うようにして充填材6004を設ける。この充填材6004は、カバー材6000を接着するための接着剤としても機能する。充填材6004としては、PVC(ポリビニルクロライド)、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。この充填材6004の内部に乾燥剤を設けておくと、吸湿効果を保持できるので好ましい。

【0192】

また、充填材6004の中にスペーサーを含有させてもよい。このとき、スペーサーをBaOなどからなる粒状物質とし、スペーサー自体に吸湿性をもたせてもよい。

【0193】

スペーサーを設けた場合、パッシベーション膜6003はスペーサー圧を緩和することができる。また、パッシベーション膜とは別に、スペーサー圧を緩和する樹脂膜などを設けてもよい。

【0194】

また、カバー材6000としては、ガラス板、アルミニウム板、ステンレス板、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリルフィルムを用いることができる。なお、充填材6004としてPVBやEVAを用いる場合、数十μmのアルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることが好ましい。

【0195】

但し、EL素子からの発光方向(光の放射方向)によっては、カバー材6000が透光性を有する必要がある。

【0196】

次に、充填材6004を用いてカバー材6000を接着した後、充填材6004の側面(露呈面)を覆うようにフレーム材6001を取り付ける。フレーム材6001はシーリング材(接着剤として機能する)6002によって接着される。このとき、シーリング材6002としては、光硬化性樹脂を用いるのが好ましいが、EL層の耐熱性が許せば熱硬化性樹脂を用いても良い。なお、シーリング材6002はできるだけ水分や酸素を透過しない材料であることが望ましい。また、シーリング材6002の内部に乾燥剤を添加してあっても良い。

【0197】

また、配線4016はシーリング材6002と基板4010との隙間を通ってFPC4017に電気的に接続される。なお、ここでは配線4016について説明したが、他の配線4014、4015も同様にしてシーリング材6002の下を通ってFPC4017に電気的に接続される。

【0198】

[実施例6]

ここでEL表示パネルにおける画素部のさらに詳細な断面構造を図19に、上面構造を図20(A)に、回路図を図20(B)に示す。図19、図20(A)及び(B)では共通の符号を用いるので互いに参照すれば良い。

【0199】

図19において、基板3501上に設けられたスイッチング用TFT3502は本願発明のNTFTを用いて形成される(実施例1、2参照)。本実施例ではダブルゲート構造としているが、構造及び作製プロセスに大きな違いはないので説明は省略する。但し、ダブルゲート構造とすることで実質的に二つのTFTが直列された構造となり、オフ電流値を低減することができるという利点がある。なお、本実施例ではダブルゲート構造としているが、シングルゲート構造でも構わないし、トリプルゲート構造やそれ以上のゲート本数を持つマルチゲート構造でも構わない。また、本願発明のPTFTを用いて形成しても構わない。

【0200】

また、電流制御用TFT3503は本願発明のNTFTを用いて形成される。このとき、スイッチング用TFT3502のドレイン配線35は配線36によって電流制御用TFTのゲート電極37に電気的に接続されている。また、38で示される配線は、スイッチング用TFT3502のゲート電極39a、39bを電気的に接続するゲート配線である。

【0201】

このとき、電流制御用TFT3503が本願発明の構造であることは非常に重要な意味を持つ。電流制御用TFTはEL素子を流れる電流量を制御するための素子であるため、多くの電流が流れ、熱による劣化やホットキャリアによる劣化の危険性が高い素子でもある。そのため、電流制御用TFTのドレイン側に、ゲート絶縁膜を介してゲート電極に重なるようにLDD領域を設ける本願発明の構造は極めて有効である。

【0202】

また、本実施例では電流制御用TFT3503をシングルゲート構造で図示しているが、複数のTFTを直列につなげたマルチゲート構造としても良い。さらに、複数のTFTを並列につなげて実質的にチャネル形成領域を複数に分割し、熱の放射を高い効率で行えるようにした構造としても良い。このような構造は熱による劣化対策として有効である。

【0203】

また、図20(A)に示すように、電流制御用TFT3503のゲート電極37となる配線は3504で示される領域で、電流制御用TFT3503のドレイン配線40と絶縁膜を介して重なる。このとき、3504で示される領域ではコンデンサが形成される。このコンデンサ3504は電流制御用TFT3503のゲートにかかる電圧を保持するためのコンデンサとして機能する。なお、ドレイン配線40は電流供給線(電源線)3506に接続され、常に一定の電圧が加えられている。

【0204】

スイッチング用TFT3502及び電流制御用TFT3503の上には第1パッシベーション膜41が設けられ、その上に樹脂絶縁膜でなる平坦化膜42が形成される。平坦化膜42を用いてTFTによる段差を平坦化することは非常に重要である。後に形成されるEL層は非常に薄いため、段差が存在することによって発光不良を起こす場合がある。従って、EL層をできるだけ平坦面に形成しうるように画素電極を形成する前に平坦化しておくことが望ましい。

【0205】

また、43は反射性の高い導電膜でなる画素電極(EL素子の陰極)であり、電流制御用TFT3503のドレインに電気的に接続される。画素電極43としてはアルミニウム合金膜、銅合金膜または銀合金膜など低抵抗な導電膜またはそれらの積層膜を用いることが好ましい。勿論、他の導電膜との積層構造としても良い。

【0206】

また、絶縁膜(好ましくは樹脂)で形成されたバンク44a、44bにより形成された溝(画素に相当する)の中に発光層45が形成される。なお、ここでは一画素しか図示していないが、R(赤)、G(緑)、B(青)の各色に対応した発光層を作り分けても良い。発光層とする有機EL材料としてはπ共役ポリマー系材料を用いる。代表的なポリマー系材料としては、ポリパラフェニレンビニレン(PPV)系、ポリビニルカルバゾール(PVK)系、ポリフルオレン系などが挙げられる。

【0207】

なお、PPV系有機EL材料としては様々な型のものがあるが、例えば「H. Shenk,H.Becker,O.Gelsen,E.Kluge,W.Kreuder,and H.Spreitzer,“Polymers for Light Emitting Diodes”,Euro Display,Proceedings,1999,p.33-37」や特開平10−92576号公報に記載されたような材料を用いれば良い。

【0208】

具体的な発光層としては、赤色に発光する発光層にはシアノポリフェニレンビニレン、緑色に発光する発光層にはポリフェニレンビニレン、青色に発光する発光層にはポリフェニレンビニレン若しくはポリアルキルフェニレンを用いれば良い。膜厚は30〜150nm(好ましくは40〜100nm)とすれば良い。

【0209】

但し、以上の例は発光層として用いることのできる有機EL材料の一例であって、これに限定する必要はまったくない。発光層、電荷輸送層または電荷注入層を自由に組み合わせてEL層(発光及びそのためのキャリアの移動を行わせるための層)を形成すれば良い。

【0210】

例えば、本実施例ではポリマー系材料を発光層として用いる例を示したが、低分子系有機EL材料を用いても良い。また、電荷輸送層や電荷注入層として炭化珪素等の無機材料を用いることも可能である。これらの有機EL材料や無機材料は公知の材料を用いることができる。

【0211】

本実施例では発光層45の上にPEDOT(ポリチオフェン)またはPAni(ポリアニリン)でなる正孔注入層46を設けた積層構造のEL層としている。そして、正孔注入層46の上には透明導電膜でなる陽極47が設けられる。本実施例の場合、発光層45で生成された光は上面側に向かって(TFTの上方に向かって)放射されるため、陽極は透光性でなければならない。透明導電膜としては酸化インジウムと酸化スズとの化合物や酸化インジウムと酸化亜鉛との化合物を用いることができるが、耐熱性の低い発光層や正孔注入層を形成した後で形成するため、可能な限り低温で成膜できるものが好ましい。

【0212】

陽極47まで形成された時点でEL素子3505が完成する。なお、ここでいうEL素子3505は、画素電極(陰極)43、発光層45、正孔注入層46及び陽極47で形成されたコンデンサを指す。図36Aに示すように画素電極43は画素の面積にほぼ一致するため、画素全体がEL素子として機能する。従って、発光の利用効率が非常に高く、明るい画像表示が可能となる。

【0213】

ところで、本実施例では、陽極47の上にさらに第2パッシベーション膜48を設けている。第2パッシベーション膜48としては窒化珪素膜または窒化酸化珪素膜が好ましい。この目的は、外部とEL素子とを遮断することであり、有機EL材料の酸化による劣化を防ぐ意味と、有機EL材料からの脱ガスを抑える意味との両方を併せ持つ。これによりEL表示装置の信頼性が高められる。

【0214】

以上のように本願発明のEL表示パネルは図19のような構造の画素からなる画素部を有し、オフ電流値の十分に低いスイッチング用TFTと、ホットキャリア注入に強い電流制御用TFTとを有する。従って、高い信頼性を有し、且つ、良好な画像表示が可能なEL表示パネルが得られる。

【0215】

なお、本実施例の構成は、実施例1、2の構成と自由に組み合わせて実施することが可能である。また、実施例3の電子機器の表示部として本実施例のEL表示パネルを用いることは有効である。

【0216】

[実施例7]

本実施例では、実施例6に示した画素部において、EL素子3505の構造を反転させた構造について説明する。説明には図21を用いる。なお、図19の構造と異なる点はEL素子の部分と電流制御用TFTだけであるので、その他の説明は省略することとする。

【0217】

図21において、電流制御用TFT3503は本願発明のPTFTを用いて形成される。作製プロセスは実施例1、2を参照すれば良い。

【0218】

本実施例では、画素電極(陽極)50として透明導電膜を用いる。具体的には酸化インジウムと酸化亜鉛との化合物でなる導電膜を用いる。勿論、酸化インジウムと酸化スズとの化合物でなる導電膜を用いても良い。

【0219】

そして、絶縁膜でなるバンク51a、51bが形成された後、溶液塗布によりポリビニルカルバゾールでなる発光層52が形成される。その上にはカリウムアセチルアセトネート(acacKと表記される)でなる電子注入層53、アルミニウム合金でなる陰極54が形成される。この場合、陰極54がパッシベーション膜としても機能する。こうしてEL素子3701が形成される。

【0220】

本実施例の場合、発光層52で発生した光は、矢印で示されるようにTFTが形成された基板の方に向かって放射される。

【0221】

なお、本実施例の構成は、実施例1、2の構成と自由に組み合わせて実施することが可能である。また、実施例3の電子機器の表示部として本実施例のEL表示パネルを用いることは有効である。

【0222】

[実施例8]

本実施例では、図20(B)に示した回路図とは異なる構造の画素とした場合の例について図22(A)〜(C)に示す。なお、本実施例において、3801はスイッチング用TFT3802のソース配線、3803はスイッチング用TFT3802のゲート配線、3804は電流制御用TFT、3805はコンデンサ、3806、3808は電流供給線、3807はEL素子とする。

【0223】

図22(A)は、二つの画素間で電流供給線3806を共通とした場合の例である。即ち、二つの画素が電流供給線3806を中心に線対称となるように形成されている点に特徴がある。この場合、電源供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

【0224】

また、図22(B)は、電流供給線3808をゲート配線3803と平行に設けた場合の例である。なお、図22(B)では電流供給線3808とゲート配線3803とが重ならないように設けた構造となっているが、両者が異なる層に形成される配線であれば、絶縁膜を介して重なるように設けることもできる。この場合、電源供給線3808とゲート配線3803とで専有面積を共有させることができるため、画素部をさらに高精細化することができる。

【0225】

また、図22(C)は、図22(B)の構造と同様に電流供給線3808をゲート配線3803と平行に設け、さらに、二つの画素を電流供給線3808を中心に線対称となるように形成する点に特徴がある。また、電流供給線3808をゲート配線3803のいずれか一方と重なるように設けることも有効である。この場合、電源供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

【0226】

なお、本実施例の構成は、実施例1、2、4または5の構成と自由に組み合わせて実施することが可能である。また、実施例3の電子機器の表示部として本実施例の画素構造を有するEL表示パネルを用いることは有効である。

【0227】

[実施例9]

実施例6に示した図20(A)、(B)では電流制御用TFT3503のゲートにかかる電圧を保持するためにコンデンサ3504を設ける構造としているが、コンデンサ3504を省略することも可能である。実施例17の場合、電流制御用TFT3503として実施例1、2に示すような本願発明のNTFTを用いているため、ゲート絶縁膜を介してゲート電極に重なるように設けられたLDD領域を有している。この重なり合った領域には一般的にゲート容量と呼ばれる寄生容量が形成されるが、本実施例ではこの寄生容量をコンデンサ3504の代わりとして積極的に用いる点に特徴がある。

【0228】

この寄生容量のキャパシタンスは、上記ゲート電極とLDD領域とが重なり合った面積によって変化するため、その重なり合った領域に含まれるLDD領域の長さによって決まる。

【0229】

また、実施例8に示した図22(A),(B),(C)の構造においても同様に、コンデンサ3805を省略することは可能である。

【0230】

なお、本実施例の構成は、実施例1、2、4〜8の構成と自由に組み合わせて実施することが可能である。また、実施例3の電子機器の表示部として本実施例の画素構造を有するEL表示パネルを用いることは有効である。

【0231】

【発明の効果】

本願発明により、非晶質半導体膜をハロゲン元素で終端させることで、

非晶質半導体膜を熱結晶化法やレーザー結晶化法を用いて作製される結晶質半導体膜の配向性を高めることができる。

【0232】

さらに、そのような結晶質半導体膜を用いることでTFTの特性を向上させ、特性バラツキを低減させることができる。

【図面の簡単な説明】

【図1】 画素回路と制御回路の作製工程を示す図。

【図2】 画素回路と制御回路の作製工程を示す図。

【図3】 画素回路と制御回路の作製工程を示す図。

【図4】 画素回路と制御回路の作製工程を示す図。

【図5】 TFTの作製工程を示す図。

【図6】 TFTの作製工程を示す図。

【図7】 TFTの作製工程を示す図。

【図8】 TFTの作製工程を示す図。

【図9】 TFTの作製工程を示す図。

【図10】 TFTの作製工程を示す図。

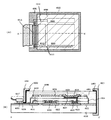

【図11】 半導体膜の結晶化工程を示す図。

【図12】 実施形態のTFTの断面を示す図。

【図13】 半導体膜の結晶化工程を示す図。

【図14】 電子機器の一例を示す図。

【図15】 電子機器の一例を示す図。

【図16】 電子機器の一例を示す図。

【図17】 EL表示装置の構造を示す図。

【図18】 EL表示装置の構造を示す図。

【図19】 EL表示装置の構造を示す図。

【図20】 EL表示装置の構造を示す図。

【図21】 EL表示装置の構造を示す図。

【図22】 EL表示装置の構造を示す図。

Claims (6)

- 基板上に非晶質半導体膜を形成し、

前記非晶質半導体膜上に前記非晶質半導体膜の結晶化を助長する触媒元素を含有する層を形成し、

前記非晶質半導体膜を第1の加熱処理により結晶質半導体膜にし、

前記結晶質半導体膜を選択的に除去して島状の結晶質半導体膜を形成し、

前記島状の結晶質半導体膜上にゲート絶縁膜を形成し、

ハロゲンを含む酸化雰囲気中で第2の加熱処理を行い、

前記非晶質半導体膜上に前記結晶化を助長する触媒元素を含有する層を形成する前に、前記非晶質半導体膜の表面から前記基板の表面または前記基板と前記非晶質半導体膜の界面にフッ素を注入し、前記基板の表面または前記基板と前記非晶質半導体膜の界面をフッ素化することを特徴とする半導体装置の作製方法。 - 基板上に非晶質半導体膜を形成し、

前記非晶質半導体膜上に前記非晶質半導体膜の結晶化を助長する触媒元素を含有する層を形成し、

前記非晶質半導体膜を第1の加熱処理により結晶質半導体膜にし、

前記結晶質半導体膜の選択された領域に15族に属する元素を添加し、

第2の加熱処理を行い、

前記結晶質半導体膜を選択的に除去して島状の結晶質半導体膜を形成し、

前記島状の結晶質半導体膜上にゲート絶縁膜を形成し、

ハロゲンを含む酸化雰囲気中で第3の加熱処理を行い、

前記非晶質半導体膜上に前記結晶化を助長する触媒元素を含有する層を形成する前に、前記非晶質半導体膜の表面から前記基板の表面または前記基板と前記非晶質半導体膜の界面にフッ素を注入し、前記基板の表面または前記基板と前記非晶質半導体膜の界面をフッ素化することを特徴とする半導体装置の作製方法。 - 基板上に非晶質半導体膜を形成し、

前記非晶質半導体膜の表面から前記基板の表面または前記基板と前記非晶質半導体膜の界面にフッ素を注入し、前記基板の表面または前記基板と前記非晶質半導体膜の界面をフッ素化し、

前記非晶質半導体膜上に選択的に絶縁膜を形成し、

前記非晶質半導体膜上及び前記絶縁膜上に前記非晶質半導体膜の結晶化を助長する触媒元素を含有する層を形成し、

前記非晶質半導体膜を第1の加熱処理により結晶質半導体膜にし、

前記絶縁膜を除去し、

前記結晶質半導体膜を選択的に除去して島状の結晶質半導体膜を形成し、

前記島状の結晶質半導体膜上にゲート絶縁膜を形成し、

ハロゲンを含む酸化雰囲気中で第2の加熱処理を行うことを特徴とする半導体装置の作製方法。 - 基板上に非晶質半導体膜を形成し、

前記非晶質半導体膜の表面から前記基板の表面または前記基板と前記非晶質半導体膜の界面にフッ素を注入し、前記基板の表面または前記基板と前記非晶質半導体膜の界面をフッ素化し、

前記非晶質半導体膜上に選択的に絶縁膜を形成し、

前記非晶質半導体膜上及び前記絶縁膜上に前記非晶質半導体膜の結晶化を助長する触媒元素を含有する層を形成し、

前記非晶質半導体膜を第1の加熱処理により結晶質半導体膜にし、

前記絶縁膜をマスクにして前記結晶質半導体膜の選択された領域に15族に属する元素を添加し、

第2の加熱処理を行い、

前記絶縁膜を除去し、

前記結晶質半導体膜を選択的に除去して島状の結晶質半導体膜を形成し、

前記島状の結晶質半導体膜上にゲート絶縁膜を形成し、

ハロゲンを含む酸化雰囲気中で第3の加熱処理を行うことを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項4のいずれか一項において、

前記触媒元素は、ニッケル(Ni)、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、及び金(Au)から選ばれた一種または複数種の元素であることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項5のいずれか一項において、

前記基板は、石英基板であることを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000002019A JP4896286B2 (ja) | 2000-01-07 | 2000-01-07 | 半導体装置の作製方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000002019A JP4896286B2 (ja) | 2000-01-07 | 2000-01-07 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001196590A JP2001196590A (ja) | 2001-07-19 |

| JP2001196590A5 JP2001196590A5 (ja) | 2007-02-22 |

| JP4896286B2 true JP4896286B2 (ja) | 2012-03-14 |

Family

ID=18531178

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000002019A Expired - Fee Related JP4896286B2 (ja) | 2000-01-07 | 2000-01-07 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4896286B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6878415B2 (en) * | 2002-04-15 | 2005-04-12 | Varian Semiconductor Equipment Associates, Inc. | Methods for chemical formation of thin film layers using short-time thermal processes |

| JP3904512B2 (ja) | 2002-12-24 | 2007-04-11 | シャープ株式会社 | 半導体装置およびその製造方法、並びに半導体装置を備えた電子機器 |

| WO2005050597A1 (en) | 2003-11-14 | 2005-06-02 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device and method for manufacturing the same |

| US8247965B2 (en) | 2003-11-14 | 2012-08-21 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting display device and method for manufacturing the same |

| CN100451797C (zh) | 2003-11-14 | 2009-01-14 | 株式会社半导体能源研究所 | 显示装置及其制造法 |

| WO2005048353A1 (en) | 2003-11-14 | 2005-05-26 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing liquid crystal display device |

| KR100796608B1 (ko) * | 2006-08-11 | 2008-01-22 | 삼성에스디아이 주식회사 | 박막 트랜지스터 어레이 기판의 제조방법 |

| US10867788B2 (en) * | 2016-12-28 | 2020-12-15 | Asm Ip Holding B.V. | Method of forming a structure on a substrate |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0323639A (ja) * | 1989-06-21 | 1991-01-31 | Sony Corp | 薄膜トランジスタ |

| JP3386863B2 (ja) * | 1993-09-29 | 2003-03-17 | 三菱電機株式会社 | 薄膜トランジスタ及びその製造方法 |

| JP3338182B2 (ja) * | 1994-02-28 | 2002-10-28 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JPH10303128A (ja) * | 1997-04-30 | 1998-11-13 | Fujitsu Ltd | 成膜方法 |

| JP4115589B2 (ja) * | 1997-10-17 | 2008-07-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP3027968B2 (ja) * | 1998-01-29 | 2000-04-04 | 日新電機株式会社 | 成膜装置 |

| JP3622492B2 (ja) * | 1998-03-30 | 2005-02-23 | セイコーエプソン株式会社 | 薄膜半導体装置の製造方法 |

| JPH11329970A (ja) * | 1998-05-18 | 1999-11-30 | Sharp Corp | 半導体装置の製造方法 |

-

2000

- 2000-01-07 JP JP2000002019A patent/JP4896286B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001196590A (ja) | 2001-07-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6170641B1 (ja) | 液晶表示装置 | |

| JP6062497B2 (ja) | 液晶表示装置 | |

| US6936844B1 (en) | Semiconductor device having a gate wiring comprising laminated wirings | |

| JP4583529B2 (ja) | 半導体装置およびその作製方法 | |

| JP4896314B2 (ja) | 表示装置 | |

| JP4651777B2 (ja) | 半導体装置の作製方法 | |

| JP4896286B2 (ja) | 半導体装置の作製方法 | |

| JP4850763B2 (ja) | 半導体装置の作製方法 | |

| JP2001210832A (ja) | 半導体装置及びその作製方法 | |

| JP4850326B2 (ja) | 半導体装置の作製方法 | |

| JP2001290171A (ja) | 半導体装置およびその作製方法 | |

| JP4776773B2 (ja) | 半導体装置の作製方法 | |

| JP2001338873A (ja) | 半導体装置の作製方法 | |

| JP4712156B2 (ja) | 半導体装置の作製方法 | |

| JP4641586B2 (ja) | 半導体装置の作製方法 | |

| JP4597295B2 (ja) | 半導体装置およびその作製方法 | |

| JP4472082B2 (ja) | 半導体装置の作製方法 | |

| JP4700159B2 (ja) | 半導体装置の作製方法 | |

| JP5159005B2 (ja) | 半導体装置の作製方法 | |

| JP2001274405A (ja) | 半導体装置およびその作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061226 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061226 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100120 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100126 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100205 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100302 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110329 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110510 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111115 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111129 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111220 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111221 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150106 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150106 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |