JP4875201B2 - 種々の電荷サンプリング回路 - Google Patents

種々の電荷サンプリング回路 Download PDFInfo

- Publication number

- JP4875201B2 JP4875201B2 JP2010274877A JP2010274877A JP4875201B2 JP 4875201 B2 JP4875201 B2 JP 4875201B2 JP 2010274877 A JP2010274877 A JP 2010274877A JP 2010274877 A JP2010274877 A JP 2010274877A JP 4875201 B2 JP4875201 B2 JP 4875201B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- input

- output

- bpcs

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000005070 sampling Methods 0.000 title claims abstract description 129

- 230000018199 S phase Effects 0.000 claims abstract description 6

- 230000004044 response Effects 0.000 claims description 44

- 239000003990 capacitor Substances 0.000 claims description 34

- 238000000034 method Methods 0.000 claims description 12

- 230000007423 decrease Effects 0.000 claims description 6

- 238000001914 filtration Methods 0.000 claims description 6

- 238000010586 diagram Methods 0.000 description 12

- 230000008569 process Effects 0.000 description 6

- 238000004088 simulation Methods 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 4

- 230000008901 benefit Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 230000002238 attenuated effect Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/0003—Software-defined radio [SDR] systems, i.e. systems wherein components typically implemented in hardware, e.g. filters or modulators/demodulators, are implented using software, e.g. by involving an AD or DA conversion stage such that at least part of the signal processing is performed in the digital domain

- H04B1/0007—Software-defined radio [SDR] systems, i.e. systems wherein components typically implemented in hardware, e.g. filters or modulators/demodulators, are implented using software, e.g. by involving an AD or DA conversion stage such that at least part of the signal processing is performed in the digital domain wherein the AD/DA conversion occurs at radiofrequency or intermediate frequency stage

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C27/00—Electric analogue stores, e.g. for storing instantaneous values

- G11C27/02—Sample-and-hold arrangements

- G11C27/024—Sample-and-hold arrangements using a capacitive memory element

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/06—Receivers

- H04B1/16—Circuits

- H04B1/26—Circuits for superheterodyne receivers

- H04B1/28—Circuits for superheterodyne receivers the receiver comprising at least one semiconductor device having three or more electrodes

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Analogue/Digital Conversion (AREA)

- Networks Using Active Elements (AREA)

- Peptides Or Proteins (AREA)

- Separation By Low-Temperature Treatments (AREA)

- Transition And Organic Metals Composition Catalysts For Addition Polymerization (AREA)

- Glass Compositions (AREA)

Description

Claims (15)

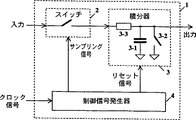

- 帯域通過電荷サンプリング(BPCS)回路(5)であって、信号制御発生器(7)を備え、差動アナログ信号の第1の端と第2の端を制御して、重みおよびサンプリング(W&S)段階で前記制御信号発生器(7)からのW&S信号に応じてW&S要素(6)で重みを付け、ここで前記アナログ信号の電流は前記W&S信号がW&S段階にあるときだけ前記W&S要素(6)を通過し、また前記制御信号発生器(7)は前記W&S段階で前記W&S要素(6)の出力信号を制御して積分器(3)で積分し、ここで前記W&S要素(6)の出力信号の電流を積分して積分電荷を生成して、前記W&S段階の終わりに比例電圧または電流サンプルを信号出力で生成することを特徴とする帯域通過電荷サンプリング(BPCS)回路(5)。

- 請求項1記載の帯域通過電荷サンプリング(BPCS)回路(5)であって、第1のスイッチ(2A)であって、前記差動アナログ信号の第1の端を受ける信号入力と、前記重みおよびサンプリング(W&S)要素(6)の信号入力に接続する信号出力と、前記制御信号発生器(7)のクロック出力に接続してクロック信号を受けるときだけ前記スイッチ(2A)を制御して導通させる制御入力とを有する第1のスイッチ(2A)と、第2のスイッチ(2B)であって、前記差動アナログ信号の第2の端を受ける信号入力と、前記重みおよびサンプリング(W&S)要素(6)の前記信号入力に接続する信号出力と、前記制御信号発生器(7)の反転クロック出力に接続してクロック信号を受けるときだけ前記スイッチ(2B)を制御して導通させる制御入力とを有する第2のスイッチ(2B)と、前記重みおよびサンプリング(W&S)要素(7)であって、前記制御信号発生器のW&S信号出力に接続する制御入力を有し、ここで前記アナログ信号の電流は前記W&S信号が前記クロックのnサイクルを含むW&S段階にあるときだけ前記W&S要素(6)を通過し、前記アナログ信号の電流は一定、直線、ガウスまたはその他の重み関数を持つ前記W&S信号により制御されるW&S要素(6)と、積分器であって、前記W&S要素(6)の出力に接続する信号入力と前記制御信号発生器(7)のリセット信号出力に接続する制御入力を持つ積分器と、を備えることを特徴とする帯域通過電荷サンプリング(BPCS)回路(5)。

- 請求項1又は2記載の帯域通過電荷サンプリング(BPCS)回路(5)であって、制御信号発生器(7)は積分器を制御して前記リセット信号が始まるリセット段階まで前記サンプルを保持することを特徴とする帯域通過電荷サンプリング(BPCS)回路(5)。

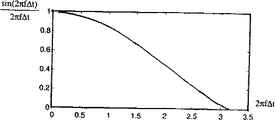

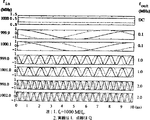

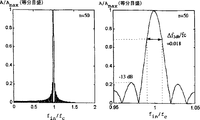

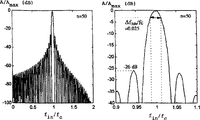

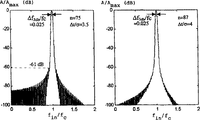

- 請求項1乃至3の何れか一項記載の帯域通過電荷サンプリング(BPCS)回路(5)であって、前記サンプルは前記アナログ信号のベースバンド内容を表し、前記出力周波数は2(p−1)fc≦fin≦pfcにおいてfout=|fin−(2p−1)fc|であり、ここでfinは前記アナログ信号の周波数成分の1つ、fcは前記クロックの周波数、pは整数で≧1であり、前記出力周波数の位相は前記finの位相とfcの位相に依存し、p=1は主周波数応答範囲を定義し、p>1では同じ形の周波数応答を繰り返すが振幅は減少し、所定のpでは(2p−1)fc−fin1=fin2−(2p−1)fcのとき周波数fin1(<(2p−1)fc)とfin2(>(2p−1)fc)において同じ出力周波数が得られるが位相は異なり、前記周波数応答の帯域幅と形は前記n(nが大きいほど帯域幅は狭い)と前記重み関数(一定、直線、ガウス、またはその他の関数)に依存し、前記BPCS回路は同時にフィルタとミクサとサンプラであることを特徴とする帯域通過電荷サンプリング(BPCS)回路(5)。

- 請求項1乃至4の何れか一項記載の第1および第2のBPCS回路を特徴とする差動帯域電荷サンプリング(BPCS)回路(8)であって、前記BPCSの全ての制御信号発生器を共通の制御信号発生器(7)に置き換え、前記第1のBPCS回路の第1信号入力と第2の信号入力を前記第1のBPCS回路の第2入力と第1入力にそれぞれ接続し、また第1の信号入力と、第2の信号入力と、前記第1のBPCS回路の信号出力と、前記第2のBPCS回路の信号出力は、前記差動帯域電荷サンプリング(BPCS)回路の第1の信号入力と、第2の信号入力と、第1の信号出力と、第2の信号出力である差動帯域電荷サンプリング(BPCS)回路(8)。

- 請求項5記載の差動帯域電荷サンプリング(BPCS)回路(8)であって、前記第1のBPCS回路と前記第2のBPCS回路内の積分器(3A,3B)を統合して単一の差動積分器(10)を形成して前記アナログ信号の差動電流を積分し、差動サンプルを前記差動BPCS回路の前記第1の信号出力と前記第2の信号出力で生成することを特徴とする差動帯域電荷サンプリング(BPCS)回路(8)。

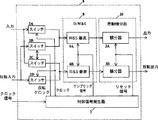

- 請求項1乃至4の何れか一項記載の多数のBPCS回路を備える並列BPCS回路(11)であって、全ての第1の信号入力をまとめて前記並列CS回路の第1のアナログ信号入力として接続して差動アナログ信号の第1の端を受け、全ての第2の信号入力をまとめて前記並列CS回路の第2のアナログ信号入力として接続して差動アナログ信号の第2の端を受け、全ての前記第1のスイッチを分離または統合し、全ての前記第2のスイッチを分離または統合し、前記BPCS回路内の全ての制御信号発生器を共通の制御信号発生器(13)に置き換え、マルチプレクサ(11)は前記BPCS回路の信号出力に接続する前記数の信号入力対と、前記共通の制御信号発生器の多重化信号出力に接続する制御入力と、信号出力とを有して、前記BPCS回路の信号出力が保持段階にあるとき前記BPCS回路の出力を多重化して前記信号出力に与え、ここで前記信号出力は前記並列BPCS回路の信号出力であり、また前記並列BPCS回路はサンプリング速度を高め、2連続サンプリング点の間の時間間隔を小さくし、前記並列BPCS回路は単一端回路であることを特徴とする並列BPCS回路(11)。

- 請求項5又は6記載の多数のBPCS回路を備える並列BPCS回路(11)であって、全ての第1の信号入力をまとめて前記並列BPCS回路の第1の信号入力として接続して差動アナログ信号の第1の端を受け、全ての第2の信号入力をまとめて前記並列BPCS回路の第2の信号入力として接続して差動アナログ信号の第2の端を受け、前記第1のBPCS回路内の全ての第1のスイッチを分離または統合し、前記第1のBPCS回路内の全ての第2のスイッチを分離または統合し、前記第2のBPCS回路内の全ての第1のスイッチを分離または統合し、前記第2のBPCS回路内の全ての第2のスイッチを分離または統合し、前記BPCS回路の全ての制御信号発生器を共通の制御信号発生器に置き換え、マルチプレクサは前記BPCS回路の信号出力対に接続する前記数の信号入力対と、前記共通の制御信号発生器の多重化信号出力に接続する制御入力と、出力対とを有して、前記BPCS回路の信号出力対が保持段階にあるとき前記BPCS回路の出力対を多重化して前記信号出力対に与え、ここで前記信号出力対は前記並列BPCS回路の信号出力対であり、また前記並列BPCS回路はサンプリング速度を高め、2連続サンプリング点の間の時間間隔を小さくし、ここで前記並列BPCS回路は差動回路であることを特徴とする並列BPCS回路(11)。

- 請求項7又は8記載の多数のBPCS回路を備える並列BPCS回路であって、制御信号発生器は、クロック入力と、クロック出力と、反転クロック出力と、前記数のW&S信号出力と、前記数のリセット信号出力と、前記数の多重化信号出力とを持ち、ここで前記クロック入力は前記並列BPCS回路のクロック入力であって、前記BPCS回路の全ての第1のスイッチの制御入力に接続する前記共通の信号制御発生器のクロック出力でクロック信号を生成し、また前記BPCS回路の全ての第2のスイッチの制御入力に接続する前記反転クロック出力の反転クロックを生成するのに用いられ、前記数のW&S信号出力は前記BPCS回路の全てのW&S要素(9A−9X)の制御入力に接続し、前記数のリセット信号出力は前記BPCS回路の全ての積分器(10A−10X)の制御入力に接続し、前記数の多重化信号とリセット信号とサンプリング信号と多重化信号とを均一に時間的に交互配置することを特徴とする並列BPCS回路。

- 請求項1乃至9の何れか一項記載の第1および第2のBPCS回路(39,42)を備える2ステップBPCS回路であって、

前記第1のBPCS回路(39)内の差動アナログ信号の第1の端と第2の端をそれぞれ受けて、前記第1のBPCS回路の信号出力または出力対で信号サンプルを第1のサンプリング速度で生成する第1の信号入力と第2の信号入力と、

前記第1のBPCS回路(39)からの信号を時間的に対称に前記第1のサンプリング速度に等しいクロック信号の周波数でその信号出力または出力対でチョッピングするチョッピング回路(40)と、

前記チョッピング回路からの信号を差動的にその信号出力対で増幅する差動出力増幅器(41)と、

を備え、

前記第2のBPCSの第1の信号入力と第2の信号入力は前記増幅器(41)の信号出力対に接続して、信号サンプルを第2のサンプリング速度で信号出力または出力対で生成することを特徴とする2ステップBPCS回路。 - 請求項10記載の2ステップBPCS回路であって、前記第1のBPCS回路(39)が用いる第1のクロック信号を受けるクロック入力を有し、また前記チョッピング回路のクロック入力と前記第2のBPCS回路のクロック入力に同時に与える第2のクロック信号を生成するクロック信号発生器(43)を備えることを特徴とする2ステップBPCS回路。

- 請求項1乃至11の何れか一項記載のBPCS回路のいずれかの種類におけるビルディング・ブロックの構成であって、

ドレンを信号入力とし、ゲートを制御入力とし、ソースを信号出力とする、n−MOSトランジスタを備える前記スイッチのn−MOS構成と、

ドレンを互いに接続して信号入力とし、ソースを互いに接続して信号出力とし、前記n−MOSトランジスタのゲートを制御入力とする、n−MOSトランジスタおよびp−MOSトランジスタと、入力を前記n−MOSトランジスタのゲートに接続し、出力を前記p−MOSトランジスタのゲートに接続するインバータと、を備える前記スイッチのCMOS構成と、

ドレンを信号入力とし、ゲートを制御入力とし、ソースを信号出力とするn−MOSトランジスタを備える前記W&S要素の構成と、

第1の端を信号入力とし、第2の端を接地するコンデンサと、必要に応じて前記信号入力と前記コンデンサの第1の端の間に挿入するオプションの抵抗器と、ドレンとソースを前記コンデンサの第1の端と第2の端にそれぞれ接続し、ゲートを制御入力とするn−MOSトランジスタと、を備える前記積分器の受動構成と、

信号入力と信号出力をそれぞれ前記差動積分器の第1の信号入力と第1の信号出力とする前記積分器の第1の受動構成と、信号入力と信号出力をそれぞれ前記差動積分器の第2の信号入力と第2の信号出力とする前記積分器の第2の受動構成と、を備える前記差動積分器の受動構成と、

正入力を接地し、負入力を前記積分器の信号入力とし、出力を前記積分器の信号出力とする差動入力単一出力増幅器と、第1の端を前記差動入力単一出力増幅器の負入力に接続するコンデンサと、入力を前記積分器の制御入力とするインバータと、信号入力を前記差動入力単一出力増幅器の負入力に接続し、制御入力を前記積分器の制御入力に接続し、信号出力を前記差動入力単一出力増幅器の出力に接続する前記スイッチの第1のn−MOSまたはCMOS構成と、信号入力を前記コンデンサの第2の端に接続し、制御入力を前記積分器の制御入力に接続し、信号出力を接地する前記スイッチの第2のn−MOSまたはCMOS構成と、信号入力を前記コンデンサの第2の端に接続し、制御入力を前記インバータの出力に接続し、信号出力を前記差動入力単一出力増幅器の出力に接続する前記スイッチの第3のn−MOSまたはCMOS構成と、必要に応じて前記積分器の信号入力と前記差動入力単一出力増幅器の負入力の間に挿入するオプションの抵抗器と、を備える前記積分器の能動構成と、

負入力と、正入力と、正出力と、負出力を前記差動積分器の第1の信号入力と、第2の信号入力と、第1の信号出力と、第2の信号出力とする差動入力差動出力増幅器と、第1の端を前記差動入力差動出力増幅器の負入力に接続する第1のコンデンサと、第1の端を前記差動入力差動出力増幅器の正入力に接続する第2のコンデンサと、入力を前記差動積分器の制御入力とするインバータと、信号入力を前記差動入力差動出力増幅器の負入力に接続し、制御入力を前記差動積分器の制御入力に接続し、信号出力を前記差動入力差動出力増幅器の正出力に接続する、前記スイッチの第1のn−MOS構成またはCMOS構成と、信号入力を前記第1のコンデンサの第2の端に接続し、制御入力を前記差動積分器の制御入力に接続し、信号出力を接地する前記スイッチの第2のn−MOS構成またはCMOS構成と、信号入力を前記第1のコンデンサの第2の端に接続し、制御入力を前記インバータの出力に接続し、信号出力を前記差動入力差動出力増幅器の正出力に接続する前記スイッチの第3のn−MOS構成またはCMOS構成と、信号入力を前記差動入力差動出力増幅器の正入力に接続し、制御入力を前記差動積分器の制御入力に接続し、信号出力を前記差動入力差動出力増幅器の負入力に接続する前記スイッチの第4のn−MOS構成またはCMOS構成と、信号入力を前記第2のコンデンサの第2の端に接続し、制御入力を前記差動積分器の制御入力に接続し、信号出力を接地する前記スイッチの第5のn−MOS構成またはCMOS構成と、信号入力を前記第2のコンデンサの第2の端に接続し、制御入力を前記インバータの出力に接続し、信号出力を前記差動入力差動出力増幅器の負出力に接続する前記スイッチの第6のn−MOS構成またはCMOS構成と、必要に応じて前記差動積分器の第1の信号入力と前記差動入力差動出力増幅器の負入力の間に挿入する第1のオプションの抵抗器と、必要に応じて前記差動積分器の第2の信号入力と前記差動入力差動出力増幅器の正入力の間に挿入する第2のオプションの抵抗器と、を備える前記差動積分器の能動構成と、

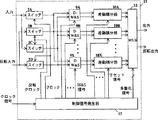

を備えることを特徴とするビルディング・ブロックの構成。 - 請求項1乃至11の何れか一項記載の第1および第2のBPCS回路を備えるフロントエンド・サンプリング無線受信装置であって、

前記クロック周波数の2倍以下の帯域幅を持ち、無線信号を受信して濾波する低域フィルタ(45)と、

差動的に増幅された無線信号を前記濾波された信号から生成する低雑音増幅器(46)と、

Iクロック信号をその信号出力に生成するローカル発振器(49)と、

信号入力を前記ローカル発振器(49)に接続して、前記Iクロック信号と同じ振幅でπ/2位相シフトしたQクロック信号をその信号出力に生成するπ/2移相器(48)と、

を備え、

前記低雑音増幅器(46)の信号出力対の2端を前記第1のBPCS回路(47A)と第2のBPCS回路(47B)にそれぞれ接続し、前記Iクロック信号出力を前記第1のBPCS回路(47A)のクロック入力に接続し、前記Qクロック信号出力を前記第2のBPCS回路(47B)のクロック入力に接続して、前記無線信号のベースバンドIサンプルを前記第1のBPCS回路(47A)の信号出力または出力対で生成し、前記無線信号のベースバンドQサンプルを前記第2のBPCS回路(47B)の信号出力または出力対で生成することを特徴とするフロントエンド・サンプリング無線受信装置。 - 請求項13記載のフロントエンド・サンプリング無線受信装置であって、

前記第1および第2のBPCS回路(47A,47B)の前記ローカル発振器(49)と前記移相器(48)と前記クロック発生器を組み合わせて、差動Iクロック信号およびQクロック信号を一層効果的にまた正確に生成し、

前記ベースバンドIサンプルおよびQサンプルを、2個の別個のアナログ・ディジタル変換器によりまたは単一の多重化アナログ・ディジタル変換器によりディジタル信号に変換し、

前記ディジタル信号をデジタル信号処理(DSP)ユニットで処理し、

前記フロントエンド・サンプリング無線受信装置は非常に簡単化されたアナログ部を有する優れたアナログ無線受信装置であり、またDSPの能力を高度に利用する、

ことを特徴とするフロントエンド・サンプリング無線受信装置。 - W&S段階で差動アナログ信号の第1の端と第2の端に重みを付け、前記W&S段階で重み付き信号を積分するステップであって、前記重み付き信号の電流が積分電荷として積分される、前記ステップと、

前記W&S段階の終わりに比例電圧または電流サンプルを生成するステップと、

を含むことを特徴とする電荷サンプリングの方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| SE9903532A SE9903532D0 (sv) | 1999-09-28 | 1999-09-28 | Versatile charge sampling circuits |

| SE9903532-1 | 1999-09-28 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001527292A Division JP4685310B2 (ja) | 1999-09-28 | 2000-09-25 | 種々の電荷サンプリング回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011103666A JP2011103666A (ja) | 2011-05-26 |

| JP4875201B2 true JP4875201B2 (ja) | 2012-02-15 |

Family

ID=20417207

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001527292A Expired - Fee Related JP4685310B2 (ja) | 1999-09-28 | 2000-09-25 | 種々の電荷サンプリング回路 |

| JP2010274877A Expired - Fee Related JP4875201B2 (ja) | 1999-09-28 | 2010-12-09 | 種々の電荷サンプリング回路 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001527292A Expired - Fee Related JP4685310B2 (ja) | 1999-09-28 | 2000-09-25 | 種々の電荷サンプリング回路 |

Country Status (9)

| Country | Link |

|---|---|

| US (3) | US7053673B1 (ja) |

| EP (2) | EP2228800A3 (ja) |

| JP (2) | JP4685310B2 (ja) |

| CN (2) | CN1174431C (ja) |

| AT (1) | ATE506677T1 (ja) |

| AU (1) | AU7820100A (ja) |

| DE (1) | DE60045867D1 (ja) |

| SE (1) | SE9903532D0 (ja) |

| WO (1) | WO2001024192A1 (ja) |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7239183B2 (en) | 2003-09-29 | 2007-07-03 | Nokia Corporation | Active current mode sampling circuit |

| JP5046622B2 (ja) | 2005-12-13 | 2012-10-10 | パナソニック株式会社 | サンプリングフィルタ装置 |

| US7671658B2 (en) | 2006-05-24 | 2010-03-02 | Panasonic Corporation | Mixer having frequency selection function |

| US8032094B2 (en) * | 2006-06-08 | 2011-10-04 | Panasonic Corporation | Discrete filter, sampling mixer, and radio device |

| JP2008017220A (ja) * | 2006-07-06 | 2008-01-24 | Sony Corp | チャージドメインフィルタ回路 |

| WO2008050630A1 (en) | 2006-10-23 | 2008-05-02 | Panasonic Corporation | Sampling filter device and radio communication device |

| FR2911449B1 (fr) * | 2007-01-16 | 2009-02-27 | Commissariat Energie Atomique | Filtre echantillonne a reponse impulsionnelle finie |

| US8385874B2 (en) | 2007-03-06 | 2013-02-26 | Panasonic Corporation | Discrete time direct sampling circuit and receiver |

| US8274418B2 (en) | 2007-05-18 | 2012-09-25 | Nokia Corporation | Analogue-to-digital converter |

| US8711917B2 (en) | 2008-01-16 | 2014-04-29 | Panasonic Corporation | Sampling filter device |

| EP2483891A2 (en) * | 2009-09-28 | 2012-08-08 | Arctic Silicon Devices As | Input configuration for analog to digital converter |

| FR2954628B1 (fr) | 2009-12-18 | 2012-02-24 | Commissariat Energie Atomique | Dispositif et procede de reception de signaux rf basee sur une architecture heterodyne a sous-echantillonnage if complexe |

| WO2012129271A1 (en) * | 2011-03-22 | 2012-09-27 | Ess Technology, Inc. | Finite impulse response filter for producing outputs having different phases |

| US9287851B2 (en) | 2011-03-22 | 2016-03-15 | Ess Technology, Inc. | Finite impulse response filter for producing outputs having different phases |

| ITFO20110009A1 (it) * | 2011-08-12 | 2013-02-13 | Marco Bennati | Apparato e metodo di riduzione del rumore in amplificatori a tempo campionato. |

| US20140049291A1 (en) | 2012-08-14 | 2014-02-20 | Luxen Technologies, Inc. | Noise-resistant sampling circuit and image sensor |

| CN107918443B (zh) * | 2016-10-11 | 2020-04-24 | 深圳市中兴微电子技术有限公司 | 一种信号生成方法和装置 |

| KR20230164443A (ko) * | 2022-05-25 | 2023-12-04 | 삼성전자주식회사 | 클락 발생 장치 및 클락 발생 장치를 포함하는 전자 장치 |

Family Cites Families (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| IT1186340B (it) * | 1985-10-29 | 1987-11-26 | Sgs Microelettronica Spa | Integratore differenziale a condensatore commutato utilizzante un unico condensatore di integrazione |

| JPS62145927A (ja) * | 1985-12-20 | 1987-06-30 | Hitachi Ltd | デ−タ変換装置 |

| IT1227615B (it) * | 1988-12-22 | 1991-04-22 | Sgs Thomson Microelectronics | Filtro completamente differenziale a condensatori commutati utilizzante amplificatori operazionali cmos senza retroazione di modo comune |

| US5128966A (en) * | 1989-02-15 | 1992-07-07 | Samsung Electronics Co., Ltd. | System for demodulating frequency- or phase-modulated signals by quadrature-phase |

| US5162670A (en) * | 1990-01-26 | 1992-11-10 | Kabushiki Kaisha Toshiba | Sample-and-hold circuit device |

| JP3337241B2 (ja) * | 1991-07-26 | 2002-10-21 | テキサス インスツルメンツ インコーポレイテツド | 改良型多重チャンネル・センサーインターフェース回路とその製造方法 |

| JPH06236698A (ja) * | 1993-02-10 | 1994-08-23 | Tamagawa Seiki Co Ltd | 正弦波のサンプル・ホールド方法及び回路 |

| DE69330490T2 (de) * | 1993-04-08 | 2002-04-25 | Lecroy S.A., Meyrin | Ladungsabtastschaltung |

| US5414311A (en) | 1993-09-14 | 1995-05-09 | Carnegie Mellon University | Sample and hold circuit and finite impulse response filter constructed therefrom |

| US5392043A (en) * | 1993-10-04 | 1995-02-21 | General Electric Company | Double-rate sampled signal integrator |

| US5617093A (en) * | 1994-09-30 | 1997-04-01 | Imp, Inc. | Switched capacitor analog circuits with low input capacitance |

| JP2708007B2 (ja) * | 1995-03-31 | 1998-02-04 | 日本電気株式会社 | サンプル・ホールド回路 |

| JPH0983588A (ja) * | 1995-09-18 | 1997-03-28 | Mitsubishi Electric Corp | 復調器及び変復調システム及び復調方法 |

| US5617063A (en) * | 1995-12-13 | 1997-04-01 | Pacific Communication Sciences, Inc. | Matched filters for processing related signal components |

| JP3392670B2 (ja) * | 1996-11-28 | 2003-03-31 | 株式会社東芝 | サンプリング装置 |

| DE69818327T2 (de) * | 1997-03-05 | 2004-07-01 | Nec Corp. | Direktmischempfänger zur Unterdrückung von Offset-Gleichspannungen |

| JPH1127569A (ja) * | 1997-07-01 | 1999-01-29 | Fuji Film Micro Device Kk | 信号サンプリング装置 |

| US5982315A (en) * | 1997-09-12 | 1999-11-09 | Qualcomm Incorporated | Multi-loop Σ Δ analog to digital converter |

| US6320459B2 (en) * | 1997-11-24 | 2001-11-20 | Mccullough Rob | Notch filter implemented using analog sampling |

| US6243430B1 (en) * | 1998-01-09 | 2001-06-05 | Qualcomm Incorporated | Noise cancellation circuit in a quadrature downconverter |

| JPH11234150A (ja) * | 1998-02-09 | 1999-08-27 | Toshiba Corp | デジタル復調装置 |

| FI120124B (fi) * | 1998-05-29 | 2009-06-30 | Nokia Corp | Menetelmä ja piiri signaalin näytteistämiseksi suurella näytteistystaajuudella |

| US6181748B1 (en) * | 1998-07-07 | 2001-01-30 | Macronix International Co. | Pulse shaper apparatus and method for ISDN U-interface |

| JP3568102B2 (ja) * | 1998-07-24 | 2004-09-22 | 松下電器産業株式会社 | 直接変換受信機 |

| US6157331A (en) * | 1998-10-01 | 2000-12-05 | Tritech Microelectronics, Ltd. | Sigma delta modulator with automatic saturation detection and recovery |

| US6246867B1 (en) * | 1998-11-17 | 2001-06-12 | Telefonaktiebolaget Lm Ericsson (Publ) | Method and apparatus for saving current while performing signal strength measurements in a homodyne receiver |

| US6366622B1 (en) * | 1998-12-18 | 2002-04-02 | Silicon Wave, Inc. | Apparatus and method for wireless communications |

| US6757340B1 (en) * | 1999-02-22 | 2004-06-29 | Telefonaktiebolaget L M Ericsson (Publ) | Radio receiver and method for preloading an average DC-offset into a channel filter |

| US6201835B1 (en) * | 1999-03-05 | 2001-03-13 | Burr-Brown Corporation | Frequency-shaped pseudo-random chopper stabilization circuit and method for delta-sigma modulator |

| US6943618B1 (en) * | 1999-05-13 | 2005-09-13 | Honeywell International Inc. | Compensation mechanism for compensating bias levels of an operation circuit in response to supply voltage changes |

-

1999

- 1999-09-28 SE SE9903532A patent/SE9903532D0/xx unknown

-

2000

- 2000-09-25 WO PCT/SE2000/001854 patent/WO2001024192A1/en not_active Ceased

- 2000-09-25 CN CNB008135592A patent/CN1174431C/zh not_active Expired - Fee Related

- 2000-09-25 CN CNA2004100598399A patent/CN1551505A/zh active Pending

- 2000-09-25 JP JP2001527292A patent/JP4685310B2/ja not_active Expired - Fee Related

- 2000-09-25 AT AT00968260T patent/ATE506677T1/de not_active IP Right Cessation

- 2000-09-25 AU AU78201/00A patent/AU7820100A/en not_active Abandoned

- 2000-09-25 EP EP10168098A patent/EP2228800A3/en not_active Withdrawn

- 2000-09-25 EP EP00968260A patent/EP1221166B1/en not_active Expired - Lifetime

- 2000-09-25 DE DE60045867T patent/DE60045867D1/de not_active Expired - Lifetime

- 2000-09-28 US US09/672,803 patent/US7053673B1/en not_active Expired - Fee Related

-

2005

- 2005-04-06 US US11/099,488 patent/US7023245B2/en not_active Expired - Fee Related

- 2005-04-06 US US11/099,460 patent/US8035421B2/en not_active Expired - Fee Related

-

2010

- 2010-12-09 JP JP2010274877A patent/JP4875201B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7023245B2 (en) | 2006-04-04 |

| US20050168371A1 (en) | 2005-08-04 |

| CN1174431C (zh) | 2004-11-03 |

| CN1377504A (zh) | 2002-10-30 |

| EP1221166A1 (en) | 2002-07-10 |

| ATE506677T1 (de) | 2011-05-15 |

| DE60045867D1 (de) | 2011-06-01 |

| US7053673B1 (en) | 2006-05-30 |

| JP4685310B2 (ja) | 2011-05-18 |

| JP2011103666A (ja) | 2011-05-26 |

| EP2228800A3 (en) | 2010-09-29 |

| CN1551505A (zh) | 2004-12-01 |

| US20050176397A1 (en) | 2005-08-11 |

| EP2228800A2 (en) | 2010-09-15 |

| JP2003510933A (ja) | 2003-03-18 |

| EP1221166B1 (en) | 2011-04-20 |

| WO2001024192A1 (en) | 2001-04-05 |

| AU7820100A (en) | 2001-04-30 |

| SE9903532D0 (sv) | 1999-09-28 |

| US8035421B2 (en) | 2011-10-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4875201B2 (ja) | 種々の電荷サンプリング回路 | |

| Yuan | A charge sampling mixer with embedded filter function for wireless applications | |

| Song | A fourth-order bandpass delta-sigma modulator with reduced numbers of op amps | |

| US8279023B2 (en) | Filter circuit and communication device | |

| US20060261875A1 (en) | Mixer circuit, receiver comprising a mixer circuit method for generating an output signal by mixing an input signal with an oscillator signal | |

| Karvonen et al. | A quadrature charge-domain sampler with embedded FIR and IIR filtering functions | |

| EP1668647B1 (en) | Active current mode sampling circuit | |

| JPH0211172B2 (ja) | ||

| CA1233890A (en) | Decimating filter | |

| US20100179977A1 (en) | Sampled filter with finite impulse response | |

| Pun et al. | Quadrature sampling schemes with improved image rejection | |

| US20070008208A1 (en) | Filter with gain | |

| Song | A narrow-band CMOS FM receiver based on single-sideband modulation IF filtering | |

| US7483684B2 (en) | Mixer | |

| Karvonen et al. | A Hilbert sampler/filter and complex bandpass SC filter for I/Q demodulation | |

| Levantino et al. | A CMOS GSM IF-sampling circuit with reduced in-channel aliasing | |

| US7671780B2 (en) | Method and device for processing an incident signal, in particular for frequency transposition | |

| Quinn | High-accuracy charge-redistribution switched-capacitor video bandpass filter in standard 0.8 µm CMOS | |

| Yim et al. | A 200-MHz CMOS I/Q downconverter | |

| Takahashi et al. | A voice band Hilbert transformer using switched capacitor technology | |

| Ng et al. | A 28-MHz wide-band switched-capacitor bandpass filter with high attenuation | |

| Pun et al. | Polyphase SC IIR Hubert transformer with reduced sensitivity to finite gain and bandwidth | |

| Hebenstreit et al. | Push-Pull Accumulator using Switched Capacttors | |

| Sekiguchi et al. | Parasitic‐insensitive switched‐capacitor all‐pass filters having low amplitude sensitivity |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111111 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111124 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141202 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |