JP4871948B2 - 仮想計算機システム、仮想計算機システムにおけるハイパバイザ、及び仮想計算機システムにおけるスケジューリング方法 - Google Patents

仮想計算機システム、仮想計算機システムにおけるハイパバイザ、及び仮想計算機システムにおけるスケジューリング方法 Download PDFInfo

- Publication number

- JP4871948B2 JP4871948B2 JP2008306964A JP2008306964A JP4871948B2 JP 4871948 B2 JP4871948 B2 JP 4871948B2 JP 2008306964 A JP2008306964 A JP 2008306964A JP 2008306964 A JP2008306964 A JP 2008306964A JP 4871948 B2 JP4871948 B2 JP 4871948B2

- Authority

- JP

- Japan

- Prior art keywords

- cpu

- logical

- virtual machine

- physical

- context

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 342

- 230000008569 process Effects 0.000 claims description 324

- 230000015654 memory Effects 0.000 claims description 76

- 238000004886 process control Methods 0.000 claims description 14

- 238000012545 processing Methods 0.000 description 42

- 238000011084 recovery Methods 0.000 description 33

- 230000006870 function Effects 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- 230000003111 delayed effect Effects 0.000 description 3

- 238000003672 processing method Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000003044 adaptive effect Effects 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/455—Emulation; Interpretation; Software simulation, e.g. virtualisation or emulation of application or operating system execution engines

- G06F9/45533—Hypervisors; Virtual machine monitors

- G06F9/45558—Hypervisor-specific management and integration aspects

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/54—Interprogram communication

- G06F9/544—Buffers; Shared memory; Pipes

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/455—Emulation; Interpretation; Software simulation, e.g. virtualisation or emulation of application or operating system execution engines

- G06F9/45533—Hypervisors; Virtual machine monitors

- G06F9/45558—Hypervisor-specific management and integration aspects

- G06F2009/4557—Distribution of virtual machine instances; Migration and load balancing

Description

スケジューリング制御テーブルから切り替え元のプロセス情報800−1を取得し、切り替え元プロセスのプロセスの識別情報710−1から、論理CPUプロセスかどうかを判定する。具体的には、プロセス識別情報710−1はそのプロセスの種類を一意に特定できるためのIDを含んでおり、これが論理CPUを示しているかどうか確認する。

まず、切り替え先プロセスのプロセスの識別情報710−1から、論理CPUプロセスかどうかを判定する。(1)の最初の動作と同じである。

切り替え先のプロセスが論理CPUプロセスである場合、当該物理CPUのスケジューリング制御テーブル800の前回論理CPUプロセス情報800−2を、切り替え先プロセスに更新する。

110,210,310 ゲストオペレーティングシステム(OS)

120,121,220,221,320,321 論理CPU

130,230,330 VM用メモリ

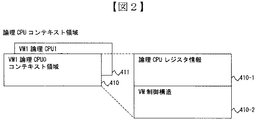

400 VMM制御用のメモリ領域

410,411,420,421,430,431 論理CPUコンテキスト格納用領域

410−1 論理CPUのレジスタ情報

410−2 論理CPUのVM制御構造

500 仮想マシンモニタ(VMM)

510 プロセス制御ブロック

520 スケジューリング制御テーブル

530 プロセススケジューリング処理

600,601,602,603 物理CPU

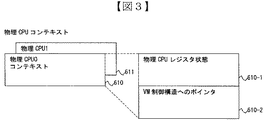

610,611,612,613 物理CPUコンテキスト

610−1 物理CPUレジスタ状態

610−2 VM制御構造へのポインタ

620,621,622 物理CPU内部メモリ

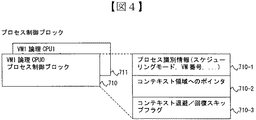

710,711,720,721,730,731,740,741,742 各プロセス制御ブロック

710−1 プロセス識別情報

710−2 コンテキスト格納領域へのポインタ

710−3 コンテキスト退避/回復スキップフラグ

800,801,802,803 各スケジューリング制御テーブル

810−1 当該物理CPUで現在走行中のプロセス

810−2 当該物理CPUで最後に走行した論理CPUプロセス

Claims (5)

- 物理CPUと、前記物理CPUを論理的に分割して複数の仮想計算機とする仮想計算機制御部と、前記仮想計算機制御部が前記仮想計算機の制御に使用する仮想計算機制御メモリとを備える仮想計算機システムにおいて、

前記仮想計算機は、前記複数の仮想計算機が前記物理CPUを共有するCPU共有モードと、前記複数の仮想計算機のうちの特定の仮想計算機が前記物理CPUを占有するCPU占有モードとを有し、

前記物理CPUは、動作中のプロセスに対応づけられた物理コンテキストを格納する内部メモリを有し、

前記仮想計算機制御メモリは、前記物理コンテキストと対応づけられた論理コンテキスト領域を有し、

前記プロセスは、前記仮想計算機の論理CPUのプロセスである第1の論理CPUプロセス、前記仮想計算機制御部用の仮想計算機の論理CPUのプロセスである第2の論理CPUプロセス、及び前記仮想計算機制御部の制御プロセスのうち何れか1つであり、

前記仮想計算機制御部は、前記仮想計算機のプロセス切り替え時における前記論理コンテキスト領域への前記物理コンテキストの退避動作を管理するプロセス制御ブロックを有し、

前記仮想計算機制御部が、次のプロセスとして前記制御プロセスを選択すると、

前記物理CPUで動作中のプロセスが前記第1の論理CPUプロセス及び前記第2の論理CPUプロセスのいずれであるかを判定し、

前記判定により、前記動作中のプロセスが前記CPU占有モードの第1の論理CPUプロセスである場合、前記仮想計算機制御部が、動作中のプロセスに対応づけられた物理コンテキストの退避を保留する前記プロセス制御ブロックの保留フラグをオンにし、

前記判定により、前記動作中のプロセスが前記CPU共有モードの第1の論理CPUプロセスである場合、前記仮想計算機制御部が、前記動作中のプロセスに対応づけられた物理コンテキストの退避を保留する前記プロセス制御ブロックの保留フラグをオフにし、

前記CPU共有モードの第1の論理CPUプロセスに対応づけられた物理コンテキストを、対応する前記論理コンテキスト領域に退避させ、

前記判定により、前記動作中のプロセスが前記第2の論理CPUプロセスである場合、前記仮想計算機制御部が、前記動作中のプロセスに対応づけられた物理コンテキストの退避を保留する前記プロセス制御ブロックの保留フラグをオフにし、

前記第2の論理CPUプロセスに対応づけられた物理コンテキストを、対応する前記論理コンテキスト領域に退避させ、

前記仮想計算機制御部が、前記制御プロセスの次のプロセスとして前記第1の論理CPUプロセスを選択すると、前記仮想計算機制御部は、前記制御プロセスの前に動作した論理CPUプロセスにおける前記保留フラグを参照し、

前記参照した保留フラグがオンである場合、前記物理CPUは、退避を保留した前記内部メモリの前記物理コンテキストを参照して、前記CPU占有モードの第1の論理CPUプロセスを実行し、前記仮想計算機制御部が前記参照した保留フラグをオフにし、

前記参照した保留フラグがオフである場合、前記仮想計算機制御部は、前記論理コンテキスト領域から前記CPU共有モードの第1の論理CPUプロセスに対応する物理コンテキストを前記内部メモリに復元し、

前記物理CPUは、前記復元した前記CPU共有モードの第1の論理CPUプロセスに対応する物理コンテキストを参照して、前記CPU共有モードの第1の論理CPUプロセスを実行し、

前記仮想計算機制御部が、前記制御プロセスの次のプロセスとして前記第2の論理CPUプロセスを選択すると、前記仮想計算機制御部は、前記制御プロセスの前に動作した論理CPUプロセスにおける前記保留フラグを参照し、

前記参照した保留フラグがオンである場合、退避を保留した前記内部メモリの前記物理コンテキストを、対応する前記論理コンテキスト領域に退避し、前記参照した保留フラグをオフにし、

前記仮想計算機制御部は、前記論理コンテキスト領域から前記第2の論理CPUプロセスに対応する物理コンテキストを前記内部メモリに復元し、

前記物理CPUは、前記復元した第2の論理CPUプロセスに対応する物理コンテキストを参照して、前記第2の論理CPUプロセスを実行し、

前記参照した保留フラグがオフである場合、

前記仮想計算機制御部は、前記論理コンテキスト領域から前記第2の論理CPUプロセスに対応する物理コンテキストを前記内部メモリに復元し、

前記物理CPUは、前記復元した第2の論理CPUプロセスに対応する物理コンテキストを参照して、前記第2の論理CPUプロセスを実行する

ことを特徴とする仮想計算機システム。 - 前記仮想計算機制御部が、前記第2の論理CPUプロセスの次のプロセスとして、前記第1の論理CPUプロセスを選択すると、

前記仮想計算機制御部は、前記論理コンテキスト領域に退避した前記物理コンテキストを、前記内部メモリに復元し、

前記物理CPUは、復元された前記内部メモリの前記物理コンテキストを参照して、前記第1の論理CPUプロセスを実行すること

を特徴とする請求項1記載の仮想計算機システム。 - 前記物理コンテキストは、物理CPUレジスタ状態情報と、仮想計算機制御構造へのポインタ情報とを有し、

前記論理コンテキスト領域は、前記物理CPUレジスタ状態情報に対応する論理CPUレジスタ情報と、前記仮想計算機制御構造へのポインタ情報に対応する仮想計算機制御構造情報とを有することを特徴とする請求項1記載の仮想計算機システム。 - 物理CPUと、前記物理CPUを論理的に分割して複数の仮想計算機とする仮想計算機制御部と、前記仮想計算機制御部が前記仮想計算機の制御に使用する仮想計算機制御メモリとを備える仮想計算機システムにおける仮想計算機制御部であって、

前記仮想計算機は、前記複数の仮想計算機が前記物理CPUを共有するCPU共有モードと、前記複数の仮想計算機のうちの特定の仮想計算機が前記物理CPUを占有するCPU占有モードとを有し、

前記物理CPUは、動作中のプロセスに対応づけられた物理コンテキストを格納する内部メモリを有し、

前記仮想計算機制御メモリは、前記物理コンテキストと対応づけられた論理コンテキスト領域を有し、

前記プロセスは、前記仮想計算機の論理CPUのプロセスである第1の論理CPUプロセス、前記仮想計算機制御部用の仮想計算機の論理CPUのプロセスである第2の論理CPUプロセス、及び前記仮想計算機制御部の制御プロセスのうち何れか1つであり、

前記仮想計算機制御部は、

前記仮想計算機のプロセス切り替え時における前記論理コンテキスト領域への前記物理コンテキストの退避動作を管理するプロセス制御ブロックを有し、

次のプロセスとして前記制御プロセスを選択すると、

前記物理CPUで動作中のプロセスが前記第1の論理CPUプロセス及び前記第2の論理CPUプロセスのいずれであるかを判定し、

前記判定により、前記動作中のプロセスが前記CPU占有モードの第1の論理CPUプロセスである場合、前記仮想計算機制御部が、動作中のプロセスに対応づけられた物理コンテキストの退避を保留する前記プロセス制御ブロックの保留フラグをオンにし、

前記判定により、前記動作中のプロセスが前記CPU共有モードの第1の論理CPUプロセスである場合、前記仮想計算機制御部が、前記動作中のプロセスに対応づけられた物理コンテキストの退避を保留する前記プロセス制御ブロックの保留フラグをオフにし、

前記CPU共有モードの第1の論理CPUプロセスに対応づけられた物理コンテキストを、対応する前記論理コンテキスト領域に退避させ、

前記判定により、前記動作中のプロセスが前記第2の論理CPUプロセスである場合、前記仮想計算機制御部が、前記動作中のプロセスに対応づけられた物理コンテキストの退避を保留する前記プロセス制御ブロックの保留フラグをオフにし、

前記第2の論理CPUプロセスに対応づけられた物理コンテキストを、対応する前記論理コンテキスト領域に退避させ、

前記仮想計算機制御部は、

前記制御プロセスの次のプロセスとして前記第1の論理CPUプロセスを選択すると、前記制御プロセスの前に動作した論理CPUプロセスにおける前記保留フラグを参照し、

前記参照した保留フラグがオンである場合、前記物理CPUにより、退避を保留した前記内部メモリの前記物理コンテキストを参照して、前記CPU占有モードの第1の論理CPUプロセスが実行され、前記仮想計算機制御部が前記参照した保留フラグをオフにし、

前記参照した保留フラグがオフである場合、前記論理コンテキスト領域から前記CPU共有モードの第1の論理CPUプロセスに対応する物理コンテキストを前記内部メモリに復元し、

前記物理CPUにより、前記復元した前記CPU共有モードの第1の論理CPUプロセスに対応する物理コンテキストを参照して、前記CPU共有モードの第1の論理CPUプロセスが実行され、

前記制御プロセスの次のプロセスとして前記第2の論理CPUプロセスを選択すると、前記制御プロセスの前に動作した論理CPUプロセスにおける前記保留フラグを参照し、

前記参照した保留フラグがオンである場合、退避を保留した前記内部メモリの前記物理コンテキストを、対応する前記論理コンテキスト領域に退避し、前記参照した保留フラグをオフにし、

前記論理コンテキスト領域から前記第2の論理CPUプロセスに対応する物理コンテキストを前記内部メモリに復元し、

前記物理CPUにより、前記復元した第2の論理CPUプロセスに対応する物理コンテキストを参照して、前記第2の論理CPUプロセスが実行され、

前記参照した保留フラグがオフである場合、

前記論理コンテキスト領域から前記第2の論理CPUプロセスに対応する物理コンテキストを前記内部メモリに復元し、

前記物理CPUにより、前記復元した第2の論理CPUプロセスに対応する物理コンテキストを参照して、前記第2の論理CPUプロセスが実行される

ことを特徴とする仮想計算機制御部。 - 物理CPUと、前記物理CPUを論理的に分割して複数の仮想計算機とする仮想計算機制御部と、前記仮想計算機制御部が前記仮想計算機の制御に使用する仮想計算機制御メモリとを備える仮想計算機システムにおけるスケジューリング方法であって、

前記仮想計算機は、前記複数の仮想計算機が前記物理CPUを共有するCPU共有モードと、前記複数の仮想計算機のうちの特定の仮想計算機が前記物理CPUを占有するCPU占有モードとを有し、

前記物理CPUは、動作中のプロセスに対応づけられた物理コンテキストを格納する内部メモリを有し、

前記仮想計算機制御メモリは、前記物理コンテキストと対応づけられた論理コンテキスト領域を有し、

前記プロセスは、前記仮想計算機の論理CPUのプロセスである第1の論理CPUプロセス、前記仮想計算機制御部用の仮想計算機の論理CPUのプロセスである第2の論理CPUプロセス、及び前記仮想計算機制御部の制御プロセスのうち何れか1つであり、

前記仮想計算機制御部は、前記仮想計算機のプロセス切り替え時における前記論理コンテキスト領域への前記物理コンテキストの退避動作を管理するプロセス制御ブロックを有し、

前記仮想計算機制御部が、次のプロセスとして前記制御プロセスを選択すると、

前記物理CPUで動作中のプロセスが前記第1の論理CPUプロセス及び前記第2の論理CPUプロセスのいずれであるかを判定し、

前記判定により、前記動作中のプロセスが前記CPU占有モードの第1の論理CPUプロセスである場合、前記仮想計算機制御部が、動作中のプロセスに対応づけられた物理コンテキストの退避を保留する前記プロセス制御ブロックの保留フラグをオンにし、

前記判定により、前記動作中のプロセスが前記CPU共有モードの第1の論理CPUプロセスである場合、前記仮想計算機制御部が、前記動作中のプロセスに対応づけられた物理コンテキストの退避を保留する前記プロセス制御ブロックの保留フラグをオフにし、

前記CPU共有モードの第1の論理CPUプロセスに対応づけられた物理コンテキストを、対応する前記論理コンテキスト領域に退避させ、

前記判定により、前記動作中のプロセスが前記第2の論理CPUプロセスである場合、前記仮想計算機制御部が、前記動作中のプロセスに対応づけられた物理コンテキストの退避を保留する前記プロセス制御ブロックの保留フラグをオフにし、

前記第2の論理CPUプロセスに対応づけられた物理コンテキストを、対応する前記論理コンテキスト領域に退避させ、

前記仮想計算機制御部が、前記制御プロセスの次のプロセスとして前記第1の論理CPUプロセスを選択すると、前記仮想計算機制御部は、前記制御プロセスの前に動作した論理CPUプロセスにおける前記保留フラグを参照し、

前記参照した保留フラグがオンである場合、前記物理CPUは、退避を保留した前記内部メモリの前記物理コンテキストを参照して、前記CPU占有モードの第1の論理CPUプロセスを実行し、前記仮想計算機制御部が前記参照した保留フラグをオフにし、

前記参照した保留フラグがオフである場合、前記仮想計算機制御部は、前記論理コンテキスト領域から前記CPU共有モードの第1の論理CPUプロセスに対応する物理コンテキストを前記内部メモリに復元し、

前記物理CPUは、前記復元した前記CPU共有モードの第1の論理CPUプロセスに対応する物理コンテキストを参照して、前記CPU共有モードの第1の論理CPUプロセスを実行し、

前記仮想計算機制御部が、前記制御プロセスの次のプロセスとして前記第2の論理CPUプロセスを選択すると、前記仮想計算機制御部は、前記制御プロセスの前に動作した論理CPUプロセスにおける前記保留フラグを参照し、

前記参照した保留フラグがオンである場合、退避を保留した前記内部メモリの前記物理コンテキストを、対応する前記論理コンテキスト領域に退避し、前記参照した保留フラグをオフにし、

前記仮想計算機制御部は、前記論理コンテキスト領域から前記第2の論理CPUプロセスに対応する物理コンテキストを前記内部メモリに復元し、

前記物理CPUは、前記復元した第2の論理CPUプロセスに対応する物理コンテキストを参照して、前記第2の論理CPUプロセスを実行し、

前記参照した保留フラグがオフである場合、

前記仮想計算機制御部は、前記論理コンテキスト領域から前記第2の論理CPUプロセスに対応する物理コンテキストを前記内部メモリに復元し、

前記物理CPUは、前記復元した第2の論理CPUプロセスに対応する物理コンテキストを参照して、前記第2の論理CPUプロセスを実行する

ことを特徴とするスケジューリング方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008306964A JP4871948B2 (ja) | 2008-12-02 | 2008-12-02 | 仮想計算機システム、仮想計算機システムにおけるハイパバイザ、及び仮想計算機システムにおけるスケジューリング方法 |

| US12/628,342 US8266629B2 (en) | 2008-12-02 | 2009-12-01 | Virtual machine system, hypervisor in virtual machine system, and scheduling method in virtual machine system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008306964A JP4871948B2 (ja) | 2008-12-02 | 2008-12-02 | 仮想計算機システム、仮想計算機システムにおけるハイパバイザ、及び仮想計算機システムにおけるスケジューリング方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010134496A JP2010134496A (ja) | 2010-06-17 |

| JP2010134496A5 JP2010134496A5 (ja) | 2010-12-09 |

| JP4871948B2 true JP4871948B2 (ja) | 2012-02-08 |

Family

ID=42223944

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008306964A Expired - Fee Related JP4871948B2 (ja) | 2008-12-02 | 2008-12-02 | 仮想計算機システム、仮想計算機システムにおけるハイパバイザ、及び仮想計算機システムにおけるスケジューリング方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8266629B2 (ja) |

| JP (1) | JP4871948B2 (ja) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20130061231A1 (en) * | 2010-05-11 | 2013-03-07 | Dong-Qing Zhang | Configurable computing architecture |

| US8812400B2 (en) * | 2010-07-09 | 2014-08-19 | Hewlett-Packard Development Company, L.P. | Managing a memory segment using a memory virtual appliance |

| JP5758914B2 (ja) * | 2010-12-21 | 2015-08-05 | パナソニック インテレクチュアル プロパティ コーポレーション オブアメリカPanasonic Intellectual Property Corporation of America | 仮想計算機システム及び仮想計算機システム制御方法 |

| KR101773166B1 (ko) | 2011-02-21 | 2017-08-30 | 삼성전자주식회사 | 가상 머신 스케줄 시점 조절 장치 및 방법 |

| US8555279B2 (en) * | 2011-04-25 | 2013-10-08 | Hitachi, Ltd. | Resource allocation for controller boards management functionalities in a storage management system with a plurality of controller boards, each controller board includes plurality of virtual machines with fixed local shared memory, fixed remote shared memory, and dynamic memory regions |

| US8793535B2 (en) | 2011-07-21 | 2014-07-29 | Microsoft Corporation | Optimizing system usage when running quality tests in a virtual machine environment |

| US9459898B2 (en) * | 2011-10-06 | 2016-10-04 | Hitachi, Ltd. | Virtual server processing control method, system, and virtual server processing control management server |

| JP5936041B2 (ja) * | 2012-03-07 | 2016-06-15 | 日本電気株式会社 | マルチプロセッサ装置、スケジューリング方法、および、スケジューリングプログラム |

| CN102750178B (zh) | 2012-06-08 | 2015-04-29 | 华为技术有限公司 | 通信设备硬件资源的虚拟化管理方法及相关装置 |

| US9569223B2 (en) * | 2013-02-13 | 2017-02-14 | Red Hat Israel, Ltd. | Mixed shared/non-shared memory transport for virtual machines |

| JP6126311B2 (ja) * | 2013-08-26 | 2017-05-10 | ヴイエムウェア インコーポレイテッドVMware,Inc. | 待ち時間の影響を受けやすい仮想マシンをサポートするように構成されるcpuスケジューラ |

| CN103699433B (zh) * | 2013-12-18 | 2017-07-14 | 中国科学院计算技术研究所 | 一种于Hadoop平台中动态调整任务数目的方法及系统 |

| CN103729252B (zh) * | 2013-12-20 | 2017-09-05 | 杭州华为数字技术有限公司 | 一种虚拟机调度的方法及调度监控器 |

| US9772867B2 (en) * | 2014-03-27 | 2017-09-26 | International Business Machines Corporation | Control area for managing multiple threads in a computer |

| JP6158751B2 (ja) * | 2014-05-30 | 2017-07-05 | 日本電信電話株式会社 | 計算機資源割当装置及び計算機資源割当プログラム |

| CN104035811B (zh) * | 2014-07-01 | 2017-07-28 | 龙芯中科技术有限公司 | 虚拟机现场数据的处理方法和装置 |

| US10127068B2 (en) * | 2016-06-30 | 2018-11-13 | Amazon Technologies, Inc. | Performance variability reduction using an opportunistic hypervisor |

| CN108984267B (zh) | 2018-07-09 | 2020-11-13 | 北京东土科技股份有限公司 | 工业服务器的微内核架构控制系统及工业服务器 |

| US20210357267A1 (en) * | 2020-05-15 | 2021-11-18 | Unisys Corporation | Defining and accessing dynamic registers in a virtual multi-processor system |

| CN111738710B (zh) * | 2020-07-23 | 2020-12-01 | 支付宝(杭州)信息技术有限公司 | 对智能合约的执行进行资源扣除的方法和处理器 |

| US20220283838A1 (en) * | 2021-03-08 | 2022-09-08 | Unisys Corporation | System and method enabling software-controlled processor customization for workload optimization |

| US11663010B2 (en) * | 2021-03-08 | 2023-05-30 | Unisys Corporation | System and method for securely debugging across multiple execution contexts |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6159539A (ja) * | 1984-08-30 | 1986-03-27 | Nec Corp | サブプロセツサのレジスタ退避/復帰方式 |

| JPH02123426A (ja) * | 1988-11-02 | 1990-05-10 | Mitsubishi Electric Corp | マイクロプロセッサ |

| JPH02173828A (ja) * | 1988-12-27 | 1990-07-05 | Nec Corp | 割込み処理方式 |

| US5452452A (en) * | 1990-06-11 | 1995-09-19 | Cray Research, Inc. | System having integrated dispatcher for self scheduling processors to execute multiple types of processes |

| JPH0451329A (ja) * | 1990-06-19 | 1992-02-19 | Nec Corp | コンテキスト切替装置 |

| JPH04155533A (ja) * | 1990-10-19 | 1992-05-28 | Fujitsu Ltd | 仮想計算機制御方式 |

| JP3644042B2 (ja) | 1993-11-15 | 2005-04-27 | ソニー株式会社 | マルチタスク処理装置 |

| JP2001282558A (ja) | 2000-03-30 | 2001-10-12 | Hitachi Ltd | マルチオペレーティング計算機システム |

| US7117319B2 (en) * | 2002-12-05 | 2006-10-03 | International Business Machines Corporation | Managing processor architected state upon an interrupt |

| US7500244B2 (en) * | 2004-06-30 | 2009-03-03 | Intel Corporation | Adaptive algorithm for selecting a virtualization algorithm in virtual machine environments |

| US7937710B1 (en) * | 2005-11-22 | 2011-05-03 | Nvidia Corporation | Context switch signaling method and system |

-

2008

- 2008-12-02 JP JP2008306964A patent/JP4871948B2/ja not_active Expired - Fee Related

-

2009

- 2009-12-01 US US12/628,342 patent/US8266629B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010134496A (ja) | 2010-06-17 |

| US8266629B2 (en) | 2012-09-11 |

| US20100138831A1 (en) | 2010-06-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4871948B2 (ja) | 仮想計算機システム、仮想計算機システムにおけるハイパバイザ、及び仮想計算機システムにおけるスケジューリング方法 | |

| JP5405320B2 (ja) | 仮想計算機制御装置、仮想計算機制御方法及び仮想計算機制御プログラム | |

| JP5655677B2 (ja) | ハイパーバイザ置き換え方法および情報処理装置 | |

| KR100893527B1 (ko) | 재구성 가능 멀티 프로세서 시스템에서의 매핑 및 스케줄링방법 | |

| US20060150194A1 (en) | Methods and apparatuses to maintain multiple execution contexts | |

| US20120188263A1 (en) | Method and system to dynamically bind and unbind applications on a general purpose graphics processing unit | |

| US9563466B2 (en) | Method and apparatus for supporting programmable software context state execution during hardware context restore flow | |

| WO2007099483A2 (en) | Method and apparatus for dynamic resizing of cache partitions based on the execution phase of tasks | |

| JP2017037370A (ja) | 計算機、プロセス制御方法およびプロセス制御プログラム | |

| US20130347000A1 (en) | Computer, virtualization mechanism, and scheduling method | |

| EP3846028A1 (en) | Method and device for resuming execution of application, and computer | |

| WO2011020281A1 (zh) | 一种高效的内存池访问方法 | |

| JP2009157684A (ja) | 仮想化プログラム、シミュレーション装置、仮想化方法 | |

| US20190236017A1 (en) | Method and system for efficient communication and command system for deferred operation | |

| JP2009223842A (ja) | 仮想計算機制御プログラム及び仮想計算機システム | |

| JP2006092042A (ja) | 情報処理装置及びコンテキスト切り替え方法 | |

| JPWO2008114415A1 (ja) | マルチプロセッシングシステム | |

| US11860785B2 (en) | Method and system for efficient communication and command system for deferred operation | |

| JP4006428B2 (ja) | 計算機システム | |

| JP7196439B2 (ja) | 仮想化環境におけるデバイスへのアクセス方法 | |

| JP4207775B2 (ja) | 計算機システムの凍結・解凍プログラム、その記録媒体、及び計算機システムの凍結・解凍方法 | |

| JP2022055002A (ja) | 情報処理装置、情報処理方法および情報処理プログラム | |

| JP2004021610A (ja) | タスク管理装置 | |

| JPS63197239A (ja) | 仮想プロセツサ制御情報退避格納方式 | |

| JP2018151968A (ja) | 管理装置、分散システム、管理方法、及びプログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101021 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101021 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110204 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110308 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110506 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110524 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110721 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110816 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110929 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111025 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111121 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4871948 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141125 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |