JP4819552B2 - サンプリング装置、それを用いた表示装置 - Google Patents

サンプリング装置、それを用いた表示装置 Download PDFInfo

- Publication number

- JP4819552B2 JP4819552B2 JP2006098350A JP2006098350A JP4819552B2 JP 4819552 B2 JP4819552 B2 JP 4819552B2 JP 2006098350 A JP2006098350 A JP 2006098350A JP 2006098350 A JP2006098350 A JP 2006098350A JP 4819552 B2 JP4819552 B2 JP 4819552B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- sampling

- data

- time

- timing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/006—Electronic inspection or testing of displays and display drivers, e.g. of LED or LCD displays

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

- G09G3/3241—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

- G09G3/3283—Details of drivers for data electrodes in which the data driver supplies a variable data current for setting the current through, or the voltage across, the light-emitting elements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/14—Picture signal circuitry for video frequency region

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0233—Improving the luminance or brightness uniformity across the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/029—Improving the quality of display appearance by monitoring one or more pixels in the display panel, e.g. by monitoring a fixed reference pixel

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal (AREA)

- Electroluminescent Light Sources (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of El Displays (AREA)

Description

本発明の目的は、補正信号出力用の配線を新たに設けることのない表示装置を提供することにある。

前記タイミング信号が入力され、該タイミング信号に同期してサンプリング信号を順次発生するシフトレジスタと、

前記サンプリング信号が入力され、前記データ線に供給された時系列データ信号を、該サンプリング信号に同期してサンプリングするとともに、サンプリングしたデータ信号に応じた電流または電圧を出力する複数のサンプリング回路と、

一端がスイッチを介して前記複数のサンプリング回路の各出力端子に接続され、他端が前記信号制御部に接続された共通出力線と、

を有するサンプリング装置であって、

前記複数のサンプリング回路は、前記シフトレジスタの少なくとも初段または最終段が発生するサンプリング信号に同期して、前記時系列データ信号をサンプリングするサンプリング回路を含んでおり、

前記信号制御部は、

前記スイッチを開閉する制御信号を発生し、

該スイッチが閉じている期間に、前記時系列データ信号を供給する手段から前記データ線に、前記シフトレジスタの段数に等しいデータ数を持ち、時系列の最初または最終のデータが第1のデータであり、その他のデータが第1のデータとは異なる第2のデータである時系列データ信号を供給し、前記タイミング信号を発生する手段から、前記同期信号に対して遅延したタイミング信号を発生させ、前記遅延時間を制御する手段により該タイミング信号の遅延時間を一定範囲で掃引しながら前記共通出力線の出力電流または電圧を計測して、前記掃引範囲において計測した電流または電圧が最大になる遅延時間を決定し、記憶する動作を行い、

該スイッチが開いている期間に、前記データ線に被サンプリング信号を供給し、前記タイミング信号を発生する手段から、前記記憶した遅延時間だけ前記同期信号に対して遅延したタイミング信号を発生させる動作を行う

ことを特徴とする。

与えられた同期信号に同期してデータ線に時系列データ信号を供給する手段と、タイミング信号を発生する手段と、該タイミング信号の該同期信号に対する遅延時間を制御する手段とを含む信号制御部と、

前記タイミング信号に同期してサンプリング信号を順次発生する前記マトリクスの列数に等しい段数のサンプリング信号発生手段と、

前記データ線に供給される時系列データ信号を、前記サンプリング信号のタイミングによりサンプリングする前記マトリクスの列数に等しい数のサンプリング手段と、

前記サンプリング信号発生手段の前または後に付加される、少なくとも1つの付加サンプリング信号発生手段と、

前記付加サンプリング信号発生手段が発生するサンプリング信号のタイミングにより、前記データ線に供給される時系列データ信号をサンプリングする、少なくとも1つの付加サンプリング手段と、

一端がスイッチを介して前記サンプリング手段および前記付加サンプリング手段の各出力端子に接続され、他端が前記信号制御部に接続された共通出力線と、

を備え、

前記信号制御部は、

第1の動作モード期間に、前記スイッチを閉じる制御信号を発生して前記サンプリング手段および前記付加サンプリング手段の出力を前記共通出力線に接続し、前記データ線に、前記サンプリング信号発生手段の段数と前記付加されたサンプリング信号発生手段の数の和に等しいデータ数を持ち、時系列の最初または最後のデータが前記サンプリング回路の出力電流を最大にするデータであり、その他のデータが前記サンプリング回路の出力電流を最小にするデータである時系列のデータ信号を供給し、前記タイミング信号を発生する手段から、前記同期信号に対して遅延したタイミング信号を発生させて、該タイミング信号の遅延時間を掃引しながら前記共通出力線の電流を計測し、一定の掃引範囲において計測された電流が最大になる遅延時間を決定して記憶する動作を行い、

第2の動作モード期間に、前記スイッチを開く制御信号を発生し、前記データ線に前記ビデオ信号を供給し、前記タイミング信号を発生する手段から、前記同期信号に対して前記記憶した遅延時間を持つタイミング信号を発生させる動作を行う

ことを特徴とする。

[実施形態1]

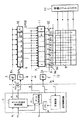

図1に本発明の表示装置のブロック図を示す。

6は画像表示部の列の数(図1ではN−1)に等しい段数を持つシフトレジスタである。サンプリング開始信号SPが1クロック周期分だけHレベルになると、その後のタイミング信号Kの立ち上がりまたは立ち下がりのタイミングで各段が順次Hレベルをシフトさせる。1つの段(k段目とする)のレジスタは、自身がHレベルのときにHレベルを出力し、これがサンプリング信号SP(k)となる。

画像表示期間でない期間内に、被サンプリング信号Sとして列間ばらつき補正用の信号を供給し、これをサンプリング回路群がサンプリングする。同時に、スイッチ群9を端子9a側に倒すと、サンプリングされた信号がGm回路の出力として共通線13に総和電流として取り出され、総和電流検出回路22で検出される。列間ばらつき補正用の信号は、列の数(今の説明でのみNとする)に等しい数のデータを時系列に並べたシリアルデータすなわち水平1ライン分のデータから構成される信号であって、以下のS(1)ないしS(N)のN種類がある。

S(1):1列目が白信号、2列目ないしN列目が黒信号

S(2):2列目が白信号、1列目と3列目ないしN列目が黒信号

S(3):3列目が白信号、1、2列目と4列目ないしN列目が黒信号

・・・

S(N):N列目が白信号、2列目ないし(N−1)列目が黒信号

これらが順次外部から被サンプリング信号Sとして送られてくる。

S(1)の信号が与えられると、1列目のGm回路が白信号に対応する最大電流を出力し、他のGm回路は黒信号に対応する最小電流すなわちゼロを出力する。このとき、共通線13を通して総和電流検出回路22によって検出される総和電流は、1列目のGm回路の最大出力値である。以下、同様に、S(2)、S(3)、・・・、S(N)の信号が与えられたときに、それらのGm回路の最大出力が検出される。これから最大電流値の平均値を求め、最大電流出力値と平均値の比を各々のGm回路の補正係数とする。実際の画像表示にあったては、画像信号に補正係数を乗じた信号が外部の回路(不図示)によって作られて、補正された画像信号が被サンプリング信号Sとして与えられる。最小電流値がゼロでなくリーク電流を含んでいる場合でも補正係数が決定できる。

d=Ts/8

としてある。

以上説明した、サンプリングタイミング調整期間と列間ばらつき補正期間とは、画素表示期間以外に設定されればよい。サンプリングタイミング調整期間と列間ばらつき補正期間とは、連続して設けられても、また分離して設けられても良い。

[実施形態2]

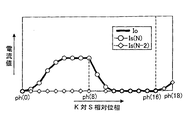

上記第1の実施形態において、位相の掃引範囲すなわち検出範囲を1サンプリング期間以上に広くすると検出ピークが複数現れ好ましい位相検出を誤ってしまう場合がある。以下、それについて説明する。

図2において位相ph(8)から位相ph(16)も検出範囲に含めると、サンプリング回路群7のN−1段目において、補正用サンプリング回路11の位相ph(0)から位相ph(8)までのサンプリングと同様な出力が共通出力線に出力される。このとき、位相ph(0)から位相ph(16)に検出範囲で検出ピークは2つとなる。位相の掃引範囲は広いほどその中に最適タイミングが捉えられる確率が高くなるので好ましいが、検出ピークが2つあると、掃引の始めと終わりをうまく選ばないと好ましい位相検出を誤ってしまう。例えば、図2の場合に位相の掃引をph(8)からph(16)に取ると、第2ピークが観測されてその最大値の位相ph(16)を最適タイミングとしてしまうことになる。

d=Ts/8

である。

[実施形態3]

図7は本発明の第3の実施形態を示すブロック図である。図7において、第2の実施形態の構成を示す図4の構成部材と同一な構成部材については同一符号を付し、説明を省略する。

[実施形態4]

図9は、本発明の第4の実施形態を示すブロック図である。図9において、第2の実施形態の構成を示す図4の構成部材と同一な構成部材については同一符号を付し、説明を省略する。

なお、以上説明した各実施形態において、表示パネルは特にELパネルに限定されず、電流信号により各画素の表示を制御しうる表示パネルであれば適用可能である。また上述の各実施形態では、補正用の信号Sの位相を固定して、補正用のサンプリング信号の位相を変化させ、共通出力線の出力に基づいてタイミング信号の位相を制御している。しかし、補正用のサンプリング信号の位相を固定して補正用の信号Sの位相を変化させ、共通出力線の出力に基づいてアナログビデオ信号の位相を制御することもできる。

また各実施形態において、タイミング信号の位相制御はサンプリング総和電流の最大値に基づいて位相を制御したが、サンプリング総和電流の微分値に基づいて位相を制御するなど、最適位相の求め方は、サンプリング総和電流値に応じた様々な演算により求めてよい。

図16はデジタルスチルカメラの一例のブロック図である。図中、129はシステム全体、123は被写体を撮像する撮影部、124は映像信号処理回路、125は表示パネル、126はメモリ、127はCPU、128は操作部を示す。撮像部123で撮影した映像または、メモリ126に記録された映像を、映像信号処理回路124で信号処理し、表示パネル125で見ることができる。CPU127では、操作部128からの入力によって、撮影部123、メモリ126、映像信号処理回路124などを制御して、状況に適した撮影、記録、再生、表示を行う。

2 計測回路、

3,4,5 レベル変換手段

6 シフトレジスタ(表示用)

7 サンプリング手段(表示用)

8 表示パネル

9 スイッチ

10 追加シフトレジスタ

11 追加サンプリング手段

13 共通出力線

20 信号制御部

60 データ線

61 データ発生手段

Claims (8)

- 同期信号が入力され、該同期信号に同期してデータ線に時系列データ信号を供給する手段と、タイミング信号を発生する手段と、該タイミング信号の該同期信号に対する遅延時間を制御する手段とを含む信号制御部と、

前記タイミング信号が入力され、該タイミング信号に同期してサンプリング信号を順次発生するシフトレジスタと、

前記サンプリング信号が入力され、前記データ線に供給された時系列データ信号を、該サンプリング信号に同期してサンプリングするとともに、サンプリングしたデータ信号に応じた電流または電圧を出力する複数のサンプリング回路と、

一端がスイッチを介して前記複数のサンプリング回路の各出力端子に接続され、他端が前記信号制御部に接続された共通出力線と、

を有するサンプリング装置であって、

前記複数のサンプリング回路は、前記シフトレジスタの少なくとも初段または最終段が発生するサンプリング信号に同期して、前記時系列データ信号をサンプリングするサンプリング回路を含んでおり、

前記信号制御部は、

前記スイッチを開閉する制御信号を発生し、

該スイッチが閉じている期間に、前記時系列データ信号を供給する手段から前記データ線に、前記シフトレジスタの段数に等しいデータ数を持ち、時系列の最初または最終のデータが第1のデータであり、その他のデータが第1のデータとは異なる第2のデータである時系列データ信号を供給し、前記タイミング信号を発生する手段から、前記同期信号に対して遅延したタイミング信号を発生させ、前記遅延時間を制御する手段により該タイミング信号の遅延時間を一定範囲で掃引しながら、前記共通出力線の出力電流または電圧を計測して、前記掃引範囲において計測した電流または電圧が最大になる遅延時間を決定し、記憶する動作を行い、

該スイッチが開いている期間に、前記データ線に被サンプリング信号を供給し、前記タイミング信号を発生する手段から、前記記憶した遅延時間だけ前記同期信号に対して遅延したタイミング信号を発生させる動作を行う

ことを特徴とするサンプリング装置。 - 前記第1のデータが前記サンプリング回路の出力電流または電圧を最大にするデータであり、前記第2のデータが前記サンプリング回路の出力電流または電圧を最小にするデータである請求項1に記載のサンプリング装置。

- 該スイッチが閉じている期間に前記データ線に供給される前記時系列データ信号は、前記第1のデータを時系列の最終のデータとする時系列データ信号であり、該期間に前記遅延時間が短い方から開始して長い方に掃引される請求項1に記載のサンプリング装置。

- 該スイッチが閉じている期間に前記データ線に供給される前記時系列データ信号は、前記第1のデータを時系列の最初のデータとする時系列データ信号であり、該期間に前記遅延時間が長い方から開始して短い方に掃引される請求項1に記載のサンプリング装置。

- 前記サンプリング回路が、前記シフトレジスタの各段に対応して設けられている請求項1に記載のサンプリング装置。

- 前記サンプリング回路が、前記シフトレジスタの最終段の隣接段を除き各段に対応して設けられており、該スイッチが閉じている期間の前記時系列データ信号が、時系列の最終のデータを前記第1のデータとする時系列データ信号である請求項1に記載のサンプリング装置。

- 前記サンプリング回路が、前記シフトレジスタの初段の隣接段を除き各段に対応して設けられており、該スイッチが閉じている期間の前記時系列データ信号が、時系列の最初のデータを前記第1のデータとする時系列データ信号である請求項1に記載のサンプリング装置。

- 請求項1ないし7のいずれか1項に記載のサンプリング装置を含む表示装置であって、行方向に延びる複数の走査電極と、該走査電極に交差する複数の列電極と、該走査電極と列電極の交差部に配置された複数の画素とを含む表示パネルを備え、前記スイッチが開かれている間、前記サンプリング回路の出力端子が、前記列電極に接続されていることを特徴とする表示装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006098350A JP4819552B2 (ja) | 2006-03-31 | 2006-03-31 | サンプリング装置、それを用いた表示装置 |

| US11/693,291 US8072542B2 (en) | 2006-03-31 | 2007-03-29 | Sampling device, display device using sampling device, and camera |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006098350A JP4819552B2 (ja) | 2006-03-31 | 2006-03-31 | サンプリング装置、それを用いた表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007271995A JP2007271995A (ja) | 2007-10-18 |

| JP2007271995A5 JP2007271995A5 (ja) | 2009-05-14 |

| JP4819552B2 true JP4819552B2 (ja) | 2011-11-24 |

Family

ID=38558312

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006098350A Expired - Fee Related JP4819552B2 (ja) | 2006-03-31 | 2006-03-31 | サンプリング装置、それを用いた表示装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8072542B2 (ja) |

| JP (1) | JP4819552B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI645719B (zh) * | 2017-01-17 | 2018-12-21 | 瑞昱半導體股份有限公司 | 取樣時脈測試電路與取樣時脈測試方法 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5854615A (en) * | 1996-10-03 | 1998-12-29 | Micron Display Technology, Inc. | Matrix addressable display with delay locked loop controller |

| JP3684800B2 (ja) * | 1997-12-11 | 2005-08-17 | ソニー株式会社 | 表示装置 |

| US6335728B1 (en) * | 1998-03-31 | 2002-01-01 | Pioneer Corporation | Display panel driving apparatus |

| JP2001282171A (ja) * | 2000-03-30 | 2001-10-12 | Sharp Corp | 画像表示装置およびその駆動制御回路 |

| JP3846871B2 (ja) * | 2002-06-24 | 2006-11-15 | シャープ株式会社 | パラレル・シリアル変換回路、シリアルデータ生成回路、同期信号生成回路、クロック信号生成回路、シリアルデータ送信装置、シリアルデータ受信装置およびシリアルデータ伝送システム |

| JP3950845B2 (ja) | 2003-03-07 | 2007-08-01 | キヤノン株式会社 | 駆動回路及びその評価方法 |

| JP4838498B2 (ja) * | 2003-05-21 | 2011-12-14 | キヤノン株式会社 | 表示装置 |

| JP4721762B2 (ja) * | 2005-04-25 | 2011-07-13 | 株式会社アドバンテスト | 試験装置 |

| JP4827499B2 (ja) | 2005-11-16 | 2011-11-30 | キヤノン株式会社 | 電流駆動型装置及び表示装置 |

| US7851996B2 (en) | 2005-11-16 | 2010-12-14 | Canon Kabushiki Kaisha | Display apparatus |

| US7692377B2 (en) | 2005-11-16 | 2010-04-06 | Canon Kabushiki Kaisha | Light emitting display device provided with external connection terminal located at peripheral portions of a display area |

| JP2007139967A (ja) | 2005-11-16 | 2007-06-07 | Canon Inc | 電流駆動型装置及び表示装置 |

-

2006

- 2006-03-31 JP JP2006098350A patent/JP4819552B2/ja not_active Expired - Fee Related

-

2007

- 2007-03-29 US US11/693,291 patent/US8072542B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20070229692A1 (en) | 2007-10-04 |

| US8072542B2 (en) | 2011-12-06 |

| JP2007271995A (ja) | 2007-10-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100770119B1 (ko) | 시프트레지스터회로 및 구동제어장치 | |

| JP3926922B2 (ja) | 画像表示装置 | |

| US7242397B2 (en) | Display device | |

| US6329980B1 (en) | Driving circuit for display device | |

| US7973782B2 (en) | Display apparatus, driving method of the same and electronic equipment using the same | |

| JP4496738B2 (ja) | 画像表示装置 | |

| US20050110737A1 (en) | Liquid crystal display device, driving circuit for the same and driving method for the same | |

| US20110216052A1 (en) | Signal line driving method for display apparatus, display apparatus and signal line driving method | |

| CN118379948B (zh) | 显示驱动装置、显示驱动方法和显示面板 | |

| KR100893966B1 (ko) | 표시장치 | |

| JP2003122318A (ja) | 表示装置 | |

| TWI254904B (en) | Display device | |

| JP4819552B2 (ja) | サンプリング装置、それを用いた表示装置 | |

| JP3858136B2 (ja) | シフトレジスタ及び電子装置 | |

| JP2760670B2 (ja) | 表示素子の駆動用集積回路 | |

| JP2003122320A (ja) | 表示装置 | |

| US20050094012A1 (en) | Solid-state image sensing apparatus | |

| JP2007133211A (ja) | 表示駆動用信号処理装置、表示装置、表示駆動用信号処理方法 | |

| US20250299610A1 (en) | Signal processing device, signal processing method, and display | |

| JP2009216806A (ja) | 電気光学装置の駆動回路、駆動方法、電気光学装置および電子機器 | |

| CN119380678A (zh) | 显示装置及其驱动方法、显示终端 | |

| JP2006121458A (ja) | 電荷転送装置及びその制御方法 | |

| KR20060020054A (ko) | 표시 장치 및 그 구동 방법 | |

| JP2010134181A (ja) | 表示装置とその駆動方法及びカメラ | |

| JP2004135136A (ja) | エリアイメージセンサ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20080207 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20090220 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090331 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090331 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20100201 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20100630 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110830 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110901 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140909 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140909 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |