JP4732009B2 - プリント配線板 - Google Patents

プリント配線板 Download PDFInfo

- Publication number

- JP4732009B2 JP4732009B2 JP2005161338A JP2005161338A JP4732009B2 JP 4732009 B2 JP4732009 B2 JP 4732009B2 JP 2005161338 A JP2005161338 A JP 2005161338A JP 2005161338 A JP2005161338 A JP 2005161338A JP 4732009 B2 JP4732009 B2 JP 4732009B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- region

- printed wiring

- wiring board

- insulating substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Manufacturing Of Printed Wiring (AREA)

Description

これについて、図8を用いて説明する。図8は従来におけるプリント配線板の断面図である。同図には、絶縁基板2の一方の面に銅箔よりなる導体層22を形成して、この導体層22の上にソルダレジスト24や金メッキ23を形成してなる従来のプリント配線板20を示している。同図に示すように、プリント配線板20の高さは、ソルダレジスト24や金メッキ23に要求される必要厚さの関係上、ソルダレジスト24を形成した領域の方が金メッキ23を形成した領域よりも高くなってしまう。その結果、それぞれの領域の境界面に生じる段差部21に応力が集中しやすくなってしまい、この段差部21での劣化が絶縁基板20に発生しやすくなるため、絶縁基板2に搭載される部品(ICチップやコンデンサ等)に悪影響を及ぼす虞がある。特に、ICチップ11が絶縁基板2の裏面に搭載される場合には、ICチップ11を絶縁基板2に装着する際に、ICチップ11に応力がかかり破損することがあり問題となっている。

このように、絶縁基板の小型化、薄板化という要望を満たしつつ、絶縁基板に搭載される部品の破損を防止する技術が要望されている。

この請求項2の発明によれば、レジスト層の表面と端子層の表面とが、略面一となるため、それぞれの部位の境界面における段差を無くして、その境界面に応力が集中することを、より確実に抑制することができる。

って、前記導体層は、前記薄肉の領域が、ハーフエッチング処理により形成されていることを特徴とする。

この請求項3の発明によれば、前記レジスト層が形成される領域の厚さを、ハーフエッチング処理により精度良く調整することができ、製造歩留まりを向上することができる。

本発明の請求項2に係る発明によれば、絶縁基板に搭載されるICチップの破損を、より確実に防止することができる。

本発明の請求項3に係る発明によれば、前記レジスト層が形成される領域の厚さを精度良く調整することができ、製造歩留まりを向上することができる。

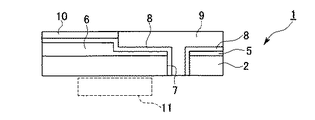

まず、プリント配線板の一実施例について、図7を参照しながら説明する。

このプリント配線板1において、絶縁基板2の表面には、銅箔の厚肉部6と、銅箔の薄部5とが形成されている。銅箔のそれぞれの部位5、6の表面およびスルーホール7の内壁面には、銅メッキ8が形成されている。厚肉部5、薄肉部6および銅メッキ8により導体層が構成されている。

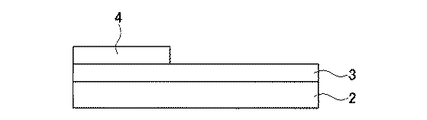

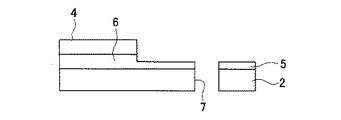

まず、絶縁基板2の表面に導体パターンを形成するための銅箔3が貼着されてなる銅張り積層板を用意する(図1)。そして、端子層形成領域における銅箔3に、マスク(エッチングレジスト)4をラミネート(積層)する(図2)。このマスク4は、感光性レジストを銅箔3の全面に塗布し、フォトマスクを用いてソルダレジスト形成領域の部位を紫外線露光、更に、現像を行うことで、形成することが好適である。

そして、アセトン等の有機溶媒でマスク4を除去した後に、製面及びデスミアを行い、無電解銅めっきの付着性を向上させるための触媒、例えばパラジウム(Pd)を銅箔5、6の表面及びスルーホール7の内壁に吸着させて、銅メッキ8を形成する(図5)。

例えば、実施の形態では、スルーホール7の内周部をソルダレジストにより穴埋めした場合について説明したが、導体パターンを給電部として電解銅メッキを行って銅メッキにより穴埋めしてもよい。また、実施の形態では、ソルダレジストと金メッキの表面がほぼ面一となるように形成しているが、若干高さのずれが生じるように構成してもよい。この場合にであっても、従来に比して応力集中を低減できているので、絶縁基板2に搭載されるICチップ11の破損を防止することができ、製造歩留まりを高めることができる。

2…絶縁基板

3…銅箔

5…薄肉部(導体層)

6…厚肉部(導体層)

8…銅メッキ(導体層)

9…ソルダレジスト(レジスト層)

10…金メッキ(端子層)

11…ICチップ

Claims (3)

- 絶縁基板と、

該絶縁基板の一方の面に形成された導体層と、

該導体層の上における一部の領域に形成された端子層と、

該導体層の上における他の領域に、前記端子層より厚い厚みで形成されたレジスト層とを備えてなり、

前記絶縁基板の、前記導体層が形成された面に対し反対側の面における、前記端子層が形成された領域と前記レジスト層が形成された領域との境界面に対応する位置に、ICチップが搭載されて使用されるプリント配線板であって、

前記導体層は、前記レジスト層の高さを前記端子層の高さに近づけるかもしくは一致させるように、前記レジスト層が形成される領域を、前記端子層が形成される領域に対

して薄肉に形成してなることを特徴とするプリント配線板。 - 前記レジスト層の表面と前記端子層の表面とが、略面一となるように構成されたことを特徴とする請求項1に記載のプリント配線板。

- 前記導体層は、前記薄肉の領域が、ハーフエッチング処理により形成されていることを特徴とする請求項1または請求項2に記載のプリント配線板。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005161338A JP4732009B2 (ja) | 2005-06-01 | 2005-06-01 | プリント配線板 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005161338A JP4732009B2 (ja) | 2005-06-01 | 2005-06-01 | プリント配線板 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006339351A JP2006339351A (ja) | 2006-12-14 |

| JP4732009B2 true JP4732009B2 (ja) | 2011-07-27 |

Family

ID=37559653

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005161338A Expired - Lifetime JP4732009B2 (ja) | 2005-06-01 | 2005-06-01 | プリント配線板 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4732009B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN116887522B (zh) * | 2023-06-19 | 2024-02-09 | 武汉铱科赛科技有限公司 | 一种线路板制作方法、系统、装置及设备 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06268355A (ja) * | 1993-03-11 | 1994-09-22 | Mitsubishi Electric Corp | プリント配線板およびその製造方法 |

| JP3424526B2 (ja) * | 1997-10-23 | 2003-07-07 | 松下電器産業株式会社 | 電子部品の実装方法 |

-

2005

- 2005-06-01 JP JP2005161338A patent/JP4732009B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006339351A (ja) | 2006-12-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10249503B2 (en) | Printed circuit board, semiconductor package and method of manufacturing the same | |

| US8206530B2 (en) | Manufacturing method of printed circuit board having electro component | |

| US8099865B2 (en) | Method for manufacturing a circuit board having an embedded component therein | |

| JP2005286112A (ja) | プリント配線板及びその製造方法 | |

| JP2008131036A (ja) | 印刷回路基板及びその製造方法 | |

| JP2009076833A (ja) | 電子素子内蔵印刷回路基板及びその製造方法 | |

| KR20100062026A (ko) | 칩 내장 인쇄회로기판 및 그 제조방법 | |

| JP7016256B2 (ja) | 印刷配線板の製造方法 | |

| US20040124003A1 (en) | Double-sided printed circuit board without via holes and method of fabricating the same | |

| JP3934104B2 (ja) | ボールグリッドアレイ基板の作製方法 | |

| KR20150102504A (ko) | 임베디드 기판 및 임베디드 기판의 제조 방법 | |

| KR100890217B1 (ko) | 기판 제조방법 | |

| JP2019046860A (ja) | 印刷配線板およびその製造方法 | |

| KR101089986B1 (ko) | 캐리어기판, 그의 제조방법, 이를 이용한 인쇄회로기판 및 그의 제조방법 | |

| KR100313611B1 (ko) | 인쇄회로기판 제조방법 | |

| JP4732009B2 (ja) | プリント配線板 | |

| JP3770895B2 (ja) | 電解めっきを利用した配線基板の製造方法 | |

| JP5000446B2 (ja) | プリント配線板の製造方法 | |

| KR20100109698A (ko) | 인쇄회로기판의 제조방법 | |

| JP5442192B2 (ja) | 素子搭載用基板、半導体モジュール、および、素子搭載用基板の製造方法 | |

| KR100704911B1 (ko) | 전자소자 내장형 인쇄회로기판 및 그 제조방법 | |

| US8450624B2 (en) | Supporting substrate and method for fabricating the same | |

| JP2005235982A (ja) | 配線基板の製造方法と配線基板、および半導体パッケージ | |

| JP4335075B2 (ja) | 多層プリント配線基板およびその製造方法 | |

| KR100771352B1 (ko) | 인쇄회로기판의 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080430 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100720 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100921 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110118 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110322 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110412 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110420 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140428 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4732009 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |