JP4662986B2 - 光−電気インターフェース、フレキシブルオプトエレクトロニクス相互接続、光トランスポンダ - Google Patents

光−電気インターフェース、フレキシブルオプトエレクトロニクス相互接続、光トランスポンダ Download PDFInfo

- Publication number

- JP4662986B2 JP4662986B2 JP2007515701A JP2007515701A JP4662986B2 JP 4662986 B2 JP4662986 B2 JP 4662986B2 JP 2007515701 A JP2007515701 A JP 2007515701A JP 2007515701 A JP2007515701 A JP 2007515701A JP 4662986 B2 JP4662986 B2 JP 4662986B2

- Authority

- JP

- Japan

- Prior art keywords

- electrical

- optical

- circuit board

- component

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/14—Structural association of two or more printed circuits

- H05K1/147—Structural association of two or more printed circuits at least one of the printed circuits being bent or folded, e.g. by using a flexible printed circuit

-

- G—PHYSICS

- G02—OPTICS

- G02B—OPTICAL ELEMENTS, SYSTEMS OR APPARATUS

- G02B6/00—Light guides; Structural details of arrangements comprising light guides and other optical elements, e.g. couplings

- G02B6/24—Coupling light guides

- G02B6/42—Coupling light guides with opto-electronic elements

- G02B6/4201—Packages, e.g. shape, construction, internal or external details

-

- G—PHYSICS

- G02—OPTICS

- G02B—OPTICAL ELEMENTS, SYSTEMS OR APPARATUS

- G02B6/00—Light guides; Structural details of arrangements comprising light guides and other optical elements, e.g. couplings

- G02B6/24—Coupling light guides

- G02B6/42—Coupling light guides with opto-electronic elements

- G02B6/4201—Packages, e.g. shape, construction, internal or external details

- G02B6/4274—Electrical aspects

-

- G—PHYSICS

- G02—OPTICS

- G02B—OPTICAL ELEMENTS, SYSTEMS OR APPARATUS

- G02B6/00—Light guides; Structural details of arrangements comprising light guides and other optical elements, e.g. couplings

- G02B6/24—Coupling light guides

- G02B6/42—Coupling light guides with opto-electronic elements

- G02B6/4201—Packages, e.g. shape, construction, internal or external details

- G02B6/4274—Electrical aspects

- G02B6/428—Electrical aspects containing printed circuit boards [PCB]

- G02B6/4281—Electrical aspects containing printed circuit boards [PCB] the printed circuit boards being flexible

-

- G—PHYSICS

- G02—OPTICS

- G02B—OPTICAL ELEMENTS, SYSTEMS OR APPARATUS

- G02B6/00—Light guides; Structural details of arrangements comprising light guides and other optical elements, e.g. couplings

- G02B6/24—Coupling light guides

- G02B6/42—Coupling light guides with opto-electronic elements

- G02B6/4201—Packages, e.g. shape, construction, internal or external details

- G02B6/4274—Electrical aspects

- G02B6/4283—Electrical aspects with electrical insulation means

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/189—Printed circuits structurally associated with non-printed electric components characterised by the use of a flexible or folded printed circuit

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10007—Types of components

- H05K2201/10121—Optical component, e.g. opto-electronic component

Description

Claims (28)

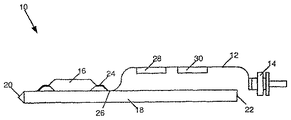

- 光−電気インターフェースであって、

回路基板と、

前記回路基板に装着される電気部品と、

光学部品と、

前記回路基板に対して物理的に離れて設けられて前記光学部品に電気的に接続される第1の端部と、前記電気部品の近くに電気的に接続される第2の端部とを有するフレキシブル相互接続であって、前記第2の端部に設けられたプラガブルコネクタを介して、前記電気部品に着脱自在に結合されるフレキシブル相互接続と

を含み、

前記回路基板は、第1のエッジと、前記第1のエッジに対向する第2のエッジとを有し、

前記第1のエッジは、電気エッジまたはカードエッジコネクタに対応し、前記第2のエッジは、光学エッジに対応し、

前記電気部品は、前記回路基板上で前記第1のエッジの近くに取り付けられており、

前記光学部品は、前記回路基板から離れて装着され、前記光学エッジの近くに配置されている、光−電気インターフェース。 - 前記フレキシブル相互接続は、

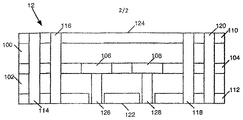

第1の信号トレースと、前記第1の信号トレースから電気的に絶縁された第2の信号トレースとを含み、第1の表面と第2の表面とを有する信号層と、

前記信号層の前記第1の表面に配置された第1の誘電層と、

前記信号層の前記第2の表面に配置された第2の誘電層と

を含む、請求項1に記載の光−電気インターフェース。 - 前記電気部品は、前記フレキシブル相互接続の前記第2の端部に直接接続された1つまたはそれ以上の電気的リードを含む、請求項1または2に記載の光−電気インターフェース。

- 前記回路基板は、1つまたはそれ以上の導電トレースを含み、

前記電気部品は、前記1つまたはそれ以上の導電トレースに接続された1つまたはそれ以上の電気的リードを含み、

前記フレキシブル相互接続の前記第2の端部は、前記電気部品の近くの位置において前記1つまたはそれ以上の導電トレースに直接接続される、請求項1または2に記載の光−電気インターフェース。 - 前記フレキシブル相互接続上に配置され、かつ、前記フレキシブル相互接続に電気的に結合される1つまたはそれ以上の回路素子

をさらに含む、請求項1から4のいずれかに記載の光−電気インターフェース。 - 前記フレキシブル相互接続は、前記回路基板に面した表面を含み、前記1つまたはそれ以上の回路素子は、前記回路基板に面した前記表面上に配置される、請求項5に記載の光−電気インターフェース。

- 前記1つまたはそれ以上の回路素子は、直流ブロック、直流入段、および、高周波マッチングネットワークの少なくとも1つを含む、請求項5または6に記載の光−電気インターフェース。

- 前記フレキシブル相互接続は、フレキシブル回路を含む、請求項1から7のいずれかに記載の光−電気インターフェース。

- 前記フレキシブル相互接続は、

前記第1の誘電層および前記第2の誘電層を介して配置され、かつ、前記第1の信号トレースおよび前記第2の信号トレースから電気的に絶縁された1つまたはそれ以上のバイアと、

前記第1の誘電層上に配置され、かつ、前記1つまたはそれ以上のバイアと電気的に接続される第1のグランド層と、

前記第2の誘電層上に配置され、かつ、前記1つまたはそれ以上のバイアと電気的に接続される第2のグランド層と

をさらに含む、請求項2に記載の光−電気インターフェース。 - 前記第1の信号トレースは、送信光学部品に電気的に接続され、前記第2の信号トレースは、受信光学部品に電気的に接続される、請求項2または9に記載の光−電気インターフェース。

- 前記第1の信号トレースは、送信電気部品の近くに電気的に接続され、前記第2の信号トレースは、受信電気部品の近くに電気的に接続される、請求項2、9、または10に記載の光−電気インターフェース。

- 前記第1の信号トレースおよび前記第2の信号トレースの少なくとも1つは、ストリップライントレース、シングルエンドトレース、または差動トレースの1つを含む、請求項2、9から11のいずれかに記載の光−電気インターフェース。

- 前記電気部品は、スモールフォームファクタ電気部品、能動電気部品、受動電気部品、パッケージシリコン電気部品、またはベアシリコン電気部品の1つを含む、請求項1から12のいずれかに記載の光−電気インターフェース。

- 前記光学部品は、プラガブルトランジスタアウトライン光学部品を含む、請求項1から13のいずれかに記載の光−電気インターフェース。

- フレキシブルオプトエレクトロニクス相互接続であって、

第1の誘電層と、

第2の誘電層と、

前記第1の誘電層と前記第2の誘電層との間に配置された信号層と

を含み、

前記信号層は、

第1の信号トレースと、

前記第1の誘電層上に配置された第1のグランドプレーン層と、

前記第2の誘電層上に配置された第2のグランドプレーン層と、

前記第1のグランドプレーン層と前記第2のグランドプレーン層とを電気的に結合する複数のバイアと

を含み、

前記第1のグランドプレーン層、前記第2のグランドプレーン層、および前記複数のバイアは、前記第1の信号トレースの周りにファラデー箱を形成し、

前記第1の信号トレースは、前記第2のグランドプレーン層の開口を通るバイアによって、前記フレキシブルオプトエレクトロニクス相互接続の表面に配置された回路素子に電気的に接続されている、フレキシブルオプトエレクトロニクス相互接続。 - 前記信号層は、

前記第1の信号トレースから電気的に絶縁された第2の信号トレース

をさらに含む、請求項15に記載のフレキシブルオプトエレクトロニクス相互接続。 - 前記第1の信号トレースは、ストリップライントレース、シングルエンドトレース、または対の差動トレースの1つを含む、請求項15または16に記載のフレキシブルオプトエレクトロニクス相互接続。

- 前記第1の信号トレースは、約50オームの制御されたインピーダンスを含む、請求項15から17のいずれかに記載のフレキシブルオプトエレクトロニクス相互接続。

- 前記第1の信号トレースは、約100オームの制御されたインピーダンスを含む、請求項15から17のいずれかに記載のフレキシブルオプトエレクトロニクス相互接続。

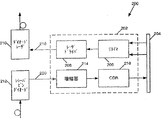

- 光トランスポンダであって、

回路基板と、

前記回路基板に装着された第1の電気部品と、

前記回路基板に装着された第2の電気部品と、

前記回路基板から離れて装着される受信光学部品と、

前記回路基板から離れて装着される送信光学部品と、

前記回路基板に対して物理的に離れて設けられて前記受信光学部品および前記送信光学部品に電気的に接続された第1の端部と、前記第1の電気部品および前記第2の電気部品の近くに電気的に接続された第2の端部とを有し、前記受信光学部品と前記第1の電気部品とを結合し、かつ、前記送信光学部品と前記第2の電気部品とを結合するフレキシブル相互接続であって、前記第2の端部に設けられたプラガブルコネクタを介して、前記第1の電気部品および前記第2の電気部品に着脱自在に結合されるフレキシブル相互接続と

を含み、

前記回路基板は、第1のエッジと、前記第1のエッジに対向する第2のエッジとを有し、

前記第1のエッジは、電気エッジまたはカードエッジコネクタに対応し、前記第2のエッジは、光学エッジに対応し、

前記第1の電気部品および前記第2の電気部品は、前記回路基板上で前記第1のエッジの近くに取り付けられており、

前記受信光学部品および前記送信光学部品は、前記光学エッジの近くに配置されている、光トランスポンダ。 - 前記フレキシブル相互接続上に配置され、かつ、前記フレキシブル相互接続と電気的に結合する1つまたはそれ以上の回路素子

をさらに備える、請求項20に記載の光トランスポンダ。 - 前記フレキシブル相互接続は、前記回路基板に面した表面を含み、

前記1つまたはそれ以上の回路素子は、前記回路基板に面した表面上に配置される、請求項21に記載の光トランスポンダ。 - 前記フレキシブル相互接続は、第1の信号トレースと、前記第1の信号トレースから電気的に絶縁された第2の信号トレースとを含み、

前記第1の信号トレースは、前記受信光学部品と前記第1の電気部品とを結合し、

前記第2の信号トレースは、前記送信光学部品と前記第2の電気部品とを結合する、請求項20から22のいずれかに記載の光トランスポンダ。 - 前記フレキシブル相互接続は、

第1の信号トレースと、前記第1の信号トレースから電気的に絶縁された第2の信号トレースとを含み、第1の表面と第2の表面とを有する信号層と、

前記信号層の前記第1の表面に配置された第1の誘電層と、

前記信号層の前記第2の表面に配置された第2の誘電層と、

前記第1の誘電層および前記第2の誘電層を介して配置され、かつ、前記第1の信号トレースおよび前記第2の信号トレースから電気的に絶縁された1つまたはそれ以上のバイアと、

前記第1の誘電層上に配置され、かつ、前記1つまたはそれ以上のバイアと電気的に接続される第1のグランドプレーンと、

前記第2の誘電層上に配置され、かつ、前記1つまたはそれ以上のバイアと電気的に接続される第2のグランドプレーンと

を含む、請求項20から22のいずれかに記載の光トランスポンダ。 - 前記第1の電気部品は、クロック・データリカバリ部品、シリアライザ/デシリアライザ、または増幅器の1つを含む、請求項20から24のいずれかに記載の光トランスポンダ。

- 前記第2の電気部品は、レーザドライバまたはリタイマの1つを含む、請求項20から25のいずれかに記載の光トランスポンダ。

- 前記受信光学部品は、受信光サブアセンブリを含む、請求項20から26のいずれかに記載の光トランスポンダ。

- 前記送信光学部品は、送信光サブアセンブリを含む、請求項20から27のいずれかに記載の光トランスポンダ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/882,906 US7316509B2 (en) | 2004-06-30 | 2004-06-30 | Apparatus for electrical and optical interconnection |

| PCT/US2005/022367 WO2006012260A1 (en) | 2004-06-30 | 2005-06-24 | Apparatus for electrical and optical interconnection |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008501247A JP2008501247A (ja) | 2008-01-17 |

| JP4662986B2 true JP4662986B2 (ja) | 2011-03-30 |

Family

ID=35344712

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007515701A Expired - Fee Related JP4662986B2 (ja) | 2004-06-30 | 2005-06-24 | 光−電気インターフェース、フレキシブルオプトエレクトロニクス相互接続、光トランスポンダ |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7316509B2 (ja) |

| EP (1) | EP1761814A1 (ja) |

| JP (1) | JP4662986B2 (ja) |

| CN (2) | CN101363948B (ja) |

| WO (1) | WO2006012260A1 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006091241A (ja) * | 2004-09-22 | 2006-04-06 | Hitachi Cable Ltd | 光電気複合配線部品及びこれを用いた電子機器 |

| US7305156B2 (en) * | 2005-03-29 | 2007-12-04 | Intel Corporation | Optical sub-assembly |

| JP4755502B2 (ja) * | 2006-02-02 | 2011-08-24 | 日本オプネクスト株式会社 | 光受信機 |

| US7450396B2 (en) * | 2006-09-28 | 2008-11-11 | Intel Corporation | Skew compensation by changing ground parasitic for traces |

| KR100871252B1 (ko) * | 2007-01-19 | 2008-11-28 | 삼성전자주식회사 | 광섬유를 이용한 광/전기 배선을 갖는 연성 인쇄회로기판 |

| TWI355155B (en) * | 2007-03-21 | 2011-12-21 | Delta Electronics Inc | Optical communicating device |

| US7866896B2 (en) * | 2007-09-06 | 2011-01-11 | Telecast Fiber Systems, Inc. | Electrical to optical and optical to electrical connector system |

| US20110110631A1 (en) * | 2008-09-08 | 2011-05-12 | Baker Eugene E | Modular, Reconfigurable Video Data Transport System |

| US8279611B2 (en) * | 2009-12-09 | 2012-10-02 | Research In Motion Limited | Flexible cable having rectangular waveguide formed therein and methods of manufacturing same |

| US20110249947A1 (en) * | 2010-04-12 | 2011-10-13 | Avago Technologies Fiber Ip (Singapore) Pte. Ltd. | Opto-electronic transceiver module with castellated electrical turn |

| US9297967B2 (en) | 2010-04-30 | 2016-03-29 | Hewlett Packard Enterprise Development Lp | Device for converting signal |

| US9413140B2 (en) * | 2013-12-19 | 2016-08-09 | Taiwan Semiconductor Manufacturing Company Limited | Semiconductor arrangement and formation thereof |

| JP6868781B2 (ja) * | 2016-02-01 | 2021-05-12 | ソニーグループ株式会社 | 光コネクタ、電子機器および光インターコネクションシステム |

| US10645027B2 (en) * | 2016-09-30 | 2020-05-05 | Facebook, Inc. | Network switches configured to employ optical or electrical interfaces |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03501435A (ja) * | 1988-07-21 | 1991-03-28 | ヒユーズ・エアクラフト・カンパニー | フレキシブルな同軸ケーブル装置および方法 |

| JPH0518059U (ja) * | 1991-08-09 | 1993-03-05 | 富士通テン株式会社 | 両面基板の表裏接続構造 |

| JP2004047574A (ja) * | 2002-07-09 | 2004-02-12 | Sumitomo Electric Ind Ltd | 多層配線基板、光トランシーバ、およびトランスポンダ |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4798918A (en) | 1987-09-21 | 1989-01-17 | Intel Corporation | High density flexible circuit |

| JP3740748B2 (ja) | 1996-06-18 | 2006-02-01 | 松下電器産業株式会社 | 光ファイバモジュール |

| US6353189B1 (en) | 1997-04-16 | 2002-03-05 | Kabushiki Kaisha Toshiba | Wiring board, wiring board fabrication method, and semiconductor package |

| JPH1187871A (ja) * | 1997-09-08 | 1999-03-30 | Alps Electric Co Ltd | 回路基板と薄型電源装置 |

| JPH11196055A (ja) * | 1997-12-26 | 1999-07-21 | Hitachi Cable Ltd | 光送受信器 |

| JP2000277814A (ja) | 1999-03-29 | 2000-10-06 | Sumitomo Electric Ind Ltd | 光通信モジュール |

| US6583902B1 (en) * | 1999-12-09 | 2003-06-24 | Alvesta, Inc. | Modular fiber-optic transceiver |

| US6388890B1 (en) * | 2000-06-19 | 2002-05-14 | Nortel Networks Limited | Technique for reducing the number of layers in a multilayer circuit board |

| US6496291B1 (en) | 2000-10-17 | 2002-12-17 | Intel Corporation | Optical serial link |

| US6671948B2 (en) * | 2000-12-18 | 2004-01-06 | General Electric Company | Interconnection method using an etch stop |

| US6322257B1 (en) | 2001-02-09 | 2001-11-27 | Lockheed Martin Corporation | Optical array chip packages with passive alignment features |

| JP2002353508A (ja) | 2001-05-23 | 2002-12-06 | Fuji Xerox Co Ltd | 光伝送装置 |

| US6739760B2 (en) | 2001-09-17 | 2004-05-25 | Stratos International, Inc. | Parallel fiber optics communications module |

| US6705769B2 (en) | 2001-09-20 | 2004-03-16 | International Business Machines Corporation | Packaging architecture for a multiple array transceiver using a flexible cable |

| US20030085452A1 (en) * | 2001-11-05 | 2003-05-08 | International Business Machines Corporation | Packaging architecture for a multiple array transceiver using a continuous flexible circuit |

| JP3803596B2 (ja) | 2002-03-14 | 2006-08-02 | 日本電気株式会社 | パッケージ型半導体装置 |

| US6797891B1 (en) * | 2002-03-18 | 2004-09-28 | Applied Micro Circuits Corporation | Flexible interconnect cable with high frequency electrical transmission line |

| US7273987B2 (en) * | 2002-03-21 | 2007-09-25 | General Electric Company | Flexible interconnect structures for electrical devices and light sources incorporating the same |

| US6870257B2 (en) * | 2003-06-04 | 2005-03-22 | Intel Corporation | Power delivery through a flex tape in decoupled I/O-power hybrid substrate |

-

2004

- 2004-06-30 US US10/882,906 patent/US7316509B2/en not_active Expired - Fee Related

-

2005

- 2005-06-24 JP JP2007515701A patent/JP4662986B2/ja not_active Expired - Fee Related

- 2005-06-24 CN CN2008101341845A patent/CN101363948B/zh not_active Expired - Fee Related

- 2005-06-24 CN CNB200580021400XA patent/CN100454064C/zh not_active Expired - Fee Related

- 2005-06-24 EP EP05771338A patent/EP1761814A1/en not_active Withdrawn

- 2005-06-24 WO PCT/US2005/022367 patent/WO2006012260A1/en not_active Application Discontinuation

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03501435A (ja) * | 1988-07-21 | 1991-03-28 | ヒユーズ・エアクラフト・カンパニー | フレキシブルな同軸ケーブル装置および方法 |

| JPH0518059U (ja) * | 1991-08-09 | 1993-03-05 | 富士通テン株式会社 | 両面基板の表裏接続構造 |

| JP2004047574A (ja) * | 2002-07-09 | 2004-02-12 | Sumitomo Electric Ind Ltd | 多層配線基板、光トランシーバ、およびトランスポンダ |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100454064C (zh) | 2009-01-21 |

| CN1977201A (zh) | 2007-06-06 |

| US20060002663A1 (en) | 2006-01-05 |

| EP1761814A1 (en) | 2007-03-14 |

| CN101363948A (zh) | 2009-02-11 |

| US7316509B2 (en) | 2008-01-08 |

| CN101363948B (zh) | 2012-02-08 |

| JP2008501247A (ja) | 2008-01-17 |

| WO2006012260A1 (en) | 2006-02-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4662986B2 (ja) | 光−電気インターフェース、フレキシブルオプトエレクトロニクス相互接続、光トランスポンダ | |

| US8655119B2 (en) | Connection device and optical device | |

| JP3803596B2 (ja) | パッケージ型半導体装置 | |

| US7275937B2 (en) | Optoelectronic module with components mounted on a flexible circuit | |

| US7217043B2 (en) | Optoelectronic transceiver | |

| US7484967B2 (en) | Optical module with a flexible printed circuit board to be electrically connected with a host board | |

| CN110780397A (zh) | 一种光模块 | |

| US8457454B1 (en) | Optical substrate chip carrier | |

| JP5654288B2 (ja) | 光モジュール及び高周波モジュール | |

| JP2016225631A (ja) | 非接触自由空間光リンク用の光電モジュール、関連するマルチチャネルモジュール、関連する相互接続システム、基板の製造及び接続方法 | |

| US7338216B2 (en) | Transmitter subassembly ground return path | |

| US11057984B2 (en) | High-speed hybrid circuit | |

| US20200174205A1 (en) | Optical component and optical module using the same | |

| TW201419774A (zh) | 具有遠離轉阻放大器之光偵測器的接收機光學總成(roas)及其相關元件、電路與方法 | |

| US10365446B2 (en) | Optical module structure | |

| JP4968311B2 (ja) | 光データリンク | |

| US6841799B2 (en) | Optoelectronic package | |

| US20050205957A1 (en) | Integrated VCSELs on traditional VLSI packaging | |

| JP2012145743A (ja) | 光モジュール | |

| US11139412B2 (en) | Electrical coupling assemblies and methods for optoelectronic modules | |

| KR102500792B1 (ko) | 광 모듈 및 솔더볼 접합 구조체 | |

| US20230194905A1 (en) | Optical module and manufacturing method of optical module for optical communication | |

| WO2016060978A1 (en) | Data transmission system with minimized crosstalk | |

| JP2020191329A (ja) | 半導体装置の実装構造、光モジュール、及び半導体装置の実装構造の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20081028 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20090127 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20090203 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20090226 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20090305 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20090327 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20090403 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090427 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091104 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100203 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100210 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100303 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100310 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100402 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100409 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100430 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101026 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101027 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101214 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110104 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140114 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |