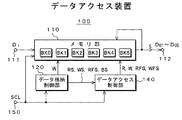

以下、図面を参照しながら、この発明の実施の形態について説明する。図1は、実施の形態としてのデータアクセス装置100の構成を示している。

このデータアクセス装置100は、メモリ部110と、データ格納制御部120と、データアクセス制御部140とを備えている。

メモリ部110は、6個のメモリバンクBK0〜BK5からなっている。このメモリ部110は、図示しない制御装置から入力端子150を介して与えられる制御信号SCLに基づいて動作する。

このメモリ部110には、初期格納時に、入力端子111から、格納すべき所定画面の画素データDiが入力される。ここで、所定画面は、水平方向に伸びる画素列が垂直方向に順次配列された構成となっており、メモリ部110には各画素列の画素データが順に注目画素としてラスタスキャン順に入力されていく。そして、このようにメモリ部110に入力されていく各注目画素の画素データは6個のメモリバンクBK0〜BK5に振り分けて格納される。

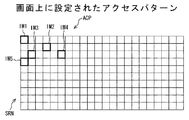

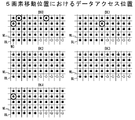

また、データアクセス時に、画面上に複数の画素のパターンがアクセスパターンACPとして設定され、このアクセスパターンACPの設定位置が開始位置から画素列方向に1画素ずつ移動した各設定位置で、アクセスパターンACPで特定される複数の画素(以下、適宜、「アクセス画素」という)の画素データDo1〜Do5が、6個のメモリバンクBK0〜BK5のいずれかから同時に読み出されて、出力端子112に出力される。

この場合、アクセスパターンACPの設定位置は、ラスタスキャン順に移動していく。この実施の形態では、アクセスパターンACPは5個の画素のパターンとされ、上述の各設定位置でアクセスパターンACPで特定される5個のアクセス画素の画素データDo1〜Do5が同時に読み出される。なお、このように各設定位置で読み出される画素データDo1〜Do5は、他のメモリバンクに格納すべき画素データとして、メモリ部110に再入力される。

データ格納制御部120は、図示しない制御装置から入力端子150を介して供給される制御信号SCLに基づいて動作する。このデータ格納制御部120は、上述したように、各注目画素の画素データをメモリ部110の6個のメモリバンクBK0〜BK5に振り分けて格納するための制御を行う。つまり、このデータ格納制御部120は、1番目の画素から順に注目画素とし、最初は6個のメモリバンクBK0〜BK5のうち最初のメモリバンク、つまりメモリバンクBK0にその注目画素の画素データを格納する。

その後に、このデータ格納制御部120は、開始位置に設定されたアクセスパターンACPで特定される5個の画素(以下、適宜、「初期アクセス画素」という)IM1〜IM5に基づき、注目画素が5個の初期アクセス画素IM1〜IM5のいずれかとなるとき、あるいは同一のメモリバンクに一定数Nの画素データを連続して格納したとき、注目画素の画素データを格納するメモリバンクを順次切り替える。この実施の形態では、画面の水平方向に伸びる画素列の画素数が22個とされ、一定数Nは画素列の画素数と同じく22とされている。

また、このデータ格納制御部120は、注目画素が5個の初期アクセス画素IM1〜IM5のいずれかになることでメモリバンクを切り替えるとき、切り替え前のメモリバンクの書き込みアドレスを一定数だけ進めて次の書き込みアドレスとする。

データ格納制御部120についてさらに詳細に説明する。図2は、このデータ格納制御部120の構成を示している。このデータ格納制御部120は、カウンタ(カウンタA)121と、カウンタ(カウンタB)122と、一致判定部123と、オフセット制御部124と、バンクアドレスカウンタ125と、ビット線アドレスカウンタ126と、ワード線アドレスカウンタ127と、アドレス生成部128と、読み出しフラグ生成部129とを有している。

カウンタ(カウンタA)121は、上述したメモリ部111に順に入力される各注目画素の画素データの入力個数をカウントする。このカウンタ121には、メモリ部110に入力される各注目画素の画素データに同期したデータクロックDCKが供給される。このデータクロックDCKは、上述した制御信号SCLのひとつを構成しており、図示しない制御装置から供給される。このカウンタ121は、最初にそのカウント値が0とされ、その後はメモリ部110に各注目画素の画素データが入力される毎に、データクロックDCKによってインクリメントされていく。

一致判定部123は、上述したメモリ部110に所定の注目画素の画素データが入力される毎に、その注目画素が、開始位置に設定されたアクセスパターンACPで特定される5個の初期アクセス画素に一致するか否かを判定する。そのため、この一致判定部123には、注目画素が当該5個の初期アクセス画素となるときに上述したカウンタ121から出力されるカウント値CN1〜CN5が、アクセスパターン情報IAPとして供給される。このアクセスパターン情報IAPは、上述した制御信号SCLのひとつを構成しており、図示しない制御装置から供給される。この一致判定部123は、ある注目画素におけるカウンタ121のカウント値が、カウント値CN1〜CN5と一致するとき、それぞれ、当該注目画素は1番目〜5番目の初期アクセス画素であると判定する。

カウンタ(カウンタB)122は、同一のメモリバンクに連続して格納される画素データの個数をカウントする。このカウンタ122には、メモリ部110に入力される各注目画素の画素データに同期したデータクロックDCKが供給されると共に、上述した一致判定部123の判定出力が供給される。このカウンタ122は、最初はそのカウント値が0とされ、上述した一致判定部123で注目画素が初期アクセス画素であると判定されるか、同一のメモリバンクに連続して格納される画素データの個数が一定数Nとなり、カウント値が一定数Nを越えるとき、そのカウント値が1にセットされ、その後はメモリ部110に各注目画素の画素データが入力される毎に、データクロックDCKによってインクリメントされていく。

バンクアドレスカウンタ125は、6個のメモリバンクBK0〜BK5のうち注目画素の画素データを格納すべきメモリバンクを示すカウント値、つまりバンクアドレスを出力する。このバンクアドレスカウンタ125には、上述した一致判定部123の判定出力が供給されると共に、カウンタ122のカウント値が供給される。このバンクアドレスカウンタ125は、最初はそのカウント値が0とされ、その後に注目画素が初期アクセス画素のいずれかであると判定されるか、あるいは同一メモリバンクに連続して格納される画素データの個数が一定数Nとなり、カウンタ122のカウント値が一定数Nを越えるとき、インクリメントされる。このバンクアドレスカウンタ125は、カウント値5の次はカウント値0となり、6進カウンタの構成となっている。このバンクアドレスカウンタ125のカウント値0〜5、つまりバンクアドレス0〜5は、それぞれメモリバンクBK0〜BK5を示している。

ビット線アドレスカウンタ126は、6個のメモリバンクBK0〜BK5にそれぞれ対応した6個のカウンタ126-0〜126-5からなっている。このビット線アドレスカウンタ126には、メモリ部110に入力される各注目画素の画素データに同期したデータクロックDCKが供給されると共に、バンクアドレスカウンタ125のカウント値(バンクアドレス)が供給される。これらのカウンタ126-0〜126-5は、最初はそのカウント値、つまりビット線アドレスが0とされ、その後はメモリ部110に各注目画素の画素データが入力されて格納される毎に、カウンタ126-0〜126-5のうちバンクアドレスに対応したカウンタがインクリメントされていく。この実施の形態では、各メモリバンクBK0〜BK5のワード線長は10とされ、カウンタ126-0〜126-5は、カウント値9の次はカウント値0となり、10進カウンタの構成となっている。

ワード線アドレスカウンタ127は、6個のメモリバンクBK0〜BK5にそれぞれ対応した6個のカウンタ127-0〜127-5からなっている。これらのカウンタ127-0〜127-5には、それぞれ上述したカウンタ126-0〜126-5の桁上げ信号であるキャリーCAが供給される。これらのカウンタ127-0〜127-5は、それぞれ、カウンタ126-0〜126-5からキャリーCAが供給される毎に、インクリメントされていく。

オフセット制御部124は、ビット線アドレスカウンタ126およびワード線アドレスカウンタ127のカウント値のオフセット制御をする。このオフセット制御部124には、一致判定部123の判定出力が供給されると共に、バンクアドレスカウンタ125のカウント値(バンクアドレス)が供給される。このオフセット制御部124は、注目画素が初期アクセス画素のいずれかとなるとき、バンクアドレスカウンタ125のカウント値で示されるメモリバンクの書き込みアドレスが一定数Nに対応したアドレスの次のアドレスとなるように、ビット線アドレスカウンタ126およびワード線アドレスカウンタ127にオフセットを与える。

アドレス生成部128は、メモリ部110に供給する書き込みアドレスWを生成する。このアドレス生成部128には、カウンタ125〜127のカウント値が供給されると共に、カウンタ122のカウント値が供給される。このアドレス生成部128は、バンクアドレスカウンタ125のカウント値(バンクアドレス)、ビット線アドレスカウンタ126を構成するカウンタ126-0〜126-5のうちバンクアドレスに対応したカウンタのカウント値(ビット線アドレス)、およびワード線アドレスカウンタ127を構成するカウンタ127-0〜127-5のうちバンクアドレスに対応したカウンタのカウント値(ワード線アドレス)を合成して、メモリ部110に供給する書き込みアドレスWを生成する。

また、このアドレス生成部128は、データアクセス制御部140で用いられる、それぞれのメモリバンクBK0〜BK5に対する、読み出し開始アドレスRSおよび書き込み開始アドレスWSを生成する。この場合、アドレス生成部128は、それぞれのメモリバンクBK0〜BK5の、初期アクセス画素の1番目の画素以降のデータであって最初に画素データが格納された書き込みアドレスWを読み出し開始アドレスRSとする。また、アドレス生成部128は、最初の画素データから連続して格納された画素データの個数が一定数Nであるとき読み出し開始アドレスRSを書き込み開始アドレスWSとし、最初の画素データから連続して格納された画素データの個数が一定数Nに満たないとき、最後の画素データが格納されたアドレスの次のアドレスを書き込み開始アドレスWSとする。

また、アドレス生成部128は、データアクセス制御部140のバンク指定部のカウンタの初期値BSを生成する。この場合、5個の初期アクセス画素のうち1番目の初期アクセス画素の画素データが格納されたメモリバンクを示すバンクアドレス(バンクアドレスカウンタ125のカウント値)を初期値とする。

読み出しフラグ生成部129は、データアクセス制御部140で用いられる、それぞれのメモリバンクBK0〜BK5に対する読み出しフラグRFGを生成する。この読み出しフラグ生成部129には、一致判定部123の判定出力が供給されると共に、バンクアドレスカウンタ125のカウント値(バンクアドレス)が供給される。この読み出しフラグ生成部129は、6個のメモリバンクBK0〜BK5のうち、5個の初期アクセス画素のいずれかに対応する画素データが格納されるメモリバンクに対する読み出しフラグRFGを読み出しを行うことを示すフラグオンの状態、例えば1とし、その他のメモリバンクに対する読み出しフラグRFGを読み出しを行わないことを示すフラグオフの状態、例えば0とする。

次に、図2に示すデータ格納制御部120の制御による初期格納時の動作を、図3のフローチャートを用いて説明する。なお、データ格納制御部120は、例えばマイクロプロセッサで構成され、図示しないプログラムメモリに格納されたデータ格納制御プログラムに従って制御処理をする。

ステップST1で、動作を開始し、ステップST2で、バンクアドレスカウンタ125のカウント値(バンクアドレス)、ビット線アドレスカウンタ126(カウンタ126-0〜126-5)のカウント値(ビット線アドレス)およびワード線アドレスカウンタ127(カウンタ127-0〜127-5)のカウント値(ワード線アドレス)をそれぞれ0にし、カウンタ(カウンタA)121およびカウンタ(カウンタB)122のカウント値をそれぞれ0にし、さらに読み出しフラグ生成部129から出力される各メモリバンクBK0〜BK5に対応する読み出しフラグRFGを全て読み出しを行わないことを示すフラグオフの状態、例えば0にする。

次に、ステップST3で、注目画素の画素データが入力されたか否かを判定する。この場合、データクロックDCKが供給されるとき、注目画素の画素データが入力されたと判定する。注目画素の画素データが入力されたと判定するとき、ステップST4で、カウンタ(カウンタA)121をインクリメントする。そして、ステップST5で、注目画素が初期アクセス画素であるか否かを、一致判定部123で判定する。この場合、カウンタ(カウンタA)121のカウント値が、アクセスパターン情報IAPとしてのカウント値CN1〜CN5のいずれかと一致するとき、注目画素が初期アクセス画素であると判定する。

注目画素が初期アクセス画素であると判定するとき、ステップST6で、注目画素が1番目の画素であるか否か、すなわちカウンタ(カウンタA)121のカウント値が1であるか否かを判定する。注目画素が1番目の画素でないときは、ステップST7で、注目画素が1番目の初期アクセス画素であるか否かを、一致判定部123で判定する。この場合、カウンタ(カウンタA)121のカウント値が、アクセスパターン情報IAPとしてのカウント値CN1と一致するとき、注目画素が1番目の初期アクセス画素であると判定する。

注目画素が1番目の初期アクセス画素ではなく、2番目以降の初期アクセス画素であると判定するとき、ステップST8で、書き込みアドレスWを、バンクアドレスに対応したメモリバンクの書き込み開始アドレスWSにし、その後にステップST9に進む。この書き込みアドレスWは、アドレス生成部128で、バンクアドレスカウンタ125のカウント値(バンクアドレス)、ビット線アドレスカウンタ126のバンクアドレスに対応したカウンタのカウント値(ビット線アドレス)およびワード線アドレスカウンタ127のバンクアドレスに対応したカウンタのカウント値(ワード線アドレス)を合成することで生成されている。

一方、注目画素が1番目の初期アクセス画素であるときは、直ちにステップST9に進む。このステップST9では、オフセット制御部124は、バンクアドレスに対応したメモリバンクの書き込みアドレスWが一定数N、この実施の形態では22に対応したアドレスの次のアドレスとなるように、ビット線アドレスカウンタ126の当該バンクアドレスに対応したカウンタおよびワード線アドレスカウンタ127の当該バンクアドレスに対応したカウンタにオフセットを与える。そして、ステップST10で、バンクアドレスカウンタ125のカウント値(バンクアドレス)をインクリメントする。その後に、ステップST11に進む。

ステップST6で、注目画素が1番目の画素であるときは、直ちにステップST11に進む。このステップST11では、注目画素が1番目の初期アクセス画素であるか否かを、一致判定部123で判定する。注目画素が1番目の初期アクセス画素であるときは、ステップST12で、バンクアドレスカウンタ125のカウント値(バンクアドレス)を、データアクセス制御部140におけるバンク指定部のカウンタの初期値にする。その後にステップST13に進む。一方、注目画素が1番目の初期アクセス画素でないときは、直ちに、ステップST13に進む。

ステップST13では、読み出しフラグ生成部129は、バンクアドレスに対応したメモリバンクの読み出しフラグRFGを読み出しを行うことを示すフラグオンの状態、例えば1にする。そして、ステップST14で、アドレス生成部128で生成されている書き込みアドレスWを、バンクアドレスに対応したメモリバンクの読み出し開始アドレスRSにする。その後に、ステップST15に進む。

ステップST15では、インクリメントされたバンクアドレスに対応した、すなわち切り替えられたメモリバンクへの画素データの連続した格納個数をカウントするために、カウンタ(カウンタB)122を1にセットする。そして、ステップST16で、アドレス生成部128で生成されている書き込みアドレスWに基づき、当該書き込みアドレスWのバンクアドレスで指定されるメモリバンクの、当該書き込みアドレスWのビット線アドレスおよびワード線アドレスで指定されるアドレス位置に、注目画素の画素データを格納する。

次に、ステップST17で、ビット線アドレスカウンタ126のバンクアドレスに対応したカウンタのカウント値(ビット線アドレス)をインクリメントする。そして、ステップST18で、ステップST17で、カウンタのカウント値が0となったとき、そのカウンタから出力されるキャリーCAにより、ワード線アドレスカウンタ127のバンクアドレスに対応したカウンタのカウント値(ワード線アドレス)をインクリメントする。その後に、ステップST19に進む。

このステップST19では、画面SRNの全ての画素の画素データが入力されたか否かを判定する。この場合、カウンタ(カウンタA)121のカウント値が、画面SRNを構成する画素の個数に等しいとき、全ての画素の画素データが入力されたと判定する。全ての画素の画素データが入力されたと判定するとき、ステップST20で、動作を終了する。一方、全ての画素の画素データが入力されていないと判定するとき、ステップST3に戻り、次の注目画素の画素データの入力を待つ。

また、上述のステップST5で、注目画素が初期アクセス画素ではないと判定するとき、ステップST21で、カウンタ(カウンタB)122のカウント値をインクリメントする。そして、ステップST22で、カウンタ(カウンタB)122のカウント値が一定数Nより大きいか否かを判定する。カウント値が一定数Nより大きいときは、ステップST23に進み、注目画素が1番目の初期アクセス画素の後の画素であるか否かを判定する。この場合、カウンタ(カウンタA)121のカウント値が、アクセスパターン情報IAPとしてのカウント値CN1より大きいとき、注目画素が1番目の初期アクセス画素の後の画素である判定する。

注目画素が1番目の初期アクセス画素の後の画素であるときは、ステップST24で、アドレス生成部128で、バンクアドレスに対応したメモリバンクの書き込み開始アドレスが既に設定されているか否かを判定する。設定されていないと判定するときは、ステップST25で、書き込み開始アドレスを、読み出し開始アドレスと同じアドレスにする。その後、ステップST26に進む。上述のステップST24で、既に設定されていると判定するときは、直ちにステップST26に進む。

このステップST26では、バンクアドレスカウンタ125のカウント値(バンクアドレス)をインクリメントする。そして、ステップST27で、アドレス生成部128で、バンクアドレスに対応した読み出し開始アドレスが既に設定されているか否かを判定する。設定されていないと判定するときは、上述したステップST14に進み、アドレス生成部128で生成されている書き込みアドレスWを読み出し開始アドレスRSにする。一方、設定されていると判定するときは、上述したステップST15に進む。

なお、上述のステップST23で、注目画素が1番目の初期アクセス画素の後でないときは、直ちに、ステップST15に進む。また、上述ステップST22で、カウンタ(カウンタB)122のカウント値が一定数Nより大きくないと判定するときは、注目画素の画素データを格納すべきメモリバンクの切り替えが必要ないので、直ちに上述したステップST16に進む。

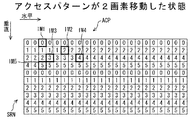

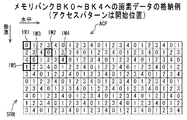

上述した初期格納時の動作により、画面SRNの各画素のデータは、図4、図5に示すように、メモリバンクBK0〜BK5に、振り分けられて格納される。

図4の「□」は上述したように1画素を示しており、その□内の数字は、その画素の画素データが格納されるメモリバンクのバンクアドレスを示している。ここで、メモリバンクBK0〜BK5のバンクアドレスは、それぞれ、0〜5である。

例えば、上述したように、画面SRNは水平方向に伸びる画素列が垂直方向に順次配列されたものであって、アクセスパターンACPは5個の画素IM1〜IM5のパターンからなっており、図4に示すアクセスパターンACPの設定位置がその開始位置であるとする。

まず、第1列の先頭画素が注目画素となるが、この画素は1番目の初期アクセス画素IM1であり、この画素からメモリバンクBK0への画素データの格納が開始される。この場合、バンクアドレスカウンタ125のカウント値(バンクアドレス)が0にあるが、これがバンク指定部のカウンタの初期値とされる。またこの場合、このメモリバンクBK0の読み出しフラグRFGは読み出しを行うことを示すフラグオンの状態、例えば1に変更されると共に、この初期アクセス画素IM1の画素データを格納すべきアドレス位置を示すアドレス(書き込みアドレスW)が、当該メモリバンクBK0の読み出し開始アドレスRSとされる(図5のメモリバンクBK0参照)。

その後、この第1列の先頭画素に続く画素が順に注目画素となり、その画素データがメモリバンクBK0に格納されていく。このメモリバンクBK0に連続して22個(一定数N)だけ画素データが格納されるまでに、注目画素が2番目の初期アクセス画素IM2とならないので、当該メモリバンクBK0には22画素の画素データが連続して格納される(図5のメモリバンクBK0の最初の22個のアドレス位置参照)。

そのため、このメモリバンクBK0の書き込み開始アドレスWSは、上述した読み出し開始アドレスRSと同じアドレスとされる(図5のメモリバンクBK0参照)。また、このメモリバンクBK0の次の書き込みアドレスWは、22個目の画素データが格納されたアドレス位置の次のアドレス位置を示すものとされる。

メモリバンクBK0に22画素の画素データが連続して格納された後、バンクアドレスがインクリメントされて、画素データを格納すべきメモリバンクはBK1となる。この場合、第2列の先頭画素が注目画素となっており、この画素からメモリバンクBK1への画素データの格納が開始される。そして、この第2列の先頭画素の画素データを格納すべきアドレス位置を示すアドレス(書き込みアドレスW)が、当該メモリバンクBK1の読み出し開始アドレスRSとされる(図5のメモリバンクBK1参照)。

その後、第2列の先頭画素に続く画素が順に注目画素となって、その画素データがメモリバンクBK1に格納されていくが、第2列の4番目の画素は2番目の初期アクセス画素IM2であるので、この画素IM2が注目画素となるとき、バンクアドレスがインクリメントされて、画素データを格納すべきメモリバンクはBK2となる。

そのため、このメモリバンクBK1には3画素の画素データが連続して格納される(図5のメモリバンクBK1の最初の3個のアドレス位置参照)。この場合、このメモリバンクBK1の書き込み開始アドレスWSは、3画素の画素データのうち最後の画素データが格納されたアドレス位置の次のアドレス位置を示すアドレスとされる(図5のメモリバンクBK1参照)。

また、このメモリバンクBK1の次の書き込みアドレスWは、仮に22画素の画素データが連続して格納されたとした場合の、22個目の画素データが格納されたアドレス位置の次のアドレス位置を示すものとされる。つまり、このメモリバンクBK1に対する書き込みアドレスWにオフセットが与えられる。なお、図5において、塗りつぶしもハッチングもされていないメモリセルMCは、初期格納時に、画素データが格納されないメモリセルMCを示している。

このように注目画素が2番目の初期アクセス画素IM2となると、メモリバンクがBK1からBK2に切り替えられるので、この画素IM2からメモリバンクBK2への画素データの格納が開始される。そして、このメモリバンクBK2の読み出しフラグRFGは読み出しを行うことを示すフラグオンの状態、例えば1に変更されると共に、この画素IM2の画素データを格納すべきアドレス位置を示すアドレス(書き込みアドレスW)が、当該メモリバンクBK2の読み出し開始アドレスRSとされる(図5のメモリバンクBK2参照)。

その後、この画素IM2に続く画素が順に注目画素となって、その画素データがメモリバンクBK2に格納されていくが、第3列の2番目の画素は3番目の初期アクセス画素IM3であるので、この画素IM3が注目画素となるとき、バンクアドレスがインクリメントされて、画素データを格納すべきメモリバンクはBK3となる。

そのため、メモリバンクBK2には20画素の画素データが連続して格納される(図5のメモリバンクBK2の最初の20個のアドレス位置参照)。この場合、このメモリバンクBK2の書き込み開始アドレスWSは、20画素の画素データのうち最後の画素データが格納されたアドレス位置の次のアドレス位置を示すアドレスとされる(図5のメモリバンクBK2参照)。また、このメモリバンクBK2の次の書き込みアドレスWは、上述したメモリバンクBK1の場合と同様に、仮に22画素の画素データが連続して格納されたとした場合の、22個目の画素データが格納されたアドレス位置の次のアドレス位置を示すものとされる。

このように注目画素が3番目の初期アクセス画素IM3となると、メモリバンクがBK2からBK3に切り替えられるので、この画素IM3からメモリバンクBK3への画素データの格納が開始される。そして、このメモリバンクBK3の読み出しフラグRFGは読み出しを行うことを示すフラグオンの状態、例えば1に変更されると共に、この画素IM3の画素データを格納すべきアドレス位置を示すアドレス(書き込みアドレスW)が、当該メモリバンクBK3の読み出し開始アドレスRSとされる(図5のメモリバンクBK3参照)。

その後、この画素IM3に続く画素が順に注目画素となって、その画素データがメモリバンクBK3に格納されていくが、第3列の6番目の画素は4番目の初期アクセス画素IM4であるので、この画素IM4が注目画素となるとき、バンクアドレスがインクリメントされて、画素データを格納すべきメモリバンクはBK4となる。

そのため、メモリバンクBK3には4画素の画素データが連続して格納される(図5のメモリバンクBK3の最初の4個のアドレス位置参照)。この場合、このメモリバンクBK3の書き込み開始アドレスWSは、4画素の画素データのうち最後の画素データが格納されたアドレス位置の次のアドレス位置を示すアドレスとされる(図5のメモリバンクBK3参照)。また、このメモリバンクBK3の次の書き込みアドレスWは、上述したメモリバンクBK1,BK2の場合と同様に、仮に22画素の画素データが連続して格納されたとした場合の、22個目の画素データが格納されたアドレス位置の次のアドレス位置を示すものとされる。

このように注目画素が4番目の初期アクセス画素IM4となると、メモリバンクがBK3からBK4に切り替えられるので、この画素IM4からメモリバンクBK4への画素データの格納が開始される。そして、このメモリバンクBK4の読み出しフラグRFGは読み出しを行うことを示すフラグオンの状態、例えば1に変更されると共に、この画素IM4の画素データを格納すべきアドレス位置を示すアドレス(書き込みアドレスW)が、当該メモリバンクBK4の読み出し開始アドレスRSとされる(図5のメモリバンクBK4参照)。

その後、この画素IM4に続く画素が順に注目画素となって、その画素データがメモリバンクBK4に格納されていくが、第4列の1番目の画素は5番目の初期アクセス画素IM5であるので、この画素IM5が注目画素となるとき、バンクアドレスがインクリメントされて、画素データを格納すべきメモリバンクはBK5となる。

そのため、メモリバンクBK4には17画素の画素データが連続して格納される(図5のメモリバンクBK4の最初の17個のアドレス位置参照)。この場合、このメモリバンクBK4の書き込み開始アドレスWSは、17画素の画素データのうち最後の画素データが格納されたアドレス位置の次のアドレス位置を示すアドレスとされる(図5のメモリバンクBK4参照)。また、このメモリバンクBK4の次の書き込みアドレスWは、上述したメモリバンクBK1〜BK3の場合と同様に、仮に22画素の画素データが連続して格納されたとした場合の、22個目の画素データが格納されたアドレス位置の次のアドレス位置を示すものとされる。

このように注目画素が5番目の初期アクセス画素IM5となると、メモリバンクがBK4からBK5に切り替えられるので、この画素IM5からメモリバンクBK5への画素データの格納が開始される。そして、このメモリバンクBK5の読み出しフラグRFGは読み出しを行うことを示すフラグオンの状態、例えば1に変更されると共に、この画素IM5の画素データを格納すべきアドレス位置を示すアドレス(書き込みアドレスW)が、当該メモリバンクBK5の読み出し開始アドレスRSとされる(図5のメモリバンクBK5参照)。

その後、この画素IM5に続く画素が順に注目画素となって、その画素データがメモリバンクBK5に格納されていく。5番目の初期アクセス画素IM5が最後の初期アクセス画素であるため、メモリバンクBK5に連続して22個(一定数N)だけ画素データが格納されるまでに注目画素が初期アクセス画素となることはなく、当該メモリバンクBK5には22画素の画素データが連続して格納される(図5のメモリバンクBK5の最初の22個のアドレス位置参照)。

そのため、このメモリバンクBK5の書き込み開始アドレスWSは、上述した読み出し開始アドレスRSと同じアドレスとされる(図5のメモリバンクBK5参照)。また、このメモリバンクBK5の次の書き込みアドレスWは、22個目の画素データが格納されたアドレス位置の次のアドレス位置を示すものとされる。

メモリバンクBK5に22画素の画素データが連続して格納された後、バンクアドレスがインクリメントされて、画素データを格納すべきメモリバンクは再びBK0となる。この場合、第5列の先頭画素が注目画素となっており、この画素からメモリバンクBK0への画素データの格納が開始される。その後、この第5列の先頭画素に続く画素が順に注目画素となって、その画素データがメモリバンクBK0に格納されていく。

この場合、メモリバンクBK0に連続して22個(一定数N)だけ画素データが格納されるまでに注目画素がアクセス画素となることはなく、当該メモリバンクBK0には22画素の画素データが連続して格納される(図5のメモリバンクBK0の2番目の22個のアドレス位置参照)。この場合、このメモリバンクBK0の次の書き込みアドレスWは、22個目の画素データが格納されたアドレス位置の次のアドレス位置を示すものとされる。

以下、同様にして、22画素の画素データが格納される毎に、画素データを格納すべきメモリバンクが切り替えられ、注目画素の画素データが各メモリバンクに22個ずつ格納されていく(図5のメモリバンクBK1〜BK5の2番目の22個のアドレス位置参照)。

図1に戻って、データアクセス制御部140は、図示しない制御装置から入力端子150を介して供給される制御信号SCLに基づいて動作する。このデータアクセス制御部140は、上述したように、アクセスパターンACPの各設定位置で、このアクセスパターンACPで特定される5個のアクセス画素IM1〜IM5の画素データを、6個のメモリバンクBK0〜BK5のいずれかから同時に読み出すための制御を行う。

つまり、このデータアクセス制御部140は、アクセスパターンACPの設定位置が所定位置にあるとき、この所定位置におけるアクセスパターンACPで特定される5個のアクセス画素IM1〜IM5の画素データを6個のメモリバンクBK0〜BK5のいずれかから同時に読み出す。

また、このデータアクセス制御部140は、アクセスパターンACPの設定位置が画素列方向に移動した際に、その設定位置におけるアクセスパターンACPで特定される5個のアクセス画素IM1〜IM5の画素データがそれぞれ異なるメモリバンクに格納されているように、読み出した画素データのいずれかあるいは全部を、その画素データが格納されていたメモリバンクの1つ前のメモリバンクに格納する。

データアクセス制御部140についてさらに詳細に説明する。図6は、このデータアクセス制御部140の構成を示している。このデータアクセス制御部140は、開始アドレス保持部141と、カウンタ(カウンタA)142と、カウンタ(カウンタB)143と、バンク指定部144と、アドレスカウンタフラグ制御部145と、書き込みアドレスカウンタ146と、読み出しアドレスカウンタ147と、書き込みアドレス生成部148と、読み出しアドレス生成部149と、読み出しフラグ生成部150と、書き込みフラグ生成部151とを有している。

カウンタ(カウンタA)142は、アクセスパターンACPの設定位置を示すカウント値を出力する。このカウンタ142には、アクセスパターンACPの設定位置を移動するための移動クロックMCKが供給される。この移動クロックMCKは、上述した制御信号SCLのひとつを構成しており、図示しない制御装置から供給される。このカウンタ142は、最初にそのカウント値が0とされ、その後アクセスパターンACPの設定位置を開始位置とするとき最初の移動クロックMCKでインクリメントされてカウント値が1となり、その後はこの設定位置が画素列方向に1画素ずつ移動する毎に、移動クロックMCKでインクリメントされていく。

カウンタ(カウンタB)143は、アクセスパターンACPの設定位置の移動に際し、一定数N毎の設定位置で、いま何番目の設定位置にあるかを示すカウント値を出力する。この実施の形態では、この一定数Nは、水平方向の画素列の画素数と同じ22である。このカウンタ143には、上述したカウンタ(カウンタA)142と同様に、移動クロックMCKが供給される。このカウンタ143は、最初にそのカウント値が0とされ、その後アクセスパターンACPの設定位置を開始位置とするとき最初の移動クロックMCKでインクリメントされてカウント値が1となり、その後はこの設定位置が画素列方向に1画素ずつ移動する毎に、移動クロックMCKでインクリメントされていく。ただし、アクセスパターンACPが一定数Nだけ移動し、そのカウント値がNとなった場合、そのカウント値は0とされ、次の一定数Nのカウントに備えられる。

バンク指定部144は、アクセスパターンACPの設定位置を一定数Nだけ移動する毎に設定される、各メモリバンクBK0〜BK5に対する次の読み出し開始アドレスRSおよび次の書き込み開始アドレスWSのうち、一定数Nだけそれらのアドレスを進めるオフセット処理を行うメモリバンクを指定するカウント値を出力する。このバンク指定部144には、カウンタ(カウンタB)143のカウント値が供給される。また、このバンク指定部144には、上述したデータ格納制御部120のアドレス生成部128で生成された初期値BSが供給される。

このバンク指定部144はカウンタ(図示せず)を備えている。最初は、そのカウント値が初期値BSにセットされる。その後、カウンタ(カウンタB)143のカウント値がNから0に変化する毎に、そのカウント値がインクリメントされる。このバンク指定部144のカウンタは、カウント値5の次はカウント値0となり、6進カウンタの構成となっている。このバンク指定部144のカウンタのカウント値0〜5は、それぞれ、メモリバンクBK0〜BK5を指定する。

開始アドレス保持部141は、それぞれのメモリバンクBK0〜BK5に対する読み出し開始アドレスRSおよび書き込み開始アドレスWSを保持する。この開始アドレス保持部141には、上述したデータ格納制御部120のアドレス生成部128で生成された、それぞれのメモリバンクBK0〜BK5に対する読み出し開始アドレスRSおよび書き込み開始アドレスWSが供給され、これが初期値として保持される。

この開始アドレス保持部141は、それぞれのメモリバンクBK0〜BK5に対する次の書き込み開始アドレスWSとして、1つ前のメモリバンクの書き込みフラグWFGがフラグオフの状態、例えば0となったとき、そのとき保持されている読み出し開始アドレスRSを保持する。また、この開始アドレス保持部141は、それぞれのメモリバンクBK0〜BK5に対する次の読み出し開始アドレスRSとして、1つ前のメモリバンクの書き込みフラグWFGがフラグオフの状態、例えば0となったとき、そのときの読み出しアドレスを保持する。

書き込みアドレスカウンタ146は、6個のメモリバンクBK0〜BK5にそれぞれ対応した6個のカウンタ146-0〜146-5からなっている。これらカウンタ146-0〜146-5のそれぞれは、ビット線アドレスを示すカウント値を得るためのビット線アドレスカウンタと、ワード線アドレスを示すカウント値を得るためのワード線アドレスカウンタとからなっている(図2のビット線アドレスカウンタ126およびワード線アドレスカウンタ127参照)。カウンタ146-0〜146-5は、アドレスカウンタフラグ制御部145の制御のもと、それぞれのメモリバンクBK0〜BK5に対する書き込みアドレス(ビット線アドレスおよびワード線アドレス)を示すカウント値を出力する。

読み出しアドレスカウンタ147は、6個のメモリバンクBK0〜BK5にそれぞれ対応した6個のカウンタ147-0〜147-5からなっている。これらカウンタ147-0〜147-5のそれぞれも、ビット線アドレスを示すカウント値を得るためのビット線アドレスカウンタと、ワード線アドレスを示すカウント値を得るためのワード線アドレスカウンタとからなっている。カウンタ147-0〜147-5は、アドレスカウンタフラグ制御部145の制御のもと、それぞれのメモリバンクBK0〜BK5に対する読み出しアドレス(ビット線アドレスおよびワード線アドレス)を示すカウント値を出力する。

読み出しフラグ生成部150は、それぞれのメモリバンクBK0〜BK5に対する読み出しフラグRFGを生成する。この読み出しフラグ生成部150には、上述したデータ格納制御部120の読み出しフラグ生成部129で生成された、それぞれのメモリバンクBK0〜BK5に対する読み出しフラグRFGが供給される。この読み出しフラグ生成部150は、アドレスカウンタフラグ制御部145の制御のもと、それぞれのメモリバンクBK0〜BK5に対する読み出しフラグRFGを生成する。

書き込みフラグ生成部151は、それぞれのメモリバンクBK0〜BK5に対する書き込みフラグWFGを生成する。この書き込みフラグ生成部151は、アドレスカウンタフラグ制御部145の制御のもと、それぞれのメモリバンクBK0〜BK5に対する書き込みフラグWFGを生成する。

アドレスカウンタフラグ制御部145は、上述した書き込みアドレスカウンタ146、読み出しアドレスカウンタ147、読み出しフラグ生成部150および書き込みフラグ生成部151の動作を制御する。このアドレスカウンタフラグ制御部145には、アクセスパターンACPの設定位置を移動するための移動クロックMCK、カウンタ(カウンタB)143のカウント値、バンクカウンタ144のカウント値、書き込みアドレスカウンタ146を構成する各カウンタ146-0〜146-5のカウント値(書き込みアドレス)、読み出しアドレスカウンタ147を構成する各カウンタ147-0〜147-5のカウント値(読み出しアドレス)、読み出しフラグ生成部150で生成される読み出しフラグRFGおよび書き込みフラグ生成部151で生成される書き込みフラグWFGが供給される。

このアドレスカウンタフラグ制御部145は、最初およびアクセスパターンACPの設定位置を一定数Nだけ移動する毎に、開始アドレス保持部141に保持されている、それぞれのメモリバンクBK0〜BK5に対する読み出し開始アドレスRSおよび書き込み開始アドレスWSをカウンタ146,147にセットする。この場合、アドレスカウンタフラグ制御部145は、読み出しアドレスカウンタ147を構成するカウンタ147-0〜147-5のカウント値(読み出しアドレス)を、それぞれ、メモリバンクBK0〜BK5に対する読み出し開始アドレスRSと等しくなるようにセットし、書き込みアドレスカウンタ146を構成するカウンタ146-0〜146-5のカウント値(読み出しアドレス)を、それぞれ、メモリバンクBK0〜BK5に対する書き込み開始アドレスWSと等しくなるようにセットする。

ただしこの場合、アクセスパターンACPの設定位置を一定数Nだけ移動する毎の読み出し開始アドレスRSおよび書き込み開始アドレスWSのセットに関しては、バンク指定部144のカウンタのカウント値で指定されるメモリバンクに対応する開始アドレスRS,WSを一定数Nだけ進めるオフセット処理をさらに行う。この場合、アドレスカウンタフラグ制御部145は、読み出しアドレスカウンタ147を構成するカウンタ147-0〜147-5のうち、バンクカウンタ144のカウント値で特定されるメモリバンクに対応するカウンタのカウント値を一定数Nだけ進めたカウント値に再セットすると共に、書き込みアドレスカウンタ146を構成するカウンタ146-0〜146-5のうち、バンクカウンタ144のカウント値で特定されるメモリバンクに対応するカウンタのカウント値を一定数Nだけ進めたカウント値に再セットする。

また、アドレスカウンタフラグ制御部145は、アクセスパターンACPの各設定位置で、カウンタ147-0〜147-5のうち、画素データの読み出しが行われるメモリバンクに対応するカウンタをインクリメントする。そして、このアドレスカウンタフラグ制御部145は、それぞれのカウンタ147-0〜147-5に対し、読み出し開始アドレスRSが一定数Nの(R−1)倍を越えると共にR倍以下にあるとき(Rは正の整数)、インクリメントされたカウント値(読み出しアドレス)が一定数NのR倍を越えないときは、インクリメントされたカウント値をそのままとするが、インクリメントされたカウント値が一定数NのR倍を越えるときは、インクリメントされたカウント値から一定数Nだけ戻したカウント値とするオフセット処理をする。

また、アドレスカウンタフラグ制御部145は、アクセスパターンACPの各設定位置で、カウンタ146-0〜146-5のうち、画素データの書き込みが行われるメモリバンクに対応するカウンタをインクリメントする。そして、このアドレスカウンタフラグ制御部145は、それぞれのカウンタ146-0〜146-5に対し、書き込み開始アドレスWSが一定数Nの(R−1)倍を越えると共にR倍以下にあるとき(Rは正の整数)、インクリメントされたカウント値(書き込みアドレス)が一定数NのR倍を越えないときは、インクリメントされたカウント値をそのままとするが、インクリメントされたカウント値が一定数NのR倍を越えるときは、インクリメントされたカウント値から一定数Nだけ戻したカウント値とするオフセット処理をする。

また、読み出しフラグ生成部150は、最初、それぞれのメモリバンクBK0〜BK5に対する読み出しフラグRFGを、上述したデータ格納制御部120の読み出しフラグ生成部129から供給される、それぞれのメモリバンクBK0〜BK5に対する読み出しフラグRFGと同じ状態とする。すなわち、開始位置に設定されたアクセスパターンACPで特定される5個の初期アクセス画素IM1〜IM5の画素データのいずれかが格納されているメモリバンクに対する読み出しフラグRFGをフラグオンの状態とし、その他のメモリバンクに対する読み出しフラグRFGをフラグオフの状態とする。

また、この読み出しフラグ生成部150は、アクセスパターンACPの設定位置が一定数Nだけ移動する毎に、それぞれのメモリバンクBK0〜BK5に対する読み出しフラグRFGを、1つ前のメモリバンクの読み出しフラグRFGとする。この場合、メモリバンクBK0,BK1,BK2,BK3,BK4,BK5の1つ前のメモリバンクは、それぞれ、メモリバンクBK5,BK0,BK1,BK2,BK3,BK4である。

また、書き込みフラグ生成部151は、最初およびアクセスパターンACPの設定位置を一定数Nだけ移動する毎に、読み出し開始アドレスRSと書き込み開始アドレスWSが同じであるメモリバンクに対応する書き込みフラグWFGを書き込みを行わないことを示すフラグオフの状態、例えば0とし、その他のメモリバンクに対応する書き込みフラグWFGを書き込みを行うことを示すフラグオンの状態、例えば1とする。

また、この書き込みフラグ制御部151は、アクセスパターンACPの各設定位置で、次の書き込みアドレスが読み出し開始アドレスRSと同じになるメモリバンクに対する書き込みフラグWFGを、フラグオンの状態からフラグオフの状態とする。

書き込みアドレス生成部148は、それぞれのメモリバンクBK0〜BK5に対する書き込みアドレスWを生成する。この書き込みアドレス生成部148には、書き込み込みアドレスカウンタ146を構成する各カウンタ146-0〜146-5のカウント値(ビット線アドレスおよびワード線アドレス)が供給される。書き込みアドレス生成部148は、カウンタ146-0〜146-5のカウント値(ビット線アドレスおよびワード線アドレス)に、それぞれ、メモリバンクBK0〜BK5のバンクアドレスを合成することで、それぞれのメモリバンクBK0〜BK5に対する書き込みアドレスWを生成する。

読み出しアドレス生成部149は、それぞれのメモリバンクBK0〜BK5に対する読み出しアドレスRを生成する。この読み出しアドレス生成部149には、読み出しアドレスカウンタ147を構成する各カウンタ147-0〜147-5のカウント値(ビット線アドレスおよびワード線アドレス)が供給される。読み出しアドレス生成部149は、カウンタ147-0〜147-5のカウント値(ビット線アドレスおよびワード線アドレス)に、それぞれ、メモリバンクBK0〜BK5のバンクアドレスを合成することで、それぞれのメモリバンクBK0〜BK5に対する読み出しアドレスRを生成する。

次に、図6に示すデータアクセス制御部140の制御によるデータアクセス時の動作を、図7のフローチャートを用いて説明する。なお、データアクセス制御部140は、例えばマイクロプロセッサで構成され、図示しないプログラムメモリに格納されたデータアクセス制御プログラムに従って制御処理をする。

ステップST31で、動作を開始し、ステップST32で、アドレスカウンタフラグ制御部145は、読み出し開始アドレスRSおよび書き込み開始アドレスWSをセットする。この場合、アドレスカウンタフラグ制御部145は、読み出しアドレスカウンタ147を構成するカウンタ147-0〜147-5のカウント値(読み出しアドレス)を、それぞれ、開始アドレス保持部141に初期値として保持されている、メモリバンクBK0〜BK5に対する読み出し開始アドレスRSと等しくなるようにセットし、書き込みアドレスカウンタ146を構成するカウンタ146-0〜146-5のカウント値(読み出しアドレス)を、それぞれ、開始アドレス保持部141に初期値として保持されている、メモリバンクBK0〜BK5に対する書き込み開始アドレスWSと等しくなるようにセットする。

またこの場合、読み出しフラグ生成部150は、それぞれのメモリバンクBK0〜BK5に対する読み出しフラグRFGを、上述したデータ格納制御部120の読み出しフラグ生成部129から供給される、それぞれのメモリバンクBK0〜BK5に対する読み出しフラグRFGと同じ状態とする。すなわち、開始位置に設定されたアクセスパターンACPで特定される5個の初期アクセス画素IM1〜IM5の画素データのいずれかが格納されているメモリバンクに対する読み出しフラグRFGをフラグオンの状態とし、その他のメモリバンクに対する読み出しフラグRFGをフラグオフの状態とする。

またこの場合、書き込みフラグ生成部151は、開始アドレス保持部141に初期値として保持されているメモリバンクBK0〜BK5に対する読み出し開始アドレスRSおよび書き込み開始アドレスWSに基づいて、読み出し開始アドレスRSと書き込み開始アドレスWSが同じであるメモリバンクに対応する書き込みフラグWFGを書き込みを行わないことを示すフラグオフの状態、例えば0とし、その他のメモリバンクに対応する書き込みフラグWFGを書き込みを行うことを示すフラグオンの状態、例えば1とする。

また、このステップST32で、カウンタ(カウンタA)142のカウント値およびカウンタ(カウンタB)143のカウント値をそれぞれ0にする。また、バンク指定部144のカウンタのカウント値を初期値BSにする。

次に、ステップST33で、移動クロックMCKにより、カウンタ(カウンタA)142をインクリメントし、ステップST34で、移動クロックMCKによりカウンタ(カウンタB)143をインクリメントする。そして、ステップST35で、メモリバンクBK0〜BK5のうち、読み出しフラグRFGが1となっている5個のメモリバンクの、読み出しアドレス生成部149で生成された読み出しアドレスRで示されるアドレス位置から、アクセスパターンACPで特定される5個のアクセス画素の画素データDo1〜Do5を読み出して出力する。

次に、ステップST36で、各メモリバンクBK0〜BK5につき、1つ前のメモリバンクの書き込みフラグWFGが1であるか否かを判定する。1つ前のメモリバンクの書き込みフラグWFGが1であるメモリバンクについてはステップST37に進む。このステップST37では、そのメモリバンクよりステップST35で読み出された画素データを、1つ前のメモリバンクの、書き込みアドレス生成部148で生成された書き込みアドレスWで示されるアドレス位置に書き込む。そして、ステップST38で、アドレスカウンタフラグ制御部145は、書き込みアドレスカウンタ146を構成するカウンタ146-0〜146-5のうち、ステップST37で、画素データが書き込まれたメモリバンクに対応するカウンタのカウント値(書き込みアドレス)をインクリメントする。その後に、ステップST39に進む。

上述のステップST36で、1つ前のメモリバンクの書き込みフラグWFGが0であるメモリバンクについてはステップST40進む。このステップST40では、開始アドレス保持部141に、次の開始アドレスRS,WSが既に保持されているか否かを判定する。次の開始アドレスRS,WSがまだ保持されていないと判定するときは、ステップST41に進む。このステップST41で、開始アドレス保持部141は、保持されている読み出し開始アドレスRSを次の書き込み開始アドレスWSとして保持する。そして、ステップST42で、読み出しアドレスカウンタ147を構成するカウンタ147-0〜147-5のうち、対応するメモリバンクのカウンタのカウント値(読み出しアドレス)を、次の読み出し開始アドレスRSとして保持する。その後にステップST39に進む。なお、ステップST40で、次の開始アドレスRS,WSが既に保持されていると判定するときは、直ちにステップST39に進む。

このステップST39では、アドレスカウンタフラグ制御部145は、読み出しアドレスカウンタ147を構成するカウンタ147-0〜147-5のうち、ステップST35で、画素データDo1〜Do5が読み出されたメモリバンクに対応するカウンタのカウント値(読み出しアドレス)をインクリメントする。

次に、ステップST43で、開始アドレスRS,WSが一定数Nの(R−1)倍を越えると共にR倍以下にあるとき(Rは正の整数)、各メモリバンクBK0〜BK5につき、読み出しアドレスまたは書き込みアドレスが一定数NのR倍を越えたか否かを判定する。上述したように、この実施の形態でNは22である。

読み出しアドレスまたは書き込みアドレスが一定数NのR倍を越えたと判定するとき、アドレスカウンタフラグ制御部145は、ステップST44で、それぞれ、読み出しアドレスカウンタ147を構成するカウンタ147-0〜147-5のうち、対応するメモリバンクのカウンタのカウント値(読み出しアドレス)または書き込みアドレスカウンタ146を構成するカウンタ146-0〜146-5のうち、対応するメモリバンクのカウンタのカウント値(書き込みアドレス)を、一定数Nだけ戻したカウント値とするオフセット処理をする。その後に、ステップST45に進む。ステップST43で、読み出しアドレスまたは書き込みアドレスが一定数NのR倍を越えていないと判定するときは、直ちにステップST45に進む。

このステップST45では、各メモリバンクBK0〜BK5につき、書き込みアドレスカウンタ146を構成するカウンタ146-0〜146-5のカウント値(書き込みアドレス)が読み出し開始アドレスRSと同じであるか否かを判定する。同じであると判定するメモリバンクについては、ステップST46に進む。このステップST46では、書き込みフラグ生成部151は、対応するメモリバンクの書き込みフラグRFGを0にする。その後に、ステップST47に進む。一方、ステップST45で、同じでないと判定するときは、直ちにステップST47に進む。

このステップST47では、全てアクセスしたか否か、つまりアクセスパターンACPが開始位置から終了位置まで移動したか否かを判定する。この場合、カウンタ(カウンタA)142のカウント値が終了位置を示す値となるとき、全てアクセスしたと判定する。全てアクセスしたと判定するとき、ステップST48で、動作を終了する。

ステップST47で、全てアクセスしていないと判定するときは、ステップST49に進む。このステップST49では、カウンタ(カウンタB)143のカウント値が一定数Nであるか否かを判定する。カウント値が一定数Nであるときは、ステップST50で、カウンタ(カウンタB)143のカウント値を0にする。

次に、ステップST51で、次の読み出し開始アドレスRSおよび次の書き込み開始アドレスWSをセットする。この場合、アドレスカウンタフラグ制御部145は、読み出しアドレスカウンタ147を構成するカウンタ147-0〜147-5のカウント値(読み出しアドレス)を、それぞれ、開始アドレス保持部141に保持されている、メモリバンクBK0〜BK5に対する次の読み出し開始アドレスRSと等しくなるようにセットし、書き込みアドレスカウンタ146を構成するカウンタ146-0〜146-5のカウント値(読み出しアドレス)を、それぞれ、開始アドレス保持部141に保持されている、メモリバンクBK0〜BK5に対する次の書き込み開始アドレスWSと等しくなるようにセットする。

次に、ステップST52で、バンク指定部144のカウンタのカウント値で指定されるメモリバンクの開始アドレスRS,WSを、一定数Nだけ進めるオフセット処理をする。この場合、アドレスカウンタフラグ制御部145は、読み出しアドレスカウンタ147を構成するカウンタ147-0〜147-5のうち、バンク指定部144のカウンタのカウント値で指定されるメモリバンクに対応するカウンタのカウント値を一定数Nだけ進めたカウント値に再セットすると共に、書き込みアドレスカウンタ146を構成するカウンタ146-0〜146-5のうち、バンク指定部144のカウンタのカウント値で指定されるメモリバンクに対応するカウンタのカウント値を一定数Nだけ進めたカウント値に再セットする。

次に、ステップST53で、バンク指定部144のカウンタのカウント値をインクリメントする。そして、ステップST54で、それぞれのメモリバンクBK0〜BKに対する書き込みフラグWFGをセットする。この場合、書き込みフラグ生成部151は、読み出し開始アドレスRSと書き込み開始アドレスWSが同じであるメモリバンクに対応する書き込みフラグWFGを0とし、その他のメモリバンクに対応する書き込みフラグWFGを1とする。

次に、ステップST55で、それぞれのメモリバンクBK0〜BKに対する読み出しフラグRFGをセットする。この場合、読み出しフラグ生成部150は、それぞれのメモリバンクBK0〜BK5に対する読み出しフラグRFGを、1つ前のメモリバンクの読み出しフラグRFGとするシフト処理をする。その後に、ステップST33に戻り、アクセスパターンACPの次の設定位置の処理に移る。上述したステップST49で、カウンタ(カウンタB)143のカウント値が一定数Nと同じでないときは、直ちにステップST33に戻り、アクセスパターンACPの次の設定位置の処理に移る。

上述したデータアクセス時の動作をさらに説明する。上述したように、初期格納時の動作により、画面SRNの各画素のデータは、上述した図4、図5に示すように、メモリバンクBK0〜BK5に、振り分けられて格納されている。

動作開始時に、メモリバンクBK0〜BK5の読み出し開始アドレスRSおよび書き込み開始アドレスWSがセットされる。この場合、メモリバンクBK0〜BK5の開始アドレスRS,WSは、図9に示すように、データ格納制御部120のアドレス生成部128で生成された開始アドレスRS,WSと同じアドレスにセットされる。そして、これらメモリバンクBK0〜BK5の初期状態の読み出しアドレスRおよび書き込みアドレスWは、図9に示すように、それぞれ、読み出し開始アドレスRSおよび書き込み開始アドレスWSと同じアドレスとなる。

また動作開始時に、読み出しフラグRFGおよび書き込みフラグWFGがセットされる。この場合、メモリバンクBK0〜BK5の読み出しフラグRFGは、図9に示すように、データ格納制御部120の読み出しフラグ生成部129で生成された読み出しフラグRFGと同じ状態にセットされる。つまり、メモリバンクBK0,BK2〜BK5の読み出しフラグRFGは読み出しを行うことを示すフラグオンの状態、例えば1とされ、その他のメモリバンクBK1は読み出しを行わないことを示すフラグオフの状態、例えば0とされる。

また、メモリバンクBK0〜BK5の書き込みフラグRFGは、図9に示すように、メモリバンクBK0,BK5については、書き込み開始アドレスRSと読み出し開始アドレスWSが同じであることから、書き込みを行わないことを示すフラグオフの状態、例えば0とされ、またその他のバンクBK1〜BK4については書き込みを行うことを示すフラグオンの状態、例えば1とされる。

カウンタ(カウンタA)142のカウントが開始され、図8に示すように、アクセスパターンACPの設定位置が開始位置とされると、メモリバンクBK0〜BK5のうち、読み出しフラグRFGが1となっている5個のメモリバンクBK0,BK2〜BK5の、読み出しアドレスRで示されるアドレス位置から、開始位置のアクセスパターンACPで特定される5個の初期アクセス画素IM1〜IM5の画素データDo1〜Do5が同時に読み出される。そして、メモリバンクBK0,BK2〜BK5の読み出しアドレスRはそれぞれインクリメントされる。

メモリバンクBK2〜BK5から読み出された画素データは、図10に示すように、1つ前のメモリバンクBK1〜BK4の書き込みフラグWRGが1であるので、その書き込み込みアドレスWで示されるアドレス位置に書き込まれる。そして、メモリバンクBK1〜BK4の書き込みアドレスWはそれぞれインクリメントされる。

メモリバンクBK0,BK1については、1つ前のメモリバンクBK5,BK0の書き込みフラグWRGが0であるので、読み出し開始アドレスRSが次の書き込み開始アドレスWSとして保持され、また読み出しアドレスRが次の読み出し開始アドレスRSとして保持される。

その後、移動クロックMCKの入力に伴ってアクセスパターンACPの設定位置が画素列方向(水平方向)に1画素移動する毎に、上述したと同様に、アクセスパターンACPで特定される5個のアクセス画素IM1〜IM5の画素データDo1〜Do5が同時に読み出され、読み出しアドレスRのインクリメント、読み出された画素データの他のメモリバンクへの移動、書き込みアドレスWのインクリメント、次の開始アドレスWS,RSの保持の処理が行われる。

この場合、図11に示すように、アクセスパターンACPの設定位置が開始位置から画素列方向に2画素移動したところでは、メモリバンクBK2のインクリメントされた書き込みアドレスWが23となって一定数N=22を越えるので、図12に示すように、メモリバンクBK2の書き込みアドレスWは一定数N=22だけ戻され、またこれにより書き込みアドレスWが読み出し開始アドレスRSと同じになるので、メモリバンクBK2の書き込みフラグWFGは0に変更される。

同様に、アクセスパターンACPの設定位置の移動に伴って、所定のメモリバンクの書き込みアドレスWまたは読み出しアドレスRが一定数N=22を越えるときは、その所定のメモリバンクの書き込みアドレスWまたは読み出しアドレスRは一定数N=22だけ戻され、またこれにより書き込みアドレスWが読み出し開始アドレスRSと同じになるとき、その所定のメモリバンクバンクの書き込みフラグWFGは0に変更される。

図13は、アクセスパターンACPの設定位置が開始位置から22画素移動した状態を示しており、この場合アクセスパターンACPの設定位置は開始位置から垂直方向に1画素移動した位置となる。図14は、そのときの各メモリバンクBK0〜BK5の状態を示しており、各メモリバンクBK0〜BK5の次の読み出し開始アドレスRS′および読み出し開始アドレスWS′は、それぞれ図示の位置となる。

図15は、上述したようにアクセスパターンACPの設定位置が開始位置から22画素移動した後に、読み出し開始アドレスRSおよび書き込み開始アドレスWSがセットされると共に、読み出しフラグRFGおよび書き込みフラグWFGがセットされた状態を示している。

この場合、メモリバンクBK0〜BK5の開始アドレスRS,WSは、それぞれ保持されている次の開始アドレスRS′,WS′(図14参照)とされる。ただしこの場合、バンク指定部144のカウンタのカウント値は0にあるので、メモリバンクBK0に対応する開始アドレスRS,WSが、さらに一定数N=22だけ進めるようにオフセット処理される。

また、メモリバンクBK0〜BK5の書き込みフラグWFGは、メモリバンクBK0,BK1については書き込み開始アドレスRSと読み出し開始アドレスWSが同じであることから、書き込みを行わないことを示すフラグオフの状態、例えば0とされ、またその他のバンクBK2〜BK5については書き込みを行うことを示すフラグオンの状態、例えば1とされる。

また、メモリバンクBK0〜BK5の読み出しフラグRFGは、それぞれ、1つ前のメモリバンクBK5〜BK4の読み出しフラグRFGとされる。つまり、メモリバンクBK0,BK1,BK3〜BK5の読み出しフラグRFGは読み出しを行うことを示すフラグオンの状態、例えば1とされ、その他のメモリバンクBK2の読み出しフラグRFGは読み出しを行わないことを示すフラグオフの状態、例えば0とされる。なお、図15に示す、メモリバンクBK0〜BK5の次の読み出し開始アドレスRS′および次の書き込み開始アドレスWS′は、アクセスパターンACPの設定位置をさらに22画素移動した後のものを示している。

アクセスパターンACPの設定位置が上述の図13に示す位置に移動した後、上述したように開始アドレスRS,WS、およびフラグRFG,WFGのセットが行われ、メモリバンクBK0〜BK5のうち、読み出しフラグRFGが1となっている5個のメモリバンクBK0,BK1,BK3〜BK5の、読み出しアドレスRで示されるアドレス位置から、アクセスパターンACPで特定される5個のアクセス画素IM1〜IM5の画素データDo1〜Do5が同時に読み出される。その後、移動クロックMCKの入力に伴ってアクセスパターンACPの設定位置が画素列方向(水平方向)に1画素移動する毎に、上述したと同様に、アクセスパターンACPで特定される5個のアクセス画素IM1〜IM5の画素データDo1〜Do5が同時に読み出される。

以下、アクセスパターンACPの設定位置が一定数N=22だけ移動する毎に、上述したと同様の動作が繰り返され、アクセスパターンACPの設定位置が終了位置となるまで、各設定位置で、アクセスパターンACPで特定される5個のアクセス画素IM1〜IM5の画素データDo1〜Do5が同時に読み出される。

図1に示すデータアクセス装置100によれば、初期格納時に、注目画素の画素データを最初のメモリバンクに格納することが開始された後、注目画素が5個の初期アクセス画素のいずれかになるとき、あるいは同一のメモリバンクに一定数N=22の画素データを連続して格納したとき、注目画素の画素データを格納するメモリバンクが順次切り替えられるものであり、5個の初期アクセス画素IM1〜IM5の画素データはそれぞれ異なるメモリバンクに格納された状態となって同時アクセスが可能となり、また6個のメモリバンクBK0〜BK5に格納される画素データの数が平均化されるため、各メモリバンクBK0〜BK5の容量を小さくできる。

また、図1に示すデータアクセス装置100によれば、データアクセス時に、アクセスパターンACPの設定位置が所定位置にあるとき、この所定位置におけるアクセスパターンで特定される5個のアクセス画素IM1〜IM5の画素データDo1〜Do5が6個のメモリバンクBK0〜BK5のいずれかから同時に読み出されると共に、この設定位置が移動した際に、この設定位置のアクセスパターンACPで特定される5個のアクセス画素IM1〜IM5の画素データDo1〜Do5がそれぞれ異なるメモリバンクに格納されているように、読み出された画素データDo1〜Do5のいずれかあるいは全部が、その画素データDo1〜Do5が格納されていたメモリバンクの1つ前のメモリバンクに格納されるものであり、アクセスパターンACPの設定位置が開始位置から移動した全ての位置で、当該アクセスパターンACPで特定される5個のアクセス画素IM1〜IM5の画素データDo1〜Do5がそれぞれ異なるメモリバンクに格納された状態となって同時アクセスが可能となる。

また、図1に示すデータアクセス装置100によれば、データ格納制御部120からデータアクセス制御部140に各メモリバンクBK0〜BK5の読み出しフラグRFGを与えるものであり、例えばこれらデータ格納制御部120およびデータアクセス制御部140を制御する制御装置が、アクセスパターンACPおよび一定数Nの情報に基づいて各メモリバンクBK0〜BK5の読み出しフラグRFGを生成して、データアクセス制御部140に与えることが必要でなくなる。

また、図1に示すデータアクセス装置100によれば、データ格納制御部120からデータアクセス制御部140に各メモリバンクBK0〜BK5の読み出し開始アドレスRSおよび書き込み開始アドレスWSを与えるものであり、例えばこれらデータ格納制御部120およびデータアクセス制御部140を制御する制御装置が、アクセスパターンACPおよび一定数Nの情報に基づいて各メモリバンクBK0〜BK5の読み出し開始アドレスRSおよび書き込み開始アドレスWSを生成して、データアクセス制御部140に与えることが必要でなくなる。

なお、上述の実施の形態においては、アクセスパターンACPが5個の画素のパターンであり、メモリ部110が6個のメモリバンクBK0〜BK5で構成され、またそれぞれのメモリバンクのワード線長が10で、同一のメモリバンクに連続して格納する一定数Nが22であるものを示したが、これに限定されるものではない。必要なワード線長、メモリバンク数、および一定数Nは、アクセスパターンACPを構成する画素の個数およびこのアクセスパターンACPの分布範囲によって定めればよい。

アクセスパターンACPを構成する各画素の画素データを異なるメモリバンクに格納するためのメモリバンクの最低個数は、アクセスパターンACPを構成する画素の個数と等しくなる。同一のメモリバンクに連続して格納する一定数Nを多くすればメモリバンクの必要個数は少なくなるが、初期格納時の書き込みアドレスWのオフセット処理により画素データが格納されない領域が増えるため、各メモリバンクに必要なメモリ容量が多くなる。逆に、一定数Nを少なくすると、各メモリバンクに必要なメモリ容量は少なくなるが、メモリバンクの必要個数が多くなる。

なお、上述実施の形態においては、画面SRNが水平方向に伸びる画素列が垂直方向に順次配列された構成であるとし、初期格納時には、各画素列の画素を順に注目画素とし、この注目画素の画素データを各メモリバンクBK0〜BK5に振り分けて格納し、データアクセス時には、アクセスパターンACPの設定位置を画素列方向に移動した各設定位置で当該アクセスパターンACPで特定される5個の画素IM1〜IM5の画素データDo1〜Do5を同時に得るものを示したが、画面SRNが垂直方向に伸びる画素列が水平方向に順次配列された構成であるとして、初期格納時およびデータアクセス時の動作を行うように構成することもできる。

また、上述実施の形態においては、データ格納制御部120からデータアクセス制御部140に開始アドレスRS,WSおよび読み出しフラグRFGを与えるものを示したが、これら開始アドレスRS,WSおよび読み出しフラグRFGを、データ格納制御部120およびデータアクセス制御部140の動作を制御する制御装置から、データアクセス制御部140に与える構成とすることもできる。

100・・・データアクセス装置、110・・・メモリ部、111・・・入力端子、112・・・出力端子、BK0〜BK5・・・メモリバンク、120・・・データ格納制御部、121・・・カウンタ(カウンタA)、122・・・カウンタ(カウンタB)、123・・・一致判定部、124・・・オフセット制御部、125・・・バンクアドレスカウンタ、126・・・ビット線アドレスカウンタ、127・・・ワードアドレス線カウンタ、128・・・アドレス生成部、129・・・読み出しフラグ生成部、140・・・データアクセス制御部、141・・・開始アドレス保持部、142・・・カウンタ(カウンタA)、143・・・カウンタ(カウンタB)、144・・・バンク指定部、145・・・アドレスカウンタフラグ制御部、146・・・書き込みアドレスカウンタ、147・・・読み出しアドレスカウンタ、148・・・書き込みアドレス生成部、149・・・読み出しアドレス生成部、150・・・読み出しフラグ生成部、151・・・書き込みフラグ生成部