JP4635504B2 - 昇圧回路 - Google Patents

昇圧回路 Download PDFInfo

- Publication number

- JP4635504B2 JP4635504B2 JP2004220137A JP2004220137A JP4635504B2 JP 4635504 B2 JP4635504 B2 JP 4635504B2 JP 2004220137 A JP2004220137 A JP 2004220137A JP 2004220137 A JP2004220137 A JP 2004220137A JP 4635504 B2 JP4635504 B2 JP 4635504B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- booster circuit

- pulse signal

- capacitor

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Dc-Dc Converters (AREA)

Description

NchトランジスタT1i(i=1〜n)のゲートにはキャパシタCmiの一端が接続されている。

NchトランジスタT1(n+1)のゲートは自身のドレインに接続されている、つまり、NchトランジスタT1(n+1)はダイオード接続されている。

なお、本明細書において、NchトランジスタT1i(i=1〜n+1)の閾値をVth1iと記載する。

NchトランジスタT21のドレインには入力端INが接続されている。NchトランジスタT2i(i=2〜n)のドレインにはノードn(i−1)が接続されている。

NchトランジスタT2i(i=1〜n)のソースはノードkiに接続されて、NchトランジスタT1i(i=1〜n)のゲートにつながっている。

NchトランジスタT2i(i=1〜n)のゲートはノードniに接続されて、キャパシタCiにつながっている。

キャパシタCmi(i=1〜n)の一端はNchトランジスタT1iのゲートに接続されている。キャパシタCmi(i:1〜nの奇数)の他端にはクロック電圧PH4が供給され、キャパシタCmi(i:1〜nの偶数)の他端にはクロック電圧PH3が供給される。

その後、クロック電圧PH2がLレベルとなって、さらに、クロック電圧PH3がHレベルとなると、キャパシタCm2を通じてNchトランジスタT12のゲート電圧(ノードk2の電位)がさらに高くなる。NchトランジスタT12のゲート電圧がノードn1の電位より閾値Vth12以上高くなると、NchトランジスタT12は三極間動作になり、ノードn1の電位は、閾値Vth12分の電圧ドロップすることなく、NchトランジスタT12を通ってノードn2へ転送される。

その後、クロック電圧PH3がLレベルとなると、クロック電圧PH3による電位の持ち上げがなくなるので、NchトランジスタT12のゲート電圧(ノードk2の電位)が下がる。

その後、クロック電圧PH2がHレベルとなり、さらに、クロック電圧PH1がLレベルとなると、ノードn1の電位がそれに応じて下がり、キャパシタC2を通じてNchトランジスタT22のゲート電圧が高くなっているのでNchトランジスタT12のゲート電圧(ノードk2の電位)が下がる。

その後、クロック電圧PH1がLレベルとなって、さらに、クロック電圧PH4がHレベルとなると、キャパシタCm3を通じてNchトランジスタT13のゲート電圧(ノードk3の電位)がさらに高くなる。NchトランジスタT13のゲート電圧がノードn2の電位より閾値Vth13以上高くなると、NchトランジスタT13は三極間動作になり、ノードn2の電位は、閾値Vth13分の電圧ドロップすることなく、NchトランジスタT13を通ってノードn3へ転送される。

その後、クロック電圧PH4がLレベルとなると、クロック電圧PH4による電位の持ち上げがなくなるので、NchトランジスタT13のゲート電圧(ノードk3の電位)が下がる。

その後、クロック電圧PH1がHレベルとなり、さらに、クロック電圧PH2がLレベルとなると、ノードn2の電位がそれに応じて下がり、キャパシタC3を通じてNchトランジスタT23のゲート電圧が高くなっているのでNchトランジスタT13のゲート電圧(ノードk3の電位)が下がる。

Vout=Vcc+(Vcc×α1−Vth11)+(Vcc×α2−Vth12)+・・・+(Vcc×αn−Vth1n)−Vth1(n+1)

となる。

但し、αi(i=1〜n)は主ポンプ用キャパシタ(キャパシタC1〜Cn)でポンプするときの効率であり、ポンプ効率αiは、

αi=Ci/(Ci+Cmi)

である。

Vout=Vcc+Vcc×α1+Vcc×α2+・・・+Vcc×αn−Vth1(n+1)

となる。

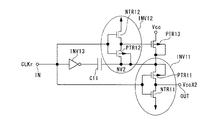

以下、本発明の第1の実施の形態における2倍昇圧回路について図1を参照しつつ説明する。図1は本実施の形態における2倍昇圧回路の構成を示す回路図である。なお、使用するクロック信号CLKの波高値(振幅)をVccとし、この反転信号CLKrが入力端INに入力される。

ソースに電源電圧Vccが入力される、充電用のP型電界効果トランジスタ(以下、Pchトランジスタという。)PTR13がある。PchトランジスタPTR13の基盤(N−Well)はPchトランジスタPTR13のドレインに接続される。一端がPchトランジスタPTR13のドレインに接続され、他端がインバータ回路INV13の出力端に接続されたキャパシタC11がある。このキャパシタC11の他端にはクロック信号CLK(クロック信号CLKの反転信号CLKrがインバータ回路INV13で反転されて得られるクロック信号CLK)が供給される。

PchトランジスタPTR11の基盤(N−Well)はPchトランジスタPTR11のソースに接続される。

PchトランジスタPTR11のゲートとNchトランジスタNTR11のゲートとが接続されており、その接続点(インバータ回路INV11の入力部)にクロック信号CLKの反転信号CLKrが入力される。

PchトランジスタPTR11のドレインとNchトランジスタNTR11のドレインとが接続されており、その接続点(インバータ回路INV11の出力部)が2倍昇圧回路の出力端OUTに接続されている。

PchトランジスタPTR11のソース、つまり、インバータ回路INV11の電源端子はキャパシタC11の一端に接続されている。

NchトランジスタNTR11のソースは接地されている。

PchトランジスタPTR12の基盤(N−Well)はPchトランジスタPTR12のソースに接続される。

PchトランジスタPTR12のゲートとNchトランジスタNTR12のゲートとが接続されており、その接続点(インバータ回路INV12の入力部)にクロック信号CLKの反転信号CLKrが入力される。

PchトランジスタPTR12のドレインとNchトランジスタNTR12のドレインとが接続されており、その接続点(インバータ回路INV12の出力部)はPchトランジスタPTR13のゲートに接続されている。

PchトランジスタPTR12のソース、つまり、インバータ回路INV12の電源端子はキャパシタC11の一端に接続されている。

NchトランジスタNTR12のソースは接地されている。

クロック信号CLKがLレベルのとき、つまりその反転信号CLKrがHレベルのとき、NchトランジスタNTR11のゲートおよびPchトランジスタPTR11のゲートにHレベルが入力されるので、NchトランジスタNTR11側がONし、出力端OUTへ接地レベル、つまりLレベルが出力される。

このとき、NchトランジスタNTR12のゲートおよびPchトランジスタPTR12のゲートにHレベルが入力されるので、NchトランジスタNTR12側がONし、PchトランジスタPTR13のゲートに接地レベル、つまりLレベルが入力され、PchトランジスタPTR11がONし、PchトランジスタPTR13を通して、電源電圧Vccでキャパシタ11が充電され、Vcc分の電荷量が蓄えられる(図2参照)。

また、反転信号CLKrがLレベルのとき、NchトランジスタNTR11のゲートおよびPchトランジスタPTR11のゲートにLレベルが入力されるので、NchトランジスタNTR11がOFFし、PchトランジスタPTR11がONする。

このとき、インバータ回路INV13の出力がLレベルからHレベルになっているので、キャパシタC11にVccレベルの電圧が供給されて、ノードNV2の電位はほぼ2×Vccとなっており、このほぼ2×Vccレベルの信号がPchトランジスタPTR11を通って出力端OUTへ出力される(図2参照)。

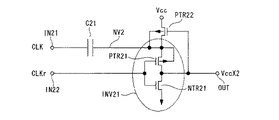

以下、本発明の第2の実施の形態における2倍昇圧回路について図3を参照しつつ説明する。図3は本実施の形態における2倍昇圧回路の構成を示す回路図である。なお、使用するクロック信号CLKの波高値(振幅)をVccとし、クロック信号CLKが入力端IN21に、クロック信号CLKの反転信号CLKrが入力端IN22に入力される。

ソースに電源電圧Vccが入力される、充電用のPchトランジスタPTR22がある。PchトランジスタPTR22の基盤(N−Well)はPchトランジスタPTR22のドレインに接続される。一端がPchトランジスタPTR22のドレインに接続され、他端が入力端IN21に接続されたキャパシタC21がある。

PchトランジスタPTR21の基盤(N−Well)はPchトランジスタPTR21のソースに接続される。

PchトランジスタPTR21のゲートとNchトランジスタNTR21のゲートとが接続されており、その接続点(インバータ回路INV21の入力部)に入力端IN22が接続される。

PchトランジスタPTR21のドレインとNchトランジスタNTR21のドレインとが接続されており、その接続点(インバータ回路INV21の出力部)に2倍昇圧回路の出力端OUTが接続されているとともに、接続点はPchトランジスタPTR22のゲートにも接続されている。

PchトランジスタPTR21のソース、つまり、インバータ回路INV21の電源端子はキャパシタC21の一端に接続されている。

NchトランジスタNTR21のソースは接地されている。

クロック信号CLKがLレベルのとき、つまりその反転信号CLKrはHレベルのとき、NchトランジスタNTR21のゲートおよびPchトランジスタPTR21のゲートにHレベルが入力されるので、NchトランジスタNTR21側がONし、出力端OUTへ接地レベル、つまりLレベルが出力される。このとき、Pchトランジスタ22のゲートに接地レベル、つまりLレベルが入力され、PchトランジスタPTR22がONし、PchトランジスタPTR22を通して、電源電圧VccでキャパシタC21が充電され、Vcc分の電荷量が蓄えられる。

このとき、キャパシタC21にVccレベルの電圧が供給されているため、ノードNV2の電位はほぼ2×Vccとなっており、このほぼ2×Vccレベルの信号がPchトランジスタPTR21を通って出力端OUTへ出力される。

以下、本発明の第3の実施の形態における3倍昇圧回路について図4を参照しつつ説明する。図4は本実施の形態における3倍昇圧回路の構成を示す回路図である。なお、使用するクロック信号CLKの波高値(振幅)をVccとし、クロック信号CLKが入力端IN31に、クロック信号CLKの反転信号CLKrが入力端IN32,33に入力される。

ソースに電源電圧Vccが入力される、充電用のPchトランジスタPTR32がある。PchトランジスタPTR32の基盤(N−Well)はPchトランジスタPTR32のドレインに接続される。一端がPchトランジスタPTR32のドレインに接続され、他端が入力端IN31に接続されたキャパシタC31がある。

PchトランジスタPTR31の基盤(N−Well)はPchトランジスタPTR31のソースに接続される。

PchトランジスタPTR31のゲートとNchトランジスタNTR31のゲートとが接続されており、その接続点(インバータ回路INV31の入力部)に入力端IN32が接続される。

PchトランジスタPTR31のドレインとNchトランジスタNTR31のドレインとが接続されており、その接続点(インバータ回路INV31の出力部)にPchトランジスタPTR34のソースが接続されているとともに、接続点はPchトランジスタPTR32のゲートにも接続されている。

PchトランジスタPTR31のソース、つまり、インバータ回路INV31の電源端子はキャパシタC31の一端に接続されている。

NchトランジスタNTR31のソースは接地されている。

PchトランジスタPTR32、キャパシタC31、インバータ回路INV31で、入力されるクロック信号CLKを2×Vccの波高値(振幅)のクロック信号に昇圧する昇圧回路が構成されており、1段目の昇圧回路部と呼ぶ。

PchトランジスタPTR33の基盤(N−Well)はPchトランジスタPTR33のソースに接続される。

PchトランジスタPTR33のゲートとNchトランジスタNTR33のゲートとが接続されており、その接続点(インバータ回路INV33の入力部)に1段目の昇圧回路部のインバータ回路INV31の出力部が接続される。

PchトランジスタPTR33のドレインとNchトランジスタNTR33のドレインとが接続されており、その接続点(インバータ回路INV33の出力部)に3倍昇圧回路の出力端OUTが接続されているとともに、接続点はPchトランジスタPTR34のゲートにも接続されている。

PchトランジスタPTR33のソース、つまり、インバータ回路INV33の電源端子はキャパシタC32の一端に接続されている。

NchトランジスタNTR33のソースは接地されている。

PchトランジスタPTR34、キャパシタC32、インバータ回路INV33で、1段目の昇圧回路部で得られる波高値(振幅)が2×Vccのクロック信号を3×Vccの波高値(振幅)のクロック信号に昇圧する昇圧回路部が構成されており、2段目の昇圧回路部と呼ぶ。

クロック信号CLKがLレベルのとき、つまりその反転信号CLKrがHレベルのとき、NchトランジスタNTR31のゲートおよびPchトランジスタPTR31のゲートにHレベルが入力されるので、NchトランジスタNTR31側がONして、インバータ回路INV31の出力は接地レベル、つまりLレベルとなり、接地レベルの信号がPchトランジスタPTR34のソースおよびインバータ回路INV33の入力部へ出力される。このとき、PchトランジスタPTR32のゲートに接地レベル、つまりLレベルが入力されるので、PchトランジスタPTR32がONして、PchトランジスタPTR32を通して、電源電圧VccでキャパシタC31が充電され、Vcc分の電荷量が蓄えられる(図5参照)。

このとき、キャパシタC31にVccレベルの電圧が供給されているため、ノードNV2の電位はほぼ2×Vccとなっており、このほぼ2×Vccレベルの信号がPchトランジスタPTR31を通って次段の昇圧回路部(2段目の昇圧回路部)のPchトランジスタPTR34のソースおよびインバータ回路INV33の入力部へ出力される(図5参照)。

このとき、キャパシタC32にVccレベルの電圧が供給されているため、ノードNV3の電位はほぼ3×Vccとなっており、このほぼ3×Vccレベルの信号がPchトランジスタPTR33を通って出力端OUTへ出力される(図5参照)。

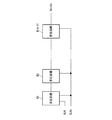

以下、本発明の第4の実施の形態におけるn倍昇圧回路について図6を参照しつつ説明する。図6は本実施の形態におけるn倍昇圧回路の構成を示す回路図である。なお、使用されるクロック信号CLKの波高値(振幅)をVccとする。

図6のn倍昇圧回路は、図4の第3の実施の形態における3倍昇圧回路を応用したものであり、図4の1段目の昇圧回路部、2段目の昇圧回路部、1段目の昇圧回路部、・・・と接続することによって構成される。

以下、本発明の第5の実施の形態における3倍昇圧回路について図7を参照しつつ説明する。図7は本実施の形態における3倍昇圧回路の構成を示す回路図である。なお、使用するクロック信号CLKの波高値(振幅)をVccとし、クロック信号CLKが入力端IN31aに、クロック信号CLKの反転信号CLKrが入力端IN32a,33aに入力される。

ソースに電源電圧Vccが入力される、充電用のPchトランジスタPTR32aがある。PchトランジスタPTR32aの基盤(N−Well)はPchトランジスタPTR32aのドレインに接続される。一端がPchトランジスタPTR32aのドレインに接続され、他端が入力端IN31aに接続されたキャパシタC31aがある。

PchトランジスタPTR31aの基盤(N−Well)はPchトランジスタPTR31aのソースに接続される。

PchトランジスタPTR31aのゲートとNchトランジスタNTR31aのゲートとが接続されており、その接続点(インバータ回路INV31aの入力部)に入力端IN32aが接続される。

PchトランジスタPTR31aのドレインとNchトランジスタNTR31aのドレインとが接続されており、その接続点(インバータ回路INV31aの出力部)はPchトランジスタPTR32aのゲートに接続されている。

PchトランジスタPTR31aのソース、つまり、インバータ回路INV31aの電源端子はキャパシタC31aの一端に接続されている。

NchトランジスタNTR31aのソースは接地されている。

PchトランジスタPTR32a、キャパシタC31a、インバータ回路INV31aで、入力されるクロック信号CLKを2×Vccの波高値(振幅)のクロック信号に昇圧する昇圧回路が構成されており、1段目の昇圧回路部と呼ぶ。

PchトランジスタPTR33aの基盤(N−Well)はPchトランジスタPTR33aのソースに接続される。

PchトランジスタPTR33aのゲートとNchトランジスタNTR33aのゲートとが接続されており、その接続点(インバータ回路INV33aの入力部)には1段目の昇圧回路部のインバータ回路INV31aの出力部が接続される。

PchトランジスタPTR33aのドレインとNchトランジスタNTR33aのドレインとが接続されており、その接続点(インバータ回路INV33aの出力部)に3倍昇圧回路の出力端OUTが接続されているとともに、接続点はPchトランジスタPTR34aのゲートにも接続されている。

PchトランジスタPTR33aのソース、つまり、インバータ回路INV33aの電源端子はキャパシタC32aの一端に接続されている。

NchトランジスタNTR33aのソースは接地されている。

PchトランジスタPTR34a、キャパシタC32a、インバータ回路INV33aで、1段目の昇圧回路部で得られる波高値(振幅)が2×Vccのクロック信号を3×Vccの波高値(振幅)のクロック信号に昇圧する昇圧回路部が構成されており、2段目の昇圧回路部と呼ぶ。

クロック信号CLKがLレベルのとき、つまりその反転信号CLKrがHレベルのとき、NchトランジスタNTR31aのゲートおよびPchトランジスタPTR31aのゲートにHレベルが入力されるので、NchトランジスタNTR31a側がONして、インバータ回路INV31aの出力は接地レベル、つまりLレベルとなり、接地レベルの信号がインバータ回路INV33aの入力部へ出力される。このとき、Pchトランジスタ32aのゲートに接地レベル、つまりLレベルが入力されるので、PchトランジスタPTR32aがONし、PchトランジスタPTR32aを通して、電源電圧Vccでキャパシタ31aが充電され、Vcc分の電荷量が蓄えられる。

このとき、キャパシタC31aにVccレベルの電圧が供給されているため、ノードNV2の電位はほぼ2×Vccとなっており、このほぼ2×Vccレベルの信号が次段の昇圧回路部(2段目の昇圧回路部)のPchトランジスタPTR34aのソースへ出力される。

このとき、キャパシタC32aにVccレベルの電圧が供給されているため、ノードNV3の電位はほぼ3×Vccとなっており、このほぼ3×Vccレベルの信号がPchトランジスタPTR33aを通って出力端OUTへ出力される。

以下、本発明の第6の実施の形態におけるn倍昇圧回路について図8を参照しつつ説明する。図8は本実施の形態におけるn倍昇圧回路の構成を示す回路図である。なお、使用されるクロック信号CLKの波高値(振幅)をVccとする。

図8のn倍昇圧回路は、図7の第5の実施の形態における3倍昇圧回路を応用したものであり、図7の1段目の昇圧回路部、2段目の昇圧回路部、1段目の昇圧回路部、・・・と接続することによって構成される。

以下、本発明の第7の実施の形態における3倍昇圧回路について図9を参照しつつ説明する。図9は本実施の形態における3倍昇圧回路の構成を示す回路図である。なお、使用するクロック信号CLKの波高値(振幅)をVccとし、クロック信号CLKが入力端IN51に、クロック信号CLKの反転信号CLKrが入力端IN52,IN53に入力される。

ソースに電源電圧Vccが入力される、充電用のPchトランジスタPTR52がある。PchトランジスタPTR52の基盤(N−Well)はPchトランジスタPTR52のドレインに接続される。一端がPchトランジスタPTR52のドレインに接続され、他端が入力端IN51に接続されたキャパシタC41がある。

PchトランジスタPTR51の基盤(N−Well)はPchトランジスタPTR51のソースに接続される。

PchトランジスタPTR51のゲートとNchトランジスタNTR51のゲートとが接続されており、その接続点(インバータ回路INV51の入力部)に入力端IN52が接続される。

PchトランジスタPTR51のドレインとNchトランジスタNTR51のドレインとが接続されており、その接続点(インバータ回路INV51の出力部)に次段のキャパシタC42が接続されているとともに、接続点はPchトランジスタPTR52のゲートにも接続されている。

PchトランジスタPTR51のソース、つまり、インバータ回路INV51の電源端子はキャパシタC41の一端に接続されている。

NchトランジスタNTR51のソースは接地されている。

PchトランジスタPTR52、キャパシタC41、インバータ回路INV51で、入力されるクロック信号CLKを2×Vccの波高値(振幅)のクロック信号に昇圧する昇圧回路が構成されており、1段目の昇圧回路部と呼ぶ。

PchトランジスタPTR53の基盤(N−Well)はPchトランジスタPTR53のソースに接続される。

PchトランジスタPTR53のゲートとNchトランジスタNTR53のゲートとが接続されており、その接続点(インバータ回路INV53の入力部)に入力端IN53が接続される。

PchトランジスタPTR53のドレインとNchトランジスタNTR53のドレインとが接続されており、その接続点(インバータ回路INV53の出力部)に3倍昇圧回路の出力端OUTが接続されているとともに、接続点はPchトランジスタPTR54のゲートにも接続されている。

PchトランジスタPTR53のソース、つまり、インバータ回路INV53の電源端子はキャパシタC42の一端に接続されている。

NchトランジスタNTR53のソースは接地されている。

PchトランジスタPTR54、キャパシタC42、インバータ回路INV53で、1段目の昇圧回路部で得られる波高値(振幅)が2×Vccのクロック信号を3×Vccの波高値(振幅)のクロック信号に昇圧する昇圧回路部が構成されており、2段目の昇圧回路部と呼ぶ。

クロック信号CLKがLレベルのとき、つまりその反転信号CLKrがHレベルのとき、NchトランジスタNTR51のゲートおよびPchトランジスタPTR51のゲートにHレベルが入力されるので、NchトランジスタNTR51側がONし、インバータ回路INV51の出力は接地レベル、つまりLレベルとなり、接地レベルの信号がキャパシタC42へ出力される。このとき、PchトランジスタPTR52のゲートに接地レベル、つまりLレベルが入力されるので、PchトランジスタPTR52がONし、PchトランジスタPTR52を通して、電源電圧Vccでキャパシタ41が充電され、Vcc分の電荷量が蓄えられる。

同じ期間で、2段目の昇圧回路部でも、NchトランジスタNTR53のゲートおよびPchトランジスタPTR53のゲートにHレベルが入力されるので、NchトランジスタNTR53側がONし、インバータ回路INV53の出力は接地レベル、つまりLレベルとなり、接地レベルの信号が出力端OUTへ出力される。このとき、PchトランジスタPTR54のゲートに接地レベル、つまりLレベルが入力されるので、PchトランジスタPTR54がONし、PchトランジスタPTR54を通して、電源電圧VccでキャパシタC42が充電され、Vcc分の電荷量が蓄えられる。

このとき、キャパシタC51にVccレベルの電圧が供給されているため、ノードNV2の電位はほぼ2×Vccとなっており、このほぼ2×Vccレベルの信号がPchトランジスタPTR51を通って次段の昇圧回路部(2段目の昇圧回路部)のキャパシタC42の他端へ出力される。

同じ期間で、2段目の昇圧回路部でも、NchトランジスタNTR53のゲートおよびPchトランジスタPTR53のゲートにLレベルが入力されるので、PchトランジスタPTR53側がONし、PchトランジスタPTR54のゲートにHレベルが入力され、PchトランジスタPTR54がOFFする。

このとき、キャパシタC42にほぼ2×Vccレベルの電圧が供給されているため、ノードNV3の電位はほぼ3×Vccとなっており、このほぼ3×Vccレベルの信号がPchトランジスタPTR53を通って3倍昇圧回路の出力端OUTへ出力される。

以下、本発明の第8の実施の形態におけるn倍昇圧回路について図10を参照しつつ説明する。図10は本実施の形態におけるn倍昇圧回路の構成を示す回路図である。なお、使用されるクロック信号CLKの波高値(振幅)をVccとする。

図10のn倍昇圧回路は、図9の3倍昇圧回路を応用したものであり、図9の1段目の昇圧回路部、2段目の昇圧回路部、2段目の昇圧回路部、2段目の昇圧回路部、・・・と接続することによって構成される。

図9の3倍昇圧回路と同様の仕組みによって、クロック信号CLKは、1クロックで、n×Vccの信号に昇圧されて、n倍昇圧回路から波高値(振幅)がn×Vccのクロック信号が出力される。

通常のPchトランジスタでは、基盤電位は常にチップ内の最高電位にしておく必要がある。なぜなら、基盤電位(N−Well電位)が順方向になると、トランジスタとしての動作ができなくなるからである。

従って、注意が必要となるのは、充電用のPchトランジスタ(PchトランジスタPTR13、PTR22、PTR32、PTR34、PTR32a、PTR34a、PTR52、PTR54)の基盤電位(N−Well電位)は中間ノード(ノードNV2、NV3)に接続されており、反転信号CLKrがHレベルに立ち上がって、充電用のPchトランジスタを介してVccで中間ノードを充電するときに一瞬の間、充電用のPchトランジスタの基盤電位(N−Well電位)が順バイアスになる可能性があるので、中間ノードの立下り波形がなるべくゆるく下がるように設定すること、および、充電用のPchトランジスタのレイアウトは、他のPchトランジスタとWellを分離孤立させて、順方向のバイアス電位になってもラッチアップが起こしにくいように工夫することが好ましい。

以下、本発明の2倍昇圧回路を利用した4相クロック駆動のチャージポンプ回路について図11および図12を参照しつつ説明する。図11は4相クロック駆動のチャージポンプ回路の構成を示す回路図である。図12は図11のチャージポンプ回路の動作を説明するための波形図である。

ただし、図11のチャージポンプ回路において、図15の従来のチャージポンプ回路と同様の役割の素子については同様の符号を付している。また、図11の補助ポンプ用キャパシタの符号を、図15と異なる符号Cs1〜Csnを使用しているが、役割としては同じである。

また、図11のチャージポンプ回路の基本的な動作は、図15の従来の4相クロック駆動のチャージポンプ回路と同様であり、その説明が適用できるため、その詳細な説明は省略する。

これにより、図15のチャージポンプ回路では、クロック電圧PH4がそのままキャパシタCmi(i:1〜nの奇数)に供給されるのに対して、図11のチャージポンプ回路では、クロック電圧PH4を2倍昇圧回路14を通すことによって得られる波高値(振幅)が2×Vccのクロック電圧PH4aがキャパシタCsi(i:1〜nの奇数)に供給されるようになっている。

したがって、図11のチャージポンプ回路は、図15のチャージポンプ回路より転送時のNchトランジスタT1i(i:1〜nの奇数)のゲート電圧の値が大きくなる。

これにより、図15のチャージポンプ回路では、クロック電圧PH3がそのままキャパシタCmi(i:1〜nの偶数)に供給されるのに対して、図11のチャージポンプ回路では、クロック電圧PH3を2倍昇圧回路13を通すことによって得られる波高値(振幅)が2×Vccの得られるクロック電圧PH3aがキャパシタCsi(i:1〜nの偶数)に供給されるようになっている。

したがって、図11のチャージポンプ回路は、図15のチャージポンプ回路より転送時のNchトランジスタT1i(i:1〜nの偶数)のゲート電圧の値が大きくなる。

Vout=Vcc+Vcc×β1+Vcc×β2+・・・+Vcc×βn−Vth1(n+1)

となる。

但し、βi(i=1〜n)は主ポンプ用キャパシタ(キャパシタC1〜Cn)でポンプするときの効率であり、ポンプ効率βiは、

βi=Ci/(Ci+Csi)

である。

この結果、図15のチャージポンプ回路のポンプ効率αi(i=1〜n)より、図11のチャージポンプ回路のポンプ効率βi(i=1〜n)を高くすることができる。

したがって、図11のチャージポンプ回路では、図15のチャージポンプ回路と同じ出力電圧を得るために必要な段数を少なくすることができ、チャージポンプ回路全体の面積を小さくすることができる。

図11のチャージポンプ回路において、電源電圧Vccを1.5V、キャパシタCi(i=1〜n)の容量とキャパシタCmiの容量との比を10:2、NchトランジスタT1(n+1)にかかっているバックゲート電圧を11V、nを9とする。

ポンプ効率αi(i=1〜n)は0.83となり、NchトランジスタT1(n+1)の閾値Vth1(n+1)は1.5V(「背景技術」の欄参照)となる。

これらを図15のチャージポンプ回路において示した上記の式に代入すると、図15のチャージポンプ回路の出力電圧Voutは、11.2Vとなる。

そして、図11のチャージポンプ回路において、電源電圧Vccを1.5V、キャパシタCi(i=1〜n)の容量とキャパシタCsiの容量との比を10:1、NchトランジスタT1(n+1)にかかっているバックゲート電圧を11V、nを8とする。

ポンプ効率βi(i=1〜n)は0.91となり、NchトランジスタT1(n+1)の閾値Vth1(n+1)は1.5V(「背景技術」の欄参照)となる。

これらを図11のチャージポンプ回路において示した上記の式に代入すると、図11のチャージポンプ回路の出力電圧Voutは、10.9Vとなる。

以下、本発明の2倍昇圧回路を利用した他の4相クロック駆動のチャージポンプ回路について図13を参照しつつ説明する。図13は4相クロック駆動のチャージポンプ回路の構成を示す回路図である。

ただし、図13のチャージポンプ回路において、図11、図15のチャージポンプ回路と同様の役割の素子については同様の符号を付している。

また、2倍昇圧回路14は、クロック電圧PH4を入力する入力端と後述するキャパシタCpの他端との間に挿入されている。

また、一端がNchトランジスタT1(n+1)のゲートに接続され、他端が2倍昇圧回路14に接続されるように、キャパシタCpを挿入する。ただし、NchトランジスタT1(n+1)、T2(n+1)、キャパシタCpで構成される補助ポンプは主ポンプ用のキャパシタCi(i=1〜n)に相当するものがないので、ポンプ効果が少ないことから、キャパシタCpとしてキャパシタCs1〜Csnの容量より大きい容量のキャパシタを使用することが好ましい。

クロック電圧PH2がHレベルとなると、NchトランジスタT2(n+1)のゲートは出力端OUTに接続されているので、NchトランジスタT1(n+1)のゲート電圧(ノードk(n+1)の電位)は出力電圧Vout−閾値Vth2(n+1)に充電される。その後、クロック電圧PH4がHレベルとなると、キャパシタCpを通じてNchトランジスタT1(n+1)のゲート電圧(ノードk(n+1)の電位)がさらに高くなる。NchトランジスタT1(n+1)のゲート電圧がノードnnの電位より閾値Vth1(n+1)以上高くなると、NchトランジスタT1(n+1)は三極間動作になり、ノードnnの電位は、閾値Vth1(n+1)分の電圧ドロップすることなく、NchトランジスタT1(n+1)を通って出力端OUTへ転送される。

Vout=Vcc+Vcc×β1+Vcc×β2+・・・+Vcc×βn

となる。

図11のチャージポンプ回路において、電源電圧Vccを1.5V、キャパシタCi(i=1〜n)の容量とキャパシタCsiの容量との比を10:1、NchトランジスタT1(n+1)にかかっているバックゲート電圧を11V、nを8とする場合、上記の「チャージポンプ回路(1)」において示したように、出力電圧Voutは、10.9Vとなる。

これらを図13のチャージポンプ回路において示した上記の式に代入すると、図13のチャージポンプ回路の出力電圧Voutは、11.1Vとなる。

以下、本発明の2倍昇圧回路および3倍昇圧回路を利用した4相クロック駆動のチャージポンプ回路について図14を参照しつつ説明する。図14は4相クロック駆動のチャージポンプ回路の構成を示す回路図である。

ただし、図14のチャージポンプ回路において、図11、図13、図15のチャージポンプ回路と同様の役割の素子については同様の符号を付している。

なお、図14の4相クロック駆動のチャージポンプ回路の基本的な動作は、クロック電圧PH1〜PH4を昇圧する点を除けば、入力端INからノードnnまでの転送については図15のチャージポンプ回路と同様であり、また、ノードnnから出力端OUTへの転送については図13のチャージポンプ回路と同様である。

これにより、図13のチャージポンプ回路では、クロック電圧PH4を2倍昇圧回路14を通すことによって得られる波高値(振幅)が2×Vccのクロック電圧PH4aがキャパシタCsi(i:1〜nの奇数)に供給されるのに対して、図14のチャージポンプ回路では、クロック電圧PH4を3倍昇圧回路34を通すことによって得られる波高値(振幅)が3×Vccのクロック電圧PH4bがキャパシタCsi(i:1〜nの奇数)およびキャパシタCpに供給されるようになっている。

したがって、図14のチャージポンプ回路は、図13のチャージポンプ回路より転送時のNchトランジスタT1i(i:1〜nの奇数)のゲート電圧の値が大きくなる。

これにより、図13のチャージポンプ回路では、クロック電圧PH3を2倍昇圧回路13を通すことによって得られる波高値(振幅)が2×Vccのクロック電圧PH3aがキャパシタCsi(i:1〜nの偶数)に供給されるのに対して、図14のチャージポンプ回路では、クロック電圧PH3を3倍昇圧回路33を通すことによって得られる波高値(振幅)が3×Vccのクロック電圧PH3bがキャパシタCsi(i:1〜nの偶数)に供給されるようになっている。

したがって、図14のチャージポンプ回路は、図13のチャージポンプ回路より転送時のNchトランジスタT1i(i:1〜nの偶数)のゲート電圧の値が大きくなる。

これにより、図13のチャージポンプ回路では、クロック電圧PH1がそのままキャパシタCi(i:1〜nの奇数)に供給されるのに対して、図14のチャージポンプ回路では、クロック電圧PH1を2倍昇圧回路31を通すことによって得られる波高値(振幅)が2×Vccのクロック電圧PH1bがキャパシタCi(i:1〜nの奇数)に供給されるようになっている。

したがって、図14のチャージポンプ回路は、図13のチャージポンプ回路より転送時のノードni(i:1〜nの奇数)の電位の値が大きくなる。

これにより、図13のチャージポンプ回路では、クロック電圧PH2がそのままキャパシタCi(i:1〜nの偶数)に供給されるのに対して、図14のチャージポンプ回路では、クロック電圧PH2を2倍昇圧回路32を通すことによって得られる波高値(振幅)が2×Vccのクロック電圧PH2bがキャパシタCi(i:1〜nの偶数)に供給されるようになっている。

したがって、図14のチャージポンプ回路は、図13のチャージポンプ回路より転送時のノードni(i:1〜nの偶数)の電位の値が大きくなる。

Vout=Vcc+(2×Vcc×γ1×β1−Vth11)+(2×Vcc×γ2×β2−Vth12)+・・・+(2×Vcc×γn×βn−Vth1n)−Vth1(n+1)

であり、図14のチャージポンプ回路では上述したようにNchトランジスタT1i(i=1〜n+1)の閾値Vth1i分の電圧ドロップがないので、出力電圧Voutは、

Vout=Vcc+2×Vcc×γ1×β1+2×Vcc×γ2×β2+・・・+2×Vcc×γn×βn

となる。

図13のチャージポンプ回路において、電源電圧Vccを1.5V、キャパシタCi(i=1〜n)の容量とキャパシタCsiの容量との比を10:1、nを7とする場合、上記の「チャージポンプ回路(2)」において示したように、出力電圧Voutは、11.1Vとなる。

これらを図14のチャージポンプ回路において示した上記の式に代入すると、図14のチャージポンプ回路の出力電圧Voutは、10.8Vとなる。

PTR22 P型電界効果トランジスタ(充電用)

C21 キャパシタ

OUT 出力端

Claims (8)

- nを3以上の整数として、

出力端と、第1〜第(n−1)の昇圧回路部とを備えた昇圧回路であって、

前記第i(i=1〜n−1)の昇圧回路部は、

第i(i=1〜n−1)の充電用P型電界効果トランジスタと、

一端が前記第i(i=1〜n−1)の充電用P型電界効果トランジスタのドレインに接続された第i(i=1〜n−1)のキャパシタと、

電源端子が前記第i(i=1〜n−1)のキャパシタの一端に接続され、出力部が前記第i(i=1〜n−1)の充電用P型電界効果トランジスタのゲートに接続された第i(i=1〜n−1)のインバータ回路と、

を有し、

前記第1、3、・・のキャパシタの他端にはHighレベルとLowレベルを交互に繰り返すパルス信号が供給され、

前記第2、4、・・のキャパシタの他端には前記パルス信号の反転信号が供給され、

前記第1のインバータ回路の入力部には前記パルス信号の反転信号が供給され、

前記第2、3、4、・・のインバータ回路の入力部には前記第1、2、3、・・の昇圧回路部の第1、2、3、・・のインバータ回路の出力が接続され、

前記第1の充電用P型電界効果トランジスタのソースには電源電圧が接続され、

前記第2、3、・・・の充電用P型電界効果トランジスタのソースには前記第1、2、・・・のインバータ回路の出力部が接続され、

前記(n−1)のインバータ回路の出力部は前記出力端に接続されていることを特徴とする昇圧回路。 - nを3以上の整数として、

出力端と、第1〜第(n−1)の昇圧回路部とを備えた昇圧回路であって、

前記第i(i=1〜n−1)の昇圧回路部は、

第i(i=1〜n−1)の充電用P型電界効果トランジスタと、

一端が前記第i(i=1〜n−1)の充電用P型電界効果トランジスタのドレインに接続された第i(i=1〜n−1)のキャパシタと、

電源端子が前記第i(i=1〜n−1)のキャパシタの一端に接続され、出力部が前記第i(i=1〜n−1)の充電用P型電界効果トランジスタのゲートに接続された第i(i=1〜n−1)のインバータ回路と、

を有し、

前記第1、3、・・のキャパシタの他端にはHighレベルとLowレベルを交互に繰り返すパルス信号が供給され、

前記第2、4、・・のキャパシタの他端には前記パルス信号の反転信号が供給され、

前記第1のインバータ回路の入力部には前記パルス信号の反転信号が供給され、

前記第2、3、4、・・のインバータ回路の入力部には前記第1、2、3、・・の昇圧回路部の第1、2、3、・・のインバータ回路の出力が接続され、

前記第1の充電用P型電界効果トランジスタのソースには電源電圧が接続され、

前記第2、3、・・・の充電用P型電界効果トランジスタのソースには前記第1、2、・・・のキャパシタの一端が接続され、

前記(n−1)のインバータ回路の出力部は前記出力端に接続されていることを特徴とする昇圧回路。 - 各前記インバータ回路は、

前記電源端子と、

該電源端子にソースが接続されたP型電界効果トランジスタと、

ドレインが該P型電界効果トランジスタのドレインに接続され、ソースが接地されたN型電界効果トランジスタと、

前記P型電界効果トランジスタのゲートと前記N型電界効果トランジスタのゲートとの接続点である前記入力部と、

前記P型電界効果トランジスタのドレインと前記N型電界効果トランジスタのドレインとの接続点である前記出力部と、

を有することを特徴とする請求項1または請求項2の何れか1項に記載の昇圧回路。 - キャパシタと、前記キャパシタの一端に接続され該キャパシタを充電する充電用P型電界効果トランジスタと、出力部が前記充電用P型電界効果トランジスタのゲートに接続され、電源電圧が前記充電用P型電界効果トランジスタを介して供給されるインバータ回路と、を備えた昇圧回路部を少なくとも2つ以上有し、前段の昇圧回路部の前記インバータ回路の出力を次段の昇圧回路部の前記インバータ回路の入力とする昇圧回路であって、

各昇圧回路部の前記キャパシタは、

前記キャパシタの他端にLレベルの信号が供給された際、前記キャパシタは充電され、

前記キャパシタの前記他端にHレベルの信号が供給された際、当該Hレベルの信号により前記キャパシタの前記一端の電圧が昇圧され、次段の昇圧回路部の前記キャパシタを該昇圧回路部の前記充電用P型電界効果トランジスタを介して充電することを特徴とする昇圧回路。 - 第1〜第m(m≧2の自然数)の昇圧回路部と、

第1のパルス信号発生回路と、

第2のパルス信号発生回路と、

出力端と、

を備えた昇圧回路であって、

前記第j(j=1〜m)の昇圧回路部は、

昇圧回路部の入力部にドレインが接続され、昇圧回路部の出力部にソースが接続された第j(j=1〜m)の主転送用N型電界効果トランジスタと、

昇圧回路部の入力部にドレインが接続され、昇圧回路部の出力部にゲートが接続され、前記第j(j=1〜m)の主転送用N型電界効果トランジスタのゲートにソースが接続された第j(j=1〜m)の補助転送用N型電界効果トランジスタと、

一端が前記第j(j=1〜m)の主転送用N型電界効果トランジスタのソースに接続された第j(j=1〜m)の第1キャパシタと、

一端が前記第j(j=1〜m)の主転送用N型電界効果トランジスタのゲートに接続された第j(j=1〜m)の第2キャパシタと、

を有し、

前記第1の昇圧回路部の入力部は電源電圧に接続され、

前記第2、3、4、・・の昇圧回路部の入力部は前記第1、2、3、・・の昇圧回路部の出力部に接続され、

前記第1、3、・・の第1キャパシタの他端には第1副パルス信号が供給され、

前記第2、4、・・の第1キャパシタの他端には第2副パルス信号が供給され、

前記第2、4、・・の第2キャパシタの他端には第3副パルス信号が供給され、

前記第1、3、・・の第2キャパシタの他端には第4副パルス信号が供給され、

前記第1のパルス信号発生回路は、

pを3以上の整数として、出力端と、第1〜第(p−1)の昇圧回路部とを備え、

前記第i(i=1〜p−1)の昇圧回路部は、ソースが電源電圧に接続された第i(i=1〜p−1)の充電用P型電界効果トランジスタと、

一端が前記第i(i=1〜p−1)の充電用P型電界効果トランジスタのドレインに接続された第i(i=1〜p−1)のキャパシタと、

電源端子が前記第i(i=1〜p−1)のキャパシタの一端に接続され、他端にHighレベルとLowレベルを交互に繰り返すパルス信号の反転信号が入力され、出力部が前記第i(i=1〜p−1)の充電用P型電界効果トランジスタのゲートに接続された第i(i=1〜p−1)のインバータ回路と、を有し、

前記第1のキャパシタの他端には前記パルス信号が供給され、

前記第2、3、・・・、(p−1)のキャパシタの他端は前記第1、2、・・、(p−2)のインバータ回路の出力部が接続され、

前記第(p−1)のインバータ回路の出力部は前記出力端に接続されている第3の昇圧回路、

請求項1記載のn=pとした第1の昇圧回路、

又は請求項2記載のn=pとした第2の昇圧回路

のうちのいずれか一の昇圧回路であって、HighレベルとLowレベルを交互に繰り返すパルス信号として第3主パルス信号が入力され、波高値が前記電源電圧のp倍である前記第3副パルス信号を出力し、

前記第2のパルス信号発生回路は、前記第1の昇圧回路、前記第2の昇圧回路、又は前記第3の昇圧回路のうちのいずれか一の昇圧回路であって、HighレベルとLowレベルを交互に繰り返すパルス信号として第4主パルス信号が入力され、波高値が前記電源電圧のp倍である前記第4副パルス信号を出力し、

前記第1副パルス信号は、波高値が前記電源電圧のq(qは、1≦q<pである整数)倍である信号であり、

前記第2副パルス信号は、波高値が前記電源電圧のq倍である信号であり、

さらに、

前記第mの昇圧回路部の出力部にドレイン及びゲートが接続され、前記出力端にソースが接続された第(m+1)の主転送用N型電界効果トランジスタと、

を有することを特徴とする昇圧回路。 - 第1〜第m(m≧2の自然数)の昇圧回路部と、

第1のパルス信号発生回路と、

第2のパルス信号発生回路と、

出力端と、

を備えた昇圧回路であって、

前記第j(j=1〜m)の昇圧回路部は、

昇圧回路部の入力部にドレインが接続され、昇圧回路部の出力部にソースが接続された第j(j=1〜m)の主転送用N型電界効果トランジスタと、

昇圧回路部の入力部にドレインが接続され、昇圧回路部の出力部にゲートが接続され、前記第j(j=1〜m)の主転送用N型電界効果トランジスタのゲートにソースが接続された第j(j=1〜m)の補助転送用N型電界効果トランジスタと、

一端が前記第j(j=1〜m)の主転送用N型電界効果トランジスタのソースに接続された第j(j=1〜m)の第1キャパシタと、

一端が前記第j(j=1〜m)の主転送用N型電界効果トランジスタのゲートに接続された第j(j=1〜m)の第2キャパシタと、

を有し、

前記第1の昇圧回路部の入力部は電源電圧に接続され、

前記第2、3、4、・・の昇圧回路部の入力部は前記第1、2、3、・・の昇圧回路部の出力部に接続され、

前記第1、3、・・の第1キャパシタの他端には第1副パルス信号が供給され、

前記第2、4、・・の第1キャパシタの他端には第2副パルス信号が供給され、

前記第2、4、・・の第2キャパシタの他端には第3副パルス信号が供給され、

前記第1、3、・・の第2キャパシタの他端には第4副パルス信号が供給され、

前記第1のパルス信号発生回路は、

pを3以上の整数として、出力端と、第1〜第(p−1)の昇圧回路部とを備え、

前記第i(i=1〜p−1)の昇圧回路部は、ソースが電源電圧に接続された第i(i=1〜p−1)の充電用P型電界効果トランジスタと、

一端が前記第i(i=1〜p−1)の充電用P型電界効果トランジスタのドレインに接続された第i(i=1〜p−1)のキャパシタと、

電源端子が前記第i(i=1〜p−1)のキャパシタの一端に接続され、他端にHighレベルとLowレベルを交互に繰り返すパルス信号の反転信号が入力され、出力部が前記第i(i=1〜p−1)の充電用P型電界効果トランジスタのゲートに接続された第i(i=1〜p−1)のインバータ回路と、を有し、

前記第1のキャパシタの他端には前記パルス信号が供給され、

前記第2、3、・・・、(p−1)のキャパシタの他端は前記第1、2、・・、(p−2)のインバータ回路の出力部が接続され、

前記第(p−1)のインバータ回路の出力部は前記出力端に接続されている第3の昇圧回路、

請求項1記載のn=pとした第1の昇圧回路、

又は請求項2記載のn=pとした第2の昇圧回路

のうちのいずれか一の昇圧回路であって、HighレベルとLowレベルを交互に繰り返すパルス信号として第3主パルス信号が入力され、波高値が前記電源電圧のp倍である前記第3副パルス信号を出力し、

前記第2のパルス信号発生回路は、前記第1の昇圧回路、前記第2の昇圧回路、又は前記第3の昇圧回路のうちのいずれか一の昇圧回路であって、HighレベルとLowレベルを交互に繰り返すパルス信号として第4主パルス信号が入力され、波高値が前記電源電圧のp倍である前記第4副パルス信号を出力し、

前記第1副パルス信号は、波高値が前記電源電圧のq(qは、1≦q<pである整数)倍である信号であり、

前記第2副パルス信号は、波高値が前記電源電圧のq倍である信号であり、

さらに、

前記第mの昇圧回路部の出力部にドレインが接続され、前記出力端にソースが接続された第(m+1)の主転送用N型電界効果トランジスタと、

前記第mの昇圧回路部の出力部にドレインが接続され、前記出力端にゲートが接続され、前記第(m+1)の主転送用N型電界効果トランジスタのゲートにソースが接続された第(m+1)の補助転送用N型電界効果トランジスタと、

一端が前記第(m+1)の主転送用N型電界効果トランジスタのゲートに接続され、他端に前記第4副パルス信号が供給されるキャパシタと、

を有することを特徴とする昇圧回路。 - 前記第1副パルス信号はHレベルの期間がLレベルの期間より長い信号であり、

前記第2副パルス信号は、前記第1副パルス信号と逆位相の関係にある信号であり、

前記第3副パルス信号はLレベルの期間がHレベルの期間より長い信号であって、前記第2副パルス信号がLレベルにある期間、該期間より短い期間Hレベルである信号であり、

前記第4副パルス信号は、前記第3副パルス信号と逆位相の関係にある信号である、

ことを特徴とする請求項5または請求項6の何れか1項に記載の昇圧回路。 - qを3以上の整数として、

第3のパルス信号発生回路と、

第4のパルス信号発生回路と、を更に備え、

前記第3のパルス信号発生回路は、

qを3以上の整数として、出力端と、第1〜第(q−1)の昇圧回路部とを備え、

前記第i(i=1〜q−1)の昇圧回路部は、ソースが電源電圧に接続された第i(i=1〜q−1)の充電用P型電界効果トランジスタと、

一端が前記第i(i=1〜q−1)の充電用P型電界効果トランジスタのドレインに接続された第i(i=1〜q−1)のキャパシタと、

電源端子が前記第i(i=1〜q−1)のキャパシタの一端に接続され、他端にHighレベルとLowレベルを交互に繰り返すパルス信号の反転信号が入力され、出力部が前記第i(i=1〜q−1)の充電用P型電界効果トランジスタのゲートに接続された第i(i=1〜q−1)のインバータ回路と、を有し、

前記第1のキャパシタの他端には前記パルス信号が供給され、

前記第2、3、・・・、(q−1)のキャパシタの他端は前記第1、2、・・、(q−2)のインバータ回路の出力部が接続され、

前記第(q−1)のインバータ回路の出力部は前記出力端に接続されている第3の昇圧回路、

請求項1記載のn=qとした第1の昇圧回路、

又は請求項2記載のn=qとした第2の昇圧回路

のうちのいずれか一の昇圧回路であって、HighレベルとLowレベルを交互に繰り返すパルス信号として第1主パルス信号が入力され、波高値が前記電源電圧のq倍である前記第1副パルス信号を出力し、

前記第4のパルス信号発生回路は、前記第1の昇圧回路、前記第2の昇圧回路、又は前記第3の昇圧回路のうちのいずれか一の昇圧回路であって、HighレベルとLowレベルを交互に繰り返すパルス信号として第2主パルス信号が入力され、波高値が前記電源電圧のq倍である前記第2副パルス信号を出力する、

ことを特徴とする請求項5から請求項7の何れか1項に記載の昇圧回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004220137A JP4635504B2 (ja) | 2004-07-28 | 2004-07-28 | 昇圧回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004220137A JP4635504B2 (ja) | 2004-07-28 | 2004-07-28 | 昇圧回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006042521A JP2006042521A (ja) | 2006-02-09 |

| JP4635504B2 true JP4635504B2 (ja) | 2011-02-23 |

Family

ID=35906889

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004220137A Expired - Fee Related JP4635504B2 (ja) | 2004-07-28 | 2004-07-28 | 昇圧回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4635504B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4787671B2 (ja) * | 2006-05-16 | 2011-10-05 | 旭化成エレクトロニクス株式会社 | クロック昇圧回路 |

| JP5292912B2 (ja) * | 2008-04-28 | 2013-09-18 | 凸版印刷株式会社 | パルス昇圧回路、およびパルス昇圧方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3190086B2 (ja) * | 1992-01-10 | 2001-07-16 | 株式会社日立製作所 | 昇圧回路 |

| JP3184065B2 (ja) * | 1994-07-25 | 2001-07-09 | セイコーインスツルメンツ株式会社 | 半導体集積回路装置及び電子機器 |

| US6191642B1 (en) * | 1999-03-30 | 2001-02-20 | Silicon Storage Technology, Inc. | Charge pump circuit |

-

2004

- 2004-07-28 JP JP2004220137A patent/JP4635504B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006042521A (ja) | 2006-02-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3488587B2 (ja) | 昇圧回路及びこれを備えたicカード | |

| US6525949B1 (en) | Charge pump circuit | |

| US6359798B1 (en) | Charge pump voltage converter | |

| US7969235B2 (en) | Self-adaptive multi-stage charge pump | |

| US8294509B2 (en) | Charge pump systems with reduction in inefficiencies due to charge sharing between capacitances | |

| US20050093614A1 (en) | Multi stage voltage pump circuit | |

| US8018270B2 (en) | Charge pump circuit | |

| CN101213499A (zh) | 用于广泛电源电压范围的有效电荷泵 | |

| JPH0614529A (ja) | 昇圧電位発生回路 | |

| JP3998278B2 (ja) | 内部電位発生回路 | |

| US7714636B2 (en) | Charge pump circuit and cell thereof | |

| US20090302930A1 (en) | Charge Pump with Vt Cancellation Through Parallel Structure | |

| CN1906832A (zh) | 电荷泵电源 | |

| US8981835B2 (en) | Efficient voltage doubler | |

| TWI520490B (zh) | 高電壓產生器及產生高電壓之方法 | |

| JP4595426B2 (ja) | 4相クロック駆動チャージポンプ回路 | |

| JP4635504B2 (ja) | 昇圧回路 | |

| JP5235944B2 (ja) | 4相クロック駆動チャージポンプ回路 | |

| CN115347782A (zh) | 电压倍增器电路 | |

| CN115622389A (zh) | 电荷泵电路和存储器 | |

| CN103219882A (zh) | 一种cts2电荷泵 | |

| JP4562479B2 (ja) | 2相クロック駆動チャージポンプ回路 | |

| Allasasmeh et al. | Switch bootstrapping technique for voltage doublers and double charge pumps | |

| JP4628375B2 (ja) | 昇圧電位発生ユニット | |

| JP4281359B2 (ja) | チャージポンプ回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070622 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100122 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100216 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100415 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100629 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100827 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101026 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101108 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4635504 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |