JP4549958B2 - 遅延ロックドループ回路 - Google Patents

遅延ロックドループ回路 Download PDFInfo

- Publication number

- JP4549958B2 JP4549958B2 JP2005264131A JP2005264131A JP4549958B2 JP 4549958 B2 JP4549958 B2 JP 4549958B2 JP 2005264131 A JP2005264131 A JP 2005264131A JP 2005264131 A JP2005264131 A JP 2005264131A JP 4549958 B2 JP4549958 B2 JP 4549958B2

- Authority

- JP

- Japan

- Prior art keywords

- clock signal

- change

- logic level

- signal

- reference clock

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

- H03L7/0812—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/07—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop using several loops, e.g. for redundant clock signal generation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/089—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses

- H03L7/0891—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses the up-down pulses controlling source and sink current generators, e.g. a charge pump

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/089—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses

- H03L7/0891—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses the up-down pulses controlling source and sink current generators, e.g. a charge pump

- H03L7/0895—Details of the current generators

Landscapes

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

- Pulse Circuits (AREA)

- Dram (AREA)

Description

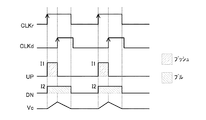

図1は、本発明の第1の実施形態に係る遅延ロックドループ回路の構成を示す。本実施形態に係る遅延ロックドループ回路は、遅延素子10、信号生成回路20、チャージポンプ回路30、及びループフィルタ40を備えている。遅延素子10は、基準クロック信号CLKrを受け、遅延クロック信号CLKdを出力する。遅延クロック信号CLKdの遅延量は、ループフィルタ40から出力された制御電圧Vcによって制御される。信号生成回路20は、基準クロック信号CLKrと遅延クロック信号CLKdの反転との論理積を信号UPとして、また、基準クロック信号CLKrと遅延クロック信号CLKdとの論理積を信号DNとして、それぞれ出力する。チャージポンプ回路30は、電流源301、電流源301が供給する電流I1の通電/遮断を信号UPに従って制御するスイッチ302、電流源303、及び、電流源303が供給する電流I2の通電/遮断を信号DNに従って制御するスイッチ304を備え、信号UPがHiレベルのとき、電流I1を外部へ出力し(プッシュ動作)、信号DNがHiレベルのとき、電流I2を外部から引き込む(プル動作)。ループフィルタ40は、容量401を備え、チャージポンプ回路30の出力を受け、これを積分して制御電圧Vcを生成する。

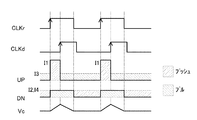

図5は、本発明の第2の実施形態に係る遅延ロックドループ回路の構成を示す。本実施形態に係る遅延ロックドループ回路は、第1の実施形態とは異なる構成の信号生成回路20を備えている。本実施形態に係る信号生成回路20は、基準クロック信号CLKrと遅延クロック信号CLKdの反転との論理積を信号UPとして、また、基準クロック信号CLKrを信号DNとして、それぞれ出力する。以下、本実施形態に係る遅延ロックドループ回路について、第1の実施形態に係る遅延ロックドループ回路と異なる点のみを説明する。

図7は、本発明の第3の実施形態に係る遅延ロックドループ回路の構成を示す。本実施形態に係る遅延ロックドループ回路は、第2の実施形態とは異なる構成のチャージポンプ回路30を備えている。本実施形態に係るチャージポンプ回路30は、第2の実施形態に係るチャージポンプ回路30に、さらに、電流源305、電流源305が供給する電流I3の通電/遮断を信号UPに従って制御するスイッチ306、電流源307、及び、電流源307が供給する電流I4の通電/遮断を信号DNに従って制御するスイッチ308を備えている。以下、第2の実施形態と異なる点についてのみ説明する。

図9は、本発明の第4の実施形態に係る遅延ロックドループ回路の構成を示す。本実施形態に係る遅延ロックドループ回路は、第2及び3の実施形態とは異なる構成のチャージポンプ回路30を備えている。本実施形態に係るチャージポンプ回路30は、第3の実施形態に係るチャージポンプ回路30に、さらに、電流源301と同極性の電流I5を供給する電流源309を備えている。すなわち、本実施形態に係るチャージポンプ回路30では、信号UP及びDNの状態にかかわらず、電流源309から電流I5が常時供給されている。以下、第3の実施形態と異なる点についてのみ説明する。

R2=R3=2R1=R、かつ、Va=(Vdd−Vss)/2=Vdd/2

を満たすように、抵抗311〜313の抵抗値、及び、電圧Vaをそれぞれ設定すると、信号/UP及びDNがそれぞれグランド電圧Vss及び電源電圧Vddとなったとき、抵抗311から信号/UPの入力端に、大きさがVdd/Rの電流が流れ出し、信号DNの入力端から抵抗312に、大きさがVdd/2/Rの電流が流れ込む。また、抵抗311〜313の接続点からグランドノードには、大きさがVdd/2/Rの電流が流れている。したがって、キルヒホッフの法則により、演算増幅器402の出力側から抵抗311〜313の接続点に、容量401を介して電流Vdd/Rが流れ込む。この結果、制御電圧Vcは漸増する。

図12は、本発明の第5の実施形態に係る遅延ロックドループ回路の構成を示す。本実施形態に係る遅延ロックドループ回路は、上記の第1から第4の実施形態に係る遅延ロックドループ回路のいずれか二つを組み合わせた構成をしており、第1の遅延ロックドループ回路は、遅延素子10r、信号生成回路20r、チャージポンプ回路30r、及びループフィルタ40rを備え、第2の遅延ロックドループ回路は、遅延素子10f、信号生成回路20f、チャージポンプ回路30f、及びループフィルタ40fを備えている。第1及び第2の遅延ロックドループ回路は、それぞれ、基準クロック信号CLKrの立ち上がり及び立ち下がりから遅延して論理レベルが変化する遅延クロック信号CLKdr及びCLKdfを出力する。第1及び第2の遅延ロックドループ回路の具体的構成は、第1から第4の実施形態で説明した通りである。また、本実施形態に係る遅延ロックドループ回路はクロック生成回路50を備えている。以下、本実施形態に特徴的な部分についてのみ説明する。

αT/2+(1−α)T/2=T/2

となり、基準クロック信号CLKrのちょうど半分の周期(T/2)となる。すなわち、基準クロック信号CLKrのデューティ比にかかわらず遅延クロック信号CLKdのデューティ比は50%となる。

図15は、本発明の第6の実施形態に係る遅延ロックドループ回路の構成を示す。本実施形態に係る遅延ロックドループ回路は、第5の実施形態に係る遅延ロックドループ回路における第1及び第2の遅延ロックドループ回路に、互いに逆位相関係にある基準クロック信号CLKr及びその反転(以下、「基準クロック信号/CLKr」と表す)を与える構成となっている。

11,11a,11b 反転回路(第1の回路)

12,12A 波形整形回路(第2の回路)

20,20r、20f 信号生成回路

30,30r、30f チャージポンプ回路

40,40r、40f ループフィルタ

50 クロック生成回路

111 トランジスタ(第1のトランジスタ)

112 トランジスタ(第2のトランジスタ)

113 トランジスタ(第3のトランジスタ)

114 トランジスタ(電流源)

121 インバータ

122 トランジスタ

301 電流源(第1の電流源)

302 スイッチ(第1のスイッチ)

303 電流源(第2の電流源)

304 スイッチ(第2のスイッチ)

305 電流源(第3の電流源)

306 スイッチ(第3のスイッチ)

307 電流源(第4の電流源)

308 スイッチ(第4のスイッチ)

309 電流源(第5の電流源)

311 抵抗(第1の抵抗)

312 抵抗(第2の抵抗)

313 抵抗(第3の抵抗)

401 容量

402 演算増幅器

Claims (14)

- 基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御する、遅延ロックドループ回路において、

前記信号生成回路は、前記第1の信号として、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成し、前記第2の信号として、前記基準クロックの第1の変化から第2の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成するものであり、

前記チャージポンプ回路は、

前記第1の動作に係る第1の電流を供給する第1の電流源と、

前記第2の動作に係る第2の電流を供給する第2の電流源と、

前記第1の信号が前記第1の論理レベルのとき、前記第1の電流を通電し、前記第2の論理レベルのとき、前記第1の電流を遮断する第1のスイッチと、

前記第2の信号が前記第1の論理レベルのとき、前記第2の電流を通電し、前記第2の論理レベルのとき、前記第2の電流を遮断する第2のスイッチとを有するものであり、

前記遅延素子は、前記ループフィルタの出力電圧の増大及び減少のいずれか一方に従って前記遅延量を減少し、他方に従って前記遅延量を増大する制御を行うものである

ことを特徴とする遅延ロックドループ回路。 - 請求項1に記載の遅延ロックドループ回路において、

前記第1の電流の大きさは、前記第2の電流の大きさの2倍に相当する

ことを特徴とする遅延ロックドループ回路。 - 基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御する、遅延ロックドループ回路において、

前記信号生成回路は、前記第1の信号として、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成し、前記第2の信号として、前記基準クロックの第1の変化から第2の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成するものであり、

前記チャージポンプ回路は、

前記第1の動作に係る第1及び第4の電流をそれぞれ供給する第1及び第4の電流源と、

前記第2の動作に係る第2及び第3の電流をそれぞれ供給する第2及び第3の電流源と、

前記第1の信号が前記第1の論理レベルのとき、前記第1の電流を通電し、前記第2の論理レベルのとき、前記第1の電流を遮断する第1のスイッチと、

前記第2の信号が前記第1の論理レベルのとき、前記第2の電流を通電し、前記第2の論理レベルのとき、前記第2の電流を遮断する第2のスイッチと、

前記第1の信号が前記第1の論理レベルのとき、前記第3の電流を遮断し、前記第2の論理レベルのとき、前記第3の電流を通電する第3のスイッチと、

前記第2の信号が前記第1の論理レベルのとき、前記第4の電流を遮断し、前記第2の論理レベルのとき、前記第4の電流を通電する第4のスイッチとを有するものであり、

前記遅延素子は、前記ループフィルタの出力電圧の増大及び減少のいずれか一方に従って前記遅延量を減少し、他方に従って前記遅延量を増大する制御を行うものである

ことを特徴とする遅延ロックドループ回路。 - 請求項3に記載の遅延ロックドループ回路において、

前記第2から第4の電流の大きさはいずれも等しく、かつ、前記第1の電流の大きさは、前記第2から第4の電流の大きさの3倍に相当する

ことを特徴とする遅延ロックドループ回路。 - 基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御する、遅延ロックドループ回路において、

前記信号生成回路は、前記第1の信号として、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成し、前記第2の信号として、前記基準クロックの第1の変化から第2の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成するものであり、

前記チャージポンプ回路は、

前記第1の動作に係る第1、第4及び第5の電流をそれぞれ供給する第1、第4及び第5の電流源と、

前記第2の動作に係る第2及び第3の電流をそれぞれ供給する第2及び第3の電流源と、

前記第1の信号が前記第1の論理レベルのとき、前記第1の電流を通電し、前記第2の論理レベルのとき、前記第1の電流を遮断する第1のスイッチと、

前記第2の信号が前記第1の論理レベルのとき、前記第2の電流を通電し、前記第2の論理レベルのとき、前記第2の電流を遮断する第2のスイッチと、

前記第1の信号が前記第1の論理レベルのとき、前記第3の電流を遮断し、前記第2の論理レベルのとき、前記第3の電流を通電する第3のスイッチと、

前記第2の信号が前記第1の論理レベルのとき、前記第4の電流を遮断し、前記第2の論理レベルのとき、前記第4の電流を通電する第4のスイッチとを有するものであり、

前記遅延素子は、前記ループフィルタの出力電圧の増大及び減少のいずれか一方に従って前記遅延量を減少し、他方に従って前記遅延量を増大する制御を行うものである

ことを特徴とする遅延ロックドループ回路。 - 請求項5に記載の遅延ロックドループ回路において、

前記第1の電流の大きさと前記第3の電流の大きさとは等しく、前記第2、第4及び第5の電流の大きさはいずれも等しく、かつ、前記第1及び第3の電流の大きさは、前記第2、第4及び第5の電流の大きさの2倍に相当する

ことを特徴とする遅延ロックドループ回路。 - 基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御する、遅延ロックドループ回路において、

前記信号生成回路は、前記第1の信号として、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、第1の電圧となり、これ以外のとき、第2の電圧となる信号を生成し、前記第2の信号として、前記基準クロックの第1の変化から第2の変化までの間、前記第2の電圧となり、これ以外のとき、前記第1の電圧となる信号を生成するものであり、

前記チャージポンプ回路は、

前記第1の信号を受ける第1の抵抗と、

前記第2の信号を受ける第2の抵抗と、

一端が前記第1及び第2の抵抗の接続箇所に接続され、他端に第3の電圧が与えられた第3の抵抗とを有するものであり、

前記ループフィルタは、

容量と、

負帰還部分に前記容量が接続され、反転入力端が前記チャージポンプ回路における第1から第3の抵抗の接続箇所に接続され、非反転入力端に第4の電圧が与えられた演算増幅器とを有するものであり、

前記遅延素子は、前記ループフィルタにおける演算増幅器の出力電圧の増大及び減少のいずれか一方に従って前記遅延量を減少し、他方に従って前記遅延量を増大する制御を行うものである

ことを特徴とする遅延ロックドループ回路。 - 請求項7に記載の遅延ロックドループ回路において、

前記第2の電圧と前記第3の電圧とは等しく、

前記第4の電圧は、前記第1の電圧と前記第2の電圧との中間に相当する電圧であり、

前記第2の抵抗の抵抗値と前記第3の抵抗の抵抗値とは等しく、

前記第1の抵抗の抵抗値は、前記第2及び第3の抵抗の抵抗値の半分に相当する

ことを特徴とする遅延ロックドループ回路。 - 基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて相補的に変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御する、遅延ロックドループ回路において、

前記遅延素子は、

直列に接続され、ゲートに前記基準クロック信号を受ける互いに逆極性の第1及び第2のトランジスタ、及びこれらトランジスタの間に挿入されて接続され、ゲートに前記ループフィルタの出力を受ける第3のトランジスタを有し、前記第1のトランジスタと前記第3のトランジスタとの接続点の電圧を出力信号とする第1の回路と、

前記第1の回路の出力信号の波形を整形する第2の回路とを備えたものであり、

前記第1の回路は、前記第3のトランジスタに並列に接続された電流源を有する

ことを特徴とする遅延ロックドループ回路。 - 基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて相補的に変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御する、遅延ロックドループ回路において、

前記遅延素子は、

直列に接続され、ゲートに前記基準クロック信号を受ける互いに逆極性の第1及び第2のトランジスタ、及びこれらトランジスタの間に挿入されて接続され、ゲートに前記ループフィルタの出力を受ける第3のトランジスタを有し、前記第1のトランジスタと前記第3のトランジスタとの接続点の電圧を出力信号とする第1の回路と、

前記第1の回路の出力信号の波形を整形する第2の回路とを備えたものであり、

前記第2の回路は、

前記第1の回路の出力信号を受けるインバータと、

前記インバータの入力及び出力をそれぞれドレイン及びゲートに受け、ソースに所定の電圧が与えられたトランジスタを有する

ことを特徴とする遅延ロックドループ回路。 - 共通の基準クロック信号が与えられる第1及び第2の遅延ロックドループ回路と、

前記第1及び第2の遅延ロックドループ回路の出力クロック信号から、前記共通の基準クロック信号の立ち上がりから遅延して立ち上がり及び立ち下がりのいずれか一方の変化が生じる一方、前記共通の基準クロック信号の立ち下がりから遅延して立ち上がり及び立ち下がりの他方の変化が生じる遅延クロック信号を生成するクロック生成回路とを備え、

前記第1及び第2の遅延ロックドループ回路は、それぞれ、

基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて相補的に変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御する

ことを特徴とする遅延ロックドループ回路。 - 請求項11に記載の遅延ロックドループ回路において、

前記第1の遅延ロックドループ回路は、前記共通の基準クロック信号の立ち上がりから、前記共通の基準クロック信号のオンデューティの半分に相当する期間遅延して、論理レベルが変化するクロック信号を出力するものであり、

前記第2の遅延ロックドループ回路は、前記共通の基準クロック信号の立ち下がりから、前記共通の基準クロック信号のオフデューティの半分に相当する期間遅延して、論理レベルが変化するクロック信号を出力するものである

ことを特徴とする遅延ロックドループ回路。 - 第1の基準クロック信号が与えられる第1の遅延ロックドループ回路と、

前記第1の基準クロック信号とは逆位相の第2の基準クロック信号が与えられる第2の遅延ロックドループ回路と、

前記第1及び第2の遅延ロックドループ回路の出力クロック信号から、前記第1の基準クロック信号の立ち上がりから遅延して立ち上がり及び立ち下がりのいずれか一方の変化が生じる一方、前記第1の基準クロック信号の立ち下がりから遅延して立ち上がり及び立ち下がりの他方の変化が生じる遅延クロック信号を生成するクロック生成回路とを備え、

前記第1及び第2の遅延ロックドループ回路は、それぞれ、

基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて相補的に変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御する

ことを特徴とする遅延ロックドループ回路。 - 請求項13に記載の遅延ロックドループ回路において、

前記第1の遅延ロックドループ回路は、前記第1の基準クロック信号の立ち上がりから、前記第1の基準クロック信号のオンデューティの半分に相当する期間遅延して、論理レベルが変化するクロック信号を出力するものであり、

前記第2の遅延ロックドループ回路は、前記第2の基準クロック信号の立ち上がりから、前記第2の基準クロック信号のオンデューティの半分に相当する期間遅延して、論理レベルが変化するクロック信号を出力するものである

ことを特徴とする遅延ロックドループ回路。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005264131A JP4549958B2 (ja) | 2005-02-09 | 2005-09-12 | 遅延ロックドループ回路 |

| US11/289,753 US20060176091A1 (en) | 2005-02-09 | 2005-11-30 | Delay locked loop circuit |

| US12/033,707 US7705645B2 (en) | 2005-02-09 | 2008-02-19 | Delay locked loop circuit |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005033625 | 2005-02-09 | ||

| JP2005264131A JP4549958B2 (ja) | 2005-02-09 | 2005-09-12 | 遅延ロックドループ回路 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010108178A Division JP4815005B2 (ja) | 2005-02-09 | 2010-05-10 | 遅延ロックドループ回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006254401A JP2006254401A (ja) | 2006-09-21 |

| JP2006254401A5 JP2006254401A5 (ja) | 2008-04-10 |

| JP4549958B2 true JP4549958B2 (ja) | 2010-09-22 |

Family

ID=36779333

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005264131A Expired - Fee Related JP4549958B2 (ja) | 2005-02-09 | 2005-09-12 | 遅延ロックドループ回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US20060176091A1 (ja) |

| JP (1) | JP4549958B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7475310B2 (en) * | 2006-08-09 | 2009-01-06 | Advantest Corporation | Signal output circuit, and test apparatus |

| US7459949B2 (en) * | 2007-01-30 | 2008-12-02 | Mosaid Technologies Incorporated | Phase detector circuit and method therefor |

| JP5389524B2 (ja) * | 2009-05-14 | 2014-01-15 | セミコンダクター・コンポーネンツ・インダストリーズ・リミテッド・ライアビリティ・カンパニー | 遅延回路 |

| US8076963B2 (en) * | 2009-09-15 | 2011-12-13 | Qualcomm Incorporated | Delay-locked loop having a delay independent of input signal duty cycle variation |

| US8970260B1 (en) * | 2013-11-21 | 2015-03-03 | Nxp B.V. | Output drivers |

| KR102005337B1 (ko) * | 2014-01-09 | 2019-07-30 | 에스케이하이닉스 주식회사 | 전압 변환 장치 |

| CN106600853B (zh) * | 2016-12-06 | 2019-06-18 | 青岛海信智能商用系统股份有限公司 | 用于充电底座的充电或信号传输防抖动电路及充电底座 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5257760A (en) * | 1975-11-07 | 1977-05-12 | Hitachi Ltd | Phase lock loop circuit |

| JPS6036908Y2 (ja) * | 1977-11-30 | 1985-11-01 | 三洋電機株式会社 | 自動位相制御方式の位相比較器 |

| JPS5619769A (en) | 1979-07-26 | 1981-02-24 | Ricoh Co Ltd | Ink-jet recording device |

| NL8302228A (nl) | 1983-06-22 | 1985-01-16 | Optische Ind De Oude Delft Nv | Meetstelsel voor het onder gebruikmaking van een op driehoeksmeting berustend principe, contactloos meten van een door een oppervlakcontour van een objectvlak gegeven afstand tot een referentieniveau. |

| JPH07109212B2 (ja) | 1986-09-16 | 1995-11-22 | 株式会社ブリヂストン | 防振ゴムの取付ボルト用キヤツプ |

| JPS6372937U (ja) * | 1986-10-31 | 1988-05-16 | ||

| US5675620A (en) * | 1994-10-26 | 1997-10-07 | At&T Global Information Solutions Company | High-frequency phase locked loop circuit |

| JPH08180678A (ja) * | 1994-12-27 | 1996-07-12 | Hitachi Ltd | ダイナミック型ram |

| KR100245077B1 (ko) * | 1997-04-25 | 2000-02-15 | 김영환 | 반도체 메모리 소자의 딜레이 루프 럭크 회로 |

| JPH118552A (ja) * | 1997-06-18 | 1999-01-12 | Nec Eng Ltd | 位相同期発振器 |

| JP2908398B1 (ja) | 1998-01-14 | 1999-06-21 | 日本電気アイシーマイコンシステム株式会社 | ディジタルpll回路および発振器の遅延素子 |

| US5969552A (en) * | 1998-01-15 | 1999-10-19 | Silicon Image, Inc. | Dual loop delay-locked loop |

| KR100301043B1 (ko) * | 1998-08-08 | 2001-09-06 | 윤종용 | 지연동기루프의위상비교기및지연동기방법 |

| US6100735A (en) * | 1998-11-19 | 2000-08-08 | Centillium Communications, Inc. | Segmented dual delay-locked loop for precise variable-phase clock generation |

| US6204705B1 (en) * | 1999-05-28 | 2001-03-20 | Kendin Communications, Inc. | Delay locked loop for sub-micron single-poly digital CMOS processes |

| KR100366618B1 (ko) * | 2000-03-31 | 2003-01-09 | 삼성전자 주식회사 | 클럭 신호의 듀티 사이클을 보정하는 지연 동기 루프 회로및 지연 동기 방법 |

| JP3807593B2 (ja) * | 2000-07-24 | 2006-08-09 | 株式会社ルネサステクノロジ | クロック生成回路および制御方法並びに半導体記憶装置 |

| US6868504B1 (en) * | 2000-08-31 | 2005-03-15 | Micron Technology, Inc. | Interleaved delay line for phase locked and delay locked loops |

| JP2002158582A (ja) * | 2000-11-20 | 2002-05-31 | Mitsubishi Electric Corp | Pll回路 |

| US8934597B2 (en) * | 2003-03-12 | 2015-01-13 | Infineon Technologies Ag | Multiple delay locked loop integration system and method |

| US7091763B1 (en) * | 2003-11-03 | 2006-08-15 | Lattice Semiconductor Corporation | Clock generation |

| US7528638B2 (en) * | 2003-12-22 | 2009-05-05 | Micron Technology, Inc. | Clock signal distribution with reduced parasitic loading effects |

| US7499513B1 (en) * | 2004-12-23 | 2009-03-03 | Xilinx, Inc. | Method and apparatus for providing frequency synthesis and phase alignment in an integrated circuit |

| KR100644127B1 (ko) * | 2005-01-03 | 2006-11-10 | 학교법인 포항공과대학교 | 무한의 위상 이동 기능을 가지는 전압 제어 지연 라인을기반으로 하는 듀얼 루프 디엘엘 |

| US7199625B1 (en) * | 2005-09-20 | 2007-04-03 | Infineon Technologies Ag | Delay locked loop structure providing first and second locked clock signals |

| US7583117B2 (en) * | 2006-04-20 | 2009-09-01 | Realtek Semiconductor Corp. | Delay lock clock synthesizer and method thereof |

-

2005

- 2005-09-12 JP JP2005264131A patent/JP4549958B2/ja not_active Expired - Fee Related

- 2005-11-30 US US11/289,753 patent/US20060176091A1/en not_active Abandoned

-

2008

- 2008-02-19 US US12/033,707 patent/US7705645B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20080303567A1 (en) | 2008-12-11 |

| US7705645B2 (en) | 2010-04-27 |

| JP2006254401A (ja) | 2006-09-21 |

| US20060176091A1 (en) | 2006-08-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100842695B1 (ko) | 듀티 검출 회로 및 그 제어 방법 | |

| US7893725B2 (en) | Delay locked loop circuit | |

| EP1966887B1 (en) | Phase interpolator | |

| KR100507873B1 (ko) | 듀티 보정 회로를 구비한 아날로그 지연고정루프 | |

| US7634039B2 (en) | Delay-locked loop with dynamically biased charge pump | |

| JP5143370B2 (ja) | 遅延制御回路 | |

| US6204705B1 (en) | Delay locked loop for sub-micron single-poly digital CMOS processes | |

| KR20100037427A (ko) | Ac 커플링 위상 보간기 및 이 장치를 이용하는 지연 고정루프 | |

| US6750689B2 (en) | Method and apparatus for correcting a clock duty cycle in a clock distribution network | |

| JP2009165109A (ja) | 半導体素子、クロック同期化回路、及び、クロック同期化回路の駆動方法 | |

| JP2006135998A (ja) | 位相同期ループ及び遅延同期ループ | |

| US7705645B2 (en) | Delay locked loop circuit | |

| KR100568538B1 (ko) | 자기 바이어스 위상 동기 루프 | |

| JP5153789B2 (ja) | 遅延ロックループ/フェーズロックループにおける移相処理 | |

| CN1972129A (zh) | 电荷泵电路及其方法 | |

| JP2001274682A (ja) | フェーズロックドループ回路 | |

| KR100711103B1 (ko) | 적응형 3상태 위상 주파수 검출기 및 검출방법과 이를이용한 위상동기루프 | |

| JP4815005B2 (ja) | 遅延ロックドループ回路 | |

| US7081781B2 (en) | Charge pump for a low-voltage wide-tuning range phase-locked loop | |

| JP2007295180A (ja) | チャージポンプ回路、それを用いたpll回路及びdll回路 | |

| JP3747578B2 (ja) | 電圧制御差動遅延素子、電圧制御発振器、位相ループ、電圧制御差動遅延素子を製造する方法、製造するシステムおよび使用する方法。 | |

| JP2008072597A (ja) | 遅延ロックループ回路 | |

| KR20080023496A (ko) | 듀티비 조절 회로 및 그 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080221 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080221 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091008 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091013 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091214 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100209 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100510 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20100518 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100615 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100707 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4549958 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130716 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |