JP4481490B2 - 二値加算器 - Google Patents

二値加算器 Download PDFInfo

- Publication number

- JP4481490B2 JP4481490B2 JP2000539394A JP2000539394A JP4481490B2 JP 4481490 B2 JP4481490 B2 JP 4481490B2 JP 2000539394 A JP2000539394 A JP 2000539394A JP 2000539394 A JP2000539394 A JP 2000539394A JP 4481490 B2 JP4481490 B2 JP 4481490B2

- Authority

- JP

- Japan

- Prior art keywords

- output

- optical

- optical logic

- logic element

- input

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/38—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation

- G06F7/48—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation using non-contact-making devices, e.g. tube, solid state device; using unspecified devices

- G06F7/50—Adding; Subtracting

- G06F7/505—Adding; Subtracting in bit-parallel fashion, i.e. having a different digit-handling circuit for each denomination

- G06F7/5055—Adding; Subtracting in bit-parallel fashion, i.e. having a different digit-handling circuit for each denomination in which one operand is a constant, i.e. incrementers or decrementers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06E—OPTICAL COMPUTING DEVICES; COMPUTING DEVICES USING OTHER RADIATIONS WITH SIMILAR PROPERTIES

- G06E1/00—Devices for processing exclusively digital data

- G06E1/02—Devices for processing exclusively digital data operating upon the order or content of the data handled

- G06E1/04—Devices for processing exclusively digital data operating upon the order or content of the data handled for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/38—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation

- G06F7/48—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation using non-contact-making devices, e.g. tube, solid state device; using unspecified devices

- G06F7/50—Adding; Subtracting

- G06F7/504—Adding; Subtracting in bit-serial fashion, i.e. having a single digit-handling circuit treating all denominations after each other

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Computational Mathematics (AREA)

- Mathematical Analysis (AREA)

- Pure & Applied Mathematics (AREA)

- Computing Systems (AREA)

- Mathematical Optimization (AREA)

- General Engineering & Computer Science (AREA)

- Optical Communication System (AREA)

- Image Analysis (AREA)

Description

発明の属する技術分野

この発明は第1と第2の光二値ワードでそれぞれが多数の光ビットスロットを有するものについての和を決めるための装置と方法とに関する。

【0002】

従来の技術

全光式処理の分野では、光信号流(ストリーム)がデータ処理応用に使用される。こういった光ストリームは光パルス列(トレーン)で成り、それが一連のビットスロットに分けられている。各ビットスロットはパルス列内部で所定の長さをもち、データの単一ビットを表わし、相補的な論理状態を表わしているビットスロット内部に光パルスが存在するものか欠如しているものかとなっている。したがって、例えば、あるパルスが存在することは二値の“1”を表わし、また光パルスが存在しなければ二値“0”を表わすか、あるいはその逆とすることができる。この応用ではしたがって、“光二値ワード(optical binary word)”という用語を使用してこのようなやり方で光によって表わされた二値ワードを意味するようにしている。

【0003】

発明が解決しようとする課題

必要とされている基本的な光処理応用の1つは、多数のビットスロットで成る2つの光二値ワードの二値和を生成することができる能力である。

【0004】

課題を解決するための手段および実施の形態

この発明の第1の特徴により、我々は第1と第2の光二値ワードの和を決めるための装置を提供し、ここで各ワードはLの光ビットスロットを有し、各ビットスロットは第1と第2の論理状態のそれぞれの1つを表わしており、この装置の構成は、

印加された二値ワードの第1の論理組合せを表わす第1の組合せワードを生成する第1の光論理ゲートと;

印加された二値ワードの第2の論理組合せを表わす第2の組合せワードを生成する第2の光論理ゲートと;

第1と第2の組合せワードを互に1ビットスロットだけオフセットして第1と第2のオフセットした組合せワードを生成するためのオフセット手段と;

印加された二値ワードの第1と第2の論理組合せを表わす第1と第2の組合せワードをそれぞれ生成する第1と第2の論理ゲートに、前に生成された第1と第2のオフセットした組合せワードを繰返し印加するための手段とで成り、

ここで第1と第2のオフセットした組合せワードが最初は該第1と第2の二値ワードを含み、該二値の和は第2の組合せワードの各ビットスロットが同じ論理状態をもつときに第1の組合せワードによって与えられるものである。

【0005】

この発明の第2の特徴により、我々は第1と第2の光二値ワードの和を決めるための方法を提供し、そこで各ワードはLの光ビットスロットを有し、各ビットスロットは第1と第2の論理状態のそれぞれ1つを表わしており、この方法は:

1)第1と第2のオフセットした組合せワードの第1の論理組合せを表わす第1の組合せワードを生成する段階と;

2)第1と第2のオフセットした組合せワードの第2の論理組合せを表わす第2の組合せワードを生成する段階と;

3)該第1の組合せワードを第2の組合せワードに対して1ビットスロットだけオフセットすることにより第1と第2のオフセットした組合せワードを生成する段階と;

4)段階1),2)及び3)を第2の組合せワードの各ビットスロットが同じ論理状態となるまで連続して繰返す段階とを含み、

第1と第2のオフセットした組合せワードが最初は第1と第2の二値ワードを含んでいて、第二の組合せワードの各ビットスロットが同じ論理状態をもつときに第1の組合せワードによって該二値の和が与えられるようになっている。

【0006】

我々は第1と第2の光二値ワードの和を生成するための装置と方法とを設計した。これは光二値ワードの第1と第2の組合せを表わす第1と第2の組合せワードを、第1と第2の光論理ゲートを使用して、生成することにより達成された。こういった光組合せワードは次に互にオフセットされて再結合されて、別の組合せワードを生成するようにした。このプロセスを繰返して、第2の組合せワードの各ビットスロットが同じ論理状態となるまで繰返し、第1と第2の二値ワードの二値の和が決められるようになる。

【0007】

一般に、第1と第2の論理ゲートは、第1と第2の入力として組合せることになる二値ワードを受領するためのものを有しているが、単一の入力が組合されることになる、連続して加えられる、二値ワードとともに利用されることになる。

【0008】

好ましいのは、前に生成された第1と第2のオフセットした組合せワードを第1と第2の論理ゲートに繰返し印加するための手段の構成が第1の論理ゲートの出力から第1と第2の論理ゲートの第2の入力への接続と、第2の論理ゲートの出力から第1と第2の論理ゲートの第1の入力への接続とを含むことである。これが実効的に帰還システムとなっていて、各論理ゲートの出力で生成された組合せワードが両論理ゲートの入力への帰還となるようにしている。

【0009】

これに代るものもあり、フィードフォワードシステムも採用できるのであって、ここでは前に生成された第1と第2のオフセットした組合せワードを第1と第2の論理ゲートに繰返し印加するための手段はNの第1と第2の光論理ゲート対を含み、各第1と第2の論理ゲート対の構成は:

印加された二値ワードの第1の論理組合せを表わす第1の組合せワードを生成する第1の光論理ゲートと;

印加された二値ワードの第2の論理組合せを表わす第2の組合せワードを生成する第2の光論理ゲートと;

第1と第2の組合せワードを互に1ビットスロットだけオフセットして第1と第2のオフセットした組合せワードを生成するためのオフセット手段とを含み、

ここで該オフセット手段は下流の第1と第2の光論理ゲート対に接続されて生成された第1と第2のオフセットした組合せワードが下流の第1と第2の光論理ゲート対の第1と第2の論理ゲートに印加されるようにしている。

【0010】

帰還(フィードバック)システムではオフセット手段は一般にLビットスロット遅延線を含み、それが第1の光論理ゲートの出力に接続されていて、また(L+1)か(L−1)ビットスロット遅延線を含んでいて、それが第2の光論理ゲートの出力に接続されている。1ビットスロット遅延を導入する適切な方法はどんなものでも使用できるが、高ビットレートで単一ビットスロット遅延を導入することはむづかしい。したがって、Lと、(L+1)か(L−1)かのいずれかとのビット遅延線を使用して1ビットスロットオフセットが関連する光二値ワード間で生成されることとなるようにするのが好い。さらに、Lと(L+1)または(L−1)ビットスロット遅延を用いることによって、出力組合せワードが後に論理ゲートの入力に帰還できて、前に入力したワードに対して干渉をしなくともそれができる。

【0011】

(L+1)もしくは(L−1)ビットスロット遅延の使用は光二値ワードのフォーマットに依存することになる。したがって、もし光二値ワードの第1のビットスロットが加えられることになる二値数の最下位ビットを表わしているとすると、(L+1)ビットスロット遅延が使用される。これに対して、第1のビットスロットが最上位ビットを表わしていれば、そのときは(L−1)ビットスロット遅延が使用される。

【0012】

論議を容易にするために、以下の明細書では例として第1のビットスロットが加算されることになる二値数の最下位ビット(LSB)を、ことわりのない限り、表わすこととする。したがって、(L+1)ビットスロット遅延の使用が仮定されることになる。違った光二値ワードフォーマットについては(L−1)ビットスロット遅延が使用されることは理解できると思う。

【0013】

一般に帰還システムでは第1の論理ゲートから第1と第2の論理ゲートの第2の入力への接続はLビットスロット遅延線を含み、またここでは追加の接続が採用できるが第2の論理ゲートの出力から第1と第2の論理ゲートの第1の入力への接続が(L+1)もしくは(L−1)のいずれかのビットスロット遅延線を含んでいる。

【0014】

帰還装置にはさらに光コンバイナが含まれているのがよく、この光コンバイナは(L+1)ビットスロット遅延線に接続された第1のコンバイナ入力と、第1と第2の光二値ワードを受領する第2のコンバイナ入力と、第1と第2の論理ゲートの第1の入力に接続されたコンバイナ出力とを有している。

【0015】

この光コンバイナは2つの光二値ワードの和を計算するために必要ではないが、コンバイナの存在はこの回路の動作に影響を与えてはいない。さらに、以下で説明するように、この回路へは2よりも多い光ワードを入力することが時として望まれる。この場合には、コンバイナが用意されてこの回路に供給された光ワードが回路内にすでに存在している光パルスと干渉するように混合するのを防ぐようにする。

【0016】

光コンバイナは第1と第2の入力で受領したビットスロットを組合せることによって動作して、もしビットスロットが同一の論理状態をもっていれば、このコンバイナの出力が第1の論理状態をもつビットスロットを生成し、またビットスロットが異なる論理状態をもってれば、コンバイナ出力が第2の論理状態をもつビットスロットを生成する。使用時には、これが第1と第2のワードをシーケンスとして第2のコンバイナ入力に供給できるようにして、第1と第2のワードがそれぞれ第1と第2の光論理ゲートの第1と第2の入力にそれぞれ加えられるようにしている。

【0017】

フィードフォワードシステムでは、オフセット手段は一般にMビットスロット遅延線を含み、これが第1の論理ゲートを下流の第1と第2の論理ゲート対の第2のゲート入力に接続し、また(M+1)ビットスロット遅延線を含み、これが第2の論理ゲートを下流の第1と第2の論理ゲート対の第1のゲート入力に接続して、第1の組合せワードの転送が第2の組合せワードの転送に対して1ビットスロットだけ遅れるようにしている。1ビットスロット遅延を導入するいずれかの適当な方法が使用できるが、高ビットレートで単一のビットスロット遅延を導入することは非常にむづかしい。したがって、Mと(M+1)ビット遅延をM>1について用いるのが好ましく、関連の光二値ワード間で1ビットスロットオフセットが生成できるようにする。

【0018】

ここでもまた、フィードフォワードシステムに関して記述したように、(M−1)ビットスロット遅延線が(M+1)ビットスロット遅延線に代って使用できるのであって、その条件としては光二値ワードのフォーマットが第1のビットスロット内の最上位ビット(MSB)であるとしている。

【0019】

好ましいのは、N番目の第1と第2の論理ゲート対が帰還装置でN番目の第1と第2の光論理ゲート対のMビットスロット遅延線を備えたものを含んでいることであり、このゲート対はLビットスロット遅延線によって構成されている。またこの帰還装置は(L+1)ビットスロット遅延線により構成されているN番目の第1と第2の光論理ゲート対の(M+1)ビットスロット遅延線を備えているのが好い。このような構成はこの発明のフィードバック(帰還)とフィードフォワードの特徴の両方の利点を組合せている。

【0020】

好ましいのは、各第1の論理ゲートがXORゲートを含み、そこでは各第2の論理ゲートがANDゲートを含むことである。しかしながら、この発明は相補的な論理を用いて実現することができ、この場合には代りの論理ゲートはXNORとNANDゲートのようなものとなってそれらが使用されることになる。

【0021】

一般に、各光ANDゲートは全光式非線形ゲートであり、そこでは第2の論理状態をもつビットスロットを第1の入力に印加することは第2の入力と出力との間の接続を単一ビットスロットに対応する時間間隔について選択的にスイッチして、第2の入力から出力への単一ビットスロットの転送をするようにし、それによってビットスロットが第1と第2の入力で受領したビットスロットの論理ANDを表わす出力で生成される。これが光ワードを組合せて2つのワードの論理ANDを生成するための簡単な手段を提供している。

【0022】

一般に、各光XORゲートは光コンバイナを含み、この光コンバイナは第1のコンバイナ出力でXORゲートの第1の入力に接続されたものと;第2のコンバイナ入力でXORゲートの第2の入力に接続されているものと;コンバイナ出力とを備えていて、ここでもし第1と第2のコンバイナ入力で受けたビットスロットが同一の論理状態を有しているとすると、第1の論理状態を有するビットスロットがコンバイナ出力で生成され、またもし第1と第2の入力で受けたビットスロットが異なる論理状態を有しているとすると、第2の論理状態を有するビットスロットがコンバイナ出力で生成される。この装置は第1と第2の二値ワードの論理XORを生成する簡単な方法を提供している。

【0023】

一般に、XORゲートはさらに第2の論理状態を有するビットスロットの流を生成する源(ソース)と、全光式非線形ゲートと、該源と接続されたゲート入力を含む非線形ゲートと、XORゲート出力に接続されたゲート出力と、光コンバイナ出力に接続されたゲートスイッチング入力とを備えていて、ここでは第2の論理状態を有するビットスロットをゲートスイッチング入力に印加することが、ゲート入力とゲート出力との間の接続を単一ビットスロットに対応する時間間隔にわたり選択的に切換えて、ゲート入力からゲート出力へ単一ビットスロットを転送するようにする。これが組合されたワードの論理XORを表わす光ワードの光学的品質を良質なものとし、回路の他部での使用に対して正しいフォーマットのものとなることを確保している。

【0024】

一般に、第2の論理状態は単一の光パルスを含むビットスロットによって定義されるが、これは回路の特定の実施に依存したものとなり、したがって単一の光パルスを含むビットスロットが第1の論理状態を定義できる。

【0025】

一般に、第1の組合せワードは二値和を表わし、その条件として第2の二値ワードの各ビットスロットが第1の論理状態を表わしているときとされるが、ここでもまた、これは回路の特定の実施に依存している。

【0026】

この発明の第3の特徴により、我々は多数の二値ワードを計数する方法を提供している。ここでは、各二値ワードはLビットスロットを有し、第1のL番目のビットスロットは第2の論理状態をもち、残りのL−1ビットスロットは第1の論理状態を有しており、この方法は:

1)第1と第3の組合せ二値ワードの第1の論理組合せを表わす第1の組合せワードを生成する段階と;

2)第1と第3の組合せ二値ワードの第2の論理組合せを表わす第2の組合せワードを生成する段階と;

3)該第1の組合せワードを第2の組合せワードに対して1ビットスロットだけオフセットすることにより第1と第2のオフセットした組合せワードを生成する段階と;

4)別の二値ワードに該オフセットした第2の組合せワードを組合せることにより第3の組合せワードを生成する段階と;

5)前記多数の二値ワードが組合されて第2の組合せワードの各ビットスロットが同じ論理状態となるまで該段階1),2),3)及び4)を連続して繰返す段階とを含み、

該第1と第2のオフセットした組合せワードの各々は最初は二値ワードの前記多数のうちの1つを含んでいて、前記多数の二値ワードの計数値が第2の組合せワードの各ビットスロットが同じ論理状態をもつときに第1の組合せワードによって与えられるようになっている。

【0027】

一般にこの発明のいずれの方法でも、第1の論理組合せはXOR組合せを含み、また第2の論理組合せはAND組合せを含んでいる。しかしながら、この方法は相補的な論理を用いて実施できるものであり、その場合には代りとなる論理組合せが使用されることになる。

【0028】

一般にこの方法は第2の組合せワードの各ビットスロットが第2の論理状態をもつまで連続して繰返されるが、これはこの方法の実施に依存することになる。

【0029】

好ましいのは第2の論理状態が単一の光パルスを含んでいるビットスロットによって定義されることであるが、単一の光パルスを含んでいるビットスロットは第1の論理状態を定義してもよいものである。

【0030】

第1のビットスロットが第2の論理状態を有している場合には、第1と第2のオフセットした組合せワードはMビットスロットに対応する時間期間だけ第1の組合せワードを一時的に記憶し、また(M+1)ビットスロットに対応する時間期間だけ第2の組合せワードを時間的に記憶することにより生成されるのがよい。これと対照的に、もしL番目ビットスロットが第2の論理状態を有していれば、そのときは第2の組合せワードは(M−1)ビットスロットに対応する時間期間だけ記憶される。フィードフォワードシステムに関して上記説明した通り、Mビットスロットと、(M+1)もしくは(M−1)のいずれかのビットスロットとの遅延を使用することは高ビットレートでの単一ビットスロット遅延の導入と関係する問題を克服する。

【0031】

この発明の第2の特徴による方法はこの発明の第1の特徴による装置を利用して実行されるのが好ましい。

【0032】

一般にはこの発明の第3の特徴による方法は、上述のようにこの発明の第1の特徴による装置がさらに光コンバイナを備えるときにはそれを利用して実行することができる。

【0033】

実施例

添付の図面を参照してこの発明の例を記述して行く。

【0034】

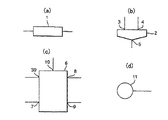

この発明を理解するために、ある種の記号が記述にあたり図中で使用されており、それらの記号(シンボル)を図1(a)ないし1(d)に示し、またそのもつ意味を記述して行く。

【0035】

図1(a)は遅延線1を示し、これは遅延線1の一端に印加された光パルス流(ストリーム)の他端への転送を所定時間期間だけ遅らせるように動作する。この時間期間は通常はビットスロットの所定数に対応している。遅延は光ファイバの長さ、シリカの平面導波路、もしくは自由空間経路のあるいは同種のもののいずれかを用いて得られ、光パルスが素子の長さを移動するために所定量の時間をとるようにしている。

【0036】

ある遅延線上の遅延の長さは導波路、自由空間経路、もしくは使用される光ファイバの物理的長さに依存することになり、また特定の伝送媒体の屈折率(この媒体内部での光速度に影響を与えることになる)にも依存している。

【0037】

図1(b)は全光式組合せ器(コンバイナ)2を示し、ここには2つのコンバイナ入力3,4と1つのコンバイナ出力とがある。コンバイナ2は2つの光パルス流で2つのコンバイナ入力3,4に加えられたものをパルスの干渉形混合を回避するやり方で組合せる。

【0038】

実用上は、このことは通常、2つの異なるパルス流のパルスがそれぞれのビットスロット内部の異なる位置に置かれるようにし、パルスが時間的には重ならないが同じビットスロット内に依然としてあるようにして達成されている。しかしこれに代るものとして、直交偏光した光コンバイナ入力をもつようにし、受領した光パルス流が少くとも若干の成分が偏光素子を通って進むようにしてこれを達成することができる。

【0039】

このパルスの非干渉混合の結果として、いずれもの1ビットスロット内での光コンバイナからの全光エネルギー出力が受領した全エネルギーの和となっている。

【0040】

光コンバイナは通常は光ファイバカップラ(結合器)か、シリカプレーナ導波路か、バルクビームスプリッタの形をとる。

【0041】

図1(c)は全光式非線形ゲート6を示し、ファイバ非線形光ループミラー(NOLM)か、ファイバNOLMでオフセット半導体増幅器を備えたものか、集積されたプレーナNOLMのような非線形光スイッチング素子の形をしている。マッハ・ツェンダー,マイケルソン及び時分割形式のこの種のデバイスも可能ではあるが、この明細書では詳細にまでは考察しないこととする。この形式の光スイッチング素子の特別な形式はテトラヘルス光非対称デマルチプレクサ(TOADS)であり、これについては“Asymmetrical Optical Loop Mirror:analysis of an all-optical switch”Applied Optics,Volume 23,No.29 1994という論文に記述されている。

【0042】

全光式ゲートは2つのゲート入力7,39と、2つのゲート出力8,9とゲートスイッチング入力10とを有している。各ゲート入力7,39は内部でそれぞれのゲート出力8,9に接続されていて、スイッチの状態に依存する接続がとられている。こうして、ゲートがスイッチされていない状態にあるときには、ゲート入力7はゲート出力9に接続され、またゲート入力39はゲート出力8に接続されている。しかし、ゲートがスイッチされた状態にあるときは、ゲート入力7はゲート出力8に接続され、またゲート入力39はゲート出力9に接続される。

【0043】

動作にあたっては、スイッチの状態はゲートスイッチング入力10へ光パルスを印加することにより制御される。これは多数のビットスロットで成る光パルス流を用いて達成され、このパルス流は多数の光パルスを含んでいる。こういった光パルスはゲートにより受領され、このゲートは所定の時間期間にわたって受領した全光エネルギーを統合するように動作する。爾後は、この時間期間は単一のビットスロットに対応すると仮定するが、ある場合にはこれよりも長いか短かいかの期間が好ましいこともある。

【0044】

こうして、例えばもし単一光パルスが全エネルギーEを有しているとし、1つの単一光パルスを含んでいる1つのビットスロットがゲートスイッチング入力10に印加されたとすると、全エネルギーEが検出されることになる。しかし、もし2つの光パルスが1つの単一ビットスロット内部に存在していたとすると、スイッチング入力は2つの光パルスに相等しい全エネルギー2Eを検出することになる。

【0045】

このゲートは概ね正弦状の応答を所定時間期間内で受領したエネルギーの全量に対してもっていて、もし受領した全エネルギーが1つの光パルス内に含まれているエネルギーの奇数倍であるときにはスイッチはスイッチされた状態に入ってゲート入力7,39の1つで受領したいずれものデータをそれぞれのゲート出力へ転送する。このゲートは次のビットスロットの開始でスイッチされていない状態に戻ることになる。もし偶数倍が受領されるとすると、スイッチはスイッチされていない状態に留まる。

【0046】

しかしながらいずれか1つの時間期間中に検出できる光パルスの数には制限がある。したがって、受領したパルスの数を誤って計数するのを避けるために、2を越えるパルスが単一のビットスロット期間中にスイッチにより受領されることがないようにすることを確かとするのが好ましい。その結果、スイッチは単一光パルスがビットスロット間で受領されるのを条件としてのみスイッチされた状態に入ることになる。単一光パルスを含んでいるこのようなビットスロットでゲートスイッチング入力10に加えるためのものを爾後スイッチング信号を呼ぶこととする。

【0047】

こうして、あるビットスロット中に、ゲートスイッチング入力10に加えられる光パルスが何もないか、あるいは2つの場合には、光パルス流でゲート入力7に印加されたものは全光式ゲートを通って第2のゲート出力9に送られることになる。しかし、ゲートスイッチング入力10への単一光パルスの印加はスイッチング信号として作用することになり、ゲート入力7に印加された光パルス流の単一ビットスロットが第2のゲート出力9から第1のゲート出力8へ分れ道をとることとする。入力光流内のいずれか別のビットスロットは別のスイッチング信号が受領されるまでは第2のゲート出力9から出力され続くことになる。

【0048】

論理的用語で言うと、ゲート6は1つの光パルスを含むビットスロットの受領は1つの論理状態の論理信号を受領するのと等価であり、また光パルスを何も含まないか2つ含むビットスロットの受領は相補的な論理状態を受領するとの等価であるように動作する。

【0049】

当事者は、ゲート出力8,9が第2のゲート6のスイッチング入力10と接続できて、波長変換を、もし必要であれば、与えられることを理解できよう。この場合に、第2のゲート6は第1のゲートのそれぞれの出力8,9から受領した光パルスをスイッチング入力として使用して、第2のゲート6からの出力が実効的に第1のゲート6の出力の再生されたコピィであるようにする。このような設定は未決特許出願WO98/44512に開示されている。

【0050】

図1dは光パルス源(ソース)11を示し、これは普通約1.5μmの波長でパルスを作る半導体レーザの形式をとっている。パルス繰返しレートは約1GHzであり、非分散性光ファイバのある長さでの線形チャープ補償後に10p秒パルスを与えるレーザを伴うものであるが、100GHzを越えるパルス繰返しレートも可能である。このようなパルス源11は一般に2つの光パルスシーケンスの1つを作るように構成されている。第1の構成は爾後パルス流発生器と呼ぶこととし、これが各ビットスロット内で1つの光パルスをもつ光パルス列を発生する。第2の構成は爾後同期パルス発生器と呼ばれるが、これが1ビットスロットだけに1つの光パルスをもつ光パルス流を発生する。

【0051】

この発明による二値加算器の例は図2と4とに示されていて、図2は二値加算器の部品の構成を模式的に示し、また図4は図2の論理ゲートの構成を模式的に示している。図示のように加算器は入力12を備えて、これが2以上の光二値ワードをシーケンスで含んでいる光パルス流を加算器回路に供給し、各二値ワードはLビットスロットの長さのものである。

【0052】

入力12は光コンバイナ13の第1のコンバイナ入力14に接続されていて、光コンバイナ13はコンバイナ出力16として光ゲート17のゲートスイッチング入力18に接続されたものを有している。ゲート17はANDゲートとして動作して、その第1のゲート出力にはゲートスイッチング入力18とゲート入力19とで受領した光パルス流の論理ANDを生成する。この情況では、ゲート入力は第1のANDゲート入力18と第2のANDゲート入力19として考えることができ、また第1のゲート出力20がANDゲート出力20である。第2のゲート出力21はこの構成では使用されない。

【0053】

ANDゲート出力20は出力遅延線22を経てコンバイナ13の第2のコンバイナ入力15に接続されている。光パルスで遅延線22に沿って移動するものは(L+1)ビットスロットだけ遅延されることになる。

【0054】

コンバイナ出力はまた光XORゲート35の第1のXORゲート入力36に接続されている。XORゲート35は光コンバイナ23と、光非線形ゲート27とパルス流発生器33で光パルス流(ストリーム)を発生するものとを含んでいる。

【0055】

コンバイナ23の第1のコンバイナ入力24は第1のXORゲート入力36を経てコンバイナ出力16に接続されている。コンバイナ出力26はゲート27のゲートスイッチング入力28に接続されていて、ゲート27のゲート入力29はパルス流発生器33に接続されて光パルス流を受領するようにしている。

【0056】

第2のゲート出力31は未接続であるが、第1のゲート出力30はXORゲート出力38を経由して遅延線32に接続されていて、この遅延線はその長さに沿って進行する光パルスに対してLビットスロットに等しい時間間隔の遅延をもたらしている。

【0057】

Lビットスロット遅延と(L+1)ビットスロット遅延とを使用することは、XORゲートとANDゲートとからの光ワード出力を互に1ビットスロットだけオフセットすることができるようにする。このようにして1ビットスロットのオフセットを得ることは単一の1ビットスロット遅延のような別の回路構成を用いるのと違って好ましいことであり、それは1ビットスロット遅延が高ビットレートでは達成し難いことによる。

【0058】

遅延線32は、第2のXORゲート入力37を経由して、コンバイナ入力25に接続されていて、また光ANDゲート17の第2のANDゲート入力19にも接続されている。

【0059】

上述のように、光ゲート27と、パルス流発生器33と、光コンバイナ23とは組合されて排他的論理和XORゲートを形成することは図4に示す通りであり、これは次のように動作する。

【0060】

光コンバイナ23はコンバイナ入力24,25で受領したいずれもの光パルスを組合せて、もし単一の光パルスだけがいずれかの1ビットスロット中に入力24,25のどちらかで受領されるとすると、そのときはコンバイナからの出力は単一の光パルスとなる。この光パルスは次にスイッチング信号として作用してゲート27がスイッチされた状態となるようにし、その結果単一の光パルスがゲート入力29から第1のゲート出力30へ転送されることになる。

【0061】

しかしもし単一光パルスがコンバイナ入力24,25の両方で受領されるとすると、そのときは光コンバイナ23は同じビットスロット内で2つの光パルスを出力することになる。上述のように、ゲートスイッチング入力22は2つの光パルスに等しい全エネルギーを検出して、これはスイッチング信号として作用しない。したがって、ゲートはスイッチされていない状態に留まって、パルス流発生器33からの光パルス流は第2のゲート出力31には転送されない。ゲートはまたそれぞれのビットスロット中に、光コンバイナ23によって何も光パルスが受領されないことを条件としてスイッチされない状態に留まる。

【0062】

こうして、XORゲート35は、XORゲート出力38に、XORゲート入力36,37で受領した光パルスのXORを生成する。光パルスがあるビットスロット中に単一光パルスだけを受領したときにXORゲート出力30から出力される。もし何も光パルスを受領しないか2つの光パルスが受領されれば、そのときは光パルスは出力されない。

【0063】

実際に、XORゲート出力38から第2のXORゲート入力37へ出力を帰還するために遅延線32を加えると、XORゲートが形成されて、それがXORゲート入力36に連続して供給された2つのLビットスロットワードのXORを生成することになる。

【0064】

二値加算器の動作をここで記述して行く。

【0065】

第1の例として記述するものは表1と図3とを参照するものであり、L=10とするとして、Lビットスロット長をそれぞれがもつ2つの二値ワードの単純な二値加算である。

【0066】

【表1】

【0067】

この場合、加算されることになる二値数は“0001101011”と“1101000111”であり、その結果は“1110110010”となる。

【0068】

第1の二値ワードは入力12から光コンバイナ13の第1の入力に向けてビットスロット1〜10の間に転送される。最初はこの回路内には他の光パルスに何も存在しない。その結果、第1のワードはコンバイナ13を経由してANDゲート17に向けて転送されて、ゲート17では、ANDゲート出力20に何も光パルスを含まない出力を生成することは図3と表1に示した通りである。

【0069】

第1のワードはまたXORゲート35に転送され、そこではXORゲート出力38でこのワードのコピィを生成する。これが遅延線32に転送されて、そこではLビットスロット(すなわち10ビットスロット)に相等しい時間遅延を導入して、このワードが第2のANDゲート入力19と第2のXORゲート入力37にビットスロット11〜20の間に転送される。

【0070】

同時に、ビットスロット11〜20の間には第2の二値ワードが第1のコンバイナ入力14に転送される。再び第2のコンバイナ入力15では光パルスは存在しないので、第2の二値ワードは単に第1のANDゲート入力18と第1のXORゲート入力36に転送されることは表1と図3に示す通りである。

【0071】

XORゲート35は出力38で第1と第2のワードの論理XOR組合せを表わす光XORワードを生成する。これが遅延線32に転送されて、Lビットスロットの時間間隔(すなわち10ビットスロット)だけ遅延された後に、光XORワードが第2のANDゲート入力19と第2のXORゲート入力37に、ビットスロット21〜30の間に転送される。

【0072】

ANDゲート17はANDゲート出力20で第1と第2のワードの論理AND組合せを表わす光ANDワードを生成する。これが遅延線22に転送されて、(L+1)ビットスロット(すなわち11ビットスロット)だけ遅延された後に、光ANDワードが第2のコンバイナ入力にビットスロット22〜31の間に転送される。入力12から転送される別の二値ワードがない状態で、光ANDワードは第1のANDゲート入力20と第1のXORゲート入力36とにビットスロット22〜31の間に転送される。

【0073】

こうして、ビットスロット21〜30の間に、XORゲート35とANDゲート17とはビットスロット11〜20の間に生成された光XORワードを受領し、また追加のビットスロットだけ遅延された光ANDワードのおかげで、ビットスロット10〜19中に生成される。こういった光ワードから、別なANDとXORの光ワードが生成されて、ANDとXORのゲート出力38,20からそれぞれ出力される。

【0074】

こういった別の光ワードは再びそれぞれの遅延線32,22によって遅延されて、第1と第2のAND及びXORゲート入力18,19,36,37に戻される。

【0075】

このプロセスはANDゲート35からの出力が完全なLビットスロット期間存在しなくなるまで、すなわちビットスロット41〜50の間繰返されることは図3と表1に示す通りである。この時点で光XORワード出力でXORゲート出力38からのものが第1と第2のワードの二値和を表わしている。

【0076】

この発明の二値加算器の第2の例は表2に示す。ここでもまた加算される二値数は“0001101011”と“1101000111”である。しかし、この例では、最上位ビット(MSB)は光二値ワードの第1のビットスロットにより表わされている。したがって、図1の遅延線22は(L−1)ビットスロット遅延線で置換えられることになる。ここでもまたビットスロット41〜50に含まれる出力は二値和“1110110010”である。

【0077】

【表2】

【0078】

表2はそれ故に表1と同様に解決されるが、ANDゲート出力20から出力された光ANDワードは(L−1)ビットスロット(すなわち9ビットスロット)に対応する時間期間だけ遅延されていて、(L+1)ビットスロットとは違っており、それから第2のコンバイナ入力へ転送される。

【0079】

図3に示したように、二値和を表わしている光ワードは回路がリセットされるまではXORゲート出力から繰返して出力される。これは第2のXORゲート入力37へ帰還されるXORゲート出力38からの出力を形成する光パルスの結果として生じている。回路内の別なところには何も追加の光パルスが存在しないことを条件として、第2のXORゲート入力37へ帰還されるどんなパルスもXORゲート35によって再生されて再び出力される。したがって、この回路のリセットはXORゲート35をリセットすることで達成される。

【0080】

XORゲートをリセットするためには、ゲートスイッチング入力28でスイッチング信号の受領時に、光パルスが何もゲート入力29から第1のゲート出力30へ転送されないことを確保する必要がある。この条件は少くともLビットスロット間は維持されなければならずこれはLビットスロット光ワードの各ビットスロットをリセットするためである。

【0081】

これは、パルス流発生器33から受領した光パルス流を、R光ビットスロットの光ビットスロットウィンドウを含んでいる光ビットスロット流によって置換することにより達成できるものであり、各Rビットスロットは光パルスを何も含んでいないものとする。したがって、ゲート27のゲートスイッチングユニットによるスイッチング信号の受領時に、Rビットスロットウィンドウ内に含まれるそれぞれ空のビットスロットは第1のゲート出力30からXORゲート出力38へ転送される。このワードのビットスロットの全部がリセットされることを確かとするためにRはLに等しいかそれより大きくなければならない。

【0082】

このようなRビットスロットウィンドウで何も光パルスを含まないものは我々は未決出願GB9719895.6に記述されており、また図5と6とを参照してここで記述して行く。

【0083】

図5はリセット可能な二値加算器を示し、ここには図2の二値加算器がウィンドウ発生器に接続されて含まれており、ウィンドウ発生器はパルス対発生器52とスイッチングデバイス53とを含んでいる。

【0084】

スイッチングデバイス53は入力ポート54を備え、そこにはパルス流発生器55が接続されていて、そのほかに2つの出力ポート56,38とスイッチング入力ポート57であってパルス対発生器52の発生器出力76に接続されたものとを備えている。

【0085】

スイッチングデバイスその自体は全光式非線形ゲート58で構成されていて、その第1のゲート出力59は、帰還ループを介して、光コンバイナ63の第2のコンバイナ入力65に接続されている。帰還ループは遅延線67から形成されていて、これはウィンドウ発生器の目的上、単一ビットスロットと等しい時間遅延を導入している。したがって、遅延線67を通って転送される光パルスは光コンバイナ63の第2のコンバイナ入力65に到着するのは、無遅延接続を通って移動したとしたときに到着したビットスロットのすぐ後に来るビットスロットということになる。

【0086】

ゲート入力61はスイッチングデバイス入力ポート54に接続されていてパルス流発生器55により生成された光パルス流を受けるようにされていて、またゲートスイッチング入力62は光コンバイナ63のコンバイナ出力66に接続されている。第1のコンバイナ入力64はスイッチングデバイスのスイッチング入力ポート57に接続されていて、パルス対発生器52からの光パルスを受領する。

【0087】

パルス対発生器52は全光コンバイナ70で構成されている。光コンバイナ70の第1のコンバイナ入力71に接続されているのが同期パルス発生器74であり、また第2の入力72に接続されているのが遅延線75である。遅延線75は同期パルス発生器74にも接続されていて、ビットスロットの数Rに等しい時間遅延を加えるように動作する。コンバイナ70のコンバイナ出力73はパルス対発生器52の出力ポート76を経由してスイッチングデバイス53のスイッチング入力ポート57に接続されている。

【0088】

図5のウィンドウ発生器の動作をここで図6を参照して記述することとし、図6はウィンドウ発生器回路の周りのいくつかの位置についてビットスロット時間ラインを示している。各時間ラインは一連のビットスロットに分割されていて、回路内のそれぞれの点での光パルスの存在を示している。パルス流はパルスの連続する存在により表わされるが、一連の離散的なパルスとしても同様に示すことができる。

【0089】

上述のように、スイッチングデバイス53はパルス流発生器55に接続されていて、これが光パルス流をスイッチングデバイスの入力ポート54に供給しており、したがってゲート58のゲート入力61に供給している。

【0090】

最初は、スイッチングデバイスのスイッチング入力ポート57に何も光パルスが加えられていない状態では、ゲート58のゲートスイッチング入力62に向けた光パルス入力は存在しないことになる。したがって、ゲート入力61に供給された光パルス流は全光式ゲート58を通ってゲート出力60に送られる。その結果、ゲート出力59からは光パルスが何も出力されず、またパルス流は第2のゲート出力60から出力される。

【0091】

図6でラベルを付したビットスロット5では、単一の光パルスが同期パルス発生器74から出力されて光コンバイナ70に転送されている。図6に示したように単一の光パルスが点77に到着して2つのコピィに分けられて、1つは直接に全光式コンバイナ70の第1のコンバイナ入力71に転送され、また他のものは遅延線75を経由して第2のコンバイナ入力72に転送される。遅延線75に沿って移動するパルスは、光コンバイナ70に直接移動するパルスに関してRビットスロット(この例ではR=10)だけ遅延していることになる。その結果、光コンバイナ70はビットスロット5ではコンバイナ入力71で1つの光パルスを受領することになり、また第2の光パルスをビットスロット15でコンバイナ入力72において受領することになることは図6に示す通りである。

【0092】

こういった光パルスはそこで組合されて単一の光パルス流となり、Rビットスロットだけ離れた2つの光パルスを含むものとなり、それがスイッチングデバイス53のスイッチング入力ポート57に転送される。

【0093】

第1のパルスがパルス対発生器52から受領されるときには、それがスイッチングデバイスのスイッチング入力ポート57へしたがって図示のように光コンバイナ63の第1のコンバイナ入力64に入力される。この光パルスは次にゲート58のゲートスイッチング入力62に転送されてスイッチング信号として作用する。これは第1の光パルスをゲート入力61からゲート出力59へビットスロット5の間切換えさせるようにしている。

【0094】

この光パルスは遅延線67を経由して光コンバイナ63の第2のコンバイナ入力65に帰還される。遅延線67は帰還ループ内に単一ビット遅延を導入するから、帰還光パルスはゲートスイッチング入力62にビットスロット6で到着する。これはパルス流発生器55からの後続の光パルス出力がゲート入力61に受領されるときである。したがって、ゲート出力59からの第1の光パルス出力はスイッチング信号として、ビットスロット6で作用することになり、次の光パルスがゲート入力61からゲート出力59へと切換えられるようにする。これがビットスロット6ないし14の間繰返されて、50の光パルス流がゲート出力59から出力されることになる。

【0095】

これは第2のパルスが、ビットスロット15で、パルス対発生器52から出力されるまで続く。このパルスはビットスロット55で光コンバイナ63の第1のコンバイナ入力64に到着することになり、これは帰還ループから光パルスが第2のコンバイナ入力65で受領されるのと同じ時間である。

【0096】

両パルスが光コンバイナ63に同時に到着すると、2つの光パルスは同じビットスロット内で出力されることになる。したがって、ゲートスイッチング入力62は2つの光パルスと等しい全エネルギーを検出することになる。これはスイッチング信号として作用せず、結果としてはパルス流発生器55からの光パルス流はもはやゲート出力59には切換えられない。

【0097】

その結果、組合せにかけられると、光コンバイナ63とゲート58とはXORシステムとして機能し、ゲート58は光コンバイナ入力64,65の1つで1つ光パルスが受領されるときに切換えられた(スイッチされた)状態に入るだけとなる。パルスが何も受領されないか、パルスか両入力で、同じビット期間に同時に、受領されるときには、コンバイナからの信号出力はスイッチング信号としては作用せずに、ゲートはスイッチされていない状態に留まるようになる。

【0098】

こうして、パルス対発生器52から2つのパルスをもつ光信号流を用意することによって、パルスは所定数のビットスロットRだけ隔てられて、ウィンドウ発生器はゲート出力59からKの光パルスで成る光信号流を出力することになる。

【0099】

さらに、パルス対発生器52内に遅延を導入するのは遅延線75であるから、ビットRの数を設定するのは遅延線75の時間遅延の長さである。こうして図6の例では遅延線75は10ビットスロットと等しい遅延をもたらして、ウィンドウ発生器が出力ポート56から50の光パルスシーケンスを出力するようにする。しかし、遅延線75が光パルスをそこで遅延させるビットスロットの数は変えることができて、スイッチングデバイス53の出力ポート56からの光パルス出力の数に対応した変化を生じさせる。

【0100】

第2のゲート出力60は第1のゲート出力59により生成された光信号流の論理的補数である光信号流を生成する。第2の出力ポート78はしたがってゲート出力60に接続されて、Rビットスロットウィンドウを含んでいる光信号流を作るようにされ、ここでRビットスロットはその中に光パルスをもたないものであり、光パルスを含んでいるのはRビットウィンドウの内部のスロットではないことになる。

【0101】

二値加算器のリセットを生じさせるためには、ウィンドウ発生器の出力ポートがXORゲート35′のゲート27のゲート入力に接続されており、このXORゲート35′は図2のXORゲート35と似ていて、パルス流発生器33だけが欠けている。

【0102】

ウィンドウ発生器はそこで光パルスを含む光ビットスロット流を発生するよう動作して、加算器が正常に使用されるようにする。そこで、加算器のリセットが求められると、ウィンドウ発生器は光ビットスロットを何も含んでいないR光ビットスロットを発生して、XORゲート35′からの出力のR光ビットスロットをリセットするようにする。したがって、R>Lについて、加算器は完全にリセットされて、回路はもはや光パルスを何も含まなくなる。

【0103】

図2の二値加算器の動作の第3の例を表3と図7とを参照して今度は記述して行く。これは簡単なカウンタ(計数用)回路としての回路の動作である。

【0104】

カウンタとして動作するためには、回路には二値ワードのシーケンスが供給されなければならず、各ワードは長さがLビットスロットのものであり、単一光パルスだけを含んでいて、この場合はこれが第1のビットスロット内にある。加算器回路は効果的に二値の値をXORゲート出力38に出力することになり、それが受領したこのフォーマットのワードの数を表わしている。

【0105】

この例では図7と表3に示すように、入力12が4つの6ビットスロット長ワード(すなわちL=6)のシーケンスを供給し、各ワードは第1のビットスロット内に単一の光パルスを有していて、それを第1のコンバイナ入力14に供給する。

【0106】

【表3】

【0107】

第1の二値ワードが入力12から光コンバイナ14の第1の入力14にビットスロット1〜6の間に転送されるときは、この回路中には他の光パルスは存在しない。その結果、第1のワードはコンバイナ13を経由してANDゲート17に転送され、そこでは光パルスを何も含んでいない出力をANDゲート出力20に発生することは図7と表3に示す通りである。

【0108】

第1のワードはまたXORゲート35に転送され、そこではXORゲート出力にそのワードのコピィを発生する。これが遅延線32に転送され、そこではLビットスロット(すなわち6ビットスロット)に等しい時間遅延がもたらされて、そのワードが第2のANDゲート入力19と第2のXORゲート入力37とにビットスロット7〜12の間に転送される。

【0109】

同時に、ビットスロット7〜12の間に、第2の二値ワードが第1のコンバイナ入力14に転送される。ここでもまた、第2のコンバイナ入力15に何も光パルスが存在していない状態で、第2の二値ワードが第1のANDゲート入力18と第1のXORゲート入力36とに単に転送されることは表3と図7に示す通りである。

【0110】

XORゲート35は光XORワードで第1と第2のワードの論理的XOR組合せを表わすものを出力38に発生し、ここには光パルスは何も含まれていない。

【0111】

同時に、ANDゲート17は光ANDワードをANDゲート出力20に発生し、それが第1と第2のワードの論理的AND組合せを表わしている。これが遅延線22に転送され、(L+1)ビットスロット(すなわち7ビットスロット)の時間間隔だけ遅れた後に、光ANDワードが第2のコンバイナ入力に向けて、ビットスロット14〜19の間に、転送される。

【0112】

第3の二値ワードがコンバイナ13の第1の入力にビットスロット13〜18の間に受領されて、ビットスロット6〜11の間に発生された光ANDワードと組合されて、組合せ光ワードを発生する。この組合せ光ワードは表3に示されるようにビットスロット13〜18の間にANDゲート17とXORゲート35の第1のゲート入力18,36に転送される。

【0113】

第2のゲート入力19,37はこの時間に供給される光パルスを何ももたないが、それは光XORワードが何も光パルスをもたずにビットスロット7〜12で発生されることによる。

【0114】

したがって、XORゲート35は光XORワードを発生するが、これは第2のXORゲート入力37に何も光パルスが存在しないので、組合せ光ワードのコピィである。この光XORワードは遅延線32に転送され、Lビットスロット(すなわち6ビットスロット)だけ遅延した後に第2のANDゲート入力19と第2のXORゲート入力37とにビットスロット19〜24の間に転送される。

【0115】

ANDゲートは光ANDワードで光パルスを含んでいないものを発生する。したがって、第2のコンバイナ入力15にはビットスロット19〜24の間には光パルスは存在せず、この時間は第4の二値ワードが第1のコンバイナ入力14で受領され、また第4の二値ワードが第1のゲート出力18,36に転送される。

【0116】

ビットスロット19〜24の間では、したがって、XORゲート35とANDゲート17とはビットスロット13〜18の間に発生された光XORワードと第4の二値ワードとを受領する。これらから、別なANDとXOR光ワードが発生されて、それぞれANDとXORゲート出力38,20からそれぞれ出力される。

【0117】

これらの別のワードはこれもまたそれぞれの遅延線32,22で遅延されて、第1と第2のANDとXORゲート入力18,19,36,37に戻される。

【0118】

入力12から転送される別な二値ワードがなければ、光ANDワードが第1のANDゲート入力20と第1のXORゲート入力36とにビットスロット26〜31の間に転送される。他方では、光XORワードは第2のゲート入力19,37にビットスロット25〜30の間に転送される。

【0119】

このプロセスは繰返されて、ANDゲート17の出力20に全Lビットスロット期間中何も光パルスがなくなるまで、すなわち、光ANDワードが図7と表3で示すようにビット期間31〜36の間何も光パルスを含まなくなるまで行なわれる。この時点で、光XORワード出力でXORゲート出力38からのものは光二値ワードで二値の値“100”をもつものとなり、これが十進法の“4”を表わす。こうして、この回路は到来する二値ワードの数を計数し、二値ワードが所要のフォーマットを有する限り計数がされる。

【0120】

ここで注意しておきたいことは、現在の例では、計数できる最大の二値の値が“111111”(すなわち十進の“63”)である点である。この制限は二値ワードが6ビットスロットしかもっていないために生じているものである。したがって、ビットスロットの数を増すことによって、計数できる最大値は増大する。数学的に表現すると、この回路が計数できる最大十進値は(2L −1)であり、ここでLは光二値ワード内の光ビットスロットの数である。

【0121】

図2の二値加算器の動作の第4の例が表4に示されている。この場合には、この回路は再び単純なカウンタとして動作し、入力光二値ワードの最後のビットスロット内の単一の光パルスで動作する。したがって、図2の遅延線22は(L−1)ビットスロット遅延によって置換えられる。

【0122】

【表4】

【0123】

表4は表3と同じように解釈されるべきものであるが、違いはANDゲート出力20からのANDワード出力が(L−1)ビットスロット(すなわち5ビットスロット)だけ第2のコンバイナ入力に転送される前に遅延されていることである。したがって、表4による動作は詳述しないこととする。

【0124】

ここでもまた回路のリセットは光ビットスロットウィンドウの使用により達成できて、各光ビットスロットは光パルスを含んでおらず、図5と6とを参照して記述したところと同様である。

【0125】

この発明の第2の実施例は図8に模式的に示してあり、ここではこの代替設計のために使用された論理ゲートの構成を模式的に示している。図8の部品で図4のものと同一のものは100を加えたのと等しい参照番号で示してある。

【0126】

図8に示すように、この加算器はANDゲート117とXORゲート135とを含んでいる。ANDゲート出力120は遅延線122(L+1ビットスロット遅延を導入する)を経由して第1のANDゲート入力118と第1のXORゲート入力136とに接続されている。XORゲート出力138は遅延線132(Lビットスロット遅延を導入する)を経由して第2のANDゲート入力119と第2のXORゲート入力137とに接続されている。入力112は加えるべきワードを供給するものであり、第1のANDゲート入力118と第1のXORゲート入力136とに接続されている。

【0127】

図4と図8とを比較すると、図8は図4の装置と似ているが、光コンバイナ13は取除かれている。図3での光パルスの調査は光コンバイナ13はこの動作の際にいずれかの光パルスを組合せることは実際には必要ないことを示しており、それは主として第2の二値ワードが供給された後にはコンバイナ入力14によって受領される光パルスが存在しないことが原因となっている。したがって、この加算器にとってコンバイナ13なしに機能することは2つだけの二値ワードがコンバイナ入力14に供給されている限り可能ということになる。

【0128】

それ故に、図8は、表1と図3とに関して記述した例でのように2つの二値数を加えるための加算器として使用できる適切な装置構成の例を示している。

【0129】

評価できると思うが、もし遅延線122が(L−1)ビットスロット遅延線により置換えられると、図8の装置は表2で設定した例と同じやり方で二値加算器として使用できる。

【0130】

図9はこの発明の第3の実施例による二値加算器で使用される論理ゲートの構成の模式図を示す。

【0131】

この発明のこの実施例では、光XORワードと光ANDワードを繰返し発生するために帰還使用することが光ANDゲートとXORゲート対201,202,203,204のシーケンスによって置換されている。

【0132】

各対201,202,203,204は同一であるので、したがって、その1つだけが図9を参照して記述される。AND/XOR対201はANDゲート217とXORゲート235とを含む。ANDゲート217とXORゲート235の第1のゲート入力218,236は一緒に第1のワード入力ポート210に接続され、これが加算される第1のワードを受領する。第2のゲート入力219,237でANDゲート217とXORゲート235のものはまた一緒に第2のワード入力ポート210に接続され、そこで加算される第2のワードを受領する。

【0133】

ANDゲート出力220は遅延線222(これは(M+1)ビットスロット遅延を導入している)を経由して出力ポート212に接続されていて、またXORゲート出力238は遅延線232(これはMビットスロット遅延を導入している)を経由して出力ポート213に接続されている。

【0134】

各AND/XOR対は第1と第2の入力ポート210,211で同時に受領した第1と第2の二値ワードについて演算をして論理的ANDを表わしている光ワードをANDゲート出力220で発生し、また論理的XORを表わしている光ワードをXORゲート出力238で発生するようにしている。光ANDワードと光XORワードとのそれぞれ第1と第2の出力ポート212,213に向けたものは、(M+1)とMのビットスロットだけそれぞれ遅延されて、光ANDワードは光XORワードに対して1ビットスロット余計に遅延されている。これらのワードはそれぞれ次のAND/XORゲート対202の第と第2のポート210,211に向けて出力される。

【0135】

したがってこの装置は、図8の装置のように機能し、そこでは帰還プロセスが後続のAND/XORゲート対への転送に置換っている。十分な数のAND/XORゲート対がシーケンスとして用意されることを確保することによって、ANDゲート出力は最終的には光パルスを何も含まなくなり、この場合には光XORワードでそれぞれのXORゲートで発生されたものが第1と第2のワードの二値和となっている。必要とされるAND/XORゲートの数はしかしながら予め定めることができず、したがってこの設計は正しい答が発生されるように十分なAND/XORゲート対を必要とする。しかしながら、各AND/XORゲート対からの光ANDワード出力を監視することによって、どのAND/XORゲート対が第1と第2のワードの二値和を表わしている光XORワードを生成するかを判断することは可能である。

【0136】

帰還ループなしでは、この装置のリセット動作は自動的であり、結果が一旦生成されると回路内には何も光パルスは残らない。さらに、遅延線にとっての要件は遅延線が出力ワードを遅延させるのは、光ANDワードがXORワードに対して1ビットスロットだけオフセットしているというものでなければならないとするだけのことであるから、遅延時間の全体長は減縮してもよい。

【0137】

したがって例えば、もし図2の回路が使用されるとして、大きな数のビットスロットLに対しては、ワードの転送は帰還当りLビットスロットだけ遅れている。しかし図9の設計では、転送はMビットスロットだけ遅れているだけであり、ここでM<<Lと制御できるのであるから、それにより処理時間を低減することになる。

【0138】

しかしながら、高ビットレートで単一ビット遅延を達成するのはむづかしいのであるからM>1という値を維持することが好ましい。したがって、(M+1)ビットスロット遅延とMビットスロット遅延を用いることによって、1ビットスロットの相対的なオフセットが便利にも得ることができる。

【0139】

ここでもまた、(M−1)ビットスロット遅延を(M+1)ビットスロット遅延に代って使用でき、その条件は二値ワードの正しいフォーマットが使用されることとしている。

【0140】

この発明の第3の実施例で記述した光AND/XORゲート対のシーケンスを、この発明の第1の実施例の帰還システムに接続することが代替の可能性となっている。これは前の計算が第1の実施例による帰還システムによって完了されつつある間に、このシステムがAND/XORゲート対のシーケンス内で2つの二値ワードを加算し始めることを可能とする。さらにまた、AND/XORゲート対の数が減らすことができて、それでいてなお第1と第2光ワードの二値和が決定できるようにしている。

【図面の簡単な説明】

【図1】 遅延線の模式図(図1(a))、光コンバイナの模式図(図1(b))、全光式非線形ゲートの模式図(図1(c))、光パルス源の模式図(図1(d))。

【図2】 この発明による二値加算器の模式図。

【図3】 図2の二値加算器の周辺のいくつかの点における光パルスの存在を示すビットスロット時間ラインを示す図。

【図4】 図2の二値加算器で使用される論理ゲートの構成の模式図。

【図5】 ウィンドウ発生器に接続された図2の二値加算器を含むリセット可能な加算器を示す模式図。

【図6】 図5のウィンドウ発生器の周辺のいくつかの点における光パルスの存在を示すビットスロット時間ラインを示す図。

【図7】 別の入力パルス流についての、図2の二値加算器の周辺のいくつかの点に向けた光パルスの存在を示すビットスロット時間ラインを示す図。

【図8】 この発明の第2の実施例による二値加算器で使用される論理ゲートの構成の模式図。

【図9】 この発明の第3の実施例による加算器で使用される論理ゲートの構成の模式図。

Claims (10)

- 第1の光二値ワードと第2の光二値ワードとの和を決めるための加算器であって、

各光二値ワードは複数のビットスロットを有し、各ビットスロットは第1及び第2の論理状態の1つを示し、

この加算器は、

第1入力(18)及び第2入力(19)を有する、少なくとも一つの第1のタイプの光論理エレメント(17)と、

第1入力(36)及び第2入力(37)を有する、少なくとも一つの第2のタイプの光論理エレメント(35)と、

前記第1及び第2のタイプの光論理エレメントのそれぞれの第1入力に結合された加算入力(14)と、

を備え、

前記第1及び第2の光二値ワードは加算入力(14)へ連続して供給され、

各光論理エレメントは、

前記加算入力から受けた前記第1及び第2の光二値ワードの論理的な組合せである出力ワードを発生する出力(20,38)を備え、

第1のタイプの光論理エレメント(17)は、前記第1と第2の入力で受けた二値ワードのAND組合せの結果を出力(20)にもたらす機能を実行するよう構成され、

第2のタイプの光論理エレメント(35)は、前記第1と第2の入力で受けた二値ワードのXOR組合せの結果を出力(38)にもたらす機能を実行するよう構成され、

第1のタイプの光論理エレメントの出力(20)からの出力ワードが第1タイプの光論理エレメントの第1入力(18)及び第2のタイプの光論理エレメントの第1入力(36)に送られ、第2のタイプの光論理エレメントの出力(38)からの出力ワードが第1のタイプの光論理エレメントの第2入力(19)及び第2のタイプの光論理エレメントの第2入力(37)に送られるように、第1のタイプの光論理エレメントおよび第2のタイプの光論理エレメントはそれぞれ連結手段により互いに連結され、

遅延手段(22,32)は、異なる光論理エレメント(17,35)からの出力ワードが一ビットスロットだけ相互に遅延されるように、前記第1のタイプの光論理エレメントと前記第2のタイプの光論理エレメントの出力(20,38)に配設され、

前記二値ワードの和は、前記XOR組合せの前記出力ワードとして前記第2のタイプの光論理エレメントの出力(38)から出力される、

ことを特徴とする加算器。 - 前記連結手段は、使用時に、前記第1及び第2のタイプの光論理エレメント(17,35)の出力ワードが、前記第1及び第2のタイプの光論理エレメント(17,35)の双方でそれぞれ受領されるように配置される、請求項1の加算器。

- 各二値ワードは、Lビットスロットを有し、前記遅延手段(22,32)は、第1の遅延線(22)と第2の遅延線(32)を有し、前記第1及び第2の遅延線(22,32)は第1及び第2のタイプの光論理エレメントからの出力ワードをL+1及びLビットスロットだけそれぞれ遅延させるように配置される、請求項2の加算器。

- 各光論理エレメント(17,35)は出力(20,38)を有し、前記第1のタイプの光論理エレメントの前記出力(20)は第1の遅延線を介して前記第1及び第2の光論理エレメント(17,35)の前記第1の入力に接続され、前記第2のタイプの光論理エレメントの出力は前記第2の遅延線(32)を介して前記第1及び第2のタイプの光論理エレメント(17,35)の前記第2の入力(19,37)に接続される、請求項3の加算器。

- 前記少なくとも一つの第2のタイプの光論理エレメント(35)は、スイッチング入力(28)、ノンスイッチング入力(29)、出力(30)を有する非線形光学ゲート(27)を有し、前記スイッチング入力は前記ゲートのノンスイッチング入力と出力との間の光学的な接続を制御し、前記光学的な接続は1つの光パルスが前記スイッチング入力(28)で受領されたときには形成され、前記光学的な接続は2つのパルスがスイッチング入力(28)にて受領されたときには形成されない、請求項1乃至4のいずれかの加算器。

- 第2の光論理エレメント(35)は、更に光パルスのソース及び光コンバイナ(26)を含み、前記光コンバイナは前記第2の光論理エレメントの第1及び第2の入力(36,37)からの光強度を結合するように配置され、前記光コンバイナは前記非線形ゲートのスイッチング入力(28)に接続される出力を有し、前記光パルスソースは非スイッチング入力に接続され、パルスは、前記第2の光論理エレメントの第1或いは第2の入力(36,37)のいずれかにて受領されたとき、XORゲートのやり方で、非線形ゲートの出力にて生成される、請求項5の加算器。

- リセット手段(52,53)は光パルスのソースを遮断するために提供され、前記加算器は一旦前記第1及び第2の二値ワードが加算されるとリセットされる、請求項6の加算器。

- 複数の第1のタイプの光論理エレメント(217)と第2のタイプの光論理エレメント(235)が提供され、前記第1のタイプの光論理エレメントと前記第2のタイプの光論理エレメントで1つのブロックを構成しており、あるブロックの前記第2のタイプの光論理エレメントからの出力ワードが他のブロックの各エレメントへと通過し、あるブロックの前記第1のタイプの光論理エレメントからの出力ワードは他のブロックの前記第1のタイプの光論理エレメント及び他のブロックの前記第2のタイプの光論理エレメントへと通過する、請求項1の加算器。

- 前記第1のタイプの光論理エレメント(17,217)はANDゲートであり、前記第2のタイプの光論理エレメント(35,235)はXORゲートである、請求項1乃至8のいずれかの加算器。

- 1つ又はそれ以上の第1のタイプの光論理エレメント(17)及び1つ又はそれ以上の第2のタイプの光論理エレメント(35)を用いて、複数のビットスロットを有する二値ワードの対を加算する方法であって、各ビットスロットは第1及び第2の論理状態の一つを表現し、第1のタイプの光論理エレメントは第1及び第2入力(18,19)に加えられるワードにAND機能を実行するように配置され、第2のタイプの各光論理エレメントは第1及び第2入力(36,37)に加えられるワードにXOR機能を実行するように配置され、

各タイプの光論理エレメントはそれぞれ第1入力(18,36)及び第2入力(19,37)を有し、

加算入力(14)が前記第1及び第2のタイプの光論理エレメントのそれぞれの第1入力に結合され、

前記第1及び第2の光二値ワードは加算入力(14)へ連続して供給され、

各光論理エレメントは、前記加算入力から受けた前記第1及び第2の光二値ワードの論理的な組合せである出力ワードを発生する出力(20,38)を備えており、

この方法は、以下のステップを有する、

(i)前記第1のタイプの光論理エレメント(17)の第1入力に一対のワードを入力して、第1の出力ワードを出力(20)に生成するステップと、

(ii)前記第2のタイプの光論理エレメント(35)の第1の入力に一対のワードを入力して、第2の出力ワードを出力(38)に生成するステップと、

(iii)前記第1のタイプの光論理エレメント(17)の前記出力(20)に接続された遅延手段(22)が前記第1のタイプの光論理エレメントからの第1の出力ワードを受信し、前記第2のタイプの光論理エレメント(35)の前記出力(38)に接続された遅延手段(32)が第2のタイプの光論理エレメントからの第2の出力ワードを受信し、第1と第2の出力ワードのうちの他方に対して、1ビットスロットだけ、第1と第2の出力ワードのうちの一方を遅延させて、第1と第2の2つの出力ワードをずらすステップと、

(iv)ずらされた前記第1のタイプの光論理エレメント及び前記第2のタイプの光論理エレメントからの出力ワードを、前記第1のタイプの光論理エレメント(17)に入力するステップと、

(v)ずらされた前記第1のタイプの光論理エレメント及び前記第2のタイプの光論理エレメントからの出力ワードを、前記第2のタイプの光論理エレメント(35)に入力するステップと、

(vi)前記ステップ(iii)から(v)を、前記第1及び第2の二値ワードの合計が前記XOR組合せの前記出力ワードとして前記第2のタイプの光論理エレメントの出力(38)から出力されるまで繰り返す、方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GB9726477.4 | 1997-12-15 | ||

| GBGB9726477.4A GB9726477D0 (en) | 1997-12-15 | 1997-12-15 | Binary adder |

| PCT/GB1998/003655 WO1999031562A2 (en) | 1997-12-15 | 1998-12-08 | Binary adder |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002508557A JP2002508557A (ja) | 2002-03-19 |

| JP2002508557A5 JP2002508557A5 (ja) | 2006-02-16 |

| JP4481490B2 true JP4481490B2 (ja) | 2010-06-16 |

Family

ID=10823636

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000539394A Expired - Fee Related JP4481490B2 (ja) | 1997-12-15 | 1998-12-08 | 二値加算器 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US6711604B1 (ja) |

| EP (1) | EP1038208B1 (ja) |

| JP (1) | JP4481490B2 (ja) |

| AU (1) | AU1494899A (ja) |

| CA (1) | CA2313241C (ja) |

| DE (1) | DE69817614T2 (ja) |

| GB (1) | GB9726477D0 (ja) |

| WO (1) | WO1999031562A2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2533078C1 (ru) * | 2013-07-09 | 2014-11-20 | Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования "Ульяновский государственный технический университет" | Двоичный сумматор |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61138337A (ja) * | 1984-12-10 | 1986-06-25 | Matsushita Electric Ind Co Ltd | 計数回路 |

| GB2201534A (en) * | 1987-02-19 | 1988-09-01 | British Telecomm | Arithmetic assembly |

| JP3182143B2 (ja) * | 1989-06-23 | 2001-07-03 | 浜松ホトニクス株式会社 | 光全加算器 |

| US5136530A (en) * | 1990-07-26 | 1992-08-04 | Yao Li | Ultrafast digital optical signal processing using a Venn diagram based spatial encoding technique |

| US5644123A (en) * | 1994-12-16 | 1997-07-01 | Rocky Mountain Research Center | Photonic signal processing, amplification, and computing using special interference |

-

1997

- 1997-12-15 GB GBGB9726477.4A patent/GB9726477D0/en not_active Ceased

-

1998

- 1998-12-08 EP EP98959009A patent/EP1038208B1/en not_active Expired - Lifetime

- 1998-12-08 US US09/555,768 patent/US6711604B1/en not_active Expired - Lifetime

- 1998-12-08 CA CA002313241A patent/CA2313241C/en not_active Expired - Fee Related

- 1998-12-08 WO PCT/GB1998/003655 patent/WO1999031562A2/en active IP Right Grant

- 1998-12-08 DE DE69817614T patent/DE69817614T2/de not_active Expired - Lifetime

- 1998-12-08 AU AU14948/99A patent/AU1494899A/en not_active Abandoned

- 1998-12-08 JP JP2000539394A patent/JP4481490B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| WO1999031562A3 (en) | 1999-07-29 |

| GB9726477D0 (en) | 1998-02-11 |

| EP1038208A2 (en) | 2000-09-27 |

| CA2313241C (en) | 2005-08-23 |

| EP1038208B1 (en) | 2003-08-27 |

| US6711604B1 (en) | 2004-03-23 |

| DE69817614T2 (de) | 2004-06-17 |

| CA2313241A1 (en) | 1999-06-24 |

| AU1494899A (en) | 1999-07-05 |

| DE69817614D1 (de) | 2003-10-02 |

| WO1999031562A2 (en) | 1999-06-24 |

| JP2002508557A (ja) | 2002-03-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2530069B2 (ja) | 光論理装置 | |

| JP4481490B2 (ja) | 二値加算器 | |

| US7081979B2 (en) | Bit differential processing | |

| JP3034764B2 (ja) | 光通信装置 | |

| JPH08265253A (ja) | 光識別再生回路 | |

| US6369921B1 (en) | Parity determining apparatus and method | |

| US8201015B2 (en) | Control card circuit and method for selecting a synchronization source among a plurality of line card circuits | |

| EP1016308B1 (en) | A method of obtaining an optical signal stream | |

| JP2546967B2 (ja) | データ伝送システム | |

| JP3810798B2 (ja) | 光スイッチ | |

| JPH03103838A (ja) | 光信号可変遅延装置を用いた光クロックの遅延方法 | |

| US7869107B2 (en) | Optical circuit for comparing two N-bit binary words | |

| JP6536959B2 (ja) | 光論理回路および加算器 | |

| US20060011819A1 (en) | Variable light signal delay apparatus, and variable light signal delay system using the same | |

| JPH06261073A (ja) | 光パケットスイッチ | |

| JP2003069495A (ja) | 光パルス列一致判定装置 | |

| JP2001526415A (ja) | 光アド/ドロップマルチプレクサ | |

| JP2855878B2 (ja) | 光セルフルーティング回路 | |

| GB2201534A (en) | Arithmetic assembly | |

| JPS63169845A (ja) | 外部タイミング方式 | |

| JP2017118242A (ja) | 光遅延回路及び光パケットの複製回路 | |

| Blumenthal et al. | A two-by-two photonic switch for computer interconnects | |

| JPH07159740A (ja) | 全光型時分割光パルス分離回路および全光型時分割光パルス多重回路 | |

| JPH04195243A (ja) | トリガ伝達回路 | |

| WO2006082418A1 (en) | Asynchronous optical regenerator |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051125 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20051125 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071205 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071211 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20080311 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20080318 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080603 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20081014 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20090114 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20090121 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090410 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090929 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100129 |

|

| A911 | Transfer of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20100208 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100223 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100318 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130326 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140326 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |