JP4334672B2 - 高速視覚センサ装置 - Google Patents

高速視覚センサ装置 Download PDFInfo

- Publication number

- JP4334672B2 JP4334672B2 JP14180199A JP14180199A JP4334672B2 JP 4334672 B2 JP4334672 B2 JP 4334672B2 JP 14180199 A JP14180199 A JP 14180199A JP 14180199 A JP14180199 A JP 14180199A JP 4334672 B2 JP4334672 B2 JP 4334672B2

- Authority

- JP

- Japan

- Prior art keywords

- light receiving

- converter

- signal

- arithmetic

- image

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Description

【発明の属する技術分野】

本発明は、画像処理機能を備えた高速視覚センサ装置に関する。

【0002】

【従来の技術】

FAシステム等においてロボットを高速で動作させるためには、高速の画像処理が必要とされる。例えば、視覚センサとアクチュエータの間でフィードバックループを形成するロボットの場合、アクチュエータはミリ秒単位で制御可能であるため、本来はこれに対応した画像処理速度が必要になる。ところが、現状のビジョンシステムでは画像処理速度がビデオフレームレートに限られているため、この画像処理速度に合わせた低速動作しかできず、ロボットの性能を十分に活かしきれていなかった。

【0003】

一方、高速CCDカメラの中には1ミリ秒程度で画像を撮像できるものもあるが、これらは撮像した画像をいったんメモリに貯えて、後から読み出して処理を行う機構になっているため、画像解析などの用途には使えるが、実時間性はほとんどなく、ロボット制御などの用途には適用できなかった。

【0004】

このような問題を解決するため、画像の取込部と処理部を一体として取り扱うビジョンチップの研究が進んでおり、マサチューセッツ工科大学、カリフォルニア工科大学、三菱電機などの研究が知られている。しかし、これらは主として集積化の容易なアナログの固定回路を用いており、出力信号の後処理が必要であったり、画像処理の内容が特定用途に限定されていて汎用性がないなどの問題点があった。

【0005】

これらに対して汎用的な画像処理を行うことができるビジョンチップとしては、特公平7−62866号公報に開示された発明(以下、従来技術1と呼ぶ)が知られている。この発明は、マトリクス状に配置された受光素子アレイの各受光素子の出力を、それぞれ1つの対応する演算素子に入力し、並列処理するものである。これにより、演算素子への入力時間、演算時間が短縮され、各種の演算にも対応できる利点がある。

【0006】

さらに、集積化を進めるために転送ラインを列毎に最適化した特開平10−145680号公報に開示された技術(以下、従来技術2と呼ぶ)もある。

【0007】

【発明が解決しようとする課題】

こうした視覚センサを生産ラインにおける検査装置に利用することで、検査時間の大幅な短縮が可能となるが、実際には、こうした画像処理と同時に、処理対象の画像を人間が目視によって確認する必要性が生じる場合が多い。例えば、ベルトコンベア上の製品検査をする場合においては、撮像位置照明状態、ピント合せ、レンズ系の汚れ、などを目視により確認することは検査状況を把握するためには不可欠である。また、検査方法のアルゴリズムを確定する際にも、しきい値レベルの設定やマッチングポイントの設定などにおいて実画像を見ながら、処理の途中結果を画像としてモニターすることで、効率良く処理アルゴリズムの評価が行なえることになる。

【0008】

しかしながら、従来技術1あるいは2の装置では、演算を行なった結果を特徴量(対象物の重心や検査結果)または制御信号(例えばモータ制御信号)の形でしか装置外部に出力せず、撮影した画像を効率よく外部の装置に取り出す機構を有していない。CCDカメラからの画像をそのまま出力すると、高速度表示に対応したモニターが必要となるが、そのようなモニターはあっても高価であり、CCDカメラの最高フレームレートには対応していないのが現状である。

【0009】

また、特開平10−21407号公報には、こうした高速画像処理装置の画像情報と従来の画像処理装置からの画像情報をオーバーレイ表示することで、高速に動く物体を解像度良くモニターする装置が開示されている(以下、従来技術3と呼ぶ)。しかしながら、この従来技術3においては、出力される画像のフレームレートが従来とほぼ同じビデオレートに制限されてしまうため、高速に動いている物体を観測する場合において、必要な情報を取り出すことが難しい。

【0010】

例えば、自動工作機械におけるプレスの瞬間やドリルの貫通する瞬間、部品を挿入する瞬間やゴルフや野球におけるボールとクラブ(バット)の当たる瞬間等の所定のタイミングの映像が重要な意味を有する場合に、これらを解像度良く表示させることは困難であった。

【0011】

そこで、本発明は、高速での画像演算を行うとともに、撮像した画像をモニター可能な高速視覚センサ装置を提供することを課題としている。

【0012】

上記課題を解決するため、本発明に係る高速視覚センサ装置は、(1)複数の受光素子が2次元状に配列されて形成された少なくとも一つの受光素子アレイと、(2)受光素子アレイの所定の受光素子または受光素子群に対応して設けられ、対応する受光素子または受光素子群から所定の第1のフレームレートで順次読み出された出力信号をアナログ・デジタル変換する複数のA/D変換器を有し、当該複数のA/D変換器が1次元状に配列されて構成されるA/D変換器アレイと、(3)受光素子アレイの各受光素子と1対1に対応して設けられ、A/D変換器アレイから転送された対応する受光素子の出力信号に相当するデジタル信号について所定の演算を行う複数の演算素子を有し、当該複数の演算素子を2次元状に配列して、並列演算処理を行う演算素子アレイと、(4)A/D変換器アレイの各A/D変換器と当該A/D変換器に対応する演算素子または演算素子群に対応して設けられ、対応するA/D変換器または演算素子もしくは演算素子群からの出力信号を連続または所定フレームおきに数フレーム分蓄積記憶するデータバッファが一次元状に配列されて構成されるバッファメモリと、(5)バッファメモリ中に蓄積されている画像を前記第1のフレームレートより低い第2のフレームレートの画像信号として読み出して出力する画像信号変換を行う信号変換器と、(6)バッファメモリ、信号変換器に対し、演算素子アレイにおける演算処理結果に基づく所望の期間中の前記A/D変換器アレイまたは前記演算素子アレイからの出力信号を変換して出力するよう指示する信号変換制御部と、(7)信号変換器から出力された画像信号を受けて画像表示するモニタと、(8)各構成要素を制御する制御回路と、を備えていることを特徴とする。

【0013】

本発明に係る高速視覚センサ装置によれば、受光素子と1対1に配置された演算素子によって並列演算処理を行うことでリアルタイムでの高速画像処理が可能となる。そして、A/D変換器に対応してA/D変換器または演算素子もしくは演算素子群からの出力信号を連続または所定フレームおきに数フレーム分蓄積記憶するデータバッファを用いることにより、受光素子アレイで得られた画像あるいは画像処理により得られた画像の中から任意の画像群を抽出して動画像として表示することができる。

【0015】

演算素子に対応して設けられ、A/D変換器からの出力信号を所定の演算素子に順次転送する複数の転送用シフトレジスタをさらに備えている。このようにすれば、転送処理と演算処理を並列して処理することが可能となるので、無駄のない高速な画像処理が可能となる。

【0016】

【発明の実施の形態】

以下、添付図面を参照して本発明の好適な実施の形態について詳細に説明する。説明の理解を容易にするため、各図面において同一の構成要素に対しては可能な限り同一の参照番号を附し、重複する説明は省略する。

【0017】

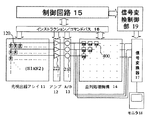

まず、図1を参照して本発明に係る高速視覚センサ装置全体の構成を簡単に説明する。図1は、本発明に係る高速視覚センサ装置の第一の実施形態のブロック図である。本実施形態の高速視覚センサ装置は、N1個×N2個の2次元状に配置された受光素子120からなる受光素子アレイ11と、受光素子アレイ11の1列ごとに対応して受光素子から出力された電荷を電圧信号に変換するN2個のチャージアンプ221からなる並列アンプ12と、チャージアンプからの出力信号をA/D変換するN2個のA/D変換器210からなるA/D変換器アレイ13と、受光素子120と1対1に対応するN1個×N2個の演算素子400からなる並列処理機構14と、回路全体に命令信号等を送って制御する制御回路15と、制御回路15からの信号を各回路に送るインストラクション/コマンドバス16と、A/D変換器アレイ13又は並列処理機構14からのデータを表示画像信号に変換する信号変換器17および変換した表示画像信号により画像表示を行うモニタ18および信号変換制御部19から構成されている。

【0018】

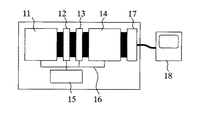

図2は、装置の構成例を示したものである。受光素子アレイ11と演算素子アレイ14、制御回路15などの半導体チップを1つの基板の上にボンディングした図である。チップを直接基板にボンディングするため高集積化が可能であり、また、それぞれの装置の特性に合わせた加工工程を採用できるため、安定した生産が可能となる。将来的にはプロセス技術の向上により1チップ上に全ての機能を集積化させることも可能である。

【0019】

続いて、各回路の内部構成について説明する。図3は、画像入力部の詳細構成を示している。画像入力部は、光を検出する受光部100(図1に示す受光素子アレイ11に相当)、受光部100からの出力信号を処理する信号処理部200(図1に示す並列アンプ12及びA/D変換器アレイ13に相当)、受光部100及び信号処理部200に動作タイミングの指示信号を通知するタイミング制御部300(図1に示す制御回路15の一部に相当)を備えている。

【0020】

最初に、図3により、図1の受光素子アレイ11に相当する受光部100の構成を説明する。受光素子120は、入力した光強度に応じて電荷を発生する光電変換素子130と、光電変換素子130の信号出力端子に接続され、垂直走査信号Vi(i=1〜N1)に応じて光電変換素子130に蓄積された電荷を出力するスイッチ素子140を1組として構成されている。この受光素子120が第1の方向(以下垂直方向と呼ぶ)に沿ってN1個配置され、各受光素子120のスイッチ素子140が電気的に接続されて垂直受光部110を構成している。そして、この垂直受光部110を垂直方向に直交する水平方向に沿ってN2個配列することにより受光部100が構成されている。

【0021】

次に、同じく図3により、図1では並列アンプ12及びA/D変換器アレイ13に相当する信号処理部200の構成を説明する。信号処理部200は、対応する垂直受光部110j(j=1〜N2)から転送されてきた電荷を個別に取り出して、処理し、この電荷強度に対応するデジタル信号を出力するA/D変換器210jをN2個配置して構成されている。A/D変換器210jは、チャージアンプ221jを含む積分回路220jと比較回路230jと容量制御機構240jの3つの回路から構成される。本実施形態では、チャージアンプ221をA/D変換器221に含む回路構成になっている。

【0022】

このうち、積分回路220jは、垂直受光部110jからの出力信号を入力として、この入力信号の電荷を増幅するチャージアンプ221jと、チャージアンプ221jの入力端子に一方の端が接続され、出力端子に他方の端が接続された可変容量部222jと、チャージアンプ221jの入力端子に一方の端が接続され、出力端子に他方の端が接続されて、リセット信号Rに応じてON、OFF状態となり、積分回路220jの積分、非積分動作を切り替えるスイッチ素子223jからなる。

【0023】

ここで、図4は、この積分回路220の詳細構成図である。本図は、4ビットつまり16階調の分解能を持つA/D変換機能を備える積分回路の例であり、以下、この回路構成により説明する。可変容量部222は、チャージアンプ221の垂直受光部からの出力信号の入力端子に一方の端子が接続された容量素子C1〜C4と、容量素子C1〜C4の他方の端子とチャージアンプ221の出力端子の間に接続され、容量指示信号C11〜C14に応じて開閉するスイッチ素子SW11〜SW14と、容量素子C1〜C4とスイッチ素子SW11〜SW14の間に一方の端子が接続され、他方の端子がGNDレベルと接続されて、容量指示信号C21〜C24に応じて開閉するスイッチ素子SW21〜SW24により構成されている。なお、容量素子C1〜C4の電気容量C1〜C4は、

C1=2C2=4C3=8C4

C0=C1+C2+C3+C4

の関係を満たす。ここで、C0は積分回路220で必要とする最大電気容量であり、受光素子130(図3参照)の飽和電荷量をQ0、基準電圧をVREFとすると、

C0=Q0/VREF

の関係を満たす。

【0024】

再び、図3に戻り、A/D変換器210jの積分回路220j以外の回路を説明する。比較回路230jは、積分回路220jから出力された積分信号VSの値を基準値VREFと比較して、比較結果信号VCを出力する。容量制御機構240jは、比較結果信号VCの値から積分回路220j内の可変容量部222jに通知する容量指示信号Cを出力すると共に、容量指示信号Cに相当するデジタル信号D1を出力する。

【0025】

続いて、図3に示すタイミング制御部300の構成を説明する。全回路のクロック制御を行う基本タイミングを発生する基本タイミング部310と、基本タイミング部310から通知された垂直走査指示に従って、垂直走査信号Viを発生する垂直シフトレジスタ320と、リセット指示信号Rを発生する制御信号部340により構成されている。

【0026】

次に、演算素子400の動作を図5により説明する。A/D変換されたデジタル信号は、それぞれの受光素子120i,jに対応する演算素子400のレジスタマトリックス401に送られる。演算素子400はそれぞれ4近傍接続されているため、インストラクションで順次隣の演算素子400に信号を送るように命令を出すことで転送する演算素子400の指定ができる。各垂直受光部110jの信号は対応する演算素子400に対して、各列が同時に転送されるため、nビット×N2回のデータ転送で、全受光素子120の光電出力データが全演算素子400に転送されることになる。

【0027】

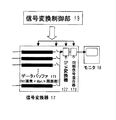

図6は、信号変換器17の詳細構成を示すブロック図である。信号変換器17内には、一列分の画像データを所定の画面数分蓄積するデータバッファ171がN2個配列され、これらのデータバッファ171には、デジタル画像信号をアナログ信号に変換するD/A変換器172とモニタ18のフレームレートに合わせて適切な同期信号を付加することにより画像信号を生成する同期信号混合器173が接続されて構成される。

【0028】

次に、図1〜図6により、本実施形態の動作について説明する。

【0029】

まず、リセット信号Rを有為に設定し、図4に示す可変容量部222のSW11〜SW14を全て「ON」、SW21〜SW24を全て「OFF」状態にする。これにより、チャージアンプ221の入力端子と出力端子間の容量値をC0に設定する。それと同時に、図3に示す全てのスイッチ素子140を「OFF」状態とし、垂直走査信号Viをいずれの受光素子120も選択しない状態に設定する。この状態から、リセット指示信号Rを非有為に設定し、各積分回路220での積分動作を開始させる。

【0030】

積分動作を開始させると、図3に示すN2個の各垂直受光部110jにある第1番目の受光素子1201,jのスイッチ素子140のみを「ON」とする垂直走査信号V1が出力される。スイッチ素子が「ON」になると、それまでの受光によって光電変換素子130に蓄積された電荷Q1は、電流信号として受光部100から出力される。つまり、光電変換素子の信号を読み出すことができる。電荷Q1は容量値C0に設定された可変容量部222に流入する。

【0031】

次に、図4により積分回路220内部の動作を説明する。容量制御機構240(図3参照)は、SW12〜SW14を開放した後、SW22〜24を閉じる。この結果、積分信号VSは、

VS=Q/C1

で示す電圧値として出力される。積分信号VSは、比較回路230に入力して、基準電圧値VREFと比較される。ここで、VSとVREFの差が、分解能の範囲以下、すなわち±(C4/2)以下の時は、一致したものとみなし、更なる容量制御は行わず、積分動作を終了する。分解能の範囲で一致しないときは、更に容量制御を行い、積分動作を続ける。

【0032】

例えば、VS>VREFであれば、容量制御機構240は、更に、SW22を開放した後に、SW12を閉じる。この結果、積分信号VSは、

VS=Q/(C1+C2)

で示す電圧値となる。この積分信号VSは、後続の比較回路230(同)に入力して、基準電圧値VREFと比較される。

【0033】

また、VS<VREFであれば、容量制御機構240は、更に、SW11及びSW22を開放した後に、SW12及びSW21を閉じる。この結果、積分信号VSは、

VS=Q/C2

で示す電圧値となる。この積分信号VSは、後続の比較回路230に送出され、基準電圧値VREFと比較される。

【0034】

以後、同様にして、積分回路220→比較回路230→容量制御機構240→積分回路220のフィードバックループによって、積分信号VSが基準電圧値VREFと分解能の範囲で一致するまで、比較及び容量設定(SW11〜SW14及びSW21〜SW24のON/OFF制御)を順次繰り返す。積分動作が終了した時点のSW11〜SW14のON/OFF状態を示す容量指示信号C11〜C14の値は、電荷Q1の値に対応したデジタル信号であり、最上位ビット(MSB)の値がC11、最下位ビット(LSB)の値がC14である。こうしてA/D変換が行われ、これらの値をデジタル信号D1として、演算素子アレイ14に出力する。以上述べたように、この装置では、デジタル信号D1の各ビット値は、MSB側からLSB側へ1ビットずつ順に定まる。

【0035】

第1番目の受光素子1201,jの光電出力に相当するデジタル信号の送出が終了すると、リセット信号Rが有為とされ、再び、非有為にして、可変容量部222jの容量値を初期化した後に、各垂直受光部110jの第2番目の受光素子1202,jのスイッチ素子140のみを「ON」とする垂直走査信号V2を出力し、上述と同様の動作により、第2番目の受光素子1202,jの光電出力を読み出し、これに相当するデジタル信号を送出する。以下、垂直走査信号を切り替えて、全受光素子120の光電出力を読み出し、相当するデジタル信号を演算素子アレイ14に出力する。

【0036】

次に、演算素子400の動作を図5により説明する。A/D変換されたデジタル信号は、それぞれの受光素子120i,jに対応する演算素子400のレジスタマトリックス401に送られる。演算素子400はそれぞれ4近傍接続されているため、インストラクションで順次隣の演算素子400に信号を送るように命令を出すことで転送する演算素子400の指定ができる。各垂直受光部110jの信号は対応する演算素子400に対して、各列が同時に転送されるため、nビット×N2回のデータ転送で、全受光素子120の光電出力データが全演算素子400に転送されることになる。

【0037】

演算素子400内部の演算は、必要があれば、各演算素子400間でそれぞれのレジスタマトリックス401に収容された信号の転送を行った後、演算に必要な信号をレジスタマトリックス401からAラッチ402とBラッチ403に読み出し、ALU404で所定の演算を行い、計算結果はレジスタマトリックス401を介して外部回路に出される。演算は全演算素子400において同時に並列処理されるため、極めて高速の演算が可能である。以下に、「エッジ抽出」を例にとり、画像処理の実行動作を詳細に説明する。

【0038】

例に挙げる「エッジ抽出」は画像処理において最も頻繁に利用される処理である。最も簡単に演算する場合は、隣接する画素の強度値との差分による2近傍演算が用いられる。これを数式で表すと、

P’(x,y)=|P(x,y)−P(x−1,y)|

となる。ここで(x,y)は素子の位置座標、P(x,y)は画像強度データの値、P’(x,y)は求めたいエッジ抽出画像の画像強度データの値である。

【0039】

転送から演算終了までの各演算素子400における演算のフロー図を図7に示す。ステップS1におけるA/D変換器210から演算素子400へのデータ転送の際に、P(x,y)とP(x−1,y)に相当するデータを各演算素子400内のレジスタマトリックス401に格納する(ステップS2)。これにより、A/D変換器アレイ11からのデータ転送が終了した後の各演算素子400間でのデータ転送をできる限り省略して、効率的で高速の処理をすることが可能になる。A/D変換器210から全演算素子400へのデータ転送が終了した時点で、レジスタマトリックス401に収容されたP(x,y)とP(x−1,y)のデータを下位ビットからAラッチ402とBラッチ403に読み出し(ステップS3)、ALU404により、差分を求める演算を行う(ステップS4)。この計算結果はいったんレジスタマトリックス401に格納する(ステップS5)。差分が求まった後、この差分値を再びAラッチ402に読み出し(ステップS6)、ALU404により、その絶対値を算出し(ステップS7)、レジスタマトリックス401に計算結果を格納し(ステップS8)、外部に出力する(ステップS9)。以上の計算処理は全ての演算素子400で同時に並列処理されるため、非常に高速で演算処理が行われる。

【0040】

画像処理でよく用いられるアルゴリズムのいくつかについて、本実施形態により演算を行った場合のステップ数、処理時間の例を表1に示す。

【0041】

【表1】

【0042】

表1から明らかなように、本実施形態では、一般的な画像処理(例えば、平滑化、細線化、コンボリューション、相関、マスク処理)演算を完全並列処理により、非常に高速で行うことができる。したがって、これまでの視覚センサ装置では、演算処理速度が遅いために制限されていたFAロボット制御などの分野への応用が可能になる。

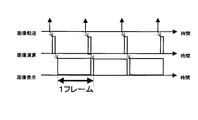

【0043】

A/D変換器アレイ13からの出力信号又は並列処理機構14からの出力信号は信号変換器17に送られ、信号変換制御部19からの指示によりモニタ18で表示するのに適した画像信号に変換される。従来技術3の装置では、図8に示されるように画像表示のタイミングに合わせて画像転送、処理演算を行う必要が有るため、高速での画像処理演算は不可能であった。これに対して、本実施形態の装置では、画像転送、画像演算を高速で行い、任意のタイミングの映像をデータバッファ171に蓄積しておいてD/A変換器172、同期信号混合器173によりモニタ18側のフレームレートに合わせた映像信号を生成して出力することで、図9にタイミングチャートを示すように、所定のタイミングの映像を抽出して時間的に引き延ばして表示することが可能である。

【0044】

例えば、図10(a)〜(c)を参照して既にチップ51、52が実装されている基板50上にさらにチップ53を装置54を用いて実装する瞬間の画像を抽出する例について説明する。図10(b)が所望のチップ53が実装される瞬間の画像であり、図10(a)、図10(c)はそれぞれその前後のタイミングで取得された画像である。

【0045】

このチップ53が実装される瞬間の画像を抽出するためには、入力画像の中から、特徴抽出演算によって対象画像であるチップ53を抽出し、その対象が基板の所定の位置に実装されるタイミングで画像を出力する。具体的には、まず、入力画像P(x,y)が並列処理機構14に転送され、すでに記憶されている検索画像s(x,y)(大きさn1×m1)を検索する。マッチングの演算アルゴリズムは数多く提案されているが、ここでは最も簡便な演算である差分演算で示す。

【0046】

【数1】

【0047】

この関数Errorの値の最も小さい位置から、入力画像P(x,y)の中から検索画像s(n1,m1)に一番似ている(誤差の小さい)画像を検索できる。この最小の誤差が得られた原画像P(x,y)を所定のタイミングにおける画像データとして信号変換制御部19から信号変換器17に対して画像信号への変換を指示することによりこのタイミングの画像(図7(b)に示されるタイミングの画像)前後の映像をモニタ18に表示させることができる。

【0048】

たとえば、本機能を用いることで、「ドリルが加工対象に接触する瞬間」や「バットがボールにぶつかる瞬間」とその前後の、最も重要な情報を含む画像列を抽出してモニター画像出力することが可能となる。従来の画像処理装置との整合性も併せ持つ為、すでに利用している画像処理アルゴリズムをそのまま利用して、高速対象物の画像処理を実現できる。また、画像処理された処理画像、例えば、エッジ抽出された画像や、移動している物体のみを抽出した画像などを出力することも可能である。

【0049】

特に、本装置においては、並列受光素子アレイ11からの信号を列並列にて転送を行なっており、並列演算機構14により並列演算を行なうことで、高速な演算処理が実現できる。高速移動物体を追跡する場合に、回転や向きの変化がある場合には、従来のTVカメラのような遅いフレームレート(30Hz)では、対象物の画像上の形状が変化してしまうため、フレーム間の画像から同じ対象物を判断するために非常に複雑なアルゴリズムが必要となりリアルタイムに表示させることが困難であった。一方、本装置のように高いフレームレート(>1KHz)で画像が捉えられる場合には、フレーム間の画像の違いは小さいために、上記のような簡単なアルゴリズムで高速にマッチングが行なえることになり、対象物を正確に追跡することが可能となる。

【0050】

本発明が目指しているのは、高速画像処理された結果から、所望のタイミングの画像を抽出してモニターする機能を有する画像センサ装置である。処理速度の目安としては、FAロボットの制御においては、対象物の移動速度とロボットのアクチュエータの速度(1〜10ミリ秒)から必要な処理速度が決まる。本実施形態では、この処理速度は、A/D変換器210におけるA/D変換処理速度によって決まるが、A/D変換器からの出力のビット数は可変できるため、より高速演算が必要な場合には、ビット数を減らすことによって高速化が可能である。例えば、8ビット変換に10μ秒かかっているような場合、4ビットにデータ長を削減することで、ほぼ2倍の変換速度が実現できることになる。

【0051】

図11は、本発明に係る高速視覚センサ装置の第二の実施形態を示す概略ブロック図である。この実施形態では、図1に示される第一の実施形態の並列処理機構14の演算素子400にそれぞれ転送専用シフトレジスタ410を設けている点が相違する。このように、データ転送専用のシフトレジスタを設けることで、演算素子400で演算処理を行っている間に、次のフレームの画像データを転送したり、演算に必要なデータの転送を行うことができるので、転送と演算を並列処理することでより高速の画像処理を行うことができて好ましい。

【0052】

ここでは、信号変換器に複数の画面分のデータバッファを有する例について説明してきたが、特定のタイミングの静止映像のみを取得すれば充分である場合には、データバッファを省略することでより簡易な装置構成とすることも可能である。

【0053】

【発明の効果】

以上説明したように本発明によれば、並列処理による高速の画像処理と目視検査等に必要となる所望のタイミングでの高速処理画像のモニター出力が可能であり、例えば、注目すべき画像のみを抽出したモニタ表示が可能となる。

【0054】

特に、信号変換器に複数の画面の画像情報を蓄積可能なデータバッファを設けることで、所望のタイミング付近の映像を時間的に引き延ばしてモニタ表示することも可能となる。

【0055】

また、A/D変換器から演算素子へのデータ転送時に、転送用シフトレジスタを用いて、演算処理と転送を独立に実行できる機能を実現することで、実時間処理が可能となる。

【図面の簡単な説明】

【図1】本発明に係る高速視覚センサ装置の第一の実施形態のブロック図である。

【図2】図1の実施形態を示す概略構成図である。

【図3】図1の実施形態の受光素子アレイ、並列アンプ及びA/D変換器アレイの回路構成図である。

【図4】図1の実施形態の積分回路の詳細回路構成図である。

【図5】図1の実施形態の演算素子のブロック図である。

【図6】図1の実施形態の信号変換器の詳細ブロック図である。

【図7】図5の演算素子の2近傍演算時のフロー図である。

【図8】従来技術における演算処理と画像表示のタイミングチャートである。

【図9】図1の実施形態における演算処理と画像表示のタイミングチャートである。

【図10】抽出する画像イメージを示す図である。

【図11】本発明に係る高速視覚センサ装置の第二の実施形態のブロック図である。

【符号の説明】

11…受光素子アレイ、12…アンプ、13…A/D変換器アレイ、14…演算素子アレイ、15…制御回路、16…インストラクション/コマンドバス、17…信号変換器、18…モニター、100…受光部、110…垂直受光部、120…受光素子、130…光電変換素子、140…スイッチ素子、200…信号処理部、210…A/D変換器、220…積分回路、221…チャージアンプ、222…可変容量部、223…スイッチ素子、230…比較回路、240…容量制御機構、300…タイミング制御部、310…基本タイミング部、320…垂直シフトレジスタ、340…制御信号部、400…演算素子、401…レジスタマトリックス、402…Aラッチ、403…Bラッチ、404…ALU、410…転送用シフトレジスタ、500…対象物、501…テレビカメラ、502…画像処理装置、C1〜C4…容量素子、SW11〜SW14、SW21〜SW24…スイッチ素子。

Claims (2)

- 複数の受光素子が2次元状に配列されて形成された少なくとも一つの受光素子アレイと、

前記受光素子アレイの所定の受光素子または受光素子群に対応して設けられ、対応する受光素子または受光素子群から所定の第1のフレームレートで順次読み出された出力信号をアナログ・デジタル変換する複数のA/D変換器を有し、当該複数のA/D変換器が1次元状に配列されて構成されるA/D変換器アレイと、

前記受光素子アレイの各受光素子と1対1に対応して設けられ、前記A/D変換器アレイから転送された対応する受光素子の出力信号に相当するデジタル信号について所定の演算を行う複数の演算素子を有し、当該複数の演算素子を2次元状に配列して、並列演算処理を行う演算素子アレイと、

前記A/D変換器アレイの各A/D変換器と当該A/D変換器に対応する演算素子または演算素子群に対応して設けられ、対応する前記A/D変換器または前記演算素子もしくは前記演算素子群からの出力信号を連続または所定フレームおきに数フレーム分蓄積記憶するデータバッファが一次元状に配列されて構成されるバッファメモリと、

前記バッファメモリ中に蓄積されている画像を前記第1のフレームレートより低い第2のフレームレートの画像信号として読み出して出力する画像信号変換を行う信号変換器と、

前記バッファメモリ、前記信号変換器に対し、前記演算素子アレイにおける演算処理結果に基づく所望の期間中の前記A/D変換器アレイまたは前記演算素子アレイからの出力信号を変換して出力するよう指示する信号変換制御部と、

前記信号変換器から出力された画像信号を受けて画像表示するモニタと、

前記各構成要素を制御する制御回路と、

を備えていることを特徴とする高速視覚センサ装置。 - 前記演算素子に対応して設けられ、前記A/D変換器からの出力信号を所定の前記演算素子に順次転送する複数の転送用シフトレジスタをさらに備えていることを特徴とする請求項1記載の高速視覚センサ装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP14180199A JP4334672B2 (ja) | 1999-05-21 | 1999-05-21 | 高速視覚センサ装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP14180199A JP4334672B2 (ja) | 1999-05-21 | 1999-05-21 | 高速視覚センサ装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000333083A JP2000333083A (ja) | 2000-11-30 |

| JP2000333083A5 JP2000333083A5 (ja) | 2006-06-01 |

| JP4334672B2 true JP4334672B2 (ja) | 2009-09-30 |

Family

ID=15300461

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP14180199A Expired - Lifetime JP4334672B2 (ja) | 1999-05-21 | 1999-05-21 | 高速視覚センサ装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4334672B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4863340B2 (ja) * | 2001-06-05 | 2012-01-25 | 浜松ホトニクス株式会社 | 画像計測カメラ |

| US7633539B2 (en) | 2004-06-07 | 2009-12-15 | Canon Kabushiki Kaisha | Image pickup device with analog-to-digital converter |

| JP4492312B2 (ja) * | 2004-11-25 | 2010-06-30 | ソニー株式会社 | 撮像装置と撮像方法 |

| JP2008154292A (ja) * | 2008-03-17 | 2008-07-03 | Canon Inc | 撮像装置及び撮像システム |

| JP2008154291A (ja) * | 2008-03-17 | 2008-07-03 | Canon Inc | 撮像装置及び撮像システム |

| CN103019656B (zh) * | 2012-12-04 | 2016-04-27 | 中国科学院半导体研究所 | 可动态重构的多级并行单指令多数据阵列处理系统 |

| US9449257B2 (en) | 2012-12-04 | 2016-09-20 | Institute Of Semiconductors, Chinese Academy Of Sciences | Dynamically reconstructable multistage parallel single instruction multiple data array processing system |

| CN108781265B (zh) | 2016-03-30 | 2020-11-03 | 株式会社尼康 | 特征提取元件、特征提取系统及判定装置 |

-

1999

- 1999-05-21 JP JP14180199A patent/JP4334672B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000333083A (ja) | 2000-11-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4592243B2 (ja) | 高速画像処理カメラシステム | |

| US6970196B1 (en) | High-speed vision sensor with image processing function | |

| EP3154258B1 (en) | Image sensor with multiple photoelectric conversion means per pixel, using only some pixel photoelectric conversion means for focus detection and all for image capture | |

| JP2010136413A (ja) | 高速視覚センサ装置 | |

| JP4334672B2 (ja) | 高速視覚センサ装置 | |

| JP2001358999A (ja) | 画像入力装置 | |

| KR20100135705A (ko) | 고체 촬상 장치 및 x선 검사 시스템 | |

| JP3308146B2 (ja) | 固体撮像装置 | |

| KR20110005770A (ko) | 고체 촬상 장치 및 x선 검사 시스템 | |

| KR20100047826A (ko) | 고체 촬상 장치 | |

| JP4928069B2 (ja) | 撮像装置及び撮像システム | |

| WO2017188018A1 (ja) | 固体撮像素子および固体撮像素子の動作方法、撮像装置、および電子機器 | |

| JP2001175878A (ja) | 画像特徴抽出装置、画像特徴抽出方法、監視検査システム、半導体露光システム、およびインターフェースシステム | |

| JPH10145680A (ja) | 高速視覚センサ装置 | |

| JP4302212B2 (ja) | 高速視覚センサ装置 | |

| US11962920B2 (en) | Imaging device, method of driving imaging device, and electronic equipment | |

| JP2000299820A (ja) | 高速視覚センサ装置 | |

| JP2003172611A (ja) | 物体表面形状計測装置 | |

| JP2995930B2 (ja) | 画像処理装置 | |

| JPH08294057A (ja) | 固体撮像素子 | |

| JP4048849B2 (ja) | 固体撮像素子 | |

| US20120120292A1 (en) | Method and system for operating an image data collection device | |

| Gallagher | Vision systems for quality control | |

| JPH1196336A (ja) | 演算処理機能を有する2次元撮像センサ及び画像計測デバイス | |

| JP2003110803A (ja) | 固体撮像装置および固体撮像システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060410 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060410 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20081210 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090106 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090306 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090623 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090624 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120703 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120703 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130703 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130703 Year of fee payment: 4 |

|

| EXPY | Cancellation because of completion of term |