JP4309070B2 - 不揮発性半導体記憶装置およびその製造方法 - Google Patents

不揮発性半導体記憶装置およびその製造方法 Download PDFInfo

- Publication number

- JP4309070B2 JP4309070B2 JP2001023973A JP2001023973A JP4309070B2 JP 4309070 B2 JP4309070 B2 JP 4309070B2 JP 2001023973 A JP2001023973 A JP 2001023973A JP 2001023973 A JP2001023973 A JP 2001023973A JP 4309070 B2 JP4309070 B2 JP 4309070B2

- Authority

- JP

- Japan

- Prior art keywords

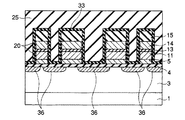

- memory cell

- transistor

- diffusion layer

- insulating film

- gate electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001023973A JP4309070B2 (ja) | 2001-01-31 | 2001-01-31 | 不揮発性半導体記憶装置およびその製造方法 |

| US10/058,343 US6835987B2 (en) | 2001-01-31 | 2002-01-30 | Non-volatile semiconductor memory device in which selection gate transistors and memory cells have different structures |

| US10/942,013 US6949794B2 (en) | 2001-01-31 | 2004-09-16 | Non-volatile semiconductor memory device in which selection gate transistors and memory cells have different structures |

| US11/225,094 US7122869B2 (en) | 2001-01-31 | 2005-09-14 | Nonvolatile semiconductor memory device in which selection transistors and memory transistors have different impurity concentration distributions |

| US11/538,944 US7274075B2 (en) | 2001-01-31 | 2006-10-05 | Nonvolatile semiconductor memory device having pair of selection transistors with different source and drain impurity concentrations and with different channel dopant concentrations |

| US11/857,934 US7737508B2 (en) | 2001-01-31 | 2007-09-19 | Non-volatile semiconductor memory device and method of manufacturing the same |

| US12/779,357 US8338252B2 (en) | 2001-01-31 | 2010-05-13 | Non-volatile semiconductor memory device and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001023973A JP4309070B2 (ja) | 2001-01-31 | 2001-01-31 | 不揮発性半導体記憶装置およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002231832A JP2002231832A (ja) | 2002-08-16 |

| JP2002231832A5 JP2002231832A5 (enExample) | 2005-10-06 |

| JP4309070B2 true JP4309070B2 (ja) | 2009-08-05 |

Family

ID=18889180

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001023973A Expired - Fee Related JP4309070B2 (ja) | 2001-01-31 | 2001-01-31 | 不揮発性半導体記憶装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4309070B2 (enExample) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100524993B1 (ko) | 2003-11-28 | 2005-10-31 | 삼성전자주식회사 | 높은 집적도 및 낮은 소스저항을 갖는 이이피롬셀,이이피롬소자 및 그 제조방법 |

| JP2005327792A (ja) * | 2004-05-12 | 2005-11-24 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2009081202A (ja) | 2007-09-25 | 2009-04-16 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| KR100884344B1 (ko) | 2007-10-10 | 2009-02-18 | 주식회사 하이닉스반도체 | 비대칭 소스/드레인 접합을 갖는 불휘발성 메모리소자 및그 제조방법 |

| JP2010161301A (ja) | 2009-01-09 | 2010-07-22 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| JP2012059945A (ja) | 2010-09-09 | 2012-03-22 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2013187504A (ja) * | 2012-03-09 | 2013-09-19 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

-

2001

- 2001-01-31 JP JP2001023973A patent/JP4309070B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002231832A (ja) | 2002-08-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6835987B2 (en) | Non-volatile semiconductor memory device in which selection gate transistors and memory cells have different structures | |

| US10741570B2 (en) | Nonvolatile memory devices having single-layered gates and methods of fabricating the same | |

| US6716703B2 (en) | Method of making semiconductor memory device having sources connected to source lines | |

| KR100398955B1 (ko) | 이이피롬 메모리 셀 및 형성 방법 | |

| US6376879B2 (en) | Semiconductor device having MISFETs | |

| US20030013253A1 (en) | Optimized flash memory cell | |

| JP2004241780A (ja) | 選択的ディスポーザブルスペーサー技術を使用する半導体集積回路の製造方法及びそれによって製造される半導体集積回路 | |

| JP4445353B2 (ja) | 直接トンネル型半導体記憶装置の製造方法 | |

| US8952536B2 (en) | Semiconductor device and method of fabrication | |

| US20030011023A1 (en) | Metal local interconnect self-aligned source flash cell | |

| JP2006286720A (ja) | 半導体装置およびその製造方法 | |

| JP4217409B2 (ja) | 不揮発性メモリ素子及びその製造方法 | |

| JP4309070B2 (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| US8878253B2 (en) | Semiconductor devices | |

| JPWO2003069675A1 (ja) | 半導体装置の製造方法 | |

| US20080023748A1 (en) | Self-aligned contacts to source/drain regions | |

| JP4972918B2 (ja) | 半導体装置及びその製造方法 | |

| KR20070049731A (ko) | 플래시 메모리 및 그 제조방법 | |

| KR20090007862A (ko) | 반도체 소자 및 그의 제조방법 | |

| JP2002289706A (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| JP3669070B2 (ja) | 半導体装置及びその製造方法 | |

| JP4031777B2 (ja) | 半導体装置 | |

| KR20080100968A (ko) | 비휘발성 메모리 소자 및 그 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050518 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050518 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071015 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080722 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080917 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090407 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090507 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120515 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120515 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130515 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130515 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140515 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |