JP4292425B2 - グレイコードカウンタ及び表示装置 - Google Patents

グレイコードカウンタ及び表示装置 Download PDFInfo

- Publication number

- JP4292425B2 JP4292425B2 JP2007075958A JP2007075958A JP4292425B2 JP 4292425 B2 JP4292425 B2 JP 4292425B2 JP 2007075958 A JP2007075958 A JP 2007075958A JP 2007075958 A JP2007075958 A JP 2007075958A JP 4292425 B2 JP4292425 B2 JP 4292425B2

- Authority

- JP

- Japan

- Prior art keywords

- gray code

- bit

- circuit

- output

- value

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000003111 delayed effect Effects 0.000 claims description 9

- 230000001934 delay Effects 0.000 claims description 5

- 239000004973 liquid crystal related substance Substances 0.000 description 11

- 238000010586 diagram Methods 0.000 description 6

- 239000011521 glass Substances 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

Images

Landscapes

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Description

11〜15 AND回路

21〜26 選択回路

31〜38 D型フリップフロップ(RDFF)

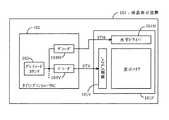

101 液晶表示装置 101P 表示パネル

101H 水平ドライバ 101V 垂直ドライバ

102 タイミングコントローラIC

103 グレイコードカウンタ

104H,104V デコーダ

Claims (4)

- グレイコードを生成するグレイコードカウンタにおいて、

第nビットのグレイコードの1つ下位ビットである第(n−1)ビットのグレイコードのクロックを2分周する分周回路と、

前記分周回路の出力を第(n−2)ビット以下のグレイコードに基づいて遅延する遅延回路と、

前記遅延回路の出力をクロックに応じて保持し、かつ遅延して、第nビットのグレイコードを出力する順序回路と、を備えることを特徴とするグレイコードカウンタ。 - 前記遅延回路は、前記第(n−2)ビット以下のグレイコードの値が第1の値である時に、前記分周回路の出力を選択して出力し、前記第(n−2)ビット以下のグレイコードの値が第2の値である時に、前記順序回路の出力を選択して出力することで、前記第(n−2)ビット以下のグレイコードの値が前記第1の値になるまで前記分周回路の出力を遅延することを特徴とする請求項1に記載のグレイコードカウンタ。

- 前記遅延回路は、第1ビットから第(n−2)ビットまでの(n−2)ビット分のグレイコードの論理積を作成する論理積回路と、この論理積が第1の値である時に、前記分周回路の出力を選択し、前記論理積が第2の値である時に、前記順序回路の出力を選択する選択回路とを備えることで、前記論理積が前記第1の値になるまで前記分周回路の出力を遅延することを特徴とする請求項1に記載のグレイコードカウンタ。

- 請求項1、2、3のいずれかに記載のグレイコードカウンタを備えた表示装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007075958A JP4292425B2 (ja) | 2007-03-15 | 2007-03-23 | グレイコードカウンタ及び表示装置 |

| US12/036,031 US7596201B2 (en) | 2007-03-15 | 2008-02-22 | Gray code counter and display device therewith |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007066104 | 2007-03-15 | ||

| JP2007075958A JP4292425B2 (ja) | 2007-03-15 | 2007-03-23 | グレイコードカウンタ及び表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008258660A JP2008258660A (ja) | 2008-10-23 |

| JP4292425B2 true JP4292425B2 (ja) | 2009-07-08 |

Family

ID=39981837

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007075958A Active JP4292425B2 (ja) | 2007-03-15 | 2007-03-23 | グレイコードカウンタ及び表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4292425B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102664062B1 (ko) * | 2019-05-30 | 2024-05-14 | 삼성전자주식회사 | 비동기 카운터와 동기 카운터를 포함하는 코드 생성기 및 그것의 동작 방법 |

| KR102868858B1 (ko) * | 2019-11-27 | 2025-10-10 | 삼성전자주식회사 | 그레이 카운터 및 그것을 포함하는 이미지 센서 |

| JP7570899B2 (ja) * | 2020-11-25 | 2024-10-22 | シャープセミコンダクターイノベーション株式会社 | 多ビットグレイコード生成回路 |

-

2007

- 2007-03-23 JP JP2007075958A patent/JP4292425B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008258660A (ja) | 2008-10-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7596201B2 (en) | Gray code counter and display device therewith | |

| CN100583295C (zh) | 移位寄存器及液晶显示装置 | |

| KR101857808B1 (ko) | 스캔구동부와 이를 이용한 유기전계발광표시장치 | |

| JP4093197B2 (ja) | 表示ドライバ及び電子機器 | |

| CN102298916B (zh) | 驱动电路、液晶显示装置和电子信息设备 | |

| CN104966506A (zh) | 一种移位寄存器、显示面板的驱动方法及相关装置 | |

| JP2003066919A (ja) | 半導体集積回路装置 | |

| JP2009109598A (ja) | 走査信号線駆動回路および表示装置 | |

| JP6115407B2 (ja) | 表示パネル、その駆動方法、および電子機器 | |

| JP4292425B2 (ja) | グレイコードカウンタ及び表示装置 | |

| CN112908275B (zh) | 数据信号线驱动电路和具备其的液晶显示装置 | |

| JP2009246482A (ja) | プライオリティエンコーダならびにそれを利用した時間デジタル変換器、試験装置 | |

| US20070146290A1 (en) | Device for driving a display panel | |

| JP6650459B2 (ja) | 表示パネル及びその駆動回路 | |

| JP6775640B2 (ja) | グレイコードカウンタ | |

| CN101079244B (zh) | 显示图像系统 | |

| JP2007006368A (ja) | A/d変換回路 | |

| JP4762251B2 (ja) | 液晶表示装置およびその駆動方法 | |

| US20090040213A1 (en) | Liquid Crystal Driving Apparatus | |

| GB2403082A (en) | Arrangement and method for a digital delay line | |

| JP4666462B2 (ja) | カウンタ回路と、それを含む半導体装置 | |

| CN102024401B (zh) | 驱动装置、显示面板、显示装置以及电子系统 | |

| KR101152461B1 (ko) | 비동기 그레이-코드 카운터 | |

| CN119339684B (zh) | 栅极驱动电路、显示面板和显示装置 | |

| JP4581667B2 (ja) | タイミングジェネレータ及び表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090106 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090217 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090311 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090324 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120417 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4292425 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120417 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130417 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130417 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140417 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |