JP4224243B2 - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP4224243B2 JP4224243B2 JP2002066727A JP2002066727A JP4224243B2 JP 4224243 B2 JP4224243 B2 JP 4224243B2 JP 2002066727 A JP2002066727 A JP 2002066727A JP 2002066727 A JP2002066727 A JP 2002066727A JP 4224243 B2 JP4224243 B2 JP 4224243B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- mos transistor

- monos

- oxide film

- channel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Description

【発明の属する技術分野】

本発明は、半導体記憶装置の構造とその製造方法とに関し、とくに低電圧読み出しが可能であり、かつ半導体記憶装置のメモリ特性向上と製造の容易さと高信頼性に関するものである。

【0002】

【従来の技術】

電気的に書き込みが可能である半導体記憶装置としては、浮遊ゲート中に電子を注入し書き込みを行う高集積半導体記憶装置として知られているフラッシュ型EEPROMや、MONOS型メモリとして知られている絶縁膜中に電子を注入し書き込みを行う半導体記憶装置などがある。これらの従来技術について以下説明する。

【0003】

[第1の従来例:図18]

従来、半導体記憶装置としてフラッシュ型EEPROMが考えられている。

以下、図18を参照にしながら、従来の半導体記憶装置の一例を説明する。図18は従来の半導体記憶装置構造の一例を示す断面図である。

N型の半導体基板1に、第1のPウェル領域11を設ける。この第1のPウェル領域11に、酸化絶縁膜である第1の酸化膜21が形成され、さらに第1の酸化膜21の上には多結晶シリコン膜で形成した浮遊ゲート31と第2の酸化膜22と多結晶シリコン膜で形成した制御ゲート32からなるメモリトランジスタ51を複数個(図面では2個)設け、積層型メモリセル52を形成する。メモリトランジスタ51の整合した領域の第1のPウェル領域11に高濃度N型拡散層41を設ける。積層型メモリセル52の周辺の半導体基板1には、積層型メモリセル52の動作を制御する周辺回路55を設ける。この周辺回路55は、半導体基板1に設けたNウェル領域13に形成するPチャネル型MOSトランジスタ54と、第2のPウェル領域12に形成するNチャネル型MOSトランジスタ53とから構成する。

【0004】

この積層型メモリセル52では、通常、消去は一括消去であるため、全ての制御ゲート32を0Vにし、一度に全ビット同時に消去する。すなわち、N型の半導体基板1と第1のPウェル領域11に高電圧を印加し、高濃度N型拡散層41はフローティングにする。浮遊ゲート31より半導体基板1の第1のPウェル領域11へ電子が第1の酸化膜21はトンネル効果で抜け、メモリトランジスタ51のしきい値電圧が正から負へシフトする。このためPウェルをメモリセル52用の第1のPウェル領域11と、周辺回路55用の第2のPウェル領域12とに分け、消去時は周辺回路55用の第2のウェル領域12は常に0Vに保つようにする。

【0005】

このように、Pウェルをメモリセル52用の第1のウェル領域11と周辺回路55用の第2のPウェル領域12とに分け、消去時の高バイアス印加による周辺回路55用のMOSトランジスタ53,54の破壊または劣化を防いでいる。

【0006】

さらに、周辺回路55用のMOSトランジスタ53とメモリトランジスタ51の初期しきい値電圧をそれぞれのPウェル領域の濃度により制御している。これにより、メモリトランジスタ51の書き込み時に用いるホットエレクトロンの発生を増すために、メモリトランジスタ51用の第1のPウェル領域11の濃度を濃くすることができ、高速書き込みが可能となっている。これに対し、周辺回路55用の第2のPウェル領域12の濃度は、薄くすることができ、ウェル濃度上昇によるドレイン耐圧低下を防ぐ事を可能としている。

【0007】

[第2の従来例:図19]

さらに、フラッシュ型メモリトランジスタは図19に示すように、絶縁膜に囲まれた導電性の蓄積電荷層を設けた構造を有する

図19は、代表的なフラッシュメモリセルを模式的に示す断面図である。

半導体基板1のPウェル領域11に、第1の酸化膜21と、浮遊ゲート31と、第2の酸化膜22と、制御ゲート32とを順次設ける。制御ゲート32に整合する領域のPウェル領域11にソース42とドレイン41を設ける。

【0008】

書き込みをドレイン41側で、消去をソース42側で行うため、ドレイン41、ソース42の拡散層は、それぞれ目的に合わせて最適化し、ドレイン41、ソース42は非対称構造としている。すなわちドレイン41側はホットエレクトロンの注入効率を高めるためにPウェル領域11の濃度より濃くしたP層14が設けられ、また、書き込み時のデータディスターブを抑制するためにドレイン41領域はソース42に比べ低濃度化されている。これに対して、ソース42は消去動作時の表面空乏化を防止するためにドレイン41に比べ高濃度化されている。これらのドレイン41、ソース42およびP層14のように、フラッシュ型メモリトランジスタは、複雑な構造を有している。

【0009】

[第3の従来例:図20]

一方、比較的低電圧で書き込み消去が可能であるMONOS型メモリトランジスタ56を有する半導体記憶装置では、MONOS型メモリトランジスタ56とMOSトランジスタ53とは、図20に示すように同一のPウェル領域11内に形成することが可能である。半導体基板1のPウェル領域11に、トンネル酸化膜71とメモリ窒化膜72とトップ酸化膜73とゲート電極33とを順次設けたMONOS型メモリトランジスタ56と、ゲート酸化膜74とゲート電極33とを順次設けたMOSトランジスタ53とを設けるゲート電極33に整合した領域のPウェル領域11に高濃度N型拡散層41を設ける。しかし一般的には、上記MONOS型メモリトランジスタ56のチャネル部分に不純物を導入したチャネルドープ層14を形成し、MONOS型メモリトランジスタ56の初期しきい値電圧を制御している。チャネルドープ層14によるMONOS型メモリトランジスタ56の初期しきい値電圧の制御は、センスレベルに対するデータ保持特性の最終収束しきい値電圧を設定するためである。

【0010】

図20で説明したMONOS型メモリトランジスタ56のデータを読み出す回路を図21の回路図を用いて説明する。

図21は、MONOS型メモリトランジスタ56を読み出す回路構成を示す図である。この図21に示す読み出し回路において、書き込みと消去における中央のしきい値電圧にセンスレベルを設定するように、Pチャネル型MOSトランジスタ54のオン抵抗を制御している。Pチャネル型MOSトランジスタ54とNチャネル型MOSトランジスタ53とMONOS型メモリトランジスタ56と出力インバータ61とから構成しており、データ読み出し時には、Nチャネル型MOSトランジスタ53とPチャネル型MOSトランジスタ54とをオンする。この場合、出力インバータ61の入力値は、MONOS型メモリトランジスタ56のオン抵抗が高い書き込み状態では、これに比べPチャネル型MOSトランジスタ54のオン抵抗が低くなりハイレベルとなる。逆に、MONOS型メモリトランジスタ56のオン抵抗が低い消去状態では、ロウレベルとなる。すなわち、Pチャネル型MOSトランジスタ54とMONOS型メモリトランジスタ56とのオン抵抗比でデータを読み出している。このため、Pチャネル型MOSトランジスタ54は、MONOS型メモリトランジスタ56の書き込みと消去におけるしきい値の中央値をセンスレベルの電圧に設定するようにオン抵抗を制御している。このため、初期、書き込み後、消去後のそれぞれのしきい値電圧管理を行っている。

【0011】

【発明が解決しようとする課題】

このように、図18を用いて説明したフラッシュEEPROMでは、書き込みまたは消去時のバイアス印加による周辺回路55用MOSトランジスタの破壊または劣化を防ぐためにPウェル領域11,12をメモリセル52用と周辺回路55用とに分けている。このため製造プロセスが長くなるとともに、Pウェル領域を制御するための回路も必要となり、チップ面積が大きくなるという問題点を有している。

【0012】

さらに、図19を用いて説明したフラッシュEEPROMのメモリトランジスタの構造は、上記したようにホットエレクトロンの発生を増すために、ドレイン領域に接する部分にP層14を設けてウェル濃度11を濃くするなど、トランジスタ構造自体が複雑になっている。このように、P層14の濃度が高いためにドレイン耐圧の低下が問題となり、さらに複雑な構造を得るための製造プロセスが長くなるという問題点を有している。

【0013】

このように、製造プロセスが長くなるということは、工程数の増加とともに、工程の複雑化が進み、各工程での歩留り低下要因が増加することとなる。 とくに、少数ビットの搭載で十分なシステムLSIでは、製造プロセスの複雑化は歩留りの面からも問題である。

【0014】

また、図21で示した上述の読み出し回路では、書き込みと消去における各しきい値電圧の中央の電圧にセンスレベルを設定するようにPチャネル型MOSトランジスタ54のオン抵抗を制御している。このしきい値電圧中央の電圧はメモリトランジスタ56の初期しきい値電圧に近い値となるように通常設定する。このため、初期読み出しデータはプロセスばらつきにより、書き込み、消去状態が混在することとなる。製品の初期検査では、各メモリトランジスタの書き込み消去特性を評価する必要があるため、テスティング時に一括消去動作を行い、データを消去状態にしてから書き込みを行う必要がある。

【0015】

さらに、センスレベルを上記のように、初期しきい値電圧に近い電圧に設定しているため、データ保持特性は書き込み側、消去側のいずれかで決まる事になり、データ保持特性ばらつきが発生する要因となる。

また、図21に示した読み出し回路では、常時メモリトランジスタ56のドレインとソース側で電位差があるため、ドレインディスターブによるデータ変化が生じ問題である。

【0016】

[発明の目的]

この発明は、このような半導体記憶装置を構成するための製造工程の増加およびチップサイズの増大をなくし、さらに、低電圧読み出しが可能であり、信頼性の高い半導体記憶装置を提供することを目的とする。

【0017】

【課題を解決するための手段】

この発明による半導体記憶装置は、上記目的を達成するために、次のような半導体記憶装置を提供する。

【0018】

この発明による半導体記憶装置は、ソースを電源電位に接続するPチャネル型MOSトランジスタと、Pチャネル型MOSトランジスタのドレインと接地電位との間に直列接続する少なくとも1つのMONOS型メモリトランジスタと、 MONOS型メモリトランジスタと並列接続するNチャネル型MOSトランジスタと、を有し、MONOS型メモリトランジスタおよびNチャネル型MOSトランジスタとPチャネル型MOSトランジスタとの接続点を出力とし、この出力を出力インバータの入力に接続することを特徴とする。

【0019】

この発明による半導体記憶装置は、請求項2記載の半導体記憶装置において、Pチャネル型MOSトランジスタのソースに定電圧発生回路を接続することを特徴とする。

【0022】

[作用]

本発明の半導体記憶装置は、周辺回路用MOSトランジスタとメモリトランジスタが同一Pウェル内に形成し、かつMOSトランジスタを構成するゲート酸化膜厚より、メモリトランジスタを構成するメモリ絶縁膜の実効酸化膜厚を薄くすることにより、メモリトランジスタのしきい値電圧を周辺回路用MOSトランジスタのしきい値電圧より低く設定している。さらに、周辺回路用MOSトランジスタとメモリトランジスタを構成するドレインとソースの拡散層の不純物濃度を同じで構成しているため、メモリトランジスタの周辺回路との混載が容易となり、製造プロセスが簡易となる。

【0023】

このように、メモリトランジスタを構成するメモリ絶縁膜の実効酸化膜厚を制御することにより、メモリトランジスタの初期しきい値を設定している。したがって、読み出し回路によるメモリトランジスタのデータ読み出しの初期値は一定の値を示し安定する。

【0024】

本発明の半導体記憶装置では、トンネル酸化膜厚を32から45Åと厚くし、半導体基板からの正孔注入が9MV/cm以下の電界で生じない構成としているため、メモリトランジスタの初期しきい値からしきい値電圧が低下することがない。このため、読み出し回路において、安定して初期データを消去状態とすることが可能となり、データ保持特性を電子注入による書き込み側のみで決める事ができ、特性が安定化できる。

【0025】

さらに、通常メモリトランジスタでは、初期しきい値電圧のばらつきを緩和するために、テスティング時に一括消去を行った後にデータ書き込みを行うが、本発明では、メモリトランジスタを構成するメモリ絶縁膜の膜厚により初期しきい値電圧を制御しているため、上記のように初期しきい値電圧はすべて消去状態となっており、正孔注入を利用するため電子注入に比べ比較的長い時間の必要な消去動作を行わなくてよく、テスティング時間の短縮となる利点も得られる。

【0026】

本発明の半導体記憶装置は、MOSトランジスタを構成するゲート酸化膜とメモリトランジスタを構成するメモリ絶縁膜の膜厚を制御することにより、同一Pウェル濃度で、MOSしきい値電圧0.4から0.6V、MONOS型メモリトランジスタのしきい値電圧を0.3V以下と制御しているため、複雑なプロセスが必要なく、しかも、しきい値電圧を低く設定しているため、1V電源での低電圧動作が可能である。

【0027】

本発明の半導体記憶装置は、メモリトランジスタの初期データをPチャネル型MOSトランジスタのON抵抗を制御し、消去状態とし、データ保持特性は電子注入状態である書き込み側のみで決まるように設定している。このため、テスティングでの消去動作が不要である。

【0028】

また、Nチャネル型MOSトランジスタをMONOS型メモリトランジスタに並列に接続した構成としており、データ読み出しを行わない待機時には、このNチャネル型MOSトランジスタをオンとしているため、待機時のMONOS型メモリトランジスタのソース、ドレイン両端子は同電位となっている。したがって、メモリトランジスタで問題となるドレイン電圧印加による電子あるいは正孔の注入または引き抜きによるデータ変化すなわちディスターブ問題が発生せず信頼性の高い半導体記憶装置が得られる。

【0029】

本発明の半導体記憶装置は、MONOS型メモリトランジスタのデータ保持特性を向上するためにトンネル酸化膜厚を厚くすると、書き込み方法はホットエレクトロンの注入方式となる。この書き込み方式では、ドレイン近傍に電子電荷が蓄積されるため、データ読み出しをする場合、この電子電荷の影響でメモリ特性がドレイン電圧依存性を持つ。このためPMOS負荷による読み出し回路の電源電圧依存性はPMOSのオン抵抗の変化よりもMONOSメモリトランジスタの依存性の方が大きくなり、電源電圧によりセンスレベルが大きく変化する。したがって、電源電圧変動をなくすために読み出し回路を定電圧発生回路による定電圧により駆動する構成とし、センスレベルの電圧変動を無くし、データ保持時間を向上することができる。

【0030】

本発明の半導体記憶装置は、請求項4記載の回路構成と同様でメモリトランジスタを複数個接続する事が可能で、高集積化が可能であり、上記したデータ保持特性の向上など同様な効果が得られる。

【0031】

本発明の半導体記憶装置の製造方法においては、同一ウェル内にNチャネル型トランジスタとNチャネル型MONOS型メモリトランジスタとを搭載し、工程数を削減することができる。

【0032】

【発明の実施の形態】

以下、図面を用いてこの発明による半導体記憶装置の構造およびその製造方法の最適な形態を詳細に説明する。

【0033】

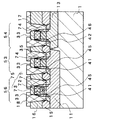

[この発明による半導体記憶装置の第1の実施形態:図1]

この発明による半導体記憶装置の第1の実施形態の構造を、図1の模式的な断面図を用いて説明する。

図1に示す半導体記憶装置は、導電型がN型の半導体基板1の表面の素子分離領域にフィールド酸化膜15を設けている。

【0034】

そして、その半導体基板1には、導電型がP型のPウェル領域11と導電型がN型のNウェル領域13を設けている。

【0035】

その導電型がN型のNウェル領域13の表面には、厚さが13nmのシリコン酸化膜からなるゲート酸化膜74と、多結晶シリコン膜からなるゲート電極33と、高濃度P型拡散層42からなるソース、ドレインと、P型LDD層46とから構成するPチャネル型MOSトランジスタ54を設けている。

【0036】

そして、導電型がP型のPウェル領域11の表面には、厚さが3nmのシリコン酸化膜からなるトンネル酸化膜71を設け、そのトンネル酸化膜71上に設けた厚さ8nmのシリコン窒化膜からなるメモリ窒化膜72と、厚さ3nmのシリコン酸化膜からなるトップ酸化膜73とによってメモリ絶縁膜75を構成し、その上に多結晶シリコンからなるゲート電極33を設け、高濃度N型拡散層41からなるソース、ドレインと、N型LDD層45とから構成するMONOS型メモリトランジスタ56を設けている。

【0037】

このメモリ絶縁膜75の実効酸化膜厚は、シリコン酸化膜の比誘電率3.8とシリコン窒化膜の比誘電率7.0から求めると約10nmである。

【0038】

さらに、MONOS型メモリトランジスタ56を設けた同一のPウェル領域11の表面には、厚さが13nmのシリコン酸化膜からなるゲート酸化膜74と、多結晶シリコンからなるゲート電極33と、高濃度N型拡散層41からなるソース、ドレインと、N型LDD層45とから構成するNチャネル型MOSトランジスタ53を設けている。このNチャネル型MOSトランジスタ53とPチャネル型MOSトランジスタ54は、MONOS型メモリトランジスタ56のメモリセルを構成するMOSトランジスタおよびMONOS型メモリトランジスタ56を制御する周辺回路用MOSトランジスタと同一の構造を用いている。

【0039】

そして、MONOS型メモリトランジスタ56とNチャネル型MOSトランジスタ53間のPウェル領域11にはフィールド酸化膜15を設け、全面に二酸化シリコン膜を主体とする層間絶縁膜16を設け、その層間絶縁膜16に形成された各コンタクトホール17を介して配線18を設けている。

【0040】

これより、同一濃度であるPウェル領域11の表面に、ゲート酸化膜厚が13nmのNチャネル型MOSトランジスタ53と実効酸化膜厚が10nmのMONOS型メモリトランジスタ56を設けているので、ゲート酸化膜厚の薄いほど、同一Pウェル領域11内に設けたトランジスタは、ゲート電界の影響が強くなり、しきい値電圧は低下するため、MONOS型メモリトランジスタ56の初期しきい値電圧をNチャネル型MOSトランジスタ53のしきい値電圧より低く設定している。

【0041】

具体的には、Nチャネル型MOSトランジスタ53のしきい値電圧を0.5Vに設定すると、MONOS型メモリトランジスタ56の初期しきい値電圧は0.3V以下となるようにPウェル領域11の濃度を制御している。

【0042】

これによって、Nチャネル型MOSトランジスタ53とMONOS型メモリトランジスタ56とを構成する高濃度N型拡散層41、N型LDD層45、ゲート電極33とを共通にしており、チップ面積の縮小が可能となる。

【0043】

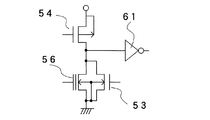

図1を用いて説明した、この発明による半導体記憶装置の構造を使用した回路構成を図2を用いて説明する。

【0044】

図2は、MONOS型メモリトランジスタ56のデータを読み出す回路構成を示している。この読み出し回路は、Pチャネル型MOSトランジスタ54と、Nチャネル型MOSトランジスタ53と、MONOS型メモリトランジスタ56と、出力インバータ61とを備えている。

【0045】

Pチャネル型MOSトランジスタ54のソースは電源電位に接続し、ドレインは並列接続したNチャネル型MOSトランジスタ53とMONOS型メモリトランジスタ56とのドレインに接続し、この出力を出力インバータ61の入力に接続し、Nチャネル型MOSトランジスタ53とMONOS型メモリトランジスタ56のソースは接地電位に接続している。

【0046】

MONOS型メモリトランジスタ56は、チャネル幅4μm、チャネル長0.8μmで構成し、Nチャネル型MOSトランジスタ53は、チャネル幅2μm、チャネル長2μmで構成している。

【0047】

MONOS型メモリトランジスタ56の初期しきい値電圧は、第1の実施形態で説明したように0.3V以下としている。

【0048】

本発明では、読み出し回路の初期データを消去とするようにセンスレベルを0.3Vより高い電圧である0.5V程度になるようにPチャネル型MOSトランジスタ54のチャネル幅、チャネル長を決めており、この場合、チャネル幅2μm、チャネル長20μmとしている。

【0049】

これにより、図2で示す読み出し回路の初期データは出力インバータ61の出力でハイレベル出力となるように設定している。

【0050】

具体的には、読み出しの場合には、電源電圧を1Vとし、Nチャネル型MOSトランジスタ53はオフとし、MONOS型メモリトランジスタ56のゲート端子は1V、Pチャネル型MOSトランジスタ54はオン状態とする。

【0051】

上記のように、初期データはMONOS型メモリトランジスタ56のオン抵抗よりPチャネル型MOSトランジスタ54のオン抵抗を高く設定しているため、出力インバータ61の入力はロウレベルとなり、出力はハイレベルとなる。すなわち消去データとしている。

【0052】

MONOS型メモリトランジスタ56へのデータ書き込みは、Nチャネル型MOSトランジスタ53をオンにし、MONOS型メモリトランジスタ56のゲート端子に9Vの電圧を時間200マイクロ秒間印加し、電子をメモリ絶縁膜中に注入させて行う。

【0053】

書き込み後の待機状態では、Pチャネル型MOSトランジスタ54をオフにし、Nチャネル型MOSトランジスタ53をオンにすることにより、MONOS型メモリトランジスタ56のソース、ドレインが0Vとなり、ドレインディスターブを防ぐことが可能となる。

【0054】

このような簡単な回路構成で、ドレインディスターブを防止でき、さらに、初期データを消去状態に設定しているため、書き込み動作のみのワンタイムROMとしても利用できる。

【0055】

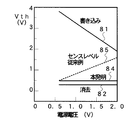

[この発明による半導体記憶装置の第2の実施形態:図3、図4]

この発明による半導体記憶装置の第2の実施形態の回路構成を図3の回路図と図4のグラフを用いて説明する。

【0056】

図3は、図2を用いて説明した第2の実施形態のMONOS型メモリトランジスタ56のデータを読み出す回路と同一のものであり、この読み出し回路の読み出し動作を定電圧発生回路62で作成した定電圧で行う構成としている。この定電圧発生回路62は一般的なカレントミラー型の定電圧回路を用いる。

【0057】

第2の実施形態で説明した方法とは異なる手段でMONOS型メモリトランジスタ56にデータを書き込む場合を以下で説明する。

【0058】

Nチャネル型MOSトランジスタ53はオフ状態にし、Pチャネル型MOSトランジスタ54はオン状態とする。

【0059】

Pチャネル型MOSトランジスタ54のソース端子とMONOS型メモリトランジスタ56のゲート端子とに書き込み電圧である9Vの電圧を時間200マイクロ秒間印加し、ホットエレクトロンをMONOS型メモリトランジスタ56のドレイン近傍のメモリ絶縁膜へ注入し書き込みを行う。

【0060】

この書き込み方法では、MONOS型メモリトランジスタ56のドレイン近傍に電子電荷が蓄積されるため、データ読み出しを行う場合、この電荷の影響でメモリ特性がドレイン電圧依存性を持つ。この相関を図4に示す。

【0061】

図4は、横軸に電源電圧を示し、縦軸にMONOS型メモリトランジスタのしきい値電圧(Vthと示す)を示している。

【0062】

MONOS型メモリトランジスタに電荷注入がない初期しきい値電圧の場合、図4に示すように消去82特性となり、電源電圧依存性はないが、ホットエレクトロン注入により書き込みを行った場合には、書き込み81後のしきい値電圧で示すように、電源電圧が高くなるとしきい値電圧は低くなるという傾向を示す。

【0063】

このしきい値電圧の電源電圧依存性は、ドレイン近傍のメモリ絶縁膜中に局所的に電荷が蓄積されていることが起因している。ドレイン近傍の蓄積電荷がドレイン電圧の影響を受けることにより、MONOS型メモリトランジスタ56のしきい値電圧が図4のグラフのように変わっている。

【0064】

また、第2の実施形態で示したように、センスレベルを決めているPチャネル型MOSトランジスタ54のオン抵抗の電源電圧依存性よりもMONOS型メモリトランジスタ56のオン抵抗の方が電源電圧依存性が大きくなり、図4の破線に示すように電源電圧によりセンスレベル85が大きく変化し、高い電源電圧側でのマージンが低下するためデータ保持特性が悪くなる。

【0065】

このため、図3で説明した電源電圧変動が生じても一定電圧となる定電圧発生回路62により読み出し回路を動作することにより本発明のセンスレベル84の電源電圧変動をなくし、データ保持特性を向上させることができる。

【0066】

[この発明による半導体記憶装置の第3の実施形態:図5]

この発明による半導体記憶装置の第3の実施形態の回路構成を図5の回路図を用いて説明する。

【0067】

図5は、MONOS型メモリトランジスタ56のデータを読み出す回路構成を示している。この読み出し回路は、Pチャネル型MOSトランジスタ54と、Nチャネル型MOSトランジスタ53と、MONOS型メモリトランジスタ56と、出力インバータ61とを備えている。

【0068】

図2と異なる点は、MONOS型メモリトランジスタ56を、複数個のMONOS型メモリトランジスタ56a〜hを直列に接続している点であり、この場合、8個のMONOS型メモリトランジスタ56a〜hを接続し、メモリセルを構成している。

【0069】

この直列に接続した複数個のMONOS型メモリトランジスタ56a〜hとNチャネル型MOSトランジスタ53を並列に接続しているため、待機時に、このNチャネル型MOSトランジスタ53をオンすることにより、複数個のMONOS型メモリトランジスタ56a〜hで構成するメモリセルのMONOS型メモリトランジスタ56aのソースと、MONOS型メモリトランジスタ56hのドレインが同電位にでき、ディスターブを防止するとともに、消去状態のMONOS型メモリトランジスタ56a〜hの微少リーク電流を抑制することができる。

【0070】

[この発明による半導体記憶装置の製造方法の実施形態:図6〜図16と図1]

次に、図1を用いて説明したこの発明による半導体記憶装置を製造する方法を説明する。

図6から図16は、その製造方法の各工程における半導体記憶装置またはその材料を示す模式的な断面図である。これらの各図と完成状態を示す図1とを用いて半導体記憶装置の製造方法の実施形態を説明する。

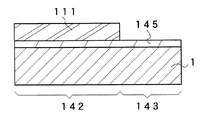

【0071】

まず図6に示すように、導電型がN型の半導体基板1を水蒸気酸化雰囲気中で酸化処理を行い、厚さ550nmの二酸化シリコン膜からなる酸化膜141を全面に形成する。

【0072】

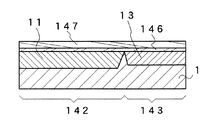

つぎに、その酸化膜141の全面にフォトレジストを形成し、所定のフォトマスクを用いて露光および現像処理を行い、Nチャネル型MOSトランジスタおよびNチャネル型のMONOS型メモリトランジスタを形成する領域であるNチャネル領域142を開口し、Pチャネル型MOSトランジスタを形成するPチャネル領域143を被覆するように、フォトレジスト110をパターン形成する。

【0073】

そして、このフォトレジスト110をエッチングマスクとして、酸化膜141をフッ酸緩衝液によりエッチングし、Nチャネル領域142の酸化膜141を除去する。その後、エッチングマスクとして用いたフォトレジスト110を除去する。

【0074】

つぎに、酸素と窒素との混合気体中で酸化処理を行い、図7に示すように厚さ80nmの二酸化シリコン膜からなる第1のバッファ酸化膜144を形成する。その結果、Pチャネル型MOSトランジスタを形成する領域であるPチャネル領域143は厚い酸化膜である酸化膜141が半導体基板1の表面に形成され、Nチャネル領域142は酸化膜141より薄い酸化膜である第1のバッファ酸化膜144が半導体基板1表面に形成される。

【0075】

その後、P型の不純物であるボロンを加速エネルギー60KeV、イオン注入量3.5×1013atoms/cm2程度でイオン注入する。

このボロンイオン注入は、酸化膜の膜厚が薄いNチャネル領域142の半導体基板1中のみになされる。その後、酸化膜141と第1のバッファ酸化膜144とをフッ酸緩衝液で全面エッチングして除去する。

【0076】

そして、酸素と窒素との混合気体中で酸化処理を行い、図8に示すように、半導体基板1の全面に厚さ40nmの二酸化シリコン膜からなる第2のバッファ酸化膜145を形成する。

その後、全面にフォトレジストを形成し、所定のフォトマスクを用いて露光および現像処理を行い、Pチャネル領域143を開口するように、フォトレジスト111をパターン形成する。

【0077】

そして、このフォトレジスト111をイオン注入マスクとして使用して、導電型がN型の不純物であるリンを加速エネルギーが100KeV、イオン注入量が2.0×1013atoms/cm2程度の条件で、Pチャネル領域143の半導体基板1中にイオン注入する。

その後、フォトレジスト111を除去し、さらに第2のバッファ酸化膜145をフッ酸緩衝液で全面エッチングする。

【0078】

つぎに、この半導体基板1を酸素と窒素との混合気体中で熱処理する。この熱処理により、イオン注入した不純物が活性化され、図9に示すようにNチャネル領域142にはPウェル領域11を、Pチャネル領域143にはNウェル領域13を形成する。

さらに、この熱処理により厚さ20nmの二酸化シリコン膜からなるパッド酸化膜146をこの半導体基板1の全面に形成する。

【0079】

ついで、この図9に示すパッド酸化膜146上の全面に、ジクロルシラン(SiH2Cl2)とアンモニア(NH3)のガスを用いて、温度740℃で化学気相成長法(以下「CVD法」と称す)によって、窒化シリコン膜からなるナイトライド膜147を、膜厚120nm程度に形成する。

【0080】

その後、そのナイトライド膜147の全面に感光性樹脂であるフォトレジストを形成し、所定のフォトマスクを用いて露光および現像処理を行い、図10に示すように、素子領域の周囲のフィールド領域を開口するようにフォトレジスト112を形成する。

【0081】

そして、このフォトレジスト112をエッチングマスクとして使用して、ナイトライド膜147をエッチングする。

このナイトライド膜147のエッチングは、SF6とCHF3とHeとの混合ガスを用いてドライエッチング法により行う。

【0082】

そして、素子領域の周囲のフィールド領域を、ナイトライド膜147の耐酸化膜をマスクにして酸化する、いわゆる選択酸化処理により、図11に示すように、フィールド酸化膜15を700nmの厚さで形成する。

この選択酸化処理は、水蒸気酸化雰囲気中で、温度1000℃で酸化処理することにより行う。

【0083】

つぎに、180℃に加熱した熱燐酸(H3PO4)を用いて、ナイトライド膜147を除去し、さらに、フッ酸緩衝液によりパッド酸化膜146をエッチング除去する。図11はナイトライド膜147とパッド酸化膜146の除去後の状態を示している。

【0084】

その後、酸素と窒素との混合気体中で酸化処理を行い図12に示すように、厚さ40nm程度を有する二酸化シリコン膜からなる犠牲酸化膜76を半導体基板1のNチャネル領域142とPチャネル領域143の全面に形成する。

【0085】

その後、全面にフォトレジストを形成し、所定のフォトマスクを用いて露光および現像処理を行い、MONOS型メモリトランジスタを形成する領域を開口するようにフォトレジスト113をパターン形成する。

【0086】

そして、このフォトレジスト113をエッチングマスクとして、開口部の犠牲酸化膜76をフッ酸緩衝液によりエッチングする。その後、エッチングマスクとして用いたフォトレジスト113を除去する。

【0087】

つぎに、酸素と窒素との混合気体中で酸化処理を行って、図13に示すように、厚さ3nm程度の二酸化シリコンからなるトンネル酸化膜71を、この半導体基板1に形成する。この場合、フィールド酸化膜15または犠牲酸化膜76がすでに形成されている表面は、トンネル酸化膜71の厚さが3nmと薄いために膜厚増加はなく、トンネル酸化膜71は、犠牲酸化膜76を除去したMONOS型メモリトランジスタの形成領域のみに形成される。

【0088】

つぎに、このトンネル酸化膜71上を含む全面にCVD法により、窒化シリコン膜からなるメモリ窒化膜72を10nm程度の厚さで形成する。

このメモリ窒化膜72の形成は、ジクロルシラン(SiH2Cl2)とアンモニア(NH3)との混合ガスを用いて、温度700℃でCVD法によって形成する。

【0089】

さらに、温度950℃、水蒸気酸化雰囲気中で酸化処理を行い、メモリ窒化膜72を酸化して、このメモリ窒化膜72上に膜厚3nmの二酸化シリコン膜からなるトップ酸化膜73を形成する。

この酸化処理により、メモリ窒化膜72の膜厚は8nm程度となる。

【0090】

これにより、MONOS型メモリトランジスタを構成するメモリ絶縁膜75は、厚さ3nmのトンネル酸化膜71と、厚さ8nmのメモリ窒化膜72と、厚さ3nmのトップ酸化膜73とからなり、このメモリ絶縁膜75の実効酸化膜厚は10nmとなる。

【0091】

つぎに、全面にフォトレジストを形成して、所定のフォトマスクを用いて露光および現像処理を行い、メモリ絶縁膜75を形成する領域に、図13に示すようにフォトレジスト114をパターン形成する。

【0092】

そして、このフォトレジスト114をエッチングマスクとして、トップ酸化膜73とメモリ絶縁膜72とトンネル酸化膜71、およびNチャネル型MOSトランジスタとPチャネル型MOSトランジスタの形成領域の犠牲酸化膜76を、CF4とHeとHBr3とO2との混合気体をエッチングガスに用いるドライエッチング法によりエッチングする。

その後、エッチングマスクとして使用したフォトレジスト114を除去する。

【0093】

その後、酸素と窒素との混合気体中で酸化処理を行い、図14に示すように、厚さ13nm程度を有する二酸化シリコン膜からなるゲート酸化膜74を半導体基板1の全面に形成する。

【0094】

このゲート酸化膜74の膜厚は、メモリ絶縁膜75の実効酸化膜10nmより厚い13nmに設定している。これにより、Nチャネル型MOSトランジスタのしきい値電圧は0.5V程度に、MONOS型メモリトランジスタの初期しきい値電圧は0.3V以下にすることができる。

すなわち、同一ウェル領域11の濃度を用いて、酸化膜厚を変えることにより、Nチャネル型MOSトランジスタとMONOS型メモリトランジスタのしきい値電圧をそれぞれ設定している。

【0095】

その後、半導体基板1の全面にモノシラン(SiH4)のガスを用いて、温度600℃でCVD法によって多結晶シリコン膜からなるゲート電極材料34を450nm程度の厚さで形成する。

【0096】

つぎに、このゲート電極材料34の全面にフォトレジストを形成し、所定のフォトマスクを用いて露光および現像を行って、ゲート電極を形成する領域に図14に示すようにフォトレジスト115をパターン形成する。

【0097】

そして、このフォトレジスト115をエッチングマスクとして使用して、ゲート電極材料34をSF6とO2との混合気体をエッチングガスとして用いるドライエッチング法によりエッチングし、図15に示すように、ゲート電極33を形成する。その後、フォトレジストを除去する。

【0098】

さらに、この半導体基板1の全面にフォトレジストを形成し、所定のフォトマスクを用いて露光および現像処理を行い、Nチャネル領域142を開口するようにフォトレジスト116をパターン形成する。

このフォトレジスト116をイオン注入のマスクとして使用して、導電型がN型の不純物であるリンを、加速エネルギー50KeV、イオン注入量が3.0×1013atoms/cm2程度で、Nチャネル領域142のPウェル領域11にイオン注入し、N型LDD層45を形成する。その後、フォトレジスト116を除去する。

【0099】

図示は省略するが、再び半導体基板1の全面にフォトレジストを形成し、所定のフォトマスクを用いて露光および現像処理を行い、Pチャネル領域143を開口するようにフォトレジストを形成する。

このフォトレジストをイオン注入のマスクとして用いて、P型の不純物であるボロンを、加速エネルギー30KeV、イオン注入量3.0×1013atoms/cm2程度でイオン注入し、P型LDD層46を形成する。その後、フォトレジストを除去する。

【0100】

つぎに、全面に二酸化シリコン膜を主体とする絶縁膜を形成する。その後、図16に示すサイドウォール35を形成するために、C2F6とHeとCHF3との混合気体をエッチングガスとして用いるドライエッチング法を用いて全面に形成した絶縁膜をエッチングする。

これにより、ゲート電極33の側壁にサイドウォール35を形成する。

【0101】

さらに、図15で説明したイオン注入と同様に、この半導体基板1の全面にフォトレジストを形成し、所定のフォトマスクを用いて露光および現像処理を行い、Nチャネル領域142を開口するようにフォトレジストをパターン形成する。このフォトレジストをイオン注入のマスクとして使用して、導電型がN型の不純物である砒素を、加速エネルギー60KeV、イオン注入量が3.0×1015atoms/cm2程度で、Nチャネル領域142のPウェル領域11にイオン注入する。その後、フォトレジストを除去する。

【0102】

同様に、半導体基板1の全面にフォトレジストを形成し、所定のフォトマスクを用いて露光および現像処理を行い、Pチャネル領域143を開口するようにフォトレジストを形成する。

このフォトレジストをイオン注入のマスクとして用いて、P型の不純物であるボロンを、加速エネルギー40KeV、イオン注入量3.0×1015atoms/cm2程度でイオン注入する。その後、フォトレジストを除去する。

【0103】

つぎに、全面に二酸化シリコン膜を主体とする層間絶縁膜16を形成する。

その後、イオン注入した不純物の活性化と層間絶縁膜16のリフローを兼ねて、窒素雰囲気中で、温度900℃の熱処理を行う。

【0104】

その結果、Nチャネル型MOSトランジスタ53およびMONOS型メモリトランジスタ56に高濃度N型拡散層41からなるソースとドレインおよびN型LDD層45と、Pチャネル型MOSトランジスタ54の高濃度P型拡散層42からなるソースとドレインおよびP型LDD層46とを形成できる。

【0105】

ついで、図示は省略するが、層間絶縁膜16上にコンタクトホール17を開口するためのフォトレジストをパターン形成する。そして、そのフォトレジストをエッチングマスクにして層間絶縁膜16をエッチングして、図16に示すように、各トランジスタのゲート電極、ソース、ドレインに対応する位置にコンタクトホール17を設ける。

【0106】

このコンタクトホール17を形成するためのエッチングは、C2F6とHeとCHF3との混合気体をエッチングガスとして用いるドライエッチング法により行う。その後、フォトレジストを除去する。

【0107】

つぎに、アルミニウムを主体とする配線材料を、層間絶縁膜16の全面に設け、その配線材料上に配線を形成するためのフォトレジストをパターン形成する。そして、そのフォトレジストをマスクに使用して配線材料をエッチングし、図1に示した各配線18を設ける。

【0108】

この配線材料のエッチングは、BCl3とCHCl3とCl2とN2との混合気体をエッチングガスとして用いるドライエッチング法により行う。

これにより、図1に示した本発明の半導体記憶装置が完成する。

【0109】

[この発明の作用効果に係る説明]

ここで、この発明による半導体記憶装置の作用効果を図17に示すデータ保持特性を示す特性図を用いて説明する。

このデータ保持特性を示す特性図は、従来例を破線86,87で表し、この発明によるデータ保持特性を実線81,83で表し、比較して示してある。

【0110】

図1で説明した、この発明による半導体記憶装置では、MONOS型メモリトランジスタの初期しきい値電圧をNチャネル型MOSトランジスタと同一のPウェル領域に形成し、かつ、MONOS型メモリトランジスタを構成するメモリ絶縁膜の実効酸化膜厚をNチャネル型MOSトランジスタのゲート酸化膜厚より薄く設計しているため、図17に示すようにMONOS型メモリトランジスタの初期しきい値電圧83を0.3V以下とすることができる。

【0111】

さらに、図2で示した読み出し回路で初期しきい値電圧状態でのデータを消去状態とするようにPチャネル型MOSトランジスタのON抵抗を設定しているため、図17に示すセンスレベルの電圧(0.5V)でMONOS型メモリトランジスタのデータが書き込み状態か消去状態かを決定している。

【0112】

したがって、従来例で示すように、消去87側のデータが電子注入状態である書き込み86側より早くセンスレベルに達する場合には、消去87側の特性によりデータ保持特性が決まることになる。

【0113】

さらに、従来例で示したようにMONOS型メモリトランジスタのウェル濃度を周辺MOSと変えて形成した場合には、それぞれの製造ばらつきがしきい値電圧に影響を与え、センスレベルに達する時間特性が必ずしも消去87側、書き込み86側のどちらか一方の特性にならず、製造ばらつきを反映し、データ保持特性がばらつく結果となる。

【0114】

また、この発明では、MONOS型メモリトランジスタを周辺MOSトランジスタと同一ウェル領域内に形成し、ソース、ドレイン領域も同一構造としているため、製造ばらつきを小さく抑えることが可能としている。

さらに、MONOS型メモリトランジスタのしきい値電圧をMOSトランジスタとの実効酸化膜厚差で制御しているため、センスレベル84をMONOS型メモリトランジスタの初期しきい値電圧83より高い電圧に設定すれば、図17に示すようにデータ保持特性は書き込み81側のみで決めることができ、信頼性を高めることができる。

【0115】

さらに、トンネル酸化膜を3.2〜4.5nmと厚くし、消去できないデバイス構造とした場合にも初期しきい値電圧は消去83状態に設定しているため、1回のみ書き込みが可能である信頼性の高いワンタイムROMとしても利用できる。

【0116】

ここで、この発明による半導体記憶装置の他の作用効果を、図4の特性図を用いて説明する。

図4は、前記したように、横軸に電源電圧、縦軸にMONOS型メモリトランジスタのしきい値電圧(Vth)を示したグラフである。

【0117】

MONOS型メモリトランジスタを電子のホットエレクトロン注入による書き込みを行った場合の書き込み81側のしきい値電圧は、ドレイン側に局所的に注入された電荷の影響で、図4に示すように電源電圧依存性を持ち、電源電圧が高いほどしきい値電圧が低下する傾向を示す。

【0118】

したがって、従来例で示した読み出し回路のセンスレベルでは、電源電圧依存性がPチャネル型MOSトランジスタのオン抵抗変化よりも、上記MONOS型メモリトランジスタのオン抵抗変化が大きく影響し、図4に示すようにセンスレベル85は電源電圧に依存し、電源電圧の上昇にともない上昇するため、データ保持特性を考慮した特性では、高電源電圧側でのマージンが低下する。

【0119】

このため、この発明では、定電圧発生回路62で発生した定電圧で動作させることにより、図4に示すように本発明84のセンスレベルを一定とすることができ、しかも、1V程度の低電圧での読み出しが可能であり、かつ、データ保持特性を向上することができる。

【0120】

【発明の効果】

以上説明してきたように、本発明の半導体記憶装置において、同一Pウェル領域内にNチャネル型MOSトランジスタとNチャネル型のMONOS型メモリトランジスタとを形成し、このNチャネル型MOSトランジスタを構成するゲート酸化膜とMONOS型メモリトランジスタを構成するメモリ絶縁膜との各膜厚を制御することにより、MONOS型メモリトランジスタの初期しきい値電圧をNチャネル型MOSトランジスタのしきい値電圧より低くしている。さらに、周辺回路を構成するNチャネル型MOSトランジスタとPチャネル型MOSトランジスタとは同一しきい値電圧に設定している。このため、Nチャネル型MONOS型メモリトランジスタ専用のPウェル領域形成は必要でなく、従来に比べ製造プロセスが簡単である半導体記憶装置を提供することができる。

【0121】

本発明によれば、MONOS型メモリトランジスタの初期データを消去状態となるように、Pチャネル型MOSトランジスタの負荷抵抗(オン抵抗)を制御しているため、テスティングでの消去動作が不要となり、テスト工程を簡略化することができる。

【0122】

さらに、本発明によれば、トンネル酸化膜厚を厚く設定しているため、消去できないワンタイムROMとして使用でき、データ保持特性を書き込み側のみで決めることができ、データ保持特性のばらつきを抑え、高信頼性の半導体記憶装置を提供することができる。

【0123】

さらに、本発明によれば、MONOS型メモリトランジスタのデータ読み出しを行わない待機時には、MONOS型メモリトランジスタと並列に接続したNチャネル型MOSトランジスタをオン状態とし、MONOS型メモリトランジスタのソース、ドレイン両端子を同一電位としているため、ドレインディスターブを完全に抑制することができる。さらに、MONOS型メモリトランジスタが消去データ時のメモリセルのリーク電流を抑制することができる。

【0124】

さらに、本発明によれば、上記、リーク電流およびドレインディスターブを抑制したMONOS型メモリトランジスタの高集積化が可能である。

【0125】

本発明によれば、センスレベルの電源電圧依存性がなくなり、電源電圧変動によるデータ保持特性の変化を防止でき、1V程度の低電圧での読み出しが可能であり、かつ、安定したデータ保持特性が得られ高信頼性を備えた半導体記憶装置が提供できる。

【図面の簡単な説明】

【図1】本発明の実施形態における半導体記憶装置の構造を示す断面図である。

【図2】本発明の実施形態における半導体記憶装置の構成を示す回路図である。

【図3】本発明の実施形態における半導体記憶装置の構成を示す回路図である。

【図4】本発明の実施形態と従来例における半導体記憶装置の電源電圧としきい値電圧との相関を示した特性図である。

【図5】本発明の実施形態における半導体記憶装置の構成を示す回路図である。

【図6】本発明の実施形態における半導体記憶装置の製造方法を示す断面図である。

【図7】本発明の実施形態における半導体記憶装置の製造方法を示す断面図である。

【図8】本発明の実施形態における半導体記憶装置の製造方法を示す断面図である。

【図9】本発明の実施形態における半導体記憶装置の製造方法を示す断面図である。

【図10】本発明の実施形態における半導体記憶装置の製造方法を示す断面図である。

【図11】本発明の実施形態における半導体記憶装置の製造方法を示す断面図である。

【図12】本発明の実施形態における半導体記憶装置の製造方法を示す断面図である。

【図13】本発明の実施形態における半導体記憶装置の製造方法を示す断面図である。

【図14】本発明の実施形態における半導体記憶装置の製造方法を示す断面図である。

【図15】本発明の実施形態における半導体記憶装置の製造方法を示す断面図である。

【図16】本発明の実施形態における半導体記憶装置の製造方法を示す断面図である。

【図17】本発明の実施形態と従来例における半導体記憶装置のデータ保持特性を示した特性図である。

【図18】従来例における半導体記憶装置の構造を示す断面図である。

【図19】従来例における半導体記憶装置の構造を示す断面図である。

【図20】従来例における半導体記憶装置の構造を示す断面図である。

【図21】従来例における半導体記憶装置の構成を示す回路図である。

【符号の説明】

1 半導体基板

11 第1のPウェル領域

12 第2のPウェル領域

13 Nウェル領域

14 チャネルドープ層

15 フィールド酸化膜

16 層間絶縁膜

17 コンタクトホール

18 配線

21 第1の酸化膜

22 第2の酸化膜

31 浮遊ゲート

32 制御ゲート

33 ゲート電極

34 ゲート電極材料

35 サイドウォール

41 高濃度N型拡散層

42 高濃度P型拡散層

43 ドレイン

44 ソース

45 N型LDD層

46 P型LDD層

51 メモリトランジスタ

53 Nチャネル型MOSトランジスタ

54 Pチャネル型MOSトランジスタ

55 周辺回路

56 MONOS型メモリトランジスタ

61 出力インバータ

71 トンネル酸化膜

72 メモリ窒化膜

73 トップ酸化膜

74 ゲート酸化膜

75 メモリ絶縁膜

76 犠牲酸化膜

Claims (2)

- ソースを電源電位に接続するPチャネル型MOSトランジスタと、該Pチャネル型MOSトランジスタのドレインと接地電位との間に直列接続する少なくとも1つのMONOS型メモリトランジスタと、該MONOS型メモリトランジスタと並列接続するNチャネル型MOSトランジスタと、を有し、

前記MONOS型メモリトランジスタおよび前記Nチャネル型MOSトランジスタと前記Pチャネル型MOSトランジスタとの接続点を出力とし、該出力を出力インバータの入力に接続することを特徴とする半導体記憶装置。 - 前記Pチャネル型MOSトランジスタのソースに定電圧発生回路を接続することを特徴とする請求項1に記載の半導体記憶装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002066727A JP4224243B2 (ja) | 2002-03-12 | 2002-03-12 | 半導体記憶装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002066727A JP4224243B2 (ja) | 2002-03-12 | 2002-03-12 | 半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003273251A JP2003273251A (ja) | 2003-09-26 |

| JP2003273251A5 JP2003273251A5 (ja) | 2005-09-02 |

| JP4224243B2 true JP4224243B2 (ja) | 2009-02-12 |

Family

ID=29198382

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002066727A Expired - Lifetime JP4224243B2 (ja) | 2002-03-12 | 2002-03-12 | 半導体記憶装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4224243B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100475541B1 (ko) * | 2003-03-28 | 2005-03-10 | 주식회사 하이닉스반도체 | 낸드 플래시 메모리 테스트 구조 및 이를 이용한 낸드플래시 메모리 채널 전압 측정 방법 |

| JP2006032797A (ja) * | 2004-07-20 | 2006-02-02 | Matsushita Electric Ind Co Ltd | 不揮発性半導体記憶装置及びその製造方法 |

| JP2008166518A (ja) * | 2006-12-28 | 2008-07-17 | Toshiba Corp | 不揮発性半導体記憶装置 |

| CN114023754B (zh) * | 2022-01-10 | 2022-03-29 | 广州粤芯半导体技术有限公司 | 非易失性闪存存储器及其擦除方法 |

-

2002

- 2002-03-12 JP JP2002066727A patent/JP4224243B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003273251A (ja) | 2003-09-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7011999B2 (en) | Method of manufacturing an integrated circuit device including forming an oxidation resistant film over an isolation region and subsequently forming a gate insulating film of a misfet | |

| KR100219331B1 (ko) | 비휘발성 반도체 메모리 디바이스 및 이의 소거 및 생산방법 | |

| JP4463954B2 (ja) | セルアレー領域内にバルクバイアスコンタクト構造を備える不揮発性メモリ素子 | |

| KR20040093404A (ko) | 반도체장치 및 그 제조방법 | |

| US6429073B1 (en) | Methods for manufacturing semiconductor devices having a non-volatile memory transistor | |

| USRE37959E1 (en) | Semiconductor integrated circuit device and method of manufacturing the same | |

| US5604150A (en) | Channel-stop process for use with thick-field isolation regions in triple-well structures | |

| EP0160003B1 (en) | Mos floating gate memory cell and process for fabricating same | |

| KR100214813B1 (ko) | 반도체 장치,마스크 롬 및 그의 제조방법 | |

| US8344440B2 (en) | Three-terminal single poly NMOS non-volatile memory cell with shorter program/erase times | |

| JP4252637B2 (ja) | 不輝発性メモリ装置の製造方法 | |

| US6717204B1 (en) | Semiconductor devices having a non-volatile memory transistor | |

| JP4224243B2 (ja) | 半導体記憶装置 | |

| JPH02177561A (ja) | 半導体不揮発性メモリ | |

| JPH11191616A (ja) | 不揮発性半導体メモリ装置の改善されたウェル構造及びその製造方法 | |

| JP2018029136A (ja) | 不揮発性記憶素子およびそれを備えるアナログ回路 | |

| US6522587B1 (en) | Non-volatile semiconductor memory devices | |

| JPH10289957A (ja) | 半導体装置およびその製造方法 | |

| US6756629B1 (en) | Semiconductor devices including a multi-well and split-gate non-volatile memory transistor structure | |

| JP2001044392A (ja) | 半導体記憶装置及びその製造方法 | |

| JPH0831539B2 (ja) | 不揮発性メモリの製造方法 | |

| JPH02295169A (ja) | 不揮発性半導体記憶装置 | |

| JP3216615B2 (ja) | 半導体装置の製造方法 | |

| JP4227036B2 (ja) | 半導体装置 | |

| KR0161396B1 (ko) | 비휘발성 반도체 메모리 장치의 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050307 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050307 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070907 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080610 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080723 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20080723 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080909 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081028 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20081118 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20081121 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4224243 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111128 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111128 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131128 Year of fee payment: 5 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |