JP4149634B2 - 分周回路 - Google Patents

分周回路 Download PDFInfo

- Publication number

- JP4149634B2 JP4149634B2 JP2000112792A JP2000112792A JP4149634B2 JP 4149634 B2 JP4149634 B2 JP 4149634B2 JP 2000112792 A JP2000112792 A JP 2000112792A JP 2000112792 A JP2000112792 A JP 2000112792A JP 4149634 B2 JP4149634 B2 JP 4149634B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- signal

- flip

- dff

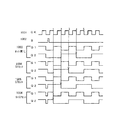

- timing chart

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000010355 oscillation Effects 0.000 claims description 11

- 230000001360 synchronised effect Effects 0.000 claims description 6

- 238000010586 diagram Methods 0.000 description 11

- 230000000630 rising effect Effects 0.000 description 7

- 239000013078 crystal Substances 0.000 description 6

- 238000005259 measurement Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 3

- 230000009471 action Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 239000013589 supplement Substances 0.000 description 1

Images

Landscapes

- Electric Clocks (AREA)

- Manipulation Of Pulses (AREA)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000112792A JP4149634B2 (ja) | 2000-04-14 | 2000-04-14 | 分周回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000112792A JP4149634B2 (ja) | 2000-04-14 | 2000-04-14 | 分周回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001298358A JP2001298358A (ja) | 2001-10-26 |

| JP2001298358A5 JP2001298358A5 (enExample) | 2007-04-05 |

| JP4149634B2 true JP4149634B2 (ja) | 2008-09-10 |

Family

ID=18624888

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000112792A Expired - Fee Related JP4149634B2 (ja) | 2000-04-14 | 2000-04-14 | 分周回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4149634B2 (enExample) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8355478B1 (en) * | 2009-05-29 | 2013-01-15 | Honeywell International Inc. | Circuit for aligning clock to parallel data |

| JP2024061521A (ja) | 2022-10-21 | 2024-05-07 | キオクシア株式会社 | 判定装置、試験システムおよび生成装置 |

-

2000

- 2000-04-14 JP JP2000112792A patent/JP4149634B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001298358A (ja) | 2001-10-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TW490932B (en) | Frequency multiplication circuit | |

| JPS6161283B2 (enExample) | ||

| GB1570659A (en) | Electronic timepiece | |

| US5606293A (en) | Clock generator for microcomputer having reduced start-up time | |

| JP4149634B2 (ja) | 分周回路 | |

| JP3523362B2 (ja) | クロック回路及びこれを用いたプロセッサ | |

| JPS60804B2 (ja) | 電子時計 | |

| US4241435A (en) | Electronic timepiece oscillator circuit | |

| US7387433B2 (en) | Integrated circuit chip for analogue electronic watch applications | |

| US20020063591A1 (en) | Divider with cycle time correction | |

| JP3130592B2 (ja) | 二相クロック発生回路 | |

| JPS6143274Y2 (enExample) | ||

| JP3332940B2 (ja) | 電圧制御発振回路 | |

| JPH0983356A (ja) | クロック発生回路 | |

| JP2622853B2 (ja) | 2逓倍回路 | |

| JPH067383Y2 (ja) | クロック発生回路 | |

| JPH09214307A (ja) | クロック回路 | |

| JP2002181971A (ja) | リアルタイムクロック | |

| JP2525138B2 (ja) | 書込み補償回路 | |

| JPH06152390A (ja) | 半導体集積回路 | |

| JPH0651860A (ja) | 発振安定時間保証回路 | |

| JPH0719012Y2 (ja) | 電圧検出回路 | |

| KR0167226B1 (ko) | 우수/기수 판별회로 | |

| JP2636313B2 (ja) | クロック発生回路 | |

| JPH03201707A (ja) | 水晶発振回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070215 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070215 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071225 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080311 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080509 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20080509 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080624 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080626 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110704 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |