JP4133350B2 - 半導体装置とその製造方法 - Google Patents

半導体装置とその製造方法 Download PDFInfo

- Publication number

- JP4133350B2 JP4133350B2 JP2003003414A JP2003003414A JP4133350B2 JP 4133350 B2 JP4133350 B2 JP 4133350B2 JP 2003003414 A JP2003003414 A JP 2003003414A JP 2003003414 A JP2003003414 A JP 2003003414A JP 4133350 B2 JP4133350 B2 JP 4133350B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- semiconductor

- trench

- semiconductor device

- type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Electrodes Of Semiconductors (AREA)

Description

【発明の属する技術分野】

本発明は、半導体装置とその製造方法に関する。

【0002】

【従来の技術】

特許文献1には、図15に示すように、n−型ドリフト領域928とp型ボディ領域930の間にn型領域929が形成された絶縁ゲート型バイポーラトランジスタ(以下「IGBT」という)が示されている。このn型領域929は、n−型ドリフト領域928よりも不純物濃度が高い。

【0003】

上記IGBTがオンすると、p+型コレクタ領域924からn+型バッファ領域926を経由して、n−型ドリフト領域928にホールが流入する。このホールは、上記n型領域929によってp型ボディ領域930への移動が抑制される。この結果、n−型ドリフト領域928と上記n型領域929の境界近傍のn−型ドリフト領域928にホールが蓄積される。これにより、n−型ドリフト領域928のキャリア分布がn+型エミッタ領域932に近い側で少なくならず、従来のIGBTに比較してオン電圧を低減できる旨が特許文献1に記載されている。

【0004】

【特許文献1】

特開平8−316479号公報(その公報の図16参照)

【0005】

【発明が解決しようとする課題】

本発明は、半導体装置のオン電圧を低減できる新規な技術を提供することを課題とする。

【0006】

【課題を解決するための手段及び作用と効果】

本発明の1つの態様のバイポーラで動作する縦型の半導体装置は、表面にトレンチが形成された半導体部と、トレンチの壁面に沿って形成されたゲート絶縁膜と、トレンチ内に形成されたゲート電極を備えている。半導体部は、第1導電型の第1半導体領域と、第2導電型の第2半導体領域と、第1導電型の第3半導体領域と、第2導電型の第4半導体領域を備えている。第1半導体領域は、半導体部の裏面に形成されているとともに、一方の主電極に電気的に接続する。第2半導体領域は、第1半導体領域上に形成されている。第3半導体領域は、第2半導体領域上に形成されており、トレンチの側面に接しているとともに他方の主電極に電気的に接続する。第4半導体領域は、第3半導体領域上に形成されており、トレンチの側面に接しているとともに他方の主電極に電気的に接続する。半導体部はさらに、トレンチの底面の一部が半導体部の表面側に窪んでいる窪み内に位置する領域(以下では「窪み内領域」という)を備えている。

この態様のように、半導体部が上記窪み内領域を有する場合、オン時にはその窪み内領域にキャリアを溜めることができる。よって、オン時に半導体部に存在するキャリアを増加させることができる。このため、半導体装置のオン電圧を低減できる。

【0007】

【発明の実施の形態】

本発明の好ましい態様や、他の態様等を以下に示す。

本発明は、オン時に第1導電型キャリアと第2導電型キャリアが流れるバイポーラ型半導体装置に適用することが好ましい。この態様によると、オン電圧を効果的に低減できる。この中でも、半導体部が、第1導電型の第1半導体領域と、第2導電型の第2半導体領域と、第1導電型の第3半導体領域と、第2導電型の第4半導体領域を有することが好ましい。第3半導体領域は、トレンチに隣合っていることが好ましい。別の表現をすると、第3半導体領域は、ゲート絶縁膜を介してゲート電極に隣合っていることが好ましい。そして、オン時には、第1導電型キャリアが第1半導体領域、第2半導体領域、第3半導体領域の順に流れることが好ましい。また、オン時には、第2導電型キャリアが第4半導体領域、第3半導体領域、第2半導体領域、第1半導体領域の順に流れることが好ましい。上記構造のバイポーラ型半導体装置としては、絶縁ゲート型バイポーラトランジスタ(IGBT)や、MOSゲート型サイリスタ等が挙げられる。

【0008】

上記構造の場合は、窪み内領域に第1導電型キャリアを溜めることができる。上記構造の場合、窪み内領域は第2導電型領域を有することが好ましい。このように、窪み内領域は、溜められるキャリアと逆導電型の領域を有することが好ましい。この第2導電型領域の不純物濃度は、上記した第2導電型の第2半導体領域の不純物濃度よりも高いことが好ましい。窪み内領域の不純物濃度は、1×1014〜1×1016cm−3であることが好ましい。これらの態様によると、窪み内領域にキャリアをより溜め易くすることができる。

【0009】

トレンチ底面は、トレンチ側に孔状に窪んでいることが好ましい。あるいは、トレンチ底面は、トレンチ側に段差状に窪んでいてもよい。

窪み内領域は、トレンチ下方に位置する半導体部からトレンチ側に(1)盛り上がっていてもよいし、(2)突出していてもよい。窪み内領域は、凸状に形成されていてもよい。窪み内領域は、直方体状や曲面体状等に形成されていてもよい。

【0010】

窪み内領域は、1つのトレンチに対して複数形成されていることが好ましい。この態様によると、窪み内領域にキャリアをより溜め易くすることができる。複数の窪み内領域の形状や大きさは等しくてもよいし、異なっていてもよい。

窪み内領域の高さは、トレンチの深さの1/10以上であることが好ましく、トレンチの深さの1/5以上であることがより好ましい。窪み内領域の高さは、トレンチの深さの3/4以下であることが好ましい。この態様によると、窪み内領域にキャリアがより溜まり易い。

【0011】

他の態様の半導体装置は、「トレンチの底面に沿ったゲート絶縁膜」がトレンチ側に窪んでおり、半導体部は、前記窪み内に位置する領域を有する。他の態様の半導体装置は、「トレンチ下方に位置する半導体部」がトレンチ側に(1)盛り上がっている、又は(2)突出している。他の態様の半導体装置は、「トレンチの底部」又は「トレンチ底面に隣接する半導体部」が凹凸形状となっている。好ましくは、奥行方向に沿って凹凸形状となっていることがよい。奥行方向に沿っていると、凹凸形状を形成し易い。

【0012】

他の態様の半導体装置の製造方法は、半導体部のトレンチ形成予定領域上に犠牲層を形成する工程と、犠牲層と半導体部をエッチングして半導体部にトレンチを形成する工程を有する。さらに、トレンチの壁面に沿ってゲート絶縁膜を形成する工程や、トレンチ内にゲート電極を形成する工程を有していてもよい。前記犠牲層を形成する工程は、半導体部のトレンチ形成予定領域の一部上に犠牲層を形成する工程であることが好ましい。この場合、トレンチを形成する工程では、犠牲層と、犠牲層が形成されていないトレンチ形成予定領域の半導体部をエッチングし、犠牲層が除去された後にもトレンチ形成予定領域の半導体部をさらにエッチングする。あるいは、前記犠牲層を形成する工程は、半導体部のトレンチ形成予定領域上に所定のエッチャント(エッチング液、エッチングガスの両方を含む)に対するエッチング速度が異なる複数種の犠牲層を形成する工程であることが好ましい。この場合、トレンチを形成する工程では、犠牲層をエッチングし、犠牲層が除去された後にもトレンチ形成予定領域の半導体部をさらにエッチングして半導体部にトレンチを形成する。これらの態様によると、底面が窪んだトレンチを1回のエッチングで形成できる。

【0013】

他の態様の半導体装置の製造方法は、半導体部の一部上に第1マスクを形成する工程と、第1マスクで覆われた半導体部を第1エッチングする工程と、第1エッチングにより露出した半導体部の一部上に第2マスクを形成する工程と、第1マスクと第2マスクで覆われた半導体部を第2エッチングする工程を有する。この態様によっても、底面が窪んだトレンチを形成できる。

【0014】

【実施例】

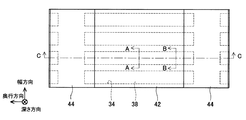

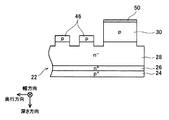

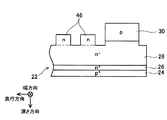

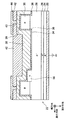

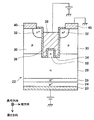

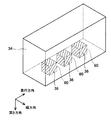

図1は、第1実施例の半導体装置の平面図の一部を示す。図2は、図1のA−A線断面図を示す。図3は、図1のB−B線断面図を示す。図4は、図1のC−C線断面図を示す。図4を参照するとわかるように、図3はトレンチ34の底が深い部分での断面図である。図4はトレンチ34の底が浅い部分での断面図である。なお、本明細書では、図1の縦方向を「幅方向」、横方向を「奥行方向」、紙面垂直方向を「深さ方向」という。

【0015】

図1に示すように、この半導体装置は、奥行方向に沿ってストライプ状に伸びるトレンチ34が幅方向に複数形成されている。図1のA−A線断面図である図2に示すように、この半導体装置は、半導体部22を備えている。半導体部22は、半導体装置を絶縁ゲート型バイポーラトランジスタ(以下「IGBT」という)として機能させるための構造を有する。具体的には、半導体部22は、p+型コレクタ領域24と、これに接するn+型バッファ領域26と、これに接するn−型ドリフト領域28と、これに接するp型ボディ領域30と、これに接するn+型エミッタ領域32等を有する。半導体部22には、上記各領域24,26,28,30,32が奥行方向に連続して形成されている。

【0016】

なお、トレンチ34のパターンは図1に示すような各トレンチ34が別個に区切られたストライプ状に限定されず、様々なパターンを採用できる。例えば、各トレンチ34がつながっているパターン(トレンチ34がチェック状や網の目状のパターン等)であってもよい。

【0017】

図2に示すように、トレンチ34は、半導体部22に形成されている。トレンチ34の壁面に沿ってゲート絶縁膜36が形成されている。トレンチ34内にはゲート電極38が形成されている。図1のC−C線断面図である図4に示すように、ゲート電極38は、トレンチ34外に位置するゲート引出し部39につながっている(連続的に形成されている)。ゲート電極38やゲート引出し部39はポリシリコンや、金属等の導電体によって形成すればよい。図4に示すように、ゲート電極38上には、層間絶縁膜42が形成されている。層間絶縁膜42には、コンタクトホール43が形成されている。層間絶縁膜42上には、ゲート配線層44が形成されている。ゲート配線層44は、アルミニウムや銅等の金属等の導電体によって形成すればよい。ゲート配線層44の一部はコンタクトホール43に入り込んでいる。コンタクトホール43内のゲート配線層44の底面はゲート引出し部39に接している。これにより、ゲート配線層44と、ゲート引出し部39及びゲート電極38は電気的に接続されている。

【0018】

図2に示すように、p+型コレクタ領域24の底面には、コレクタ電極20が接している。n+型エミッタ領域32とp型ボディ領域30(詳細にはボディコンタクト領域)の頂面には、エミッタ電極40が接している。

【0019】

図4に示すように、トレンチ34の底面は、トレンチ34側に孔状に窪んでいる。トレンチ34の底面には、この窪みが複数形成されている。半導体部22は、その窪み内に位置する領域(窪み内領域)46を有する。窪み内領域46は、複数形成されている。各窪み内領域46はn型領域となっている。各窪み内領域46は、n−型ドリフト領域28の不純物濃度よりも高い。本実施例では、窪み内領域46の不純物濃度は、約1×1015cm−3である。本実施例では、窪み内領域46の高さは、トレンチ34の深さの約1/4〜1/3となっている。各窪み内領域46は、トレンチ34の幅方向(図4の紙面垂直方向)に沿って伸びている。各窪み内領域46は、トレンチ34の奥行方向に沿って間欠的に形成されている。各窪み内領域46の頂面と2つの側面は、ゲート絶縁膜36によって覆われている。これら2つの側面は、トレンチ34の幅方向に伸びている。

【0020】

第1実施例の半導体装置の動作を説明する。図2に示すように、エミッタ電極40を接地した状態でゲート電極38とコレクタ電極20に正電圧を印加する。これにより、IGBTをオンさせる。すると、ゲート電極38にゲート絶縁膜36を介して隣合うp型ボディ領域30にn型チャネルが形成される。この結果、エレクトロンがn+型エミッタ領域32から、n型チャネル、n−型ドリフト領域28、n+型バッファ領域26を通ってp+型コレクタ領域24に流入する。また、ホールがp+型コレクタ領域24から、n+型バッファ領域26、n−型ドリフト領域28を通って、p型ボディ領域30(p型ボディコンタクト領域)に流入する。

【0021】

第1実施例の半導体装置では、図4に示すように、トレンチ34の底面がトレンチ34側に窪んでいる。半導体部22は、その窪み内に位置する領域(窪み内領域)46を有する。この窪み内領域46の側面と頂面はゲート絶縁膜36によって覆われている。よって、この窪み内領域46に流れ込んだホールは、ゲート絶縁膜36の壁によってこの窪み内領域46外への移動が抑制される。このため、半導体部22を流れるホールは、この窪み内領域46に溜められる。この窪み内領域46に溜められたホールの存在が、図2に示すn+型エミッタ領域32からのエレクトロンの流入を促進する働きをする。この結果、n−型ドリフト領域28でのホールとエレクトロンによる伝導度変調現象を活発化させることができる。このため、オン電圧を低減できる。

【0022】

図15に示す従来の半導体装置では、p型ボディ領域930の底面とn−型ドリフト領域928の頂面の間全体にn型領域929を介在させている。この構造の場合、n−型ドリフト領域928とn型領域929の境界付近にホールが蓄積されると、p+型コレクタ領域924、n型領域群926,928,929、p型ボディ領域930、n+型エミッタ領域932で構成されるpnpn構造の寄生サイリスタがオンし易い(ラッチアップし易い)という問題があった。

これに対し、第1実施例の半導体装置では、図2に示すように、p型ボディ領域30の底面とn−型ドリフト領域28の頂面の間にはn型領域が設けられていない。第1実施例の半導体装置は、図4に示すトレンチ34の底面の窪み内に位置する窪み内領域46にホールを溜めるものである。よって、図15に示す従来の半導体装置とは異なり、寄生サイリスタがオンしにくい。

【0023】

第1実施例の半導体装置の構造は、チップの中でもチップ周辺部に設けることが好ましい。チップ周辺部は熱が溜まりにくいので、寄生サイリスタがよりオンしにくくなる。但し、チップ中央部を含むチップ全体に設けても勿論よい

【0024】

また、図15に示す従来の半導体装置では、p型ボディ領域930の底面とn−型ドリフト領域928の頂面の間全体にn型領域929を介在させている。即ち、p型ボディ領域930とn型領域929が直接に接している。このn型領域929はn−型ドリフト領域928よりも不純物濃度が高い。よって、このようなn型領域929が存在せず、p型ボディ領域30の底面とn−型ドリフト領域28の頂面が直接に接している構造に比べて空乏層が伸びにくい。このため、耐圧が低下するという問題があった。

これに対し、第1実施例の半導体装置では、図2に示すように、p型ボディ領域30の底面とn−型ドリフト領域28の頂面が直接に接している。よって、n−型ドリフト領域28側に空乏層が伸びやすい。このため、高耐圧を保持できる。

【0025】

また、図3に示すようにトレンチ34の底が浅い部分では、トレンチ34の底面は、p型ボディ領域30の底面よりも浅い位置にある。この構造によると、トレンチ34の底面がp型ボディ領域30の底面よりも深い位置にある場合に比べて、ゲート絶縁膜36へのコレクタ電圧の影響を小さくできる。特に、相対的に絶縁破壊が生じ易いトレンチ34の下側コーナー部に位置するゲート絶縁膜36a(図3参照)へのコレクタ電圧の影響を小さくできる。よって、ゲート絶縁膜36の絶縁破壊を生じにくくすることができる。このため、耐圧を上昇させることができる。

また、第1実施例の半導体装置によると、図3に示すn型の窪み内領域46とp型ボディ領域30の接合部からも空乏層を伸ばすことができる。よって、耐圧をより上昇させることができる。

【0026】

次に、第1実施例の半導体装置の第1製造方法について説明する。まず、図5に示すような半導体部22を形成する。半導体部22の形成方法としては種々の方法があり、公知の方法を採用できる。例えば、p型半導体基板24上に、n+型エピタキシャル層26、n−型エピタキシャル層28を順に成長させ、p型領域30をイオン注入によって作製する方法が挙げられる。次に、半導体部22のうち、トレンチ34を形成しない領域上にマスク50を形成する。また、半導体部22のうち、浅いトレンチを形成する領域上に厚さL1〔μm〕の犠牲層51を形成する。

【0027】

所定のエッチャントは、半導体部22(例えばシリコン)をエッチング可能である。このエッチャントは、マスク50はほとんとエッチングしない。このエッチャントは、犠牲層51をエッチング可能である。本実施例では、所定のエッチャントによる半導体部22のエッチング速度V2と犠牲層51のエッチング速度V1の比(エッチング選択比)V2/V1がL2/L1となるように各材料(エッチャント、半導体部22、犠牲層51)が選択されている。この場合、犠牲層51が例えばL1〔μm〕エッチングされると、半導体部22がL2〔μm〕エッチングされる。

【0028】

エッチャントとして例えば、HBrとNF3とO2を所定の混合比で混合したエッチングガスを用いると、シリコンとシリコン酸化膜のエッチング選択比をL2/L1に調整できる。エッチャントとして、SF6とO2を所定の混合比で混合したエッチングガスを用いる場合も同様である。また、これらのエッチングガスは、窒化膜(SiN)はほとんどエッチングしない。よって、これらのエッチングガスを用いる場合、半導体部22をシリコンで形成し、マスク50を窒化膜で形成し、犠牲層51をシリコン酸化膜で形成するとよい。なお、マスク50は酸窒化膜で形成してもよい。エッチャント、マスク50、犠牲層51として他の材料を用いることができるのは勿論である。また、半導体部22のうち、深いトレンチを形成する領域上には何も形成しない。即ち、半導体部22のうち、深いトレンチを形成する領域は露出させておく。

【0029】

次に、RIE(Reactive Ion Etching)等によってエッチングを行う。すると、図6に示すように、厚さL1〔μm〕の犠牲層51がエッチングされる間に、半導体部22はL2〔μm〕エッチングされる。この状態では、犠牲層51が除去されるため、半導体部22のうち犠牲層51の下方に位置する領域が露出する。この状態から、さらにエッチングを継続する。すると、マスク50で覆われていない部分の半導体部22がさらに除去される。

これにより、半導体部22には、図7に示すように、底面が窪んだトレンチ34が形成される。本実施例の場合、底の深い部分と浅い部分を有するトレンチ34が形成される。トレンチ34の下方に位置する半導体部22は、その窪み内に位置する領域(窪み内領域)46を有する。この窪み内領域46のうち上部と中間部はp型領域となっている。窪み内領域46のうち下部はn型領域となっている。

【0030】

次に、この窪み内領域46に、n型不純物をイオン注入する。すると、図8に示すように、この窪み内領域46の上部と中間部もn型領域となる。即ち、窪み内領域46全体がn型領域となる。

【0031】

次に、半導体部(シリコン)22の表面を例えば熱酸化法によって酸化する。これにより、図4に示すように、半導体部22の表面に沿って絶縁膜(シリコン酸化膜)36が形成される。次に、表面に絶縁膜36が形成された半導体部22上に、電極層38,39を積層する。次に、この電極層38,39をエッチングによって所定の形状にパターニングする。これにより、ゲート電極38とゲート引出し部39が形成される。次に、ゲート電極38とゲート引出し部39上に層間絶縁膜42を形成する。次に、ゲート引出し部39上の層間絶縁膜42にコンタクトホール43を形成する。次に、層間絶縁膜42上にゲート配線層44を積層する。次に、このゲート配線層44をエッチングによって所定の形状にパターニングする。次に、熱処理(アニール処理)を行う。これにより、ゲート配線層44とゲート引出し部39のコンタクト性を向上できる。また、半導体部22にイオン注入した不純物を活性化できる。

以上の工程を経て、第1実施例の半導体装置が製造される。

【0032】

図15に示す従来の半導体装置では、p型ボディ領域930よりも深い位置にn型領域929を形成する必要があった。このようなn型領域929を形成するためには、半導体部の頂面から深い位置へのイオン注入等を行う必要があった。このため、n型領域929を形成するのに手間がかかるという問題があった。

これに対し、第1実施例の半導体装置の場合、トレンチ34を形成した後、そのトレンチ34の底面から浅い位置にイオン注入することで、n型の窪み内領域46を形成できる(図8参照)。このため、n型の窪み内領域46を形成するのは、図15のn型領域929を形成するのに比べて少ない手間で済む。

【0033】

また、第1実施例では、窪み内領域46にn型不純物をイオン注入している。しかし、窪み内領域46には、n型不純物をイオン注入しない態様も可能である。即ち、窪み内領域46がp型であっても、窪み内領域46にホールを溜める効果が得られる。この場合、窪み内領域46にn型不純物をイオン注入する手間が省ける。よって、図15のn型領域929を形成する場合に比べて、より製造工程を簡単化できる。

【0034】

次に、第1実施例の半導体装置の第2製造方法について説明する。なお、第1製造方法と共通する部分については説明を省略する。

第2製造方法では、図9に示すように、半導体部22のうち、トレンチを形成しない領域上に第1マスク52を形成する。次に、図10に示すように、第1マスク52で覆われていない半導体部22をRIE等によって所定深さまでエッチングする。これにより、浅いトレンチをまず形成する。次に、その浅いトレンチ底面に隣接する半導体部22のうち、深いトレンチを形成しない領域上に第2マスク53を形成する。次に、図11に示すように、第1マスク52と第2マスク53で覆われていない半導体部22をRIE等によって所定深さまでエッチングする。なお、第1マスク52と第2マスク53は、エッチングの際に使用するエッチャントに対してほとんどエッチングされない材料を用いることが好ましい。これにより、半導体部22には、第1製造方法の場合と同様に、底面が窪んだトレンチ34が形成される。

【0035】

図12は、第2実施例の半導体装置について図1のC−C線断面図に対応する図を示す。第2実施例においても、トレンチ34の底面は、トレンチ34側に窪んでいる。第2実施例の場合、トレンチ34の底面は段差状に窪んでいる。半導体部22は、その窪み内に位置する領域(窪み内領域)56を有する。窪み内領域56の頂面と1つの側面は、ゲート絶縁膜36によって覆われている。この側面は、トレンチ34の幅方向に伸びている。

【0036】

第2実施例によっても、オン時にはこの窪み内領域56にホールを溜めることができる。よって、オン電圧を低減できる。

【0037】

図13は、第3実施例の半導体装置について図1のA−A線断面図に対応する図を示す。第3実施例においても、トレンチ34の底面は、トレンチ34側に窪んでいる。半導体部22は、その窪み内に位置する領域(窪み内領域)58を有する。この窪み内領域58は、トレンチ34の奥行方向(図13の紙面垂直方向)に沿って伸びている。この窪み内領域58の頂面と2つの側面は、ゲート絶縁膜36によって覆われている。これら2つの側面は、トレンチ34の奥行方向に伸びている

【0038】

第3実施例によっても、オン時にはこの窪み内領域58にホールを溜めることができる。よって、オン電圧を低減できる。

【0039】

図14は、第4実施例の半導体装置のトレンチ34付近の模式図を示す。第4実施例においても、トレンチ34の底面は、トレンチ34側に窪んでいる。半導体部22は、その窪み内に位置する領域(窪み内領域)60を複数有する。各窪み内領域60は、頂面と全ての側面(4つの側面)がゲート絶縁膜36で覆われている。なお、図14では、ゲート絶縁膜36を模式的に斜線によって示している。

【0040】

第4実施例では、窪み内領域60は、頂面と全ての側面がゲート絶縁膜36で覆われている。よって、オン時には窪み内領域60にホールをより溜め易くすることができる。このため、オン抵抗をより低減し得る。

【0041】

以上、本発明の具体例を詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

【図面の簡単な説明】

【図1】第1実施例の半導体装置の平面図の一部を示す。

【図2】図1のA−A線断面図を示す。

【図3】図1のB−B線断面図を示す。

【図4】図1のC−C線断面図を示す。

【図5】第1実施例の半導体装置の第1製造方法の説明図を示す(1)。

【図6】第1実施例の半導体装置の第1製造方法の説明図を示す(2)。

【図7】第1実施例の半導体装置の第1製造方法の説明図を示す(3)。

【図8】第1実施例の半導体装置の第1製造方法の説明図を示す(4)。

【図9】第1実施例の半導体装置の第2製造方法の説明図を示す(1)。

【図10】第1実施例の半導体装置の第2製造方法の説明図を示す(2)。

【図11】第1実施例の半導体装置の第2製造方法の説明図を示す(3)。

【図12】第2実施例の半導体装置について図1のC−C線断面図に対応する図を示す。

【図13】第3実施例の半導体装置について図1のA−A線断面図に対応する図を示す。

【図14】第4実施例の半導体装置のトレンチ付近の模式図を示す。

【図15】従来の半導体装置の断面図を示す。

【符号の説明】

20:コレクタ電極

22:半導体部

24:p+型コレクタ領域

26:n+型バッファ領域

28:n−型ドリフト領域

30:p型ボディ領域

32:n+型エミッタ領域

34:トレンチ

36:ゲート絶縁膜

38:ゲート電極

39:ゲート引出し部

40:エミッタ電極

42:層間絶縁膜

44:ゲート配線層

46:窪み内領域

Claims (5)

- バイポーラで動作する縦型の半導体装置であって、

表面にトレンチが形成された半導体部と、トレンチの壁面に沿って形成されたゲート絶縁膜と、トレンチ内に形成されたゲート電極を備え、

前記半導体部は、

裏面に形成されているとともに、一方の主電極に電気的に接続する第1導電型の第1半導体領域と、

その第1半導体領域上に形成されている第2導電型の第2半導体領域と、

その第2半導体領域上に形成されており、前記トレンチの側面に接しているとともに他方の主電極に電気的に接続する第1導電型の第3半導体領域と、

その第3半導体領域上に形成されており、前記トレンチの側面に接しているとともに前記他方の主電極に電気的に接続する第2導電型の第4半導体領域と、

前記トレンチの底面の一部が前記半導体部の表面側に窪んでおり、その窪み内に位置する領域と、を有する半導体装置。 - 前記半導体部は、1つのトレンチについて前記窪み内に位置する領域を複数有する請求項1に記載の半導体装置。

- 前記窪み内に位置する領域は、第2導電型領域を有する請求項1又は2に記載の半導体装置。

- 請求項1に記載の半導体装置を製造する方法であり、

半導体部のトレンチ形成予定領域上の一部に犠牲層を形成する工程と、

前記犠牲層と前記犠牲層が形成されていないトレンチ形成予定領域の前記半導体部をエッチングし、前記犠牲層が除去された後にも前記トレンチ形成予定領域の半導体部をさらにエッチングして半導体部にトレンチを形成する工程を有する半導体装置の製造方法。 - 請求項1に記載の半導体装置を製造する方法であり、

半導体部のトレンチ形成予定領域上に、エッチャントに対するエッチング速度が異なる複数種の犠牲層を形成する工程と、

前記犠牲層をエッチングし、前記犠牲層が除去された後にも前記トレンチ形成予定領域の半導体部をさらにエッチングして半導体部にトレンチを形成する工程を有する半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003003414A JP4133350B2 (ja) | 2003-01-09 | 2003-01-09 | 半導体装置とその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003003414A JP4133350B2 (ja) | 2003-01-09 | 2003-01-09 | 半導体装置とその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004221126A JP2004221126A (ja) | 2004-08-05 |

| JP4133350B2 true JP4133350B2 (ja) | 2008-08-13 |

Family

ID=32894689

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003003414A Expired - Fee Related JP4133350B2 (ja) | 2003-01-09 | 2003-01-09 | 半導体装置とその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4133350B2 (ja) |

-

2003

- 2003-01-09 JP JP2003003414A patent/JP4133350B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004221126A (ja) | 2004-08-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7279770B2 (ja) | 半導体装置 | |

| JP4414863B2 (ja) | 絶縁ゲート型半導体装置およびその製造方法 | |

| CN110914996B (zh) | 半导体器件 | |

| JP2019021931A (ja) | 逆導通型絶縁ゲートバイポーラトランジスタの製造方法および逆導通型絶縁ゲートバイポーラトランジスタ | |

| CN107180855B (zh) | 半导体装置 | |

| JP5569600B2 (ja) | 半導体装置およびその製造方法 | |

| JP2010147477A (ja) | シリコンウェハ上にパワートランジスタデバイスを製造する方法 | |

| JP2018019045A (ja) | 炭化珪素半導体装置および炭化珪素半導体装置の製造方法 | |

| JP4456013B2 (ja) | 半導体装置 | |

| JP2010153864A (ja) | 半導体ダイ上に製造されるパワートランジスタデバイス | |

| JP2012059841A (ja) | 半導体装置 | |

| JP2008034794A (ja) | 縦型トレンチ型絶縁ゲートmos半導体装置 | |

| JP2001168327A (ja) | 半導体装置とそれを用いたパワースイッチング駆動システム | |

| JP4940535B2 (ja) | 半導体装置 | |

| CN106997899B (zh) | 一种igbt器件及其制备方法 | |

| CN108574000A (zh) | 半导体装置和半导体装置的制造方法 | |

| JP2010147475A (ja) | 半導体ダイ上に製造されるパワートランジスタデバイス | |

| CN103295907A (zh) | 半导体装置及其制造方法 | |

| CN102163623B (zh) | 半导体元件及半导体元件的制造方法 | |

| JP2012174989A (ja) | 半導体装置の製造方法 | |

| JP2023099104A (ja) | 半導体装置 | |

| JP2012089824A (ja) | 半導体素子およびその製造方法 | |

| CN117397042A (zh) | 半导体装置 | |

| JP2019021891A (ja) | 半導体装置 | |

| US11264475B2 (en) | Semiconductor device having a gate electrode formed in a trench structure |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050726 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080130 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080205 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080402 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080507 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080602 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110606 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120606 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120606 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130606 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |