JP4090906B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP4090906B2 JP4090906B2 JP2003034014A JP2003034014A JP4090906B2 JP 4090906 B2 JP4090906 B2 JP 4090906B2 JP 2003034014 A JP2003034014 A JP 2003034014A JP 2003034014 A JP2003034014 A JP 2003034014A JP 4090906 B2 JP4090906 B2 JP 4090906B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor chip

- circuit board

- electrode terminal

- terminal portion

- connection

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

- H01L2224/48465—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond the other connecting portion not on the bonding area being a wedge bond, i.e. ball-to-wedge, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8319—Arrangement of the layer connectors prior to mounting

- H01L2224/83191—Arrangement of the layer connectors prior to mounting wherein the layer connectors are disposed only on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/921—Connecting a surface with connectors of different types

- H01L2224/9212—Sequential connecting processes

- H01L2224/92122—Sequential connecting processes the first connecting process involving a bump connector

- H01L2224/92125—Sequential connecting processes the first connecting process involving a bump connector the second connecting process involving a layer connector

Description

【発明の属する技術分野】

本発明は、半導体装置及びその製造方法に関するものであり、より詳しくは、素子形成面の中央部に電極を有する半導体チップと、回路基板とを、フリップチップ実装方式により接続する半導体装置及びその製造方法に関するものである。

【0002】

【従来の技術】

近年、携帯電話等の携帯情報機器の小型化、軽量化の進展にはめざましいものがある。それに伴い、これらの機器に搭載される半導体装置をはじめ、あらゆる部品の小型化、軽量化が求められている。そのようななか、半導体装置においては、半導体チップの実装構造の小型化、回路基板への高密度実装が求められている。

【0003】

そこで、このような要求に応えるべく、近年、半導体のベアチップを回路基板に直接実装するフリップチップ実装方式を用いた実装(以下、単にフリップチップ実装もしくはフリップチップ実装方法と記す)が実施されている。

【0004】

上記フリップチップ実装方法としては、半導体チップに設けられた導電性の突起電極(バンプ)を、該突起電極に対応して回路基板に設けられた接続パッドに圧接させた状態で、上記半導体チップと回路基板との間隙を、異方導電性樹脂(Anisotropic Conductive Film or Paste)や絶縁性樹脂(Non Conductive Film or Paste)などの液状またはフィルム状の界面封止樹脂にて封止する方法が一般的に用いられている。このように界面封止樹脂を用いた半導体チップと回路基板との接合は、上記半導体チップと回路基板とを位置合わせした状態で加熱加圧ツールにより上記半導体チップが搭載された回路基板を一定時間保持することで、両者の接続部が保持できる程度に上記異方導電性樹脂を硬化させることにより行われる。

【0005】

これに対し、近年、圧接ではなく、突起電極(バンプ)の変形を伴う金属接合を用いたフリップチップ実装方法として、超音波を用いたフリップチップ実装(以下、超音波接合と記す)が注目され始めている。該方法においては、半導体チップの電極パッドに設けられた突起電極(バンプ)を回路基板上に設けられた接続パッドに接触させ、超音波による振動を用いて上記突起電極を押圧して変形させることにより、両者の接合を行っている。このため、該方法は、上記圧接による接合方法と比較して短時間で金属接合が可能であり、生産性向上及び信頼性向上の可能性を有している。

【0006】

しかしながら、何れの場合においても、例えばダイナミックラムと称されるDRAM(Dynamic Random Access Memory)等のように、素子形成面の中央部に複数の電極パッドが直鎖状に配列された、いわゆるセンターパッドを有する半導体チップを用いてフリップチップ実装を行う場合、上記電極パッド上に形成される突起電極(バンプ)を支点として半導体チップが傾き易いという問題がある。このため、そのままでは、半導体チップのフリップチップ実装を行う際に上記半導体チップの素子(能動素子)形成面と回路基板とが実質的に平行な間隔を保持した状態で両者を固定することは困難である。このため、このようにして得られた半導体装置は、半導体チップと回路基板との接続の安定性が悪く、接続不良や信頼性の低下を引き起こす可能性がある。

【0007】

これに対し、例えば特許文献1には、界面封止樹脂を用いたフリップチップ実装において上記問題点を解決するための方法として、図9に示すように、レジスト層などの絶縁性の支持部材76を、回路基板72の四隅に、半導体チップ71のチップサイズよりも該支持部材76で囲まれた領域(開口部)の面積が小さくなるように設け、該支持部材76で上記半導体チップ71の周辺部を支えることで、半導体チップ71と回路基板72とを実質平行に支持し、半導体チップ71の電極パッド74(センターパッド)上に形成された突起電極78と、回路基板72上に設けられた接続パッド73とを、界面封止樹脂として異方導電性樹脂79(Anisotropic Conductive Film or Paste)を用いて接合する方法が開示されている。

【0008】

【特許文献1】

特開2000−332055号公報(2000年11月30日公開)

【0009】

【発明が解決しようとする課題】

しかしながら、超音波などを用いて突起電極を変形させることにより金属接合を行うフリップチップ実装において、上述したようにいわゆるセンターパッドを有する半導体チップの実装を行う場合の問題点を解決する方法は未だ知られていない。

【0010】

そこで、本願発明者等は、上記特許文献1におけるフリップチップ実装方法に、突起電極を変形させることにより金属接合を行うフリップチップ実装方法として上記超音波接合を適用することで、上記した問題点を解決することを試みた。

【0011】

図10(a)〜(c)は上記超音波接合を前記特許文献1に記載のフリップチップ実装方法を用いた半導体装置の製造方法に適用したときの半導体装置の製造工程を工程順に示す断面図である。

【0012】

まず、図10(a)に示すように、回路基板72における、レジスト層などの絶縁性の支持部材76を含む半導体装置実装対象となる領域に、界面封止樹脂としての異方導電性樹脂79をコートする。

【0013】

次いで、上記回路基板72における接続パッド73と、半導体チップ71の電極パッド74(センターパッド)に設けられた突起電極78とを位置合わせし、図10(b)に示すように超音波印加ツール7を用いて上記半導体チップ71に、加熱状態にて超音波を印加して所定の荷重を加える。これにより、図10(c)に示すように突起電極78を塑性変形させて、上記半導体チップ71が上記支持部材76によって支持された状態で、上記半導体チップ71と回路基板72とを接合する。

【0014】

このように、超音波接合を特許文献1におけるフリップチップ実装方法に適用した場合、短時間で上記半導体チップ71と回路基板72とを金属接合することが可能になる。

【0015】

しかしながら、上記したように突起電極78を変形させて上記半導体チップ71と回路基板72とを接合させるためには、図10(b)に示すように、半導体チップ71に形成された突起電極78の高さは、レジスト層などの絶縁性の支持部材76よりも、上記突起電極78の変形分だけ必ず高くなければならない。

【0016】

従って、超音波接合を特許文献1におけるフリップチップ実装方法に適用した場合、上記半導体チップ71の中央部に形成された上記突起電極78に超音波などを加えて該突起電極78を変形させるとき、上記半導体チップ71を、上記回路基板72に対して実質的に平行に支持するものがないので、上記半導体チップ71に超音波を印加して所定の荷重を加えたときの半導体チップ71の挙動が不安定になり、図10(c)に示すように突起電極78と接続パッド73とが位置ずれを起こし、接続不良や接続信頼性の低下を招く可能性がある。

【0017】

このため、超音波接合のように電極の塑性変形を伴うフリップチップ接合において上記した問題点の解決が望まれる。

【0018】

また、上記特許文献1は、上述したように回路基板72の四隅に設けられた、レジスト層などの絶縁性部材からなる支持部材76により、上記半導体チップ71の周辺部を支持しているが、このようにレジスト層などの絶縁性部材により上記支持部材76を形成する場合、フリップチップ実装時に上記半導体チップ71を押圧するときに、上述したように接続位置の横方向のズレが大きいことは勿論として、縦方向、即ち、電気的な接続の信頼性に関わる高さ方向のばらつきも大きいため、実使用上、問題がある。

【0019】

つまり、上記回路基板72側に設けられるレジスト層などの絶縁性部材は、一般的にはソルダレジストと称され、回路基板72の強度確保や、上記回路基板72における金属配線の絶縁などのためには必要なものである。ところが、このソルダレジストは、厚みの制御が容易ではなく、材料に起因する厚さのばらつきが比較的大きいという問題点を有している。また、エッチング加工により厚みを制御する場合における制御性においても同様のことが言える。

【0020】

このため、上記特許文献1に記載のように上記支持部材76としてソルダレジストを用いた場合、超音波接合を行うか否かに拘らず、回路基板72毎に、支持部材76の厚みがばらつくので、各回路基板72毎に適切なバンプ高さ、つまり上記突起電極78の高さを設定する必要がある。また、支持部材76を精度良く形成しようとすると、回路基板72の製造工程が増加し、コストアップにつながる。

【0021】

本発明は、上記の問題点に鑑みてなされたものであり、その目的は、中央部に、センターパッドと称される電極パッドを有する半導体チップを回路基板にフリップチップ実装するに際し、半導体チップの素子形成面と回路基板とを実質的に平行に支持した状態で、安定して固定することができ、半導体チップと回路基板との接続不良や接続信頼性の低下を防止することができる半導体装置及びその製造方法を提供することにある。

【0022】

【課題を解決するための手段】

本発明にかかる半導体装置は、上記の課題を解決するために、素子形成面の中央部に電極端子部(例えばセンターパッドと称される電極パッド)が設けられた半導体チップが、上記電極端子部にて、回路基板の接続用電極端子部(例えば接続パッド)に架設状態でフリップチップ実装されており、上記回路基板は、上記半導体チップよりも大きく、かつ、表面に絶縁体層(例えばソルダレジスト)が設けられている半導体装置において、上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部が突起状に形成されており、上記回路基板表面の絶縁体層は、上記半導体チップの素子(例えば能動素子)形成面よりも大きな開口部(例えばソルダレジスト開口部)を備え、該開口部内で上記半導体チップと回路基板とが架設状態でフリップチップ実装されており、上記半導体チップと回路基板との間隙には、突起状に形成された上記電極端子部とほぼ同じ高さを有し、上記半導体チップと回路基板とを実質平行に支持する支持体が設けられていることを特徴としている。

【0023】

上記の構成によれば、従来のように、回路基板上に配されるソルダレジストと称される絶縁体層を、フリップチップ実装時に上記半導体チップを支持する支持部材(支持体)として使用しないので、ソルダレジストを上記支持部材として用いた場合における従来の問題点を招来しない。

【0024】

特に、上記の構成によれば、上記絶縁体層が、上記半導体チップの素子形成面よりも大きな開口部を有し、上記絶縁体層と半導体チップとが互いに非接触状態にて上記半導体チップが上記接続用電極端子部にフリップチップ実装されるので、上記支持体並びに突起形状を有する電極端子部の形成に際し、上記絶縁体層による制限を受けず、しかも、上記絶縁体層とは別に上記支持体が設けられていることから、該支持体の形成に際し、材料の選択の自由度が大きく、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより厳密に制御することが可能となるので、上記したように中央部にセンターパッドと称される電極端子部を有する半導体チップを回路基板にフリップチップ実装するに際し、半導体チップの素子形成面と回路基板とを実質的に平行に支持した状態で、安定して固定することができる。

【0025】

よって、上記の構成によれば、半導体チップの素子形成面と回路基板とが実質的に平行に支持された状態で、しかも、上記半導体チップの電極端子部と上記接続用電極端子部とが、横方向に位置ズレすることなくフリップチップ実装されるので、半導体チップと回路基板との接続不良が防止され、接続信頼性が高い半導体装置を提供することができる。

【0026】

しかも、上記の構成によれば、本発明は、超音波接合などの、電極端子部の塑性変形を伴う接合を行う場合にも好適に適用できるので、塑性変形によって強固に接続され、半導体チップと回路基板との位置ズレがなく、接続不良が防止され、接続信頼性が高い半導体装置を提供することができる。

【0027】

本発明にかかる半導体装置は、上記の課題を解決するために、上記支持体は、突起状に形成された電極端子部と同じ材料からなることを特徴としている。

【0028】

上記の構成によれば、上記支持体が、突起状に形成された電極端子部と同じ材料からなることで、既存の技術により、両者の高さを容易に一致させることができる。このため、より一層接続信頼性が高い半導体装置を提供することができる。

【0029】

しかも、上記の構成によれば、超音波接合などの、電極端子部の塑性変形を伴う接合を行う場合、該塑性変形による、上記支持体と、突起状に形成された電極端子部との変形量を容易に一致させることができるので、上記半導体チップと回路基板とを平行に支持した状態で接合することが可能となる。よって、上記の構成によれば、塑性変形によって強固に接続され、半導体チップと回路基板との位置ズレがなく、接続不良が防止され、接続信頼性がより高い半導体装置を提供することができる。

【0030】

本発明にかかる半導体装置は、上記の課題を解決するために、上記支持体は金属からなることを特徴としている。

【0031】

金属材料は、その厚さをエッチング加工する技術が特に充実しており、厚みの制御を容易に行うことができる。このため、上記支持体が金属からなる場合、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより一層厳密かつ容易に制御することが可能となるので、上記支持体の高さを、突起状に形成された電極端子部の高さと容易に合わせることができる。このため、より接続信頼性が高い半導体装置を提供することができる。

【0032】

本発明にかかる半導体装置は、上記の課題を解決するために、上記半導体チップと回路基板とが、突起状に形成された上記電極端子部及び上記支持体の塑性変形により接合されていることを特徴としている。

【0033】

上記の構成によれば、上述したように、超音波接合などの、電極端子部の塑性変形を伴う接合を行う場合であっても上記半導体チップのフリップチップ実装を行う際に、上記半導体チップを上記回路基板と平行に支持することができるので、塑性変形によって強固に接続され、半導体チップと回路基板との位置ズレがなく、接続不良が防止され、接続信頼性が高い半導体装置を提供することができる。

【0034】

なお、従来は、超音波接合などの、電極端子部の塑性変形を伴う接合を行う場合に、半導体チップと回路基板とを平行に支持した状態でフリップチップ接続を行う技術は知られておらず、回路基板上に設けられたソルダレジストと称される絶縁体層を、半導体チップを支持する支持部材として用いる技術を、電極端子部の塑性変形を伴う接合に適用した場合、突起電極は必ず半導体チップ側に形成する必要があり、しかも、該突起電極の高さは、該突起電極の変形分、上記絶縁体層からなる支持部材よりも高くする必要がある。このため、従来は、半導体チップと回路基板とを平行に支持した状態でフリップチップ接続を行うことはできなかった。

【0035】

しかしながら、本発明によれば、上記したように、塑性変形によって強固に接続され、半導体チップと回路基板との位置ズレがなく、接続不良が防止され、接続信頼性が高い半導体装置を提供することができる。

【0036】

本発明にかかる半導体装置は、上記の課題を解決するために、上記半導体チップと回路基板とが、該半導体チップと回路基板との間隙を封止する界面封止樹脂(例えば異方導電性樹脂や絶縁性樹脂など)によりさらに固着されていることを特徴としている。

【0037】

上記の構成によれば、上記半導体チップと回路基板とを、より強固に安定して接合することができる。例えば、上記半導体チップと回路基板との接合が超音波接合によりなされる場合、上記半導体チップの電極端子部と回路基板の接続用電極端子部との溶着(接合)は、一般的に、中心部ではなく、その周辺にドーナツ状に生じる。このため、上記半導体チップと回路基板との間隙を上記界面封止樹脂によりさらに固着することで、両者の接合をより強固で安定したものとすることができる。

【0038】

本発明にかかる半導体装置は、上記の課題を解決するために、上記接続用電極端子部と半導体チップの電極端子部とが架設状態で圧接されており、上記半導体チップと回路基板とが、該半導体チップと回路基板との間隙を封止する界面封止樹脂により固着されていることを特徴としている。

【0039】

上記の構成によれば、従来のように、回路基板上に配されるソルダレジストと称される絶縁体層を、フリップチップ実装時に上記半導体チップを支持する支持部材(支持体)として使用しないので、上記のように半導体チップの電極端子部と接続用電極端子部とを圧接させて電気的に接続すると共に上記半導体チップと回路基板とを界面封止樹脂により固着させる場合においても、半導体チップと回路基板とソルダレジストを上記支持部材として用いた場合における従来の問題点を招来しない。

【0040】

特に、上記の構成によれば、上記絶縁体層が、上記半導体チップの素子形成面よりも大きな開口部を有し、上記絶縁体層と半導体チップとが互いに非接触状態にて上記半導体チップが上記接続用電極端子部にフリップチップ実装されるので、半導体チップを支持するための支持部材並びに上記電極端子部(突起電極)の形成に際し、上記絶縁体層による制限を受けず、しかも、上記絶縁体層とは別に上記支持体が設けられていることから、該支持体の形成に際し、材料の選択の自由度が大きく、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより厳密に制御することが可能となる。

【0041】

このため、上記の構成によれば、上記したように中央部にセンターパッドと称される電極端子部を有する半導体チップを回路基板にフリップチップ実装するに際し、半導体チップの素子形成面と回路基板とを実質的に平行に支持した状態で、安定して固定することができ、半導体チップと回路基板との接続不良が防止され、接続信頼性が高い半導体装置を提供することができる。

【0042】

本発明にかかる半導体装置は、上記の課題を解決するために、上記支持体と半導体チップとの接触面積が、突起状に形成された上記電極端子部と半導体チップとの接触面積よりも大きいことを特徴としている。

【0043】

上記の構成によれば、上記支持体と半導体チップとの接触面積を、突起状に形成された上記電極端子部と半導体チップとの接触面積よりも大きくすることで、上記支持体が上記半導体チップの素子形成面に当たることによるダメージを軽減することができる。

【0044】

本発明にかかる半導体装置は、上記の課題を解決するために、上記半導体チップの素子形成面とは反対側の面に少なくとも1つの半導体チップが積層され、該積層された半導体チップの電極端子部と、上記回路基板における上記絶縁体層の開口部内でかつ上記半導体チップのフリップチップ実装領域外に設けられた接続用電極端子部とが金属細線により電気的に接続されていることを特徴としている。

【0045】

上記の構成によれば、上記半導体装置1個当たり、言い換えれば、上記回路基板上の上記半導体チップ実装領域の面積当たりの、該半導体チップの搭載数が増加し、上記半導体チップの実装密度がより高い半導体装置を実現することができる。

【0046】

本発明にかかる半導体装置の製造方法は、上記の課題を解決するために、素子(例えば能動素子)形成面の中央部に電極端子部(例えばセンターパッドと称される電極パッド)が設けられた半導体チップを、上記電極端子部にて、上記半導体チップよりも大きく、かつ、表面に絶縁体層(例えばソルダレジスト)が設けられた回路基板における接続用電極端子部(例えば接続パッド)に架設状態でフリップチップ実装する半導体装置の製造方法において、上記回路基板表面に、該回路基板における上記半導体チップのフリップチップ実装対象領域に上記半導体チップの素子形成面よりも大きな開口部(例えばソルダレジスト開口部)を有する絶縁体層を形成し、上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部を突起状に形成すると共に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、突起状に形成された上記電極端子部とほぼ同じ高さを有し、上記半導体チップと回路基板とを実質平行に支持する支持体を形成し、突起状に形成された上記電極端子部と支持体とによって、上記回路基板における上記絶縁体層の開口部内で上記半導体チップと回路基板とを実質平行に支持してフリップチップ実装を行うことを特徴としている。

【0047】

上記の方法によれば、従来のように、回路基板上に配されるソルダレジストと称される絶縁体層を、フリップチップ実装時に上記半導体チップを支持する支持部材(支持体)として使用しないので、ソルダレジストを上記支持部材として用いた場合における従来の問題点を招来しない。

【0048】

特に、上記の方法によれば、上記絶縁体層が、上記半導体チップの素子形成面よりも大きな開口部を有することで、上記絶縁体層と半導体チップとを互いに非接触状態にて上記半導体チップを上記接続用電極端子部にフリップチップ実装することができるので、上記支持体並びに突起形状を有する電極端子部の形成に際し、上記絶縁体層による制限を受けず、しかも、上記絶縁体層とは別に上記支持体を設けることで、該支持体の形成に際し、材料の選択の自由度が大きく、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより厳密に制御することが可能となるので、上記したように中央部にセンターパッドと称される電極端子部を有する半導体チップを回路基板にフリップチップ実装するに際し、半導体チップの素子形成面と回路基板とを実質的に平行に支持した状態で、安定して固定することができる。

【0049】

よって、上記の方法によれば、半導体チップの素子形成面と回路基板とが実質的に平行に支持された状態で、しかも、上記半導体チップの電極端子部と上記接続用電極端子部とが、横方向に位置ズレすることなくフリップチップ実装することができるので、半導体チップと回路基板との接続不良を防止することができ、接続信頼性が高い半導体装置を製造することができる。

【0050】

しかも、上記の方法によれば、本発明は、超音波接合などの、電極端子部の塑性変形を伴う接合を行う場合にも好適に適用できるので、上記の方法を用いれば、塑性変形によって強固に接続され、半導体チップと回路基板との位置ズレがなく、接続不良が防止され、接続信頼性が高い半導体装置を製造することができる。

【0051】

本発明にかかる半導体装置の製造方法は、上記の課題を解決するために、素子(例えば能動素子)形成面の中央部に電極端子部(例えばセンターパッドと称される電極パッド)が設けられた半導体チップを、上記電極端子部にて、上記半導体チップよりも大きく、かつ、表面に絶縁体層(例えばソルダレジスト)が設けられた回路基板における接続用電極端子部(例えば接続パッド)に架設状態でフリップチップ実装する半導体装置の製造方法において、上記回路基板表面に、該回路基板における上記半導体チップのフリップチップ実装対象領域に上記半導体チップの素子形成面よりも大きな開口部(例えばソルダレジスト開口部)を有する絶縁体層を形成し、上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部を突起状に形成すると共に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、突起状に形成された上記電極端子部とほぼ同じ高さを有し、かつ、少なくとも最表層が上記半導体チップのフリップチップ実装による上記接続用電極端子部との接合条件で塑性変形すると共に、該塑性変形による変形量が、突起状に形成された上記電極端子部とほぼ同じ材料からなり、上記半導体チップと回路基板とを実質平行に支持する支持体を形成し、突起状に形成された上記電極端子部と支持体とによって、上記回路基板における上記絶縁体層の開口部内で上記半導体チップと回路基板とを架設状態で実質平行に支持し、突起状に形成された上記電極端子部及び上記支持体を塑性変形させて上記半導体チップと回路基板とを接合することを特徴としている。

【0052】

上記の方法によれば、従来のように、回路基板上に配されるソルダレジストと称される絶縁体層を、フリップチップ実装時に上記半導体チップを支持する支持部材(支持体)として使用しないので、ソルダレジストを上記支持部材として用いた場合における従来の問題点を招来しない。

【0053】

特に、上記の方法によれば、上記絶縁体層が、上記半導体チップの素子形成面よりも大きな開口部を有することで、上記絶縁体層と半導体チップとを互いに非接触状態にて上記半導体チップを上記接続用電極端子部にフリップチップ実装することができるので、上記支持体並びに突起形状を有する電極端子部の形成に際し、上記絶縁体層による制限を受けず、しかも、上記絶縁体層とは別に上記支持体を設けることで、該支持体の形成に際し、材料の選択の自由度が大きく、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより厳密に制御することが可能となるので、上記したように中央部にセンターパッドと称される電極端子部を有する半導体チップを回路基板にフリップチップ実装するに際し、半導体チップの素子形成面と回路基板とを実質的に平行に支持した状態で、安定して固定することができる。

【0054】

よって、上記の方法によれば、半導体チップの素子形成面と回路基板とが実質的に平行に支持された状態で、しかも、上記半導体チップの電極端子部と上記接続用電極端子部とが、横方向に位置ズレすることなくフリップチップ実装することができるので、半導体チップと回路基板との接続不良を防止することができ、接続信頼性が高い半導体装置を製造することができる。

【0055】

なお、従来は、超音波接合などの、電極端子部の塑性変形を伴う接合を行う場合に、半導体チップと回路基板とを平行に支持した状態でフリップチップ接続を行う技術は知られておらず、回路基板上に設けられたソルダレジストと称される絶縁体層を、半導体チップを支持する支持部材として用いる技術を、電極端子部の塑性変形を伴う接合に適用した場合、突起電極は必ず半導体チップ側に形成する必要があり、しかも、該突起電極の高さは、該突起電極の変形分、上記絶縁体層からなる支持部材よりも高くする必要がある。このため、従来は、半導体チップと回路基板とを平行に支持した状態でフリップチップ接続を行うことはできなかった。

【0056】

しかしながら、上記の方法によれば、上述したように、超音波接合などの、電極端子部の塑性変形を伴う接合を行う場合であっても上記半導体チップのフリップチップ実装を行う際に、上記半導体チップを上記回路基板と平行に支持することができるので、塑性変形によって強固に接続され、半導体チップと回路基板との位置ズレがなく、接続不良が防止され、接続信頼性が高い半導体装置を提供することができる。

【0057】

なお、本発明によれば、例えば、超音波、熱、圧力のうち少なくとも1つを上記半導体チップと回路基板との接合部に与える(印加する)ことにより、突起状に形成された上記電極端子部及び上記支持体の塑性変形による上記半導体チップと回路基板との接合を行うことができる。

【0058】

本発明にかかる半導体装置の製造方法は、上記の課題を解決するために、突起状に形成された上記電極端子部及び上記支持体を塑性変形させて上記半導体チップと回路基板とを接合させた後、上記半導体チップと回路基板との間隙に、該間隙を封止する界面封止樹脂(例えば異方導電性樹脂や絶縁性樹脂など)を注入し、該界面封止樹脂を硬化させることを特徴としている。

【0059】

上記の方法によれば、上記半導体チップと回路基板とを、より強固に安定して接合することができる。例えば、上記半導体チップと回路基板との接合が超音波接合によりなされる場合、上記半導体チップの電極端子部と回路基板の接続用電極端子部との溶着(接合)は、一般的に、中心部ではなく、その周辺にドーナツ状に生じる。このため、上記半導体チップと回路基板との間隙を上記界面封止樹脂によりさらに固着することで、両者の接合をより強固で安定したものとすることができる。

【0060】

そして、この場合、本発明においては、上記回路基板表面の絶縁体層が、上記半導体チップのフリップチップ実装領域(実装対象領域)において上記半導体チップの素子形成面よりも大きく開口されていることで、上記半導体チップを上記接続用電極端子部にフリップチップ実装したとき、上記半導体チップと回路基板との間隙に、容易に上記界面封止樹脂を注入することができる。

【0061】

本発明にかかる半導体装置の製造方法は、上記の課題を解決するために、素子形成面の中央部にほぼ直鎖状に複数の電極端子部が設けられた半導体チップを使用し、上記回路基板に、上記半導体チップの電極端子部に対応してほぼ直鎖状に複数の接続用電極端子部を設けると共に、上記接続用電極端子部からなる列の片側に、上記接続用電極端子部と平行に上記支持体を形成し、上記半導体チップと回路基板とを接合後に、上記支持体が形成された側とは上記接続用電極端子部を挟んで反対側、もしくは、上記接続用電極端子部からなる列に対し、ほぼ直交する方向から上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入することを特徴としている。

【0062】

上記の方法によれば、上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入することで、上記半導体チップと回路基板とを、より強固に安定して接合することができる。そして、このとき、上記支持体を、上記接続用電極端子部からなる列の片側に、上記接続用電極端子部と平行に上記支持体を形成し、上記支持体が形成された側とは上記接続用電極端子部を挟んで反対側、もしくは、上記接続用電極端子部からなる列に対し、ほぼ直交する方向から上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入することで、該界面封止樹脂の注入性を向上させることができ、効率良く、しかも、上記間隙に上記界面封止樹脂を満遍なく充填させることができる。

【0063】

本発明にかかる半導体装置の製造方法は、上記の課題を解決するために、素子形成面の中央部にほぼ直鎖状に複数の電極端子部が設けられた半導体チップを使用し、上記回路基板に、上記半導体チップの電極端子部に対応してほぼ直鎖状に複数の接続用電極端子部を設けると共に、上記接続用電極端子部からなる列の両側に、上記接続用電極端子部と平行に上記支持体を形成し、上記半導体チップと回路基板とを接合後に、上記接続用電極端子部からなる列に対し、ほぼ直交する方向から上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入することを特徴としている。

【0064】

上記の方法によれば、上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入することで、上記半導体チップと回路基板とを、より強固に安定して接合することができる。そして、このとき、上記支持体を、上記接続用電極端子部からなる列の両側に、上記接続用電極端子部と平行に上記支持体を形成し、上記接続用電極端子部からなる列に対し、ほぼ直交する方向から上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入することで、該界面封止樹脂の注入性を向上させることができ、効率良く、しかも、上記間隙に上記界面封止樹脂を満遍なく充填させることができる。

【0065】

本発明にかかる半導体装置の製造方法は、上記の課題を解決するために、突起状に形成された上記電極端子部と支持体とによって上記半導体チップと回路基板とを支持する前に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、上記半導体チップと回路基板との間隙を封止する界面封止樹脂からなる層を配し、上記間隙に界面封止樹脂(例えばシート状もしくはペースト状の界面封止樹脂)からなる層が配された状態で、突起状に形成した上記電極端子部と上記支持体とによって、上記半導体チップと回路基板とを架設状態で実質平行に支持し、突起状に形成された上記電極端子部及び上記支持体の塑性変形と上記界面封止樹脂の硬化とを、同一の工程において行うことを特徴としている。

【0066】

上記の方法によれば、上記半導体チップと回路基板との間隙を上記界面封止樹脂によって封止することで、上記半導体チップと回路基板とを、より強固に安定して接合することができる。

【0067】

この場合、上記の方法によれば、上記半導体チップの電極端子部と接続用電極端子部との電気的な接続と上記界面封止樹脂の硬化とを同時進行させることができるので、上記間隙を界面封止樹脂で封止する場合における半導体チップの実装にかかる時間を短縮させることができる。

【0068】

本発明にかかる半導体装置の製造方法は、上記の課題を解決するために、上記接続用電極端子部及び半導体チップの電極端子部のうち突起状に形成する電極端子部と支持体との最表層に、導電性接着剤(例えば半田材料や導電ペーストなど)からなる接合層を各々設けることを特徴としている。

【0069】

上記の方法によれば、上記半導体チップと回路基板とを、より強固に安定して接合することができる。例えば、上記半導体チップと回路基板との接合が超音波接合によりなされる場合、上記半導体チップの電極端子部と回路基板の接続用電極端子部との溶着(接合)は、一般的に、中心部ではなく、その周辺にドーナツ状に生じる。このため、上記接続用電極端子部及び半導体チップの電極端子部のうち突起状に形成する電極端子部と支持体との最表層に上記接合層を設けることで、両者の接合をより強固で安定したものとすることができる。

【0070】

本発明にかかる半導体装置の製造方法は、上記の課題を解決するために、素子(例えば能動素子)形成面の中央部に電極端子部(いわゆるセンターパッドと称される電極パッド)が設けられた半導体チップを、上記電極端子部にて、上記半導体チップよりも大きく、かつ、表面に絶縁体層(例えばソルダレジスト)が設けられた回路基板における接続用電極端子部(例えば接続パッド)に架設状態でフリップチップ実装する半導体装置の製造方法において、上記回路基板表面に、該回路基板における上記半導体チップのフリップチップ実装対象領域に上記半導体チップの素子形成面よりも大きな開口部(例えばソルダレジスト開口部)を有する絶縁体層を形成し、上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部を突起状に形成すると共に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、突起状に形成された上記電極端子部とほぼ同じ高さを有し、上記半導体チップの素子形成面と上記回路基板表面とを実質平行に支持する支持体を形成し、突起状に形成された上記電極端子部と支持体とによって、上記回路基板における上記絶縁体層の開口部内で、上記半導体チップと回路基板とを架設状態で実質平行に支持した状態で、上記半導体チップと回路基板との間隙を界面封止樹脂(例えば異方導電性樹脂や絶縁性樹脂など)により封止して上記接続用電極端子部と上記半導体チップの電極端子部とを圧接させることを特徴としている。

【0071】

上記の方法によれば、従来のように、回路基板上に配されるソルダレジストと称される絶縁体層を、フリップチップ実装時に上記半導体チップを支持する支持部材(支持体)として使用しないので、ソルダレジストを上記支持部材として用いた場合における従来の問題点を招来しない。

【0072】

特に、上記の方法によれば、上記絶縁体層が、上記半導体チップの素子形成面よりも大きな開口部を有することで、上記絶縁体層と半導体チップとを互いに非接触状態にて上記半導体チップを上記接続用電極端子部にフリップチップ実装することができるので、上記支持体並びに突起形状を有する電極端子部の形成に際し、上記絶縁体層による制限を受けず、しかも、上記絶縁体層とは別に上記支持体を設けることで、該支持体の形成に際し、材料の選択の自由度が大きく、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより厳密に制御することが可能となるので、上記したように中央部にセンターパッドと称される電極端子部を有する半導体チップを回路基板にフリップチップ実装するに際し、半導体チップの素子形成面と回路基板とを実質的に平行に支持した状態で、安定して固定することができる。

【0073】

よって、上記の方法によれば、半導体チップの素子形成面と回路基板とが実質的に平行に支持された状態で、しかも、上記半導体チップの電極端子部と上記接続用電極端子部とが、横方向に位置ズレすることなくフリップチップ実装することができるので、半導体チップと回路基板との接続不良を防止することができ、接続信頼性が高い半導体装置を製造することができる。

【0074】

上記の方法によれば、従来のように、回路基板上に配されるソルダレジストと称される絶縁体層を、フリップチップ実装時に上記半導体チップを支持する支持部材(支持体)として使用しないので、上記のように半導体チップの電極端子部と接続用電極端子部とを圧接させて電気的に接続すると共に上記半導体チップと回路基板とを界面封止樹脂により固着させる場合においても、半導体チップと回路基板とソルダレジストを上記支持部材として用いた場合における従来の問題点を招来しない。

【0075】

特に、上記の方法によれば、上記絶縁体層が、上記半導体チップの素子形成面よりも大きな開口部を有し、上記絶縁体層と半導体チップとが互いに非接触状態にて上記半導体チップが上記接続用電極端子部にフリップチップ実装されるので、半導体チップを支持するための支持部材並びに上記電極端子部(突起電極)の形成に際し、上記絶縁体層による制限を受けず、しかも、上記絶縁体層とは別に上記支持体が設けられていることから、該支持体の形成に際し、材料の選択の自由度が大きく、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより厳密に制御することが可能となる。

【0076】

このため、上記の方法によれば、上記したように中央部にセンターパッドと称される電極端子部を有する半導体チップを回路基板にフリップチップ実装するに際し、半導体チップの素子形成面と回路基板とを実質的に平行に支持した状態で、安定して固定することができ、半導体チップと回路基板との接続不良が防止され、接続信頼性が高い半導体装置を提供することができる。

【0077】

本発明にかかる半導体装置の製造方法は、上記の課題を解決するために、上記界面封止樹脂として、内部に導電粒子が分散された異方導電性樹脂を用いることを特徴としている。

【0078】

上記の方法によれば、上記異方導電性樹脂中に存在する導電粒子により、より良好な電気的接続を得ることができる。特に、超音波などを用いて電極端子部を塑性変形させることにより上記半導体チップのフリップチップ実装を行う場合、上記半導体チップの電極端子部と接続用電極端子部との接合部に上記導電粒子が埋め込まれ、該導電粒子により、より良好な電気的接続を得ることができる。

【0079】

本発明にかかる半導体装置の製造方法は、上記の課題を解決するために、上記接続用電極端子部及び半導体チップの電極端子部のうち突起状に形成する電極端子部と支持体とを、同じ材料で形成することを特徴としている。

【0080】

上記の方法によれば、上記支持体を、突起状に形成された電極端子部と同じ材料で形成することで、既存の技術により、両者の高さを容易に一致させることができる。このため、上記の方法によれば、より一層接続信頼性が高い半導体装置を製造することができる。

【0081】

また、上記の方法によれば、上記支持体と、突起状に形成された電極端子部とを、同一工程、例えばエッチング加工やメッキ等の基板配線の形成工程において同時に形成することが可能になるので、工程数の増加を招くこともなく、安価かつ容易に上記支持体を形成することができる。

【0082】

しかも、上記の方法によれば、超音波接合などの、電極端子部の塑性変形を伴う接合を行う場合、該塑性変形による、上記支持体と、突起状に形成された電極端子部との変形量を容易に一致させることができるので、上記半導体チップと回路基板とを平行に支持した状態で接合することが可能となる。よって、上記の方法によれば、塑性変形によって強固に接続され、半導体チップと回路基板との位置ズレがなく、接続不良が防止され、接続信頼性がより高い半導体装置を製造することができる。

【0083】

本発明にかかる半導体装置の製造方法は、上記の課題を解決するために、上記支持体を金属で形成することを特徴としている。

【0084】

金属材料は、その厚さをエッチング加工する技術が特に充実しており、厚みの制御を容易に行うことができる。このため、上記支持体を金属で形成する場合、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより一層厳密かつ容易に制御することが可能となるので、上記支持体の高さを、突起状に形成された電極端子部の高さと容易に合わせることができる。このため、上記の方法によれば、より接続信頼性が高い半導体装置を製造することができる。

【0085】

本発明にかかる半導体装置の製造方法は、上記の課題を解決するために、上記接続用電極端子部及び半導体チップの電極端子部のうち上記接続用電極端子部を突起状に形成すると共に、上記接続用電極端子部の形成工程と同一の工程で上記回路基板に上記支持体を形成することを特徴としている。

【0086】

上記の方法によれば、上記接続用電極端子部及び半導体チップの電極端子部のうち上記接続用電極端子部を突起状に形成すると共に、上記接続用電極端子部の形成工程と同一の工程で上記回路基板に上記支持体を形成することで、上記支持体と、突起状に形成された電極端子部とを、例えばエッチング加工やメッキ等の基板配線の形成工程において、配線の形成と同時に、あるいは、上記配線を利用して形成することが可能になるので、工程数の増加を招くこともなく、安価かつ容易に上記支持体を形成することができる。また、上記の方法によれば、既存の技術により、両者の高さを容易に一致させることができる。このため、上記の方法によれば、より一層接続信頼性が高い半導体装置を、安価かつ容易に製造することができる。

【0087】

【発明の実施の形態】

〔実施の形態1〕

本発明の実施の一形態について図1(a)〜(d)乃至図4に基づいて説明すれば、以下の通りである。なお、図1(a)〜(d)は本実施の形態にかかる半導体装置の製造工程の一例を示す断面図であり、そのうち、図1(d)は、本実施の形態にかかる半導体装置の断面の概略構成を示している。また、図2は、図1(a)〜(d)に示す半導体チップ1の素子形成面の概略構成を示す平面図であり、図3は、図1(a)〜(d)に示す回路基板2の概略構成を示す平面図である。

【0088】

本実施の形態にかかる半導体装置は、図1(d)に示すように、ボンディングパッドとしていわゆるセンターパッドと称される平面電極(電極パッド)からなる電極端子部5を有する半導体チップ1(ベアチップ)が、回路基板2に、上記電極端子部5に対応して突出して設けられた接続電極3(接続用電極端子部)によってフリップチップ実装されている構成を有している。上記半導体チップ1と回路基板2とは界面封止樹脂8により固着されている。

【0089】

上記半導体チップ1は、素子(能動素子)形成面の中央部に、平面電極(電極パッド)からなる電極端子部5を有すると共に、該電極端子部5が露出するように該電極端子部5を除く素子形成面、つまり、素子が、絶縁膜13で覆われた構成を有している。これにより、上記半導体チップ1は、その素子形成面が上記回路基板2と対向するように上記回路基板2にフリップチップ実装されている。以下、本実施の形態において、上記半導体チップ1の素子形成面を素子面と称し、該素子面の反対側の面を裏面と称する。

【0090】

上記半導体チップ1の例としては、例えばDRAMなどが挙げられる。DRAMなどの半導体チップ1は、例えば、図2に示すように、素子面の中央部に、例えばアルミパッドなどの電極パッドからなる複数の電極端子部5が直鎖状に形成された構成を有し、該電極端子部5…を除く素子面が、該電極端子部5…とほぼ面一となるように該電極端子部5…の厚み(高さ)とほぼ同じ厚みを有する絶縁膜13で覆われた構成を有している。すなわち、上記絶縁膜13は、素子形成面を平坦化する平坦化膜としても機能する。

【0091】

上記半導体チップ1の構造並びに上記電極端子部5の構成は、上記電極端子部5において平面電極(電極パッド)上に突起電極が設けられていないことを除けば、センターパッドを有する従来の半導体チップの構造並びに電極パッドの構成と基本的に同じであり、ここではその説明を省略する。上記電極端子部5(平面電極)の最表層は、接続電極3との電気的接続を良くするため、低抵抗金属、通常はAl、Si、Cuなどの金属で構成されているが、これに限定されるものではなく、Ni、Cr、Ti、Wなどの、バリアメタルもしくはアンダーバンプメタルに使用される金属で構成されていてもよい。

【0092】

なお、以下の実施の形態では、上記半導体装置の例として、上記半導体チップ1に、図2に示すDRAMを用いた場合を例に挙げて説明するものとするが、本発明は、これに限定されるものではない。また、上記電極端子部5の設置数は特に限定されず、任意の数でよい。さらに、上記電極端子部5の配列形態も、これら電極端子部5…がいわゆるセンターパッドと称される形態であれば、特に限定されない。

【0093】

一方、上記回路基板2は、図1(a)〜(d)に示すように、上記半導体チップ1が実装(搭載)される側の面(以下、単に半導体チップ搭載面と記す)に、金属配線などの配線20(配線パターン)が設けられた構成を有している。上記回路基板2における半導体チップ搭載面(第1面)とは反対側の面(第2面)には、絶縁体層10(絶縁性部材)が設けられていると共に、半田ボールなどの図示しない外部入出力端子が設けられている構成を有している。上記外部入出力端子は、回路基板2並びに該回路基板2の第2面を覆う上記絶縁体層10を貫く貫通孔11を介して上記配線20と電気的に接続されている。

【0094】

上記回路基板2は、図3に示すように、上記半導体チップ1よりも縦横共に大きく、該回路基板2における半導体チップ搭載面、つまり、配線20形成面には、上記半導体チップ1のチップサイズよりも大きく開口(窓開け)された絶縁体層6(絶縁性部材)が設けられている。

【0095】

上記絶縁体層6は、一般的にソルダレジストと称されるものである。しかしながら、前記したように、ソルダレジストは、例えば金属材料などからなる部材と比較して、厚みの制御が困難であり、材料に起因する厚さのばらつきが比較的大きい。また、エッチング加工により厚みを制御する場合における制御性も、例えば金属材料とソルダレジストとでは大きな差がある。このため、上記ソルダレジストを上記支持部材として使用することは、接続不良や接続信頼性の低下を招くことになるとともに、製造工程の増加やコストアップにつながる。

【0096】

そこで、本実施の形態においては、上述したように回路基板2の絶縁体層6を半導体チップ1のチップサイズよりも大きく開口することで、上記回路基板2の半導体チップ搭載面に、上記半導体チップ1のチップサイズよりも大きなソルダレジスト開口部12を形成すると共に、上記回路基板2の半導体チップ搭載面に、上記絶縁体層6とは別に、上記半導体チップ1のフリップチップ実装時に上記半導体チップ1を支持する支持体4(支持部材)を形成している。

【0097】

つまり、本実施の形態においては、上記絶縁体層6は、図3に示すように、回路基板2の周縁部に形成され、該絶縁体層6により形成されたソルダレジスト開口部12の面積は回路基板2に搭載される半導体チップ1の素子面の面積よりも大きいことで、該絶縁体層6を、例えば前記特許文献1に示すようにセンターパッドを有する半導体チップのフリップチップ実装のための支持部材としてではなく、ソルダレジストとして、回路基板2の強度確保や、上記回路基板2における配線20の絶縁状態の確保に使用している。

【0098】

上記ソルダレジスト開口部12内には、上記半導体チップ1の電極端子部5に対応して接続電極3が形成されている。該接続電極3は、突出構造を有している。すなわち、本実施の形態において上記回路基板2におけるソルダレジスト開口部12内には、半導体チップ1の電極端子部5…に対応して、突出構造(突起)を有する複数の接続パッドからなる接続電極3が設けられている。

【0099】

これら接続電極3…は、上記ソルダレジスト開口部12内の中央部に配され、上記半導体チップ1は、該半導体チップ1の素子面が上記絶縁体層6と非接触の状態で上記回路基板2にフリップチップ実装されるようになっている。

【0100】

よって、本実施の形態において、支持体4は、上記ソルダレジスト開口部12内における上記半導体チップ1の実装対象領域において突起(突出)して設けられ、これにより、上記半導体チップ1のフリップチップ実装時に上記半導体チップ1と回路基板2とを実質平行に支持するようになっている。本実施の形態において、上記半導体チップ1と回路基板2とを実質平行に支持するとは、半導体チップ1の素子面と上記回路基板2表面(基板平面)とを実質平行に支持することを示す。

【0101】

上記支持体4は、上記接続電極3とほぼ同じ高さを有し、上記接続電極3の周辺部に、例えば図3に示すように接続電極3…の配列方向に沿ってこれら接続電極3…とほぼ平行に設けられている。

【0102】

なお、図3に示す回路基板2では、半導体チップ1の実装対象領域において接続電極3…を挟んで両側に支持体4が設けられている構成としたが、上記支持体4は、上記半導体チップ1のフリップチップ実装時に上記半導体チップ1を上記回路基板2と実質平行に支持することができさえすれば特に限定されるものではなく、例えば、支持体4が回路基板2上に設けられた接続電極3…の片側にのみ設けられている構成としてもよい。

【0103】

上記支持体4の材料としては、上記半導体チップ1を、上記回路基板2と実質平行に支持することができると共に上記半導体チップ1のフリップチップ実装条件において塑性変形する材料、好適には上記フリップチップ実装時における変形量が上記接続電極3とほぼ同じ材料、より好適には上記変形量が上記接続電極3と同じ材料が用いられる。

【0104】

これにより、上記接続電極3と電極端子部5とを強固に安定してかつ短時間で接合することができると共に、上記変形量の違いに起因する接続不良を抑制、好適には防止することができる。

【0105】

上記支持体4の材料のなかでも、特に好ましい材料は、上記の観点から上記接続電極3と同じ材料であり、そのなかでも特に、支持体4の高さ(厚み)の制御が容易であり、また、金属接合により上記接続電極3と電極端子部5とを強固に安定してかつ短時間で接合することができることから、最も好ましくは金属材料である。

【0106】

上記接続電極3の材料としては、従来の半導体装置における回路基板の接続電極(接続パッド)もしくは半導体チップにおける電極端子部(突起電極)に用いられている材料と同様の材料を用いることができる。具体的には、上記接続電極3の材料としては、前記電極端子部5を構成する平面電極材料、すなわち、前記例示の金属材料などを用いることができるが、これに限定されるものではない。

【0107】

上記接続電極3及び支持体4と前記電極端子部5を構成する平面電極材料との組み合わせは特に限定されるものではないが、上記半導体チップ1のフリップチップ実装に際し、上述したように超音波などを用いて電極の塑性変形を伴う接合(例えば金属接合)を行う場合、上記接続電極3及び支持体4の材料としては、前記電極端子部5を構成する平面電極材料よりも柔らかい材料からなることが望ましい。上記接続電極3及び支持体4の材料としては、例えばAuやSnなどが好適に用いられるが、これに限定されるものではない。

【0108】

また、上記接続電極3及び支持体4としては、Sn、Pbを主成分とする半田を使用してもよく、公知の半田突起電極(バンプ)を形成する方法を用いて該接続電極3及び支持体4を形成することもできる。

【0109】

半田突起電極の形成方法としては、例えば、半田ワイヤを用いて、ワイヤボンディングを応用したワイヤバンプ法や、無電界メッキ、電解メッキを用いる方法などがある。この場合、上記接続電極3及び支持体4の最表面には、酸化防止層として、例えばAuメッキが施されていることが望ましい。また、例えば、Cuなどの配線材料上にもAuメッキなどが施されている構成としてもよい。なお、上記接続電極3をAuで構成する場合は、酸化防止層は特に形成する必要はない。また、上記接続電極3及び支持体4をメッキ処理により形成する場合、上記配線20上には、メッキ阻止膜が設けられていることが望ましい。

【0110】

ソルダレジストと例えば金属材料とでは厚さのコントロール並びにエッチングによる加工時における制御性に大きな差があることは勿論であるが、導電性パターン、特に金属パターンを形成する場合、従来からエッチングによる加工などによりその厚みを制御する技術が充実している。このため、上記支持体4に金属材料を用いることで、上記支持体4の形成に、極めて普遍的な技術を応用することができる。

【0111】

よって、上記支持体4に金属材料などの導電性部材を用いる場合、例えば、上記回路基板2側の電極部材(金属部材などの導電性部材)を上記支持体4として用いることもできる。また、この場合、上記電極部材は、信号配線として、上記半導体チップ1の中央部に設けられた電極端子部5…と接続することもできる。

【0112】

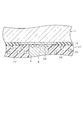

つまり、図3に示す回路基板2は、例えば図4に示すような断面構造を有していてもよい。図4に示すように回路基板2側の電極部材、例えば配線20を上記支持体4に用いることで、該支持体4を、エッチングやメッキ等による配線パターン形成工程において、例えば配線20や接続電極3と同じ材料、例えば同じ金属材料(配線材料)を用いて同時に形成することができる。

【0113】

このように上記支持体4が例えば上記接続電極3と同じ材料にて形成されていることで、突起電極である接続電極3の塑性変形により電極端子部5と接続電極3とを接続する際の支持体4と接続電極3との変形量を同じにすることができ、両者の変形量の違いに起因する接続不良を防止することができる。

【0114】

また、上記支持体4と接続電極3とを同一工程で形成することにより、両者の高さを容易に同じ高さに形成することができる。

【0115】

但し、上記支持体4の構造並びに形成方法は、上記図4に示す構造並びに上述した方法に限定されるものではない。上記支持体4は、他の電極部材とは離間(独立)して設けられた構造を有していてもよく、また、上記接続電極3形成前あるいは形成後に上記支持体4を形成してもよいことは言うまでもないことである。

【0116】

図4に示すように、上記接続電極3及び支持体4の高さ(厚みd)、つまり、配線20の厚みを含む、これら接続電極3及び支持体4による突起部分の厚みは、使用する材料や、上記配線20の厚みなどに応じて、従来、半導体チップと回路基板との接続に用いられている突起電極の高さ(厚み)と同様に設定すればよく、特に限定されるものではないが、20μm〜60μmの範囲内とすることが好ましい。

【0117】

本実施の形態によれば、上記絶縁体層6を上記半導体チップ1の支持部材として使用しないことで、図4に示すように、上記支持体4を、上記絶縁膜6よりも高さ(層厚)が小さくなるように形成することができる。このように上記支持体4を形成すれば、半導体装置の小型化を図ることが可能になると共に、上記半導体チップ1と回路基板2との接合をより安定して行うことが可能となる。

【0118】

また、上記支持体4の先端面の面積、つまり、上記支持体4における該支持体4と半導体チップ1との接触面の面積(以下、説明の便宜上、単に支持体4の面積と記す)は、上記接続電極3の先端面の面積、つまり、上記接続電極3における該接続電極3と半導体チップ1との接触面の面積(以下、説明の便宜上、単に接続電極3の面積と記す)よりも大きく形成されていることが好ましい。

【0119】

上記支持体4の面積によっては、半導体チップ1を加圧するとき、半導体チップ1の素子面に支持体4が押圧されることで、該押圧部に応力が集中して上記半導体チップ1の素子面がダメージを受ける可能性がある。よって、支持体4が半導体チップ1の素子面に当たることによるダメージを軽減するためには、該支持体4の面積を前記接続電極3の面積よりも大きくすることが好ましい。

【0120】

なお、本実施の形態において、図3に示す回路基板2上に設けられた配線20、接続電極3、及び支持体4のパターン構造(形状、大きさ)、並びに、ソルダレジスト開口部12の大きさや形状は、図3に示す構造(形状、大きさ)並びに上記説明に限定されるものではなく、各々の構成要素について上記の条件に適合すれば任意のものでよいものとする。

【0121】

なお、上記回路基板2としては、例えば、ワイヤボンドターミナルを有するリードフレームや、ポリイミド樹脂、BTレジン(ビスマレイミド・トリアジン樹脂)等で製作された有機基板などを使用することができるが、特に限定されるものではなく、任意の基板を用いることができる。

【0122】

上記半導体チップ1と回路基板2とは、図1(d)に示すように、上記接続電極3…及び電極端子部5…で互いに接合されていると共に、異方導電性導電性樹脂や絶縁性樹脂などの界面封止樹脂8にて上記半導体チップ1と回路基板2との間隙を封止するように固着されている。上記界面封止樹脂8としては、例えばエポキシ樹脂などの熱硬化性樹脂が使用されるが、これに限定されるものではない。

【0123】

次に、本実施の形態にかかる上記半導体装置の製造工程の一例について、図1(a)〜(d)乃至図4に基づいて以下に説明する。

【0124】

先ず、図1(a)に示すように、上記半導体装置の製造に用いる半導体チップ1及び回路基板2を準備する。

【0125】

上記半導体チップ1の作製においては、図2に示すように該半導体チップ1の素子面中央部に、平面電極からなる電極端子部5…を設けると共に、これら電極端子部5…を除く素子面を、該電極端子部5…と面一となるように該電極端子部5…の厚み(高さ)とほぼ同じ厚みを有する絶縁膜13で覆っておく。

【0126】

一方、上記回路基板2の作製においては、図3に示すように該回路基板2上に、上記半導体チップ1の実装対象領域よりも大きく開口された絶縁体層6を形成する。また、上記回路基板2における上記半導体チップ1の実装対象領域には、上記半導体チップ1の電極端子部5…に対応して接続電極3…を形成すると共に、これら接続電極3とほぼ同じ高さ(厚み)を有する支持体4…を形成する。このとき、上記接続電極3…並びに支持体4…は、突起状に形成する。上記支持体4…は、上記回路基板2上に、接続電極3…や配線20などをエッチング等により形成するときに同時に作製することができ、かつ、高さを合わせることも容易にできる。

【0127】

上記電極端子部5、配線20、接続電極3、及び支持体4の材料としては、従来の半導体装置において電極や配線に通常使用される材料を用いることができ、前記したように、例えば、Al、Si、Cu、Ni、Cr、Ti、W、Auなどの材料を用いることができる。また、上記した以外の半導体チップ1及び回路基板2の構成は、従来と同様に作製することができる。

【0128】

次に、図1(b)に示すように、回路基板2に設けられた接続電極3…と半導体チップ1の電極端子部5…とが各々接触するように位置合わせを行う。この際、支持体4の高さが接続電極3とほぼ同じ高さであることにより、半導体チップ1と回路基板2とを容易に実質平行に保持することができる。このため、上記接続電極3…と電極端子部5…との接触を、安定した状態とすることができる。

【0129】

続いて、同図1(b)に示すように、上記半導体チップ1と回路基板2とが実質平行に保持され、かつ、上記接続電極3…と電極端子部5とが接触している状態で、超音波印加ツール7または図示しないステージまたはその併用により、加熱状態にて超音波を印加して所定の荷重を加えることにより、上記接続電極3…と電極端子部5…とを、各々電気的に接続する。

【0130】

具体的には、上記半導体チップ1と回路基板2との接合部を100℃〜150℃に加熱した状態で、超音波印加ツール7によって40kHzの超音波を印可して上記接合部に数Nから数十Nの荷重を1秒間程度加える。

【0131】

これにより、上記半導体チップ1の電極端子部5…と回路基板2の接続電極3…とは、回路基板2に設けられた上記接続電極3…及び支持体4…の塑性変形を伴い、電気的に接続される。このとき接続電極3…と支持体4…とに、ほぼ同じ塑性変形する材料、より好適には同じ塑性変形する材料(例えば同じ材料)を用いることで、両者の変形量をほぼ同じにすることができ、変形量の違いに起因する接続不良を防止することができ、接続電極3と電極端子部5との接続信頼性を向上させることができる。

【0132】

次いで、図1(c)に示すように、半導体チップ1の側面からノズル9を用いて、上記接続電極3及び支持体4によって架設された上記半導体チップ1と回路基板2との間隙に、界面封止樹脂8として、液状の界面封止樹脂材料を注入する。

【0133】

このとき、図3に示すように、半導体チップ1の素子面の中央部にほぼ直線状に形成されている電極端子部5…に対応して回路基板2における半導体チップ1の実装対象領域の中央部にほぼ直線状に上記接続電極3…が設けられている場合において、上記回路基板2に、これら接続電極3…の配列方向に沿ってこれら接続電極3…と実質的に平行かつこれら接続電極3…の両側に上記支持体4…を形成した場合には、上記間隙に、上記電極端子部5…の配列方向(つまり、接続電極3…の配列方向)に対しほぼ直交する方向から上記界面封止樹脂8に用いられる液状の界面封止樹脂材料を注入することで、該界面封止樹脂8の注入性を向上させることができる。

【0134】

一方、半導体チップ1の素子面の中央部にほぼ直線状に形成されている電極端子部5…に対応して回路基板2における半導体チップ1の実装対象領域の中央部にほぼ直線状に上記接続電極3…が設けられている場合において、上記回路基板2に、これら接続電極3…の配列方向に沿ってこれら接続電極3…と実質的に平行かつこれら接続電極3…の片側にのみ上記支持体4…を形成した場合には、上記間隙に、接続電極3…のもう一方の片側、つまり、上記支持体4…が形成されている側とは上記接続電極3…を挟んで反対側、もしくは、上記電極端子部5…の配列方向(つまり、接続電極3…の配列方向)に対しほぼ直交する方向から上記界面封止樹脂8を注入することで、該界面封止樹脂8の注入性を向上させることができる。

【0135】

このように本実施の形態では、前記特許文献1に示すようにソルダレジスト、(本実施の形態では回路基板2における絶縁体層6)を半導体チップ1の支持体(支持部材)として使用しないので、該ソルダレジスト(絶縁体層6)によるソルダレジスト開口部12を、該半導体チップ1のチップサイズよりも大きく設定することができる。このため、図1(c)に示すように上記回路基板2上に半導体チップ1を搭載した後に該半導体チップ1と回路基板2との間隙に上記界面封止樹脂8を注入する場合、該界面封止樹脂8の注入を容易に行うことができる。

【0136】

また、本実施の形態によれば、上記したように上記半導体チップ1と回路基板2とを接合した後で、両者の間隙に上記界面封止樹脂8を注入することができることから、前記特許文献1に示すように半導体チップを回路基板に搭載するに際し、両者の接続状態を維持するために界面封止樹脂を硬化させる間、半導体チップを加熱加圧ツールにより一定時間保持(加圧)する必要はない。このため、上記界面封止樹脂8の硬化時に上記半導体チップ1と回路基板2との間のタクト短縮、つまり、上記半導体チップ1の実装(ボンディング固定)に係る時間の短縮を行うことができる。

【0137】

本実施の形態においては、上記界面封止樹脂8として、例えば熱硬化性樹脂であるエポキシ樹脂を用いている。該界面封止樹脂8を硬化させることにより、図1(d)に示すように、上記半導体チップ1が上記回路基板2にフリップチップ実装される。

【0138】

〔実施の形態2〕

本発明にかかる他の実施形態について、図5(a)〜(c)に基づいて説明すれば、以下のとおりである。なお、説明の便宜上、前記実施の形態1にて説明した図面と同じ機能を有する部材については、同じ符号を付記し、その説明を省略する。また、前記実施の形態1で述べた各種の特徴点については、本実施の形態についても組み合わせて適用し得るものとする。

【0139】

図5(a)〜(c)は本実施の形態にかかる半導体装置の製造工程の一例を示す断面図であり、そのうち、図5(d)は、本実施の形態にかかる半導体装置の断面の概略構成を示している。また、図6は、図5(c)に示す本実施の形態にかかる半導体装置の要部の構成を概略的に示す断面図である。

【0140】

前記実施の形態1では、半導体チップ1と回路基板2との間隙を封止する界面封止樹脂として、液状の熱硬化性樹脂を使用した。これに対し、本実施の形態では、界面封止樹脂として、異方導電性樹脂からなる界面封止樹脂21(異方導電性樹脂フィルム)を使用する。

【0141】

本実施の形態にかかる半導体装置は、図5(c)に示すように、半導体チップ1における電極端子部5…と回路基板2における接続電極3…とが、上記界面封止樹脂21を介してフリップチップ実装された構造を有している。

【0142】

図6に示すように、異方導電性樹脂からなる界面封止樹脂21は、バインダー樹脂22に導電粒子23…が分散されてなる。上記界面封止樹脂21は、例えばフィルム状のエポキシ樹脂中に導電粒子23が分散しており、導電粒子23を挟み込む所定の導電部分だけその間隙が導電粒子23の粒形以下に小さくなることで導電状態が得られ、他は絶縁状態となる特性を有する。

【0143】

このため、上記界面封止樹脂21を介して上記電極端子部5…と接続電極3…とが接合されることで、上記電極端子部5…と接続電極3…とは、上記導電粒子23を介して電気的に接続される。また、このとき上記電極端子部5…と接続電極3…とは、上記導電粒子23が両者の接合部にクサビのように埋め込まれた状態で金属接合される。また、熱圧着の際に、フィルム状のバインダー樹脂22は溶融して一旦ペースト状となり、上記半導体チップ1と回路基板2との間隙を封止すると共に両者を接続する。

【0144】

次に、本実施の形態にかかる上記半導体装置の製造工程の一例について、図5(a)〜(c)及び図6に基づいて以下に説明する。

【0145】

先ず、図5(a)に示すように、前記実施の形態1と同様にして上記半導体装置の製造に用いる半導体チップ1及び回路基板2を準備する。但し、本実施の形態においては、同図5(a)に示すように、上記半導体チップ1と回路基板2とを接合する前に、予め、上記半導体チップ1の素子面にフィルム状の異方導電性樹脂からなる界面封止樹脂21(異方導電性樹脂フィルム)を貼り付けておく。

【0146】

これにより、本実施の形態においては、上記半導体チップ1は、該半導体チップ1の素子面に上記フィルム状の界面封止樹脂21が貼り付けられた状態で回路基板2にフリップチップ実装される。

【0147】

上記半導体チップ1と回路基板2との接合(実装)は、図5(b)に示すように、上記半導体チップ1の素子面に上記フィルム状の界面封止樹脂21が貼り付けられた状態で上記半導体チップ1の電極端子部5…と回路基板2の接続電極3…とを位置合わせする。本実施の形態においても、上記支持体4の高さが接続電極3とほぼ同じ高さであることにより、半導体チップ1と回路基板2とを容易に実質平行に保持することができる。このため、上記接続電極3…と電極端子部5…との接触を、安定した状態とすることができる。

【0148】

続いて、同図5(b)に示すように、上記半導体チップ1と回路基板2とが実質平行に保持され、かつ、上記接続電極3…と電極端子部5…とが接触している状態で、超音波印加ツール7または図示しないステージまたはその併用により、加熱状態にて超音波を印加して所定の荷重を加えることにより、上記接続電極3…と電極端子部5…とを、各々電気的に接続する。

【0149】

但し、本実施の形態においては、電極端子部5…と接続電極3…との電気的な接続と同時に上記界面封止樹脂21の硬化を進めることで上記5…と接続電極3…との接合部を保持するため、該接合部を120℃〜240℃に加熱した状態で、超音波印加ツール7によって40kHzの超音波を印可して上記接合部に数Nから数十Nの荷重を3秒間程度加える。

【0150】

これにより、上記半導体チップ1と回路基板2とは、上記界面封止樹脂21によって接続(接合)されると共に、上記接続電極3…及び支持体4…と上記半導体チップ1との各々の接合部において、例えば図6に示すように上記界面封止樹脂21中の導電粒子23が、該接合部(特に該接合部における上記接続電極3…及び支持体4…)にクサビのように埋め込まれることで、上記接続電極3…及び支持体4…の塑性変形を伴い、電気的に接続される。

【0151】

このように、本実施の形態では、上記半導体チップ1と回路基板2との電気的な接続と同時に上記界面封止樹脂21の硬化を進めることで、上記半導体チップ1と回路基板2との接続部、特に、上記半導体チップ1と接続電極3…及び支持体4…との接合部を保持する。なお、該工程の後、必要に応じて、オーブンなどの加熱手段を用いて上記界面封止樹脂21の硬化をさらに進めてもよい。これにより、図5(d)に示すように、上記半導体チップ1と回路基板2とをフリップチップ実装することができる。

【0152】

なお、本実施の形態においても、前記実施の形態1と同様、電極端子部5の最表層は、通常、AlやSi、Cuにて形成されるが、より高い接続信頼性を確保するためには、該電極端子部5の表面が、Ni、Cr、Ti、W、Auなどの金属で構成されており、好ましくはAuの厚さが1μm程度あるほうがよい。

【0153】

以上のように、本実施の形態においては、上記半導体チップ1と回路基板2とを、両者の間隙に設けられる界面封止樹脂21に異方導電性を持たせるために添加された導電粒子23を、両者の接合部に噛み混ませた状態で、電気的に接合することで、上記接合部の初期の接続安定性や接続信頼性を向上させることができる。

【0154】

さらに、前記実施の形態1では半導体チップ1と回路基板2の電気的な接続を行った後、両者の間隙に液状の界面封止樹脂8を注入して硬化させることによりフリップチップ実装を行ったが、本実施の形態では、予め半導体チップ1の素子面にフィルム状の界面封止樹脂21が貼り付けられているので、電極端子部5…と接続電極3…との電気的な接続と界面封止樹脂21の硬化とを同時進行させることができるので、半導体チップ1の実装(ボンディング固定)にかかる時間を短縮させることができる。

【0155】

なお、通常、半導体チップの電極端子部の配列に対して垂直方向(側面の方向)から界面封止樹脂を注入すると、該半導体チップの側面方向位置ずれが問題となり、高い位置決め精度を持った装置が必要となるが、上記したようにフィルム状の異方導電性樹脂を半導体チップ1の素子面に貼り付けた状態で上記半導体チップ1の実装を行うことで、該半導体チップ1の横方向のアライメント精度にマージンがあり、半導体装置の側面方向での位置ずれの問題を招来しないので、より安価な構成とすることができる。

【0156】

〔実施の形態3〕

本発明にかかるさらに他の実施形態について、図7(a)〜(d)に基づいて説明すれば、以下のとおりである。なお、説明の便宜上、前記実施の形態1及び実施の形態2にて説明した図面と同じ機能を有する部材については、同じ符号を付記し、その説明を省略する。また、前記実施の形態1及び実施の形態2で述べた各種の特徴点については、本実施の形態についても組み合わせて適用し得るものとする。

【0157】

図7(a)〜(d)は本実施の形態にかかる半導体装置の製造工程の一例を示す断面図であり、そのうち、図7(d)は、本実施の形態にかかる半導体装置の断面の概略構成を示している。

【0158】

本実施の形態において用いられる回路基板2は、図7(a)に示すように、前記実施の形態1及び2に示す接続電極3…及び支持体4…の最表層に、回路基板2と半導体チップ1とを接続(接合)するための接合層31もしくは接合層32が設けられている構成を有している。

【0159】

すなわち、本実施の形態において用いられる回路基板2は、接続電極及び支持体として、前記実施の形態1及び2に示す接続電極3…及び支持体4…を半導体チップ1と回路基板2とを架設状態で支持する支持層とし、該支持層上に、上記半導体チップ1の実装(接合)条件において塑性変形することにより上記半導体チップ1と回路基板2とを接続(接合)する接合層31・32が形成された積層構造を有する接続電極33(接続用電極端子部)及び支持体34が設けられている構成を有している。

【0160】

例えば、上記接続電極33及び支持体34は、上記支持層としての第1導電層(接続電極3もしくは支持体4)上に、接合層31もしくは接合層32として、上記第1導電層並びに電極端子部5…よりも柔らかい材料からなる第2導電層が設けられている構成を有している。

【0161】

上記接合層31・32には、例えば、Sn、または、Snを含む半田材料などの導電性材料からなる接続材料が用いられる。しかしながら、上記導電性材料(接続材料)としては、これに限らず、Agやメッキを施した樹脂粒子(導電粒子)を含む導電ペーストなどの導電性接着剤を用いてもよい。

【0162】

上記接合層31・32は、例えば、上記第1導電層(接続電極3もしくは支持体4)上に上記接続材料を塗布あるいは滴下するなどの方法により容易に形成することができる。また、上記接合層31・32は、上記第1導電層の面積よりも該接合層31・32の面積、つまり、該接合層31・32における半導体チップ1との接触面の面積が大きくなるように設けることができる。

【0163】

上記半導体チップ1の電極端子部5の最表層は、通常AlやSiやCuにより構成されるが、上記接合層31・32が半田材料からなる場合にはこれに限らず、NiやCrやTiやWなどの、バリアメタルもしくはアンダーバンプメタルに使用される金属で構成されていてもよい。

【0164】

本実施の形態においては、図7(a)に示すように、接続電極及び支持体として、回路基板2に、上記したように最表層に回路基板2と半導体チップ1とを接続(接合)するための接合層31もしくは接合層32を有する接続電極33及び支持体34を形成したことを除けば、図7(b)〜(d)に示すように、前記実施の形態1に係る半導体装置と同様の実装工程を経て、半導体装置を製造する。

【0165】

本実施の形態においても、上記支持体34における支持層(第1導電層)は、前記実施の形態1同様、上記回路基板2に、接続電極33…における支持層(第1導電層)や配線20などをエッチング等により形成するときに同時に作製することができる。また、上記接合層31及び接合層32もまた、同材料で、同時に形成することができる。

【0166】

さらに、前記実施の形態1同様、本実施の形態においても、図7(b)に示すように、接続電極33…と電極端子部5…とを位置合わせし、上記半導体チップ1と回路基板2とが実質平行に保持され、かつ、上記接続電極33…と電極端子部5…とが接触している状態で、超音波印加ツール7または図示しないステージまたはその併用により、上記半導体チップ1と回路基板2との接合部を100℃〜150℃に加熱し、超音波印加ツール7によって40kHzの超音波を印可して上記接合部に数Nから数十Nの荷重を1秒間程度加えることで、上記接続電極33及び支持体34と半導体チップ1とを安定して接合することができる。また、このとき、半田を使用していれば、より強固な金属接合を行うことができる。

【0167】

なお、本実施の形態においても、上記半導体チップ1と回路基板2との間隙を封止する界面界面封止樹脂としては、液状の界面封止樹脂8を使用し、上記間隙への界面封止樹脂8の注入は、半導体チップ1の側面から行った。また、上記界面封止樹脂8としては、熱硬化性樹脂であるエポキシ樹脂を用いた。

【0168】

以上のように、本実施の形態においては、接続電極及び支持体として、上記接合層31・32を有する接続電極33及び支持体34を用いた。

【0169】

フリップチップ実装において超音波を用いて押圧する方法では、一般的に、電極端子部5の最表層に形成されている金属は、一定の加圧と同時に超音波振動を加えることにより、塑性流動を生じる。この塑性流動には金属の変形と同時に超音波振動による波動的流動も伴っており、このため電極端子部5と接続電極3との両金属界面の酸化膜が破壊され、新生面の接触により接合が生じる。しかし、この超音波による接続では、溶着が加圧の中心部ではなく、その周辺にドーナツ状に生じる。

【0170】

そこで、前記実施の形態1では、液状の界面封止樹脂8を用いて上記接合を強くしたが、本実施の形態では、さらに、上記接続電極3及び支持体4上に上記導電性材料からなる接合層31・32を設けることにより、より強固な金属接合を可能とした。

【0171】

〔実施の形態4〕

本発明にかかるさらに他の実施形態について、図8(a)〜(d)に基づいて説明すれば、以下のとおりである。なお、説明の便宜上、前記実施の形態1乃至実施の形態3にて説明した図面と同じ機能を有する部材については、同じ符号を付記し、その説明を省略する。また、前記実施の形態1乃至実施の形態3で述べた各種の特徴点については、本実施の形態についても組み合わせて適用し得るものとする。

【0172】

図8(a)〜(d)は本実施の形態にかかる半導体装置の製造工程の一例を示す断面図であり、そのうち、図8(d)は、本実施の形態にかかる半導体装置の断面の概略構成を示している。

【0173】

なお、本実施の形態においては、半導体チップの電極端子部が形成される面を表面、電極端子部が形成されない面を裏面と称することとする。

【0174】

本実施の形態にかかる半導体装置は、前記実施の形態2において、導電粒子23…が分散された、フィルム状の異方導電性樹脂に代えて、フィルム状の絶縁樹脂からなる界面封止樹脂47を用いると共に、複数の半導体チップを各半導体チップの厚さ方向に互いに積層してなる構成を有している。

【0175】

本実施の形態にかかる半導体装置は、図8(c)・(d)に示すように、センターパッドを有する第1の半導体チップ41(ベアチップ)が、回路基板43に、上記第1の半導体チップ41に設けられた電極端子部5…に対応して突出して設けられた接続電極3…(第1の接続電極、接続用電極端子部)並びに支持体4…によってフリップチップ実装されていると共に、該フリップチップ実装された第1の半導体チップ41の裏面に、第2の半導体チップ42の裏面を貼り付けた状態で、該第2の半導体チップ42が、金属細線45…により、上記回路基板43におけるソルダレジスト開口部12内に設けられた接続パッド46…(第2の接続電極、接続用電極端子部)に電気的に接続された構成を有している。

【0176】

上記第1の半導体チップ41は、例えば前記実施の形態1〜3に記載の半導体チップ1と同様の構成を有している。また、上記回路基板43は、該回路基板43におけるソルダレジスト開口部12内の半導体チップ形成領域外に、上記ソルダレジスト開口部12に沿って、上記接続パッド46…が設けられていることを除けば、例えば前記実施の形態1または2に記載の回路基板2と同様の構成を有している。

【0177】

なお、上記半導体装置を構成する第2の半導体チップ42の種類、サイズは特に限定されず、任意のものを使用することができる。

【0178】

上記第2の半導体チップ42は、該第2の半導体チップ42における素子面に設けられた電極端子部44…と、上記接続パッド46…とを、上記金属細線45…によりワイヤボンディングすることにより、上記回路基板43と電気的に接続されている。上記第2の半導体チップ42における素子面には、電極端子部44…を除く素子面表面を覆うと共に該素子面表面を平坦化する絶縁膜50が設けられている。本実施の形態では、平面電極(電極パッド)からなる電極端子部44…が、上記第2の半導体チップ42の縁部(端部)に沿って設けられている場合を例に挙げて説明するが、本発明はこれに限定されるものではない。

【0179】

上記電極端子部5・44の材料としては、配線20、接続電極3、及び支持体4の材料と同様、前記実施の形態1〜3にて説明したように、従来の半導体装置において電極や配線に通常使用される材料を用いることができる。具体的には、前記実施の形態1〜3に記載の金属材料などを用いることができる。

【0180】

また、上記第1の半導体チップ41と回路基板43との間隙は、上記絶縁樹脂(第1の絶縁樹脂)からなる界面封止樹脂47により封止されている。上記回路基板43上には、該回路基板43の半導体チップ搭載面(すなわち、上記半導体装置の実装面)を、上記第1の半導体チップ41及び第2の半導体チップ42ごと封止(被覆)する封止樹脂(第2の絶縁樹脂)からなる封止樹脂層49が設けられている。これにより、上記第2の半導体チップ42と上記回路基板43の接続パッド46…とを接続する金属細線45…は、上記半導体装置の実装面を被覆する封止樹脂層49により保護されている。

【0181】

また、上記回路基板43における半導体チップ搭載面(第1面)とは反対側の面(第2面)には、前記回路基板2同様、絶縁体層10(絶縁性部材)が設けられていると共に、半田ボールなどの外部入出力端子53が設けられている。上記外部入出力端子53は、回路基板43並びに該回路基板43の第2面を覆う上記絶縁体層10を貫く貫通孔52を介して該回路基板43の半導体チップ搭載面に設けられた配線20と電気的に接続されている。

【0182】

次に、本実施の形態にかかる上記半導体装置の製造工程の一例について、図8(a)〜(d)に基づいて以下に説明する。

【0183】

先ず、図8(a)に示すように、例えば前記実施の形態1〜3に記載の半導体チップ1及び回路基板2と同様にして上記半導体装置の製造に用いる第1の半導体チップ41及び回路基板43を準備する。但し、本実施の形態においては、同図8(a)に示すように、上記第1の半導体チップ41と回路基板43とを接合する前に、予め、上記上記第1の半導体チップ41の素子面にフィルム状の絶縁樹脂からなる界面封止樹脂47(絶縁樹脂フィルム)を貼り付けておく。

【0184】

また、上記回路基板43におけるソルダレジスト開口部12内には、前記実施の形態1同様、上記第1の半導体チップ41の実装対象領域に、上記第1の半導体チップ41の電極端子部5…に対応した接続電極3…並びにこれら接続電極3とほぼ同じ高さ(厚み)を有する支持体4…を形成すると共に、上記第1の半導体チップ41の実装対象領域外に、上記第1の半導体チップ41上に積層される第2の半導体チップ42(図8(c)参照)における電極端子部44…と接続される接続パッド46…を形成する。

【0185】

上記接続パッド46…もまた、支持体4…同様、上記回路基板43上に、接続電極3…や配線20などをエッチング等により形成するときに同時に作製することができる。

【0186】

上記第1の半導体チップ41と回路基板43との接合(実装)は、前記実施の形態2における半導体チップ1と回路基板2との接合(実装)工程(方法)と同様の工程(方法)により行うことができる。

【0187】

つまり、上記第1の半導体チップ41と回路基板43との接合(実装)は、図8(b)に示すように、上記第1の半導体チップ41の素子面に上記フィルム状の界面封止樹脂47が貼り付けられた状態で上記第1の半導体チップ41の電極端子部5…と回路基板43の接続電極3…とを位置合わせし、上記第1の半導体チップ41と回路基板43とが実質平行に保持され、かつ、上記接続電極3…と電極端子部5…とが接触している状態で、超音波印加ツール7または図示しないステージまたはその併用により加熱状態にて上記第1の半導体チップ41と回路基板43との接合部に超音波を印加して所定の荷重を加えることにより行われる。

【0188】

本実施の形態においても、上記支持体4の高さが接続電極3とほぼ同じ高さであることにより、上記第1の半導体チップ41と回路基板43とを容易に実質平行に保持することができ、上記接続電極3…と電極端子部5…との接触を、安定した状態とすることができる。

【0189】

次に、図8(c)に示すように、フリップチップ接続された上記第1の半導体チップ41の裏面に、接着剤層48を介して、予め準備しておいた第2の半導体チップ42の裏面を貼り付ける。

【0190】

上記接着剤層48に用いられる接着剤としては、例えば液状の接着剤や、シート状の接着剤などを使用することができる。上記接着剤は、上記第1の半導体チップ41の裏面と第2の半導体チップ42の裏面とをその全領域に渡って均一に接着できるものであれば、その種類は問わない。

【0191】

続いて、該第2の半導体チップ42の表面に設けられた電極端子部44…を、金属細線45…により、回路基板43上に設けられた接続パッド46…と電気的に接続する。上記金属細線45の材料については特に限定しないが、Al、Auが好ましい。

【0192】

上記電極端子部44及び接続パッド46と金属細線45とを電気的に接続する方法としては、(1)接続部に熱と圧力とを加え、その境界面で塑性変形を起こさせて両者の接続部での酸化膜崩壊、表面の活性化を促し、両金属間の拡散接合によって金属間化合物を形成させることにより両者を接続する、熱圧着を用いたワイヤボンディング法(熱圧着ワイヤボンディング法)、(2)加圧と超音波の印可とにより接続部を固層溶接する、超音波を用いたワイヤボンディング法(超音波ワイヤボンディング法)、及び(3)熱圧着ワイヤボンディング法に超音波を併用するワイヤボンディング法(超音波併用熱圧着ワイヤボンディング法)などが挙げられるが、特に限定されるものではない。

【0193】

また、上記電極端子部44及び接続パッド46と金属細線45とをワイヤボンディングする順番、つまり、上記第2の半導体チップ42及び回路基板43と金属細線45とをワイヤボンディングする順番も特に限定されないが、回路基板と金属細線とを接続した後に、第半導体チップと金属細線とを接続するいわゆるリバースワイヤボンディング法が、該リバースワイヤボンディング法と逆の順番で接続を行ういわゆるフォワードワイヤボンディング法に比べて、金属細線の高さを低くすることができ、半導体装置をより一層薄型化することができることからより好ましい。

【0194】

リバースワイヤボンディング法を行う場合は、半導体チップに設けられた電極端子上に金バンプを形成し、最初に金属細線と回路基板との接続を行い、その後に上記金属細線と上記金バンプとの接続を行う。

【0195】

但し、上記電極端子部44と接続パッド46とを接続する方法としては、上記方法に限定されるものではない。

【0196】

次に、同図8(c)に示すように、上記電極端子部44と金属細線45との接続部を、絶縁膜51で保護した後、図8(d)に示すように、上記回路基板43の半導体チップ搭載面全面を、封止樹脂(第2の絶縁樹脂)で覆い、該封止樹脂からなる封止樹脂層49で上記金属細線45を保護する。

【0197】

本実施の形態では、固形の熱硬化性樹脂を加熱融解させて金型内に移行、充填させ、硬化させるトランスファーモールド法を用いて、エポキシ樹脂により上記封止樹脂層49を形成した。

【0198】

しかしながら、上記封止樹脂層49の形成方法はこれに限定されるものではなく、例えば、シリンジなどに入った液状の樹脂をディスペンサなどで適量滴下させ、その後加熱硬化させることによって封止するポッティング法、パッケージ内部に液状樹脂を注入する注形法など、任意の方法を適用することができる。また上記封止樹脂の種類も、エポキシ樹脂に限定に限定されるものではなく、任意の熱硬化性樹脂を用いることができる。

【0199】

最後に図8(d)に示すように、回路基板43の裏面に、外部入出力端子53として半田ボールを形成する。なお、外部入出力端子53の種類は特に限定されず、任意のものを使用することができる。

【0200】

なお、本実施の形態では、フリップチップ接続された第1の半導体チップ41の裏面に、第2の半導体チップ42を1つ貼り付けたが、積層される半導体チップの個数はこれに限定されるものではなく、任意の数とすることができる。

【0201】

なお、上記第1の半導体チップ41の裏面に、複数の半導体チップを貼り付ける場合、例えば、第2の半導体チップ42の電極端子部44と第3の半導体チップの電極端子部とを対向配置させてワイヤボンディングさせることにより共通の信号を用いる構成としてもよく、あるいは、上記第2の半導体チップ42よりも小さい第3の半導体チップを、上記第2の半導体チップ42の電極端子部44と接触しないように上記第2の半導体チップ42上に積層する構成としてもよく、従来公知の積層型の半導体装置(半導体装置パッケージ)と同様にして上記半導体チップの積層を行うことができる。

【0202】

このように複数の半導体チップを回路基板に積層することにより、半導体チップの実装密度の高い半導体装置を実現することができる。

【0203】

また、本実施の形態では、上記界面封止樹脂47に絶縁性樹脂を用いたが、上記界面封止樹脂47としては、これに限定されるものではなく、前記実施の形態1〜3で使用した界面封止樹脂と同様の界面封止樹脂を用いることができる。また、上記界面封止樹脂47としては、フィルム状の界面封止樹脂を用いたが、該界面封止樹脂としては、前記実施の形態1及び3に示すように液状であってもよく、また、ペースト状であってもよい。

【0204】

さらに、上記各実施の形態においては、電極の塑性変形を伴う接合方法として、超音波接合を用いた場合を例に挙げて説明したが、本発明は、これに限定されるものではなく、例えば、超音波、熱、圧力の何れか、またはそれらを併用し、超音波、熱、圧力のうち少なくとも1つを上記半導体チップと回路基板との接合部に与える(印加する)ことにより、突起状に形成された上記電極端子部及び上記支持体の塑性変形による上記半導体チップと回路基板との接合を行うことができる。

【0205】

また、上記接合条件としては、上記電極材料(上記各実施の形態においては接続電極並びに支持体の材料)に応じて、該電極材料が、半導体チップとの接合部において塑性変形するように接合条件を適宜設定すればよい。言い換えれば、上記接合条件において塑性変形する材料により上記電極を形成すればよい。

【0206】

上記接合に超音波を用いた場合、短時間で金属接合が可能であり、生産性及び接続信頼性をより一層向上させることができる。

【0207】

また、上記した各実施の形態では、超音波を用いて電極端子部を塑性変形させることにより上記半導体チップと回路基板とを接合する場合を例に挙げて説明したが、本発明はこれに限定されるものではなく、半導体チップの電極端子部と接続用電極端子部とを圧接させて電気的に接続すると共に上記半導体チップと回路基板とを界面封止樹脂により固着させる場合にも適用することができる。

【0208】

具体的には、例えば、前記実施の形態2において、接合条件を変更、つまり、超音波印加ツール7に代えて加熱加圧ツールを使用し、上記半導体チップ1と回路基板2とを位置合わせした状態で、上記加熱加圧ツールにより上記半導体チップ1が搭載された回路基板2を一定時間保持して異方導電性樹脂からなる界面封止樹脂21(異方導電性樹脂フィルム)を硬化させることにより、上記半導体チップ1の電極端子部5と回路基板2の接続電極3とを圧接により電気的に接続することができる。また、この場合、上記実施の形態2において、界面封止樹脂21に代えて、ペースト状の異方導電性樹脂からなる界面封止樹脂、もしくは、フィルム状あるいはペースト状の絶縁性樹脂を用いてもよいことは言うまでもない。

【0209】

なお、上記半導体チップ1のフリップチップ実装に際し、超音波などを用いて電極端子部の塑性変形を伴う接合を行う場合、上記支持体4の材料としては、少なくともその最表層に、例えば前記実施の形態1〜4に記載したように、半導体チップ1のフリップチップ実装条件において塑性変形する材料が用いられるが、上記半導体チップ1における電極端子部5と回路基板2における接続電極3とを圧接により接合する場合には、上記支持体4の材料としては、上記半導体チップ1を、上記回路基板2と実質平行に支持することができるものであればよい。

【0210】

この場合、上記支持体4の材料としては、圧接による接合条件において塑性変形しないものであればよく、前記実施の形態1〜4と同様の材料を用いることができる。

【0211】

上記半導体チップ1における電極端子部5と回路基板2における接続電極3とを圧接により接合する場合にも、制御の容易さから、上記支持体4の材料のなかでも、特に好ましい材料は、上記の観点から上記接続電極3と同じ材料であり、そのなかでも特に、支持体4の高さ(厚み)の制御が容易であり、また、金属接合により上記接続電極3と電極端子部5とを強固に安定してかつ短時間で接合することができることから、最も好ましくは金属材料である。

【0212】

以上のように、本発明の実施の一形態にかかる半導体装置の製造方法は、素子形成面の中央部に電極端子部が設けられた半導体チップを、上記電極端子部にて、上記半導体チップよりも大きく、かつ、表面に絶縁体層が設けられた回路基板における接続用電極端子部に架設状態でフリップチップ実装する半導体装置の製造方法において、上記回路基板表面に、該回路基板における上記半導体チップのフリップチップ実装対象領域に上記半導体チップの素子形成面よりも大きな開口部を有する絶縁体層を形成し、上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部を突起状に形成すると共に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、突起状に形成された上記電極端子部とほぼ同じ高さを有し、上記半導体チップと回路基板とを実質平行に支持する支持体を形成し、突起状に形成された上記電極端子部と支持体とによって、上記回路基板における上記絶縁体層の開口部内で上記半導体チップと回路基板とを実質平行に支持してフリップチップ実装を行う方法である。

【0213】

より具体的には、上記回路基板表面に、該回路基板における上記半導体チップのフリップチップ実装対象領域に上記半導体チップの素子形成面よりも大きな開口部を有する絶縁体層を形成し、上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部を突起状に形成すると共に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、突起状に形成された上記電極端子部とほぼ同じ高さを有し、かつ、少なくとも最表層が上記半導体チップのフリップチップ実装による上記接続用電極端子部との接合条件で塑性変形すると共に、該塑性変形による変形量が、突起状に形成された上記電極端子部とほぼ同じ材料からなり、上記半導体チップと回路基板とを実質平行に支持する支持体を形成し、突起状に形成された上記電極端子部と支持体とによって、上記回路基板における上記絶縁体層の開口部内で上記半導体チップと回路基板とを架設状態で実質平行に支持し、突起状に形成された上記電極端子部及び上記支持体を塑性変形させて上記半導体チップと回路基板とを接合する方法である。

【0214】

また、上記半導体装置の製造方法は、上記回路基板表面に、該回路基板における上記半導体チップのフリップチップ実装対象領域に上記半導体チップの素子形成面よりも大きな開口部を有する絶縁体層を形成し、上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部を突起状に形成すると共に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、突起状に形成された上記電極端子部とほぼ同じ高さを有し、上記半導体チップの素子形成面と上記回路基板表面とを実質平行に支持する支持体を形成し、突起状に形成された上記電極端子部と支持体とによって、上記回路基板における上記絶縁体層の開口部内で、上記半導体チップと回路基板とを架設状態で実質平行に支持した状態で、上記半導体チップと回路基板との間隙を界面封止樹脂により封止して上記接続用電極端子部と上記半導体チップの電極端子部とを圧接させる方法であってもよい。

【0215】

さらには、上記半導体装置の製造方法は、素子形成面の中央部に形成された複数の電極(電極端子部)を含む半導体チップが第1の面及び第2の面を有し、該半導体チップが、上記第1の面に支持体が形成された回路基板上に搭載されてなる半導体装置の製造方法であって、上記回路基板の接続パッド(接続用電極端子部)の周辺に形成された支持体により、上記半導体チップが、上記回路基板に対し、ほぼ平行になる状態で、上記半導体チップの素子形成面の中央部付近に形成された複数の電極と、上記回路基板の第1の面に、上記半導体チップの複数の電極にそれぞれ対応して配置された突起を有する複数の接続パッドとを、超音波、熱、圧力の何れか、またはそれらの併用により、直接または部材を介して、電気的に接続する工程と、上記半導体チップの素子形成面と上記回路基板との間隙に界面封止樹脂を注入する工程と、該界面封止樹脂を硬化させる工程とを含む方法であってもよい。

【0216】

また、上記半導体装置の製造方法は、素子形成面の中央部に形成された複数の電極(電極端子部)を含む半導体チップが第1の面及び第2の面を有し、該半導体チップが、上記第1の面に支持体が形成された回路基板上に搭載されてなる半導体装置の製造方法であって、上記回路基板の接続パッド(接続用電極端子部)の周辺に形成された支持体により、上記半導体チップが、上記回路基板に対し、ほぼ平行になる状態で、かつ、予め半導体チップまたは上記回路基板に、界面封止樹脂シートまたは界面封止樹脂ペーストを配置する工程と、上記半導体チップの素子形成面の中央部に形成された複数の電極と、上記回路基板の第1の面に、上記半導体チップの複数の電極にそれぞれ対応して配置された突起を有する複数の接続パッドとを、超音波、熱、圧力の何れか、またはそれらの併用により、直接または部材を介して、電気的に接続すると同時に、界面封止樹脂の硬化を行う、または、少なくとも開始させる工程と、必要に応じて、一括してオーブン等で、該界面封止樹脂の硬化を促進させる工程とを含む方法であってもよい。

【0217】

さらには、上記半導体装置の製造方法は、上記回路基板の上記第1の面に、上記半導体チップの複数の電極(電極端子部)にそれぞれ対応して配置された突起を有する複数の接続パッド(接続用電極端子部)を、エッチングやメッキ工程で形成すると同時に、同工程により支持体を形成する方法であってもよい。

【0218】

また、上記半導体装置の製造方法は、上記半導体チップの素子形成面と上記回路基板との間隙に設けられる樹脂が異方導電性を有し、上記回路基板の接続パッドの周辺に形成された支持体により、上記半導体チップが、上記回路基板に対してほぼ平行になる状態で、上記半導体チップの素子形成面の中央部に形成された複数の電極(電極端子部)と、上記回路基板の第1の面に、上記半導体チップの複数の電極にそれぞれ対応して配置された突起を有する複数の接続パッド(接続用電極端子部)とを、超音波を必ず印可し、熱、圧力の何れか、またはそれらの併用により電気的に接続すると同時に、界面封止樹脂の硬化を行う、または、少なくとも開始させる工程とを含む方法であってもよい。

【0219】

また、上記半導体装置の製造方法は、上記回路基板の第1の面に形成された突起を有する接続パッド(接続用電極端子部)と、支持体の最表層に導電性材料が形成されていて、上記回路基板の接続パッドの周辺に形成された支持体により、上記半導体チップが、上記回路基板に対し、ほぼ平行になる状態で、上記半導体チップの素子形成面の中央部に形成された複数の電極(電極端子部)と、上記回路基板の第1の面に、上記半導体チップの複数の電極にそれぞれ対応して配置された突起を有する複数の接続パッドとを、超音波を必ず印可し、熱、圧力の何れか、またはそれらの併用により電気的に接続すると同時に、界面封止樹脂の硬化を行う、または、少なくとも開始させる工程とを含む方法であってもよい。

【0220】

さらに、本発明の一実施形態にかかる半導体装置は、例えば以下の構成とすることができる。

【0221】

例えば、上記半導体装置は、半導体チップが、素子形成面の中央部に形成された複数の電極(電極端子部)を含み、第1の面および第2の面を有し、かつ、共に表層は絶縁体層が形成された、上記半導体チップを搭載する回路基板を備え、上記回路基板は、上記第1の面に、上記半導体チップの複数の電極にそれぞれ対応して配置された突起を有する複数の接続パッド(接続用電極端子部)と、上記接続パッドとほぼ同じ高さで、上記接続パッド周辺に形成された支持体と、上記接続パッドと電気的に接続された複数の外部入出力端子と、上記絶縁体層には、少なくとも上記半導体チップよりも大きな開口部を備え、上記半導体装置の素子面と前記回路基板との間隙に設けられる樹脂を備え、上記半導体チップの電極と、上記回路基板の接続パッドをフリップチップ方式で、直接または部材を介して、電気的に接続する構造を有していてもよい。

【0222】

また、上記素子形成面の中央部に形成された複数の電極(電極端子部)が、ほぼ直鎖状に形成されている場合、上記支持体が、上記電極に対応した直鎖状の接続パッド(接続用電極端子部)の片側、または両側に配置されている構成であってもよい。

【0223】

さらに、上記半導体装置は、上記フリップチップ接続された半導体チップの裏面に、少なくとも1つ以上の半導体チップが積層され、上記積層された半導体チップの電極(電極端子部)と、上記回路基板上の上記半導体チップの外側に配置された接続パッド(接続用電極端子部)がそれぞれ金属細線で結線され、上記回路基板の半導体チップが実装されている面が、封止樹脂で覆われている構成であってもよい。

【0224】

また、上記した各実施の形態では、突起構造を有する電極(上記各実施の形態においては接続電極)と支持体とが、共に回路基板に形成されている場合を例に挙げて説明したが、本発明はこれに限定されるものではなく、突起構造を有する電極と支持体とが、例えば半導体チップの素子形成面に形成されている配線を利用するなどして共に半導体チップに形成されている構成としてもよく、突起構造を有する電極と支持体とが、回路基板と半導体チップとに各々別々に設けられている構成としても構わない。

【0225】

但し、上記突起構造を有する電極と支持体とは、回路基板または半導体チップの何れか一方に設けられていることが、両者の高さを制御、つまり、両者の高さを合わせる上で好ましく、上記突起構造を有する電極と支持体とが共に回路基板側に設けられていることが、回路基板における配線を利用して例えば該配線と同一材料にて同時に上記突起構造を有する電極と支持体とを形成することができ、厚みの制御が容易となり、安価かつ精度良く上記突起構造を有する電極と支持体とを形成することができる。

【0226】

本発明は上述した各実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能であり、異なる実施形態にそれぞれ開示された技術的手段を適宜組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。

【0227】

【発明の効果】

本発明にかかる半導体装置は、以上のように、素子形成面の中央部に電極端子部が設けられた半導体チップが、上記電極端子部にて、回路基板の接続用電極端子部に架設状態でフリップチップ実装されており、上記回路基板は、上記半導体チップよりも大きく、かつ、表面に絶縁体層が設けられている半導体装置において、上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部が突起状に形成されており、上記回路基板表面の絶縁体層は、上記半導体チップの素子形成面よりも大きな開口部を備え、該開口部内で上記半導体チップと回路基板とが架設状態でフリップチップ実装されており、上記半導体チップと回路基板との間隙には、突起状に形成された上記電極端子部とほぼ同じ高さを有し、上記半導体チップと回路基板とを実質平行に支持する支持体が設けられている構成である。

【0228】

上記の構成によれば、上記絶縁体層が、上記半導体チップの素子形成面よりも大きな開口部を有し、上記絶縁体層と半導体チップとが互いに非接触状態にて上記半導体チップが上記接続用電極端子部にフリップチップ実装されるので、上記支持体並びに突起形状を有する電極端子部の形成に際し、上記絶縁体層による制限を受けず、しかも、上記絶縁体層とは別に上記支持体が設けられていることから、該支持体の形成に際し、材料の選択の自由度が大きく、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより厳密に制御することが可能となるので、上記したように中央部にセンターパッドと称される電極端子部を有する半導体チップを回路基板にフリップチップ実装するに際し、半導体チップの素子形成面と回路基板とを実質的に平行に支持した状態で、安定して固定することができる。よって、上記の構成によれば、半導体チップと回路基板との接続不良が防止され、接続信頼性が高い半導体装置を提供することができるという効果を奏する。

【0229】

本発明にかかる半導体装置は、以上のように、上記支持体は、突起状に形成された電極端子部と同じ材料からなる構成である。

【0230】

上記の構成によれば、上記支持体が、突起状に形成された電極端子部と同じ材料からなることで、既存の技術により、両者の高さを容易に一致させることができる。このため、より一層接続信頼性が高い半導体装置を提供することができるという効果を奏する。

【0231】

本発明にかかる半導体装置は、以上のように、上記支持体は金属からなる構成である。

【0232】

金属材料は、その厚さをエッチング加工する技術が特に充実しており、厚みの制御を容易に行うことができるので、上記支持体が金属からなることで、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより一層厳密かつ容易に制御することができる。よって、上記の構成によれば、より接続信頼性が高い半導体装置を提供することができるという効果を奏する。

【0233】

本発明にかかる半導体装置は、以上のように、上記半導体チップと回路基板とが、突起状に形成された上記電極端子部及び上記支持体の塑性変形により接合されている構成である。

【0234】

上記の構成によれば、超音波接合などの、電極端子部の塑性変形を伴う接合を行う場合であっても上記半導体チップのフリップチップ実装を行う際に、上記半導体チップを上記回路基板と平行に支持することができるので、塑性変形によって強固に接続され、半導体チップと回路基板との位置ズレがなく、接続不良が防止され、接続信頼性が高い半導体装置を提供することができるという効果を奏する。

【0235】

本発明にかかる半導体装置は、以上のように、上記半導体チップと回路基板とが、該半導体チップと回路基板との間隙を封止する界面封止樹脂によりさらに固着されている構成である。

【0236】

上記の構成によれば、上記半導体チップと回路基板との間隙を上記界面封止樹脂によりさらに固着することで、両者の接合をより強固で安定したものとすることができるという効果を奏する。

【0237】

本発明にかかる半導体装置は、以上のように、上記接続用電極端子部と半導体チップの電極端子部とが架設状態で圧接されており、上記半導体チップと回路基板とが、該半導体チップと回路基板との間隙を封止する界面封止樹脂により固着されている構成である。

【0238】

上記の構成によれば、上記絶縁体層が、上記半導体チップの素子形成面よりも大きな開口部を有し、上記絶縁体層と半導体チップとが互いに非接触状態にて上記半導体チップが上記接続用電極端子部にフリップチップ実装されるので、上記支持体並びに突起形状を有する電極端子部の形成に際し、上記絶縁体層による制限を受けず、しかも、上記絶縁体層とは別に上記支持体が設けられていることから、該支持体の形成に際し、材料の選択の自由度が大きく、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより厳密に制御することが可能となる。このため、上記のように半導体チップの電極端子部と接続用電極端子部とを圧接させて電気的に接続すると共に上記半導体チップと回路基板とを界面封止樹脂により固着させる場合においても、上記したように中央部にセンターパッドと称される電極端子部を有する半導体チップを回路基板にフリップチップ実装するに際し、半導体チップの素子形成面と回路基板とを実質的に平行に支持した状態で、安定して固定することができる。よって、上記の構成によれば、半導体チップと回路基板との接続不良が防止され、接続信頼性が高い半導体装置を提供することができるという効果を奏する。

【0239】

本発明にかかる半導体装置は、以上のように、上記支持体と半導体チップとの接触面積が、突起状に形成された上記電極端子部と半導体チップとの接触面積よりも大きい構成である。

【0240】

上記の構成によれば、上記支持体と半導体チップとの接触面積を、突起状に形成された上記電極端子部と半導体チップとの接触面積よりも大きくすることで、上記支持体が上記半導体チップの素子形成面に当たることによるダメージを軽減することができるという効果を奏する。

【0241】

本発明にかかる半導体装置は、以上のように、上記半導体チップの素子形成面とは反対側の面に少なくとも1つの半導体チップが積層され、該積層された半導体チップの電極端子部と、上記回路基板における上記絶縁体層の開口部内でかつ上記半導体チップのフリップチップ実装領域外に設けられた接続用電極端子部とが金属細線により電気的に接続されている構成である。

【0242】

上記の構成によれば、上記半導体装置1個当たりの半導体チップの搭載数が増加し、上記半導体チップの実装密度がより高い半導体装置を実現することができるという効果を奏する。

【0243】

本発明にかかる半導体装置の製造方法は、以上のように、素子形成面の中央部に電極端子部が設けられた半導体チップを、上記電極端子部にて、上記半導体チップよりも大きく、かつ、表面に絶縁体層が設けられた回路基板における接続用電極端子部に架設状態でフリップチップ実装する半導体装置の製造方法において、上記回路基板表面に、該回路基板における上記半導体チップのフリップチップ実装対象領域に上記半導体チップの素子形成面よりも大きな開口部を有する絶縁体層を形成し、上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部を突起状に形成すると共に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、突起状に形成された上記電極端子部とほぼ同じ高さを有し、上記半導体チップと回路基板とを実質平行に支持する支持体を形成し、突起状に形成された上記電極端子部と支持体とによって、上記回路基板における上記絶縁体層の開口部内で上記半導体チップと回路基板とを実質平行に支持してフリップチップ実装を行う方法である。

【0244】

上記の方法によれば、上記絶縁体層が、上記半導体チップの素子形成面よりも大きな開口部を有することで、上記絶縁体層と半導体チップとを互いに非接触状態にて上記半導体チップを上記接続用電極端子部にフリップチップ実装することができるので、上記支持体並びに突起形状を有する電極端子部の形成に際し、上記絶縁体層による制限を受けず、しかも、上記絶縁体層とは別に上記支持体を設けることで、該支持体の形成に際し、材料の選択の自由度が大きく、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより厳密に制御することが可能となるので、上記したように中央部にセンターパッドと称される電極端子部を有する半導体チップを回路基板にフリップチップ実装するに際し、半導体チップの素子形成面と回路基板とを実質的に平行に支持した状態で、安定して固定することができる。よって、上記の方法によれば、半導体チップと回路基板との接続不良を防止することができ、接続信頼性が高い半導体装置を提供することができるという効果を奏する。

【0245】

本発明にかかる半導体装置の製造方法は、以上のように、素子形成面の中央部に電極端子部が設けられた半導体チップを、上記電極端子部にて、上記半導体チップよりも大きく、かつ、表面に絶縁体層が設けられた回路基板における接続用電極端子部に架設状態でフリップチップ実装する半導体装置の製造方法において、上記回路基板表面に、該回路基板における上記半導体チップのフリップチップ実装対象領域に上記半導体チップの素子形成面よりも大きな開口部を有する絶縁体層を形成し、上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部を突起状に形成すると共に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、突起状に形成された上記電極端子部とほぼ同じ高さを有し、かつ、少なくとも最表層が上記半導体チップのフリップチップ実装による上記接続用電極端子部との接合条件で塑性変形すると共に、該塑性変形による変形量が、突起状に形成された上記電極端子部とほぼ同じ材料からなり、上記半導体チップと回路基板とを実質平行に支持する支持体を形成し、突起状に形成された上記電極端子部と支持体とによって、上記回路基板における上記絶縁体層の開口部内で上記半導体チップと回路基板とを架設状態で実質平行に支持し、突起状に形成された上記電極端子部及び上記支持体を塑性変形させて上記半導体チップと回路基板とを接合する方法である。

【0246】

上記の方法によれば、上記絶縁体層が、上記半導体チップの素子形成面よりも大きな開口部を有することで、上記絶縁体層と半導体チップとを互いに非接触状態にて上記半導体チップを上記接続用電極端子部にフリップチップ実装することができるので、上記支持体並びに突起形状を有する電極端子部の形成に際し、上記絶縁体層による制限を受けず、しかも、上記絶縁体層とは別に上記支持体を設けることで、該支持体の形成に際し、材料の選択の自由度が大きく、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより厳密に制御することが可能となる。

【0247】

このため、上記の方法によれば、上述したように、超音波接合などの、電極端子部の塑性変形を伴う接合を行う場合であっても、上記したように中央部にセンターパッドと称される電極端子部を有する半導体チップを回路基板にフリップチップ実装するに際し、半導体チップの素子形成面と回路基板とを実質的に平行に支持した状態で、安定して固定することができる。よって、上記の方法によれば、半導体チップと回路基板との接続不良を防止することができ、接続信頼性が高い半導体装置を製造することができるという効果を奏する。

【0248】

本発明にかかる半導体装置の製造方法は、以上のように、突起状に形成された上記電極端子部及び上記支持体を塑性変形させて上記半導体チップと回路基板とを接合させた後、上記半導体チップと回路基板との間隙に、該間隙を封止する界面封止樹脂を注入し、該界面封止樹脂を硬化させる方法である。

【0249】

上記の方法によれば、上記半導体チップと回路基板との間隙を上記界面封止樹脂によりさらに固着することができ、両者の接合をより強固で安定したものとすることができるという効果を奏する。また上記の構成によれば、前記したように、上記回路基板表面の絶縁体層が、上記半導体チップのフリップチップ実装領域(実装対象領域)において上記半導体チップの素子形成面よりも大きく開口されていることで、上記半導体チップを上記接続用電極端子部にフリップチップ実装したとき、上記半導体チップと回路基板との間隙に、容易に上記界面封止樹脂を注入することができるという効果を奏する。

【0250】

本発明にかかる半導体装置の製造方法は、以上のように、素子形成面の中央部にほぼ直鎖状に複数の電極端子部が設けられた半導体チップを使用し、上記回路基板に、上記半導体チップの電極端子部に対応してほぼ直鎖状に複数の接続用電極端子部を設けると共に、上記接続用電極端子部からなる列の片側に、上記接続用電極端子部と平行に上記支持体を形成し、上記半導体チップと回路基板とを接合後に、上記支持体が形成された側とは上記接続用電極端子部を挟んで反対側、もしくは、上記接続用電極端子部からなる列に対し、ほぼ直交する方向から上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入する方法である。

【0251】

上記の方法によれば、上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入することで、上記半導体チップと回路基板とを、より強固に安定して接合することができるという効果を奏する。また、上記の方法によれば、上記支持体を、上記接続用電極端子部からなる列の片側に、上記接続用電極端子部と平行に上記支持体を形成し、上記支持体が形成された側とは上記接続用電極端子部を挟んで反対側、もしくは、上記接続用電極端子部からなる列に対し、ほぼ直交する方向から上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入することで、該界面封止樹脂の注入性を向上させることができ、効率良く、しかも、上記間隙に上記界面封止樹脂を満遍なく充填させることができるという効果を併せて奏する。

【0252】

本発明にかかる半導体装置の製造方法は、以上のように、素子形成面の中央部にほぼ直鎖状に複数の電極端子部が設けられた半導体チップを使用し、上記回路基板に、上記半導体チップの電極端子部に対応してほぼ直鎖状に複数の接続用電極端子部を設けると共に、上記接続用電極端子部からなる列の両側に、上記接続用電極端子部と平行に上記支持体を形成し、上記半導体チップと回路基板とを接合後に、上記接続用電極端子部からなる列に対し、ほぼ直交する方向から上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入する方法である。

【0253】

上記の方法によれば、上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入することで、上記半導体チップと回路基板とを、より強固に安定して接合することができるという効果を奏する。また、上記の方法によれば、上記支持体を、上記接続用電極端子部からなる列の両側に、上記接続用電極端子部と平行に上記支持体を形成し、上記接続用電極端子部からなる列に対し、ほぼ直交する方向から上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入することで、該界面封止樹脂の注入性を向上させることができ、効率良く、しかも、上記間隙に上記界面封止樹脂を満遍なく充填させることができるという効果を併せて奏する。

【0254】

本発明にかかる半導体装置の製造方法は、以上のように、突起状に形成された上記電極端子部と支持体とによって上記半導体チップと回路基板とを支持する前に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、上記半導体チップと回路基板との間隙を封止する界面封止樹脂からなる層を配し、上記間隙に界面封止樹脂からなる層が配された状態で、突起状に形成した上記電極端子部と上記支持体とによって、上記半導体チップと回路基板とを架設状態で実質平行に支持し、突起状に形成された上記電極端子部及び上記支持体の塑性変形と上記界面封止樹脂の硬化とを、同一の工程において行う方法である。

【0255】

上記の方法によれば、上記半導体チップと回路基板との間隙を上記界面封止樹脂によって封止することで、上記半導体チップと回路基板とを、より強固に安定して接合することができるという効果を奏する。また、上記の方法によれば、上記半導体チップの電極端子部と接続用電極端子部との電気的な接続と上記界面封止樹脂の硬化とを同時進行させることができるので、上記間隙を界面封止樹脂で封止する場合における半導体チップの実装にかかる時間を短縮させることができるという効果を併せて奏する。

【0256】

本発明にかかる半導体装置の製造方法は、以上のように、上記接続用電極端子部及び半導体チップの電極端子部のうち突起状に形成する電極端子部と支持体との最表層に、導電性接着剤からなる接合層を各々設ける方法である。

【0257】

上記の方法によれば、上記接続用電極端子部及び半導体チップの電極端子部のうち突起状に形成する電極端子部と支持体との最表層に上記接合層を設けることで、両者の接合をより強固で安定したものとすることができるという効果を奏する。

【0258】

本発明にかかる半導体装置の製造方法は、以上のように、素子形成面の中央部に電極端子部が設けられた半導体チップを、上記電極端子部にて、上記半導体チップよりも大きく、かつ、表面に絶縁体層が設けられた回路基板における接続用電極端子部に架設状態でフリップチップ実装する半導体装置の製造方法において、上記回路基板表面に、該回路基板における上記半導体チップのフリップチップ実装対象領域に上記半導体チップの素子形成面よりも大きな開口部を有する絶縁体層を形成し、上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部を突起状に形成すると共に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、突起状に形成された上記電極端子部とほぼ同じ高さを有し、上記半導体チップの素子形成面と上記回路基板表面とを実質平行に支持する支持体を形成し、突起状に形成された上記電極端子部と支持体とによって、上記回路基板における上記絶縁体層の開口部内で、上記半導体チップと回路基板とを架設状態で実質平行に支持した状態で、上記半導体チップと回路基板との間隙を界面封止樹脂により封止して上記接続用電極端子部と上記半導体チップの電極端子部とを圧接させる方法である。

【0259】

上記の方法によれば、上記絶縁体層が、上記半導体チップの素子形成面よりも大きな開口部を有することで、上記絶縁体層と半導体チップとを互いに非接触状態にて上記半導体チップを上記接続用電極端子部にフリップチップ実装することができるので、上記支持体並びに突起形状を有する電極端子部の形成に際し、上記絶縁体層による制限を受けず、しかも、上記絶縁体層とは別に上記支持体を設けることで、該支持体の形成に際し、材料の選択の自由度が大きく、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより厳密に制御することが可能となる。このため、上記の方法によれば、上記のように半導体チップの電極端子部と接続用電極端子部とを圧接させて電気的に接続すると共に上記半導体チップと回路基板とを界面封止樹脂により固着させる場合においても、上記したように中央部にセンターパッドと称される電極端子部を有する半導体チップを回路基板にフリップチップ実装するに際し、半導体チップの素子形成面と回路基板とを実質的に平行に支持した状態で、安定して固定することができるという効果を奏する。

【0260】

本発明にかかる半導体装置の製造方法は、以上のように、上記界面封止樹脂として、内部に導電粒子が分散された異方導電性樹脂を用いる方法である。

【0261】

上記の方法によれば、上記異方導電性樹脂中に存在する導電粒子により、より良好な電気的接続を得ることができるという効果を奏する。特に、超音波などを用いて電極端子部を塑性変形させることにより上記半導体チップのフリップチップ実装を行う場合、上記半導体チップの電極端子部と接続用電極端子部との接合部に上記導電粒子が埋め込まれ、該導電粒子により、より良好な電気的接続を得ることができる。

【0262】

本発明にかかる半導体装置の製造方法は、以上のように、上記接続用電極端子部及び半導体チップの電極端子部のうち突起状に形成する電極端子部と支持体とを、同じ材料で形成する方法である。

【0263】

上記の方法によれば、上記支持体を、突起状に形成された電極端子部と同じ材料で形成することで、既存の技術により、両者の高さを容易に一致させることができる。このため、上記の方法によれば、より一層接続信頼性が高い半導体装置を製造することができるという効果を奏する。また、上記の方法によれば、上記支持体と、突起状に形成された電極端子部とを、同一工程、例えばエッチング加工やメッキ等の基板配線の形成工程において同時に形成することが可能になるので、工程数の増加を招くこともなく、安価かつ容易に上記支持体を形成することができるという効果を併せて奏する。

【0264】

本発明にかかる半導体装置の製造方法は、以上のように、上記支持体を金属で形成する方法である。

【0265】

上記の方法によれば、上記支持体を金属で形成することで、電気的な接続の信頼性に関わる高さ方向のばらつきの防止や厚みをより一層厳密かつ容易に制御することが可能となるので、より接続信頼性が高い半導体装置を製造することができるという効果を奏する。

【0266】

本発明にかかる半導体装置の製造方法は、以上のように、上記接続用電極端子部及び半導体チップの電極端子部のうち上記接続用電極端子部を突起状に形成すると共に、上記接続用電極端子部の形成工程と同一の工程で上記回路基板に上記支持体を形成する方法である。

【0267】

上記の方法によれば、上記支持体と、突起状に形成された電極端子部とを、例えばエッチング加工やメッキ等の基板配線の形成工程において、配線の形成と同時に、あるいは、上記配線を利用して形成することが可能になるので、工程数の増加を招くこともなく、安価かつ容易に上記支持体を形成することができるという効果を奏する。また、上記の方法によれば、既存の技術により、両者の高さを容易に一致させることができる。このため、上記の方法によれば、より一層接続信頼性が高い半導体装置を、安価かつ容易に製造することができるという効果を併せて奏する。

【図面の簡単な説明】

【図1】(a)〜(d)は本発明の実施の一形態にかかる半導体装置の製造工程の一例を示す断面図である。

【図2】図1(a)〜(d)に示す半導体チップの素子形成面の概略構成を示す平面図である。

【図3】図1(a)〜(d)に示す回路基板の概略構成を示す平面図である。

【図4】図3に示す回路基板の要部の構成を概略的に示す断面図である。

【図5】図5(a)〜(c)は本発明の他の実施の形態にかかる半導体装置の製造工程の一例を示す断面図である。

【図6】図5(c)に示す半導体装置の要部の構成を概略的に示す断面図である。

【図7】図7(a)〜(d)は本発明のさらに他の実施の形態にかかる半導体装置の製造工程の一例を示す断面図である。

【図8】図8(a)〜(d)は本発明のさらに他の実施の形態にかかる半導体装置の製造工程の一例を示す断面図である。

【図9】従来の半導体装置の構成を概略的に示す断面図である。

【図10】図10(a)〜(c)は従来のフリップチップ実装方法を用いた半導体装置の製造方法に超音波接合を適用したときの半導体装置の製造工程を示す断面図である。

【符号の説明】

1 半導体チップ

2 回路基板

3 接続電極(接続用電極端子部)

4 支持体

5 電極端子部

6 絶縁体層

7 超音波印加ツール

8 界面封止樹脂

9 ノズル

10 絶縁体層

11 貫通孔

12 ソルダレジスト開口部

13 絶縁膜

20 配線

21 界面封止樹脂

22 バインダー樹脂

23 導電粒子

31 接合層

32 接合層

33 接続電極(接続用電極端子部)

34 支持体

41 第1の半導体チップ

42 第2の半導体チップ

43 回路基板

44 電極端子部

46 接続パッド(接続用電極端子部)

47 界面封止樹脂

48 接着剤層

49 封止樹脂層

50 絶縁膜

51 絶縁膜

52 貫通孔

53 外部入出力端子

Claims (20)

- 素子形成面の中央部のみに直鎖状に配置された、回路基板との電気的な接続を形成するための電極端子部が設けられた半導体チップが、上記電極端子部にて、上記回路基板の接続用電極端子部に架設状態でフリップチップ実装されており、上記回路基板は、上記半導体チップよりも大きく、かつ、表面に絶縁体層が設けられている半導体装置において、

上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部が突起状に形成されており、

上記回路基板表面の絶縁体層は、上記半導体チップの素子形成面よりも大きな開口部を備え、該開口部内で上記半導体チップと回路基板とが架設状態でフリップチップ実装されており、

上記半導体チップと回路基板との間隙には、突起状に形成された上記電極端子部とほぼ同じ高さを有し、上記半導体チップと回路基板とを実質平行に支持する支持体が設けられており、上記支持体として上記回路基板の配線が用いられていることを特徴とする半導体装置。 - 上記支持体は、突起状に形成された電極端子部と同じ材料からなることを特徴とする請求項1記載の半導体装置。

- 上記支持体は金属からなることを特徴とする請求項1または2記載の半導体装置。

- 上記半導体チップと回路基板とが、突起状に形成された上記電極端子部及び上記支持体の塑性変形により接合されていることを特徴とする請求項1〜3の何れか1項に記載の半導体装置。

- 上記半導体チップと回路基板とが、該半導体チップと回路基板との間隙を封止する界面封止樹脂によりさらに固着されていることを特徴とする請求項4記載の半導体装置。

- 上記接続用電極端子部と半導体チップの電極端子部とが架設状態で圧接されており、

上記半導体チップと回路基板とが、該半導体チップと回路基板との間隙を封止する界面封止樹脂により固着されていることを特徴とする請求項1〜3の何れか1項に記載の半導体装置。 - 上記支持体と半導体チップとの接触面積が、突起状に形成された上記電極端子部と半導体チップとの接触面積よりも大きいことを特徴とする請求項1記載の半導体装置。

- 上記半導体チップの素子形成面とは反対側の面に少なくとも1つの半導体チップが積層され、該積層された半導体チップの電極端子部と、上記回路基板における上記絶縁体層の開口部内でかつ上記半導体チップのフリップチップ実装領域外に設けられた接続用電極端子部とが金属細線により電気的に接続されていることを特徴とする請求項1記載の半導体装置。

- 素子形成面の中央部のみに直鎖状に配置された、回路基板との電気的な接続を形成するための電極端子部が設けられた半導体チップを、上記電極端子部にて、上記上記半導体チップよりも大きく、かつ、表面に絶縁体層が設けられた回路基板における接続用電極端子部に架設状態でフリップチップ実装する半導体装置の製造方法において、

上記回路基板表面に、該回路基板における上記半導体チップのフリップチップ実装対象領域に上記半導体チップの素子形成面よりも大きな開口部を有する絶縁体層を形成し、上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部を突起状に形成すると共に、

上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、突起状に形成された上記電極端子部とほぼ同じ高さを有し、上記半導体チップと回路基板とを実質平行に支持する支持体を上記回路基板の配線を用いて形成し、

突起状に形成された上記電極端子部と支持体とによって、上記回路基板における上記絶縁体層の開口部内で上記半導体チップと回路基板とを実質平行に支持してフリップチップ実装を行うことを特徴とする半導体装置の製造方法。 - 素子形成面の中央部のみに直鎖状に配置された、回路基板との電気的な接続を形成するための電極端子部が設けられた半導体チップを、上記電極端子部にて、上記半導体チップよりも大きく、かつ、表面に絶縁体層が設けられた上記回路基板における接続用電極端子部に架設状態でフリップチップ実装する半導体装置の製造方法において、

上記回路基板表面に、該回路基板における上記半導体チップのフリップチップ実装対象領域に上記半導体チップの素子形成面よりも大きな開口部を有する絶縁体層を形成し、

上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部を突起状に形成すると共に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、突起状に形成された上記電極端子部とほぼ同じ高さを有し、かつ、少なくとも最表層が上記半導体チップのフリップチップ実装による上記接続用電極端子部との接合条件で塑性変形すると共に、該塑性変形による変形量が、突起状に形成された上記電極端子部とほぼ同じ材料からなり、上記半導体チップと回路基板とを実質平行に支持する支持体を上記回路基板の配線を用いて形成し、

突起状に形成された上記電極端子部と支持体とによって、上記回路基板における上記絶縁体層の開口部内で上記半導体チップと回路基板とを架設状態で実質平行に支持し、突起状に形成された上記電極端子部及び上記支持体を塑性変形させて上記半導体チップと回路基板とを接合することを特徴とする半導体装置の製造方法。 - 突起状に形成された上記電極端子部及び上記支持体を塑性変形させて上記半導体チップと回路基板とを接合させた後、上記半導体チップと回路基板との間隙に、該間隙を封止する界面封止樹脂を注入し、該界面封止樹脂を硬化させることを特徴とする請求項10記載の半導体装置の製造方法。

- 素子形成面の中央部にほぼ直鎖状に複数の電極端子部が設けられた半導体チップを使用し、

上記回路基板に、上記半導体チップの電極端子部に対応してほぼ直鎖状に複数の接続用電極端子部を設けると共に、上記接続用電極端子部からなる列の片側に、上記接続用電極端子部と平行に上記支持体を形成し、

上記半導体チップと回路基板とを接合後に、上記支持体が形成された側とは上記接続用電極端子部を挟んで反対側、もしくは、上記接続用電極端子部からなる列に対し、ほぼ直交する方向から上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入することを特徴とする請求項11記載の半導体装置の製造方法。 - 素子形成面の中央部にほぼ直鎖状に複数の電極端子部が設けられた半導体チップを使用し、

上記回路基板に、上記半導体チップの電極端子部に対応してほぼ直鎖状に複数の接続用電極端子部を設けると共に、上記接続用電極端子部からなる列の両側に、上記接続用電極端子部と平行に上記支持体を形成し、

上記半導体チップと回路基板とを接合後に、上記接続用電極端子部からなる列に対し、ほぼ直交する方向から上記半導体チップと回路基板との間隙に上記界面封止樹脂を注入することを特徴とする請求項11記載の半導体装置の製造方法。 - 突起状に形成された上記電極端子部と支持体とによって上記半導体チップと回路基板とを支持する前に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、上記半導体チップと回路基板との間隙を封止する界面封止樹脂からなる層を配し、

上記間隙に界面封止樹脂からなる層が配された状態で、突起状に形成した上記電極端子部と上記支持体とによって、上記半導体チップと回路基板とを架設状態で実質平行に支持し、

突起状に形成された上記電極端子部及び上記支持体の塑性変形と上記界面封止樹脂の硬化とを、同一の工程において行うことを特徴とする請求項10記載の半導体装置の製造方法。 - 上記接続用電極端子部及び半導体チップの電極端子部のうち突起状に形成する電極端子部と支持体との最表層に、導電性接着剤からなる接合層を各々設けることを特徴とする請求項10記載の半導体装置の製造方法。

- 素子形成面の中央部のみに直鎖状に配置された、回路基板との電気的な接続を形成するための電極端子部が設けられた半導体チップを、上記電極端子部にて、上記半導体チップよりも大きく、かつ、表面に絶縁体層が設けられた上記回路基板における接続用電極端子部に架設状態でフリップチップ実装する半導体装置の製造方法において、

上記回路基板表面に、該回路基板における上記半導体チップのフリップチップ実装対象領域に上記半導体チップの素子形成面よりも大きな開口部を有する絶縁体層を形成し、

上記接続用電極端子部及び半導体チップの電極端子部のうち何れか一方の電極端子部を突起状に形成すると共に、上記半導体チップ及び回路基板のうち何れか一方における他方との対向面に、突起状に形成された上記電極端子部とほぼ同じ高さを有し、上記半導体チップの素子形成面と上記回路基板表面とを実質平行に支持する支持体を上記回路基板の配線を用いて形成し、

突起状に形成された上記電極端子部と支持体とによって、上記回路基板における上記絶縁体層の開口部内で、上記半導体チップと回路基板とを架設状態で実質平行に支持した状態で、上記半導体チップと回路基板との間隙を界面封止樹脂により封止して上記接続用電極端子部と上記半導体チップの電極端子部とを圧接させることを特徴とする半導体装置の製造方法。 - 上記界面封止樹脂として、内部に導電粒子が分散された異方導電性樹脂を用いることを特徴とする請求項14または16に記載の半導体装置の製造方法。

- 上記接続用電極端子部及び半導体チップの電極端子部のうち突起状に形成する電極端子部と支持体とを、同じ材料で形成することを特徴とする請求項9、10、16の何れか1項に記載の半導体装置の製造方法。

- 上記支持体を金属で形成することを特徴とする請求項9、10、16、18の何れか1項に記載の半導体装置の製造方法。

- 上記接続用電極端子部及び半導体チップの電極端子部のうち上記接続用電極端子部を突起状に形成すると共に、

上記接続用電極端子部の形成工程と同一の工程で上記回路基板に上記支持体を形成することを特徴とする請求項9、10、16、18の何れか1項に記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003034014A JP4090906B2 (ja) | 2003-02-12 | 2003-02-12 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003034014A JP4090906B2 (ja) | 2003-02-12 | 2003-02-12 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004247415A JP2004247415A (ja) | 2004-09-02 |

| JP4090906B2 true JP4090906B2 (ja) | 2008-05-28 |

Family

ID=33019818

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003034014A Expired - Lifetime JP4090906B2 (ja) | 2003-02-12 | 2003-02-12 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4090906B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102008000128B4 (de) | 2007-01-30 | 2013-01-03 | Denso Corporation | Halbleitersensorvorrichtung und deren Herstellungsverfahren |

| CN115580983B (zh) * | 2022-09-30 | 2023-08-29 | 荣耀终端有限公司 | 电路板组件和电子设备 |

-

2003

- 2003-02-12 JP JP2003034014A patent/JP4090906B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004247415A (ja) | 2004-09-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3565319B2 (ja) | 半導体装置及びその製造方法 | |

| US6815252B2 (en) | Method of forming flip chip interconnection structure | |

| JP4175197B2 (ja) | フリップチップ実装構造 | |

| TWI277187B (en) | Semiconductor device and manufacturing method for the same | |

| TW502353B (en) | Flip chip assembly structure for semiconductor device and its assembling method | |

| US20020004258A1 (en) | Semiconductor device and method of fabricating the same, circuit board, and electronic equipment | |

| JP2002359345A (ja) | 半導体装置及びその製造方法 | |

| US6528889B1 (en) | Electronic circuit device having adhesion-reinforcing pattern on a circuit board for flip-chip mounting an IC chip | |

| JP2006310649A (ja) | 半導体装置パッケージおよびその製造方法、ならびに半導体装置パッケージ用一括回路基板 | |

| US6489180B1 (en) | Flip-chip packaging process utilizing no-flow underfill technique | |

| JP2002359323A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2000277649A (ja) | 半導体装置及びその製造方法 | |

| JP4090906B2 (ja) | 半導体装置及びその製造方法 | |

| JP2001127242A (ja) | 半導体チップ、マルチチップパッケージ、半導体装置、並びに電子機器、およびそれらの製造方法 | |

| JP3981817B2 (ja) | 半導体装置の製造方法 | |

| KR100533847B1 (ko) | 캐리어 테이프를 이용한 적층형 플립 칩 패키지 | |

| JP3582513B2 (ja) | 半導体装置及びその製造方法、回路基板並びに電子機器 | |

| JP2002190544A (ja) | 配線基板、半導体装置、及びその製造方法 | |

| JP4035949B2 (ja) | 配線基板及びそれを用いた半導体装置、ならびにその製造方法 | |

| JP2001127102A (ja) | 半導体装置およびその製造方法 | |

| JP3721859B2 (ja) | 半導体パッケージ | |

| JPH11340278A (ja) | 半導体装置実装用樹脂シート及びフリップチップ実装方法並びに回路基板 | |

| EP4090141A1 (en) | Composite wiring substrate, semiconductor device, and method of manufacturing composite wiring substrate | |

| JP3721986B2 (ja) | 半導体装置及びその製造方法 | |

| JP3669986B2 (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050810 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070227 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070306 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070426 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20070426 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071204 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080130 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080226 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080227 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110307 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120307 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120307 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130307 Year of fee payment: 5 |