JP4076079B2 - 半導体集積回路装置および半導体集積回路 - Google Patents

半導体集積回路装置および半導体集積回路 Download PDFInfo

- Publication number

- JP4076079B2 JP4076079B2 JP2003001825A JP2003001825A JP4076079B2 JP 4076079 B2 JP4076079 B2 JP 4076079B2 JP 2003001825 A JP2003001825 A JP 2003001825A JP 2003001825 A JP2003001825 A JP 2003001825A JP 4076079 B2 JP4076079 B2 JP 4076079B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- mos transistor

- input

- pair

- terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/0264—Arrangements for coupling to transmission lines

- H04L25/0272—Arrangements for coupling to multiple lines, e.g. for differential transmission

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/118—Masterslice integrated circuits

- H01L27/11803—Masterslice integrated circuits using field effect technology

- H01L27/11807—CMOS gate arrays

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/003—Changing the DC level

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/0264—Arrangements for coupling to transmission lines

- H04L25/0292—Arrangements specific to the receiver end

Description

【発明の属する技術分野】

本発明は、半導体集積回路における差動型の入力回路さらにはディジタル入力信号の波形歪みおよびジッタの低減に適用して有効な技術に関し、例えばゲートアレイの入力バッファ回路に利用して有効な技術に関する。

【0002】

【従来の技術】

プリント配線基板(以下、ボードと称する)上に実装された複数の半導体集積回路間や異なるボード上の半導体集積回路間でデータを伝送する場合、パッケージの端子やボード上の配線、ケーブル等に寄生する抵抗による信号の減衰や入出力端子での反射によりデータ信号の振幅が小さくなったり位相がずれたりすることで波形が歪んでしまうことが知られている。さらに、近年、データ伝送速度の高速化が進められているが、これに伴って、高周波の信号は伝送線の表面近傍を通るため抵抗が増大するという表皮効果が顕著になり、信号波形の歪みが一層大きくなるという問題がある。

【0003】

また、半導体集積回路間やボード間で伝送されるデータはまちまちであり、例えば“0101010101010101……”のように高周波成分を多く含む場合や、“000000111111000000111111……”のように比較的低周波の成分を多く含む場合があり、低周波成分を多く含む場合には伝送路を通過する信号は表皮効果の影響が少ないため信号の振幅は大きく、高周波成分を多く含む場合には伝送路を通過する信号は表皮効果の影響を強く受けるため振幅は小さくなる。しかも、このような振幅の変動は伝送線の長さが長くなるほど顕著になる。

【0004】

そのため、従来の一般的な差動アンプからなる入力回路にあっては、伝送する信号に含まれる周波数成分によってその出力の振幅が異なり振幅の変動が大きくなる。また、入力信号の振幅が小さい時は論理レベルの変化の際にロジックスレッショールドに到達するまでの時間が短いため信号の遅延が小さく、逆に入力信号の振幅が大きい時は信号の遅延が大きくなるため、伝送する信号に含まれる周波数成分の変動によりジッタが発生する。

【0005】

その結果、図24に示すように、入力回路の出力信号は波形が大きく歪んでしまい、アイパターンの開口度が小さくなる。そして、この開口度があまりにも小さくなってしまうと入力回路はデータを弁別できなくなり、正確なデータの伝送が困難になるという問題がある。

【0006】

かかる問題点を解決するため、例えば図25に示すように、差動型入力回路において差動入力トランジスタQ1,Q2のドレイン側にインダクタL1,L2を設けることにより、信号の歪みを低減する技術が提案されている(例えば非特許文献1参照)。また、図26に示すように、入力信号IN,/INの低周波成分を増幅する可変利得アンプAMP1,AMP2と高周波成分を増幅する可変利得アンプAMP3,AMP4を設け、低周波成分と高周波成分を別々に増幅した信号を抵抗を介して合成し、さらにアンプAMP5,AMP6で増幅して差動型コンパレータCPMに入力して弁別するようにした入力回路も提案されている(例えば非特許文献2参照)。

【0007】

【非特許文献1】

2001 IEEE International Solid-State Circuits Conference DIGEST OF TECHNICAL PAPERS p78-p79

【非特許文献2】

2002 Symposium On VLSI Circuits Conference Digest of Technical Papers p64-p67

【0008】

【発明が解決しようとする課題】

差動入力トランジスタQ1,Q2のドレイン側にインダクタL1,L2を設けるようにした図25のような差動型入力回路において、1G(ギガ)bpsのような速度で伝送されるデータ信号の歪みを所望のレベル以下に抑える場合、本発明者等の試算によるとインダクタL1,L2のインダクタンスとして数nHが必要となる。

【0009】

かかるインダクタンスを、半導体チップ上において例えば渦巻き状に形成された幅9μm、配線間隔3μm、巻数「2」の配線パターンで得ようとした場合、その直径は約200μmにもなってしまい、面積は入出力バッファ5個分の面積に相当することが分かった。そのため、入力ピンが数100〜数1000個にも達するゲートアレイに、図25のような差動型入力回路を適用するとインダクタの占有面積が非常に大きなものとなる。

【0010】

しかも、インダクタを構成する配線の下に他の配線が存在したり基板との間の絶縁膜が薄くて寄生容量値が大きかったりするとインダクタンスの値が低下するため、インダクタを構成する配線は最上層の導電層で形成するのが望ましく、その場合その下方には何ら他の配線や素子を形成することができない。そのため、図25のような差動型入力回路にあっては、空いているスペースを利用してインダクタL1,L2を形成してチップサイズの低減を図ることが困難であり、チップサイズの大幅な増大は避けられないという課題がある。

【0011】

また、入力信号IN,/INの低周波成分を増幅する可変利得アンプAMP1,AMP2と高周波成分を増幅する可変利得アンプAMP3,AMP4を設けた図26のような入力回路にあっても、差動型コンパレータCMPの他に6個のアンプが必要であり、入力回路の素子数が増加するためチップサイズの増大は避けられないという課題がある。

【0012】

さらに、上記記述ではデータ信号を伝送する場合について説明したが、半導体集積回路間でクロックパルスを伝送する場合にも周波数依存性が問題となる。具体的には、一般にシステムが決まればクロックパルスの周波数も決まるので、周波数に応じてクロックパルス信号の振幅や遅延時間が変動してジッタが発生することはないが、システムが異なれば使用されるクロックパルスの周波数が異なったり、クロックパルスの伝送線の長さが異なったりすることがある。その場合、クロックパルスのデューティが許容範囲からはずれて、受信したクロックパルスに同期してデータ信号をラッチする回路においては、マージンが低下して誤ったデータを取り込んでしまうおそれがある。

【0013】

この発明の目的は、チップサイズを増大させることなく高速のデータ信号を取り込んで波形を歪ませずに内部回路へ伝達することができる入力回路を備えた半導体集積回路装置を提供することにある。

【0014】

この発明の他の目的は、伝送されるデータの配列に依存して入力データ信号の振幅が変動したりジッタが増加したりするのを抑えて、データを内部回路へ正確に伝達することができる入力回路を備えた半導体集積回路装置を提供することにある。

【0015】

この発明のさらに他の目的は、クロックパルス信号のデューティの変動を防止して、クロックパルスに同期してデータ信号をラッチする回路においてマージンが低下して誤ったデータを取り込むのを回避することができる入力回路を備えた半導体集積回路装置を提供することにある。

【0016】

この発明の前記ならびにそのほかの目的と新規な特徴については、本明細書の記述および添付図面から明らかになるであろう。

【0017】

【課題を解決するための手段】

本願において開示される発明のうち代表的なものの概要を説明すれば、下記のとおりである。

【0018】

すなわち、差動型の入力回路において、差動信号が入力される一対の入力端子に制御端子が接続され主として低周波成分を増幅するための第1の差動入力トランジスタ対の他に、差動信号が入力される一対の入力端子に制御端子が各々容量素子を介して接続され第1の差動入力トランジスタ対と差動結合点(共通ソース)が共通結合されて主として高周波成分を増幅するための第2の差動入力トランジスタ対を設けるようにしたものである。

【0019】

なお、上記第1の差動入力トランジスタ対を構成するトランジスタは、入力端子に制御端子が直接接続され入力端子から電流を流し込むことができるのでバイポーラ・トランジスタでも電界効果トランジスタであってもよいが、第2の差動入力トランジスタ対を構成するトランジスタは、制御端子が容量を介して入力端子に接続されていて入力端子からベース電流を流し込むことができないので、バイポーラ・トランジスタを用いるのは不適当であり電界効果トランジスタに限定される。また、第2の差動入力トランジスタ対が電界効果トランジスタである場合、この第2の差動入力トランジスタ対と差動結合点(共通ソース)が共通結合される第1の差動入力トランジスタ対も電界効果トランジスタであることが望ましい。

【0020】

上記した手段によれば、入力信号の低周波成分のみならず高周波成分をも増幅することができるため、入力データ信号の伝送速度が速くなっても伝送されるデータの配列に依存して入力データ信号の振幅が変動したりジッタが増加したりするのを抑えて、データを内部回路へ正確に伝達することができるようになる。また、入力端子に接続される容量と高周波成分を増幅するための第2の差動入力トランジスタ対が必要であるが、半導体集積回路において容量はインダクタに比べて小さな面積で形成することができるため、チップサイズをそれほど増大させることなく高速のデータ信号を取り込んで波形を歪ませずに内部回路へ伝達することができる。

【0021】

さらに、外部から入力されるクロックパルス信号を取り込んで内部回路へ供給する入力回路においては、入力信号の低周波成分のみならず高周波成分をも増幅することができることにより、クロックの周波数が高くなっても信号の振幅が小さくなったりしないためクロックパルス信号のデューティのずれを防止して、クロックパルスに同期してデータ信号をラッチする回路においてマージンが低下して誤ったデータを取り込むのを回避することができる。

【0022】

本出願に係る第2の発明は、差動信号が入力される一対の入力端子に制御端子が接続され主として低周波成分を増幅するための第1の差動入力トランジスタ対の他に、差動信号が入力される一対の入力端子に制御端子が各々容量素子を介して接続され第2の差動入力トランジスタ対と差動結合点(共通ソース)が共通結合されて主として高周波成分を増幅するための第2の差動入力トランジスタ対を有する差動型の入力回路において、上記容量素子として、第1配線と該第1の配線の周囲を囲むように形成されたチューブ状の第2配線との間のカップリング容量を使用するようにしたものである。これにより専用の占有領域を設けることなく高周波成分を伝達する容量素子を形成することができる。

【0023】

【発明の実施の形態】

以下、本発明の好適な実施例を図面に基づいて説明する。

【0024】

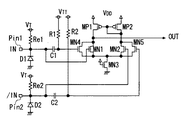

図1は、本発明を適用した差動型入力回路(以下、単に入力回路と称する)の第1の実施例を示す。

【0025】

図1において、Pin1,Pin2は差動入力信号IN,/INが外部から供給される入力端子である。半導体集積回路においては、この入力端子は、一般に、ボンディングワイヤの一端が結合されたボンディングパッドと呼ばれる電極あるいは半田ボール等を介してパッケージ側の電極と接合されるパッドとして構成される。

【0026】

この実施例の入力回路は、互いにソース端子が結合されゲート端子が各々前記入力端子Pin1,Pin2に接続された一対のNチャネル型差動入力MOSFET MN1,MN2と、ソース端子が前記型差動入力MOSFET MN1,MN2のソース端子に結合されゲート端子が各々容量C1,C2を介して前記入力端子Pin1,Pin2に接続された一対のNチャネル型差動入力MOSFET MN4,MN5と、これらのMOSFET MN1〜MN5の共通ソース端子と接地点(VSS)との間に接続された定電流用MOSFET MN3と、前記差動入力MOSFET MN1,MN2のドレイン端子と電源電圧端子VDDとの間に接続されたPチャネル型のMOSFET MP1,MP2と、前記差動入力MOSFET MN4,MN5の各ゲート端子と定電圧端子VTTとの間に接続された抵抗R1,R2と、前記入力端子Pin1,Pin2と接地点との間に接続された保護ダイオードD1,D2と、前記入力端子Pin1,Pin2と定電圧端子VTとの間に接続された終端抵抗Re1,Re2とから構成されている。図示はされないが、保護ダイオードはD1,D2のほかに前記入力端子Pin1,Pin2と電源VDDとの間に接続したものを挿入しても良い。

【0027】

上記負荷MOSFET MP2はゲートとドレインが結合され、他方の負荷MOSFET MP1は該MOSFET MP2とゲート共通結合されて、カレントミラー型のアクティブ負荷を構成している。抵抗R1,R2を介して差動入力MOSFET MN4,MN5のゲート・バイアス電位すなわち振幅の中心電位を与える定電圧端子VTTは、MOSFET MN4のしきい値電圧Vthと電源電圧VDDとの間の電圧であれば良い。VTは終端電位である。この実施例では、特に制限されるものでないが、VDDは1.5V、VTTは1.0V、VTは1.0Vに設定されている。

【0028】

終端抵抗Re1,Re2は本実施例で想定している伝送線のインピーダンス(50Ω)に合わせて例えば50Ωのような抵抗値に設定されている。伝送線とほぼ同じインピーダンスとすることによって、端子を介して入力された高速の信号が内部で反射等を起こすなどして波形が乱れてしまうことを防ぐことが可能となる。図示はしないが終端抵抗Re1,Re2は外付けの素子として入力端子Pin1,Pin2に接続することで、チップ内部に設けないようにすることも可能である。

【0029】

本実施例では、入力データ信号IN,/INの伝送速度として1Gbpsを想定して、前記容量C1,C2は例えば0.2pFのような容量値を有し、抵抗R1,R2は1kΩのような抵抗値を有するように設計されることで、CR時定数が約200psになるように設定されている。これにより、前記入力端子Pin1,Pin2に数百MHz〜数GHzの信号が入力されているときに、その高周波成分を容量C1,C2を介してMOSFET MN4,MN5のゲート端子に供給して増幅させることができるように構成されている。前記入力端子Pin1,Pin2とMOSFET MN1,MN2のゲート端子との間には容量が介挿されていないので、MOSFET MN1,MN2はもっぱら入力信号の低周波成分を増幅する。

【0030】

従って、前記入力端子Pin1,Pin2に数百MHz〜数GHzの信号が入力されているときは、MOSFET MN1,MN2およびMN4,MN5により、入力信号の低周波成分と高周波成分の両方が増幅され、入力端子Pin1,Pin2に数百MHz以下の信号が入力されているときは、MOSFET MN1,MN2のみに信号が入力され、低周波成分が増幅されて内部回路へ供給される。

【0031】

また例えば、入力データ信号IN,/INの伝送速度として3Gbps(約300ps)想定するのであれば、CR時定数がデータ伝送速度の周期より小さく、1kΩのような抵抗値を有する抵抗を用いる場合は、容量Cを例えば0.16pFのような容量値を有するように設計すればよい。

【0032】

図12(A)〜図12(C)は、本実施例の入力回路と、差動入力MOSFET MN4,MN5および容量C1,C2を設けない従来型の差動入力回路について、ゲイン特性とディレイ特性をシミュレーションによって求めた結果を示す。このうち、図12(A),図12(B)はゲイン特性を、図12(C)はディレイ特性を示す。また、図12(A)〜図12(C)において、実線A1,A2,A3は本実施例の入力回路の特性を、破線B1,B2は従来型の差動入力回路の特性を、一点鎖線Dは伝送線の損失特性を、点線Eはゲイン特性A2と損失特性Dの合成特性を示す。

【0033】

図12(A)から、差動入力MOSFET MN4,MN5および容量C1,C2を設けない従来型の差動入力回路は300MHz以上の信号に対するゲインが周波数の増加に伴い徐々に下がるが、本実施例の入力回路は、百MHz以上4GHz以下の信号に対するゲインがそれ以外の周波数の信号に対するゲインよりも高くなっていることが分かる。また、図12(B)から、伝送線の損失により入力信号の振幅が小さくなっても、本実施例の入力回路は百MHz以上4GHz以下の信号に対するゲインが高くなっているため、点線Eのように伝送線による損失を補償して1GHzまでほとんど振幅の低下のない信号を内部回路へ供給できることが分かる。

【0034】

さらに、図12(C)から、差動入力MOSFET MN4,MN5および容量C1,C2を設けない従来型の差動入力回路では周波数が100MHzを超えると信号のディレイが減少し始めるが、本実施例の入力回路は、数GHzまで信号のディレイが低下せずむしろ大きくなることが分かる。なお、このように、本実施例の入力回路において信号のディレイが低下しないのは、信号の振幅が大きくなることによって最大レベルもしくは最小レベルから回路のロジックシュレッショールドに到達するまでの時間が長くなるためである。

【0035】

図13(A)〜図13(D)には、本実施例の入力回路に対して、伝送線を介して1Gbpsのデータ信号を伝送したときの入出力信号の波形をシミュレーションによって求めた結果を示す。このうち図13(A)は出力回路の出力信号すなわち伝送線の始端での信号の波形を、図13(B)は容量C1,C2を介さない差動入力MOSFET MN1,MN2のゲート端子への入力信号の波形を、図13(C)は容量C1,C2を介する差動入力MOSFET MN4,MN5への入力信号の波形を、図13(D)は本実施例の入力回路の出力信号波形をそれぞれ示す。

【0036】

図13(D)より、本実施例の入力回路の出力信号は、入力信号の周波数が高い場合にも低い場合にも充分な振幅を有することが分かる。一方、差動入力MOSFET MN4,MN5および容量C1,C2を設けない従来型の差動入力回路の出力信号は、図13(B)の入力信号をそのまま増幅した信号となり波形自身は相似になるので、入力信号の周波数が低い場合には振幅は充分に出るが、周波数が高い場合には振幅が充分に出ないことが分かる。

【0037】

図2は、図1の第1実施例の入力回路の第1変形例を示す。

【0038】

図2の回路は、図1の回路における差動入力MOSFET MN4,MN5のゲート・バイアス電位を与える抵抗R1,R2の代わりに、電源電圧VDDとの間に接続されたPチャネルMOSFET MP3,MP4と、接地点との間に接続されたNチャネルMOSFET MN6,MN7とを設け、MP3とMP4のゲート端子には接地電位VSSを印加し、MN6とMN7のゲート端子には電源電圧VDDを印加して、MP3とMN6のオン抵抗の比およびMP4とMN7のオン抵抗の比で差動入力MOSFET MN4とMN5のゲート・バイアス電位を与えるようにしたものである。この変形例の回路は、終端抵抗Re1,Re2を外付け抵抗とする場合に特に有効である。

【0039】

その理由は、MOSFETの抵抗比で差動入力MOSFET MN4とMN5のゲート・バイアス電位を生成することができ、これによって定電圧VTTが不要になるためである。定電圧VTTが不要であるため、定電圧VTTを外部から供給する場合には外部端子が、また定電圧VTTをチップ内部で生成する場合には定電圧回路が不要になり、その分チップサイズの増大を抑えることができる。

【0040】

図3は、図1の第1実施例の入力回路の第2変形例を示す。

【0041】

図3の回路は、図1の回路における負荷MOSFET MP1,MP2のゲート電圧を、ダイオード接続のカレントミラー用MOSFET MP2のドレイン端子から与える代わりに、図示しない定電圧回路で生成した最適なバイアス電圧Vgを与えるようにしたものである。この変形例の回路では、定電圧回路が必要になるが入力回路から内部回路へ供給される信号の中心電位を素子(MN1〜MN5,MP1,MP2)の定数や特性に依存することなく任意に設定できるという利点がある。バイアス電圧Vgはチップ外部から与えるようにすることも可能である。ただしその場合には、外部端子が別途必要となる。

【0042】

この変形例においても、差動入力MOSFET MN4,MN5のゲート・バイアス電位を与える抵抗R1,R2の代わりに、電源電圧VDDとの間に接続されたPチャネルMOSFET MP3,MP4と、接地点との間に接続されたNチャネルMOSFET MN6,MN7とを設け、MP3とMN6の抵抗比およびMP4とMN7の抵抗比で差動入力MOSFET MN4とMN5のゲート・バイアス電位を与えるようにしても良いし、終端抵抗Re1,Re2を外付け抵抗とするようにしても良い。

【0043】

図4は、図1の第1実施例の入力回路の第3変形例を示す。

【0044】

図4の回路は、図1の回路における負荷MOSFET MP1,MP2の代わりに、負荷抵抗R3,R4を用いたものである。この抵抗R3,R4は、例えばMOSFETを構成するゲート電極と同一のポリシリコン層あるいは半導体チップ上に形成した拡散層により構成することができる。この変形例の回路は、入力回路から内部回路へ供給される信号の中心電位を素子(MN1〜MN5,MP1,MP2)の定数や特性に依存することなく抵抗R3,R4の抵抗値で設定できるという利点がある。

【0045】

この変形例においても、抵抗R1,R2の代わりに、電源電圧VDDとの間に接続されたPチャネルMOSFET MP3,MP4と、接地点との間に接続されたNチャネルMOSFET MN6,MN7とを設け、MP3とMN6の抵抗比およびMP4とMN7の抵抗比で差動入力MOSFET MN4とMN5のゲート・バイアス電位を与えるようにしても良いし、終端抵抗Re1,Re2を外付け抵抗とするようにしても良い。

【0046】

図5は、図1の第1実施例の入力回路の第4変形例を示す。

【0047】

図5の回路は、図1の回路における負荷MOSFET MP1と並列にスイッチMOSFET MPSを設けて、定電流用MOSFET MN3のゲート端子と共通の信号を入力させ、通常動作状態ではスイッチMOSFET MPSと定電流用MOSFET MN3のゲート端子に電源電圧VDDを供給してスイッチMOSFET MPSをオフ、MN3をオンさせて入力回路に電流を流して回路を動作させ、スタンバイモードのような状態では接地電位VSSに切り替えて定電流用MOSFET MN3をオフさせて電流を遮断して入力回路を非動作状態にさせる。また、このときスイッチMOSFET MPSをオンさせて、出力ノードの電位をハイレベルに固定して次段のCMOS回路に貫通電流が流れないようにしたものである。

【0048】

なお、図示しないが、図2や図3の回路において、図5に示すような負荷MOSFET MP1,MN1と並列なスイッチMOSFET MPSを設けた変形例も考えられる。図4の変形例で、入力回路をオン/オフ制御可能にするためには、図5のスイッチMOSFET MPSを設ける必要はなく、定電流用MOSFET MN3のゲート電圧のみ切り替えられるように構成すれば良い。

【0049】

図6は、図1の第1実施例の入力回路の第5変形例を示す。

【0050】

図6の回路は、図1の実施例の入力回路の次段にもう1つ差動増幅回路を設け、入力回路から出力信号を差動で取り出して次段の差動増幅回路に入力して更に増幅して内部回路へ伝送するようにしたものである。この変形例においても、図2〜図5の変形例と同様な構成変更が可能である。

【0051】

図7は、本発明を適用した入力回路の第2の実施例を示す。

【0052】

この実施例の入力回路は、差動入力MOSFETおよび定電流用MOSFETとしてNチャネルMOSFETの代わりにPチャネルMOSFET MP1〜MP5を、またPチャネル負荷MOSFETの代わりに、Nチャネル負荷MOSFET MN1,MN2を用いたものである。この実施例は、第1の実施例の入力回路に比べて内部回路へ供給される信号の中心電位を低くすることができるという特徴がある。

【0053】

図8は第2の実施例における第1の実施例の図3に相当する変形例、図9は第2の実施例における第1の実施例の図4に相当する変形例である。図示しないが、図8および図9の回路における抵抗R1,R2の代わりに、図2に示されている抵抗分割用のMOSFETMP3,MN6,MP4,MN7を用いる変形例、図8や図9の回路において、図5に示すような負荷MOSFET MP1,MN1と並列なスイッチMOSFET MPSを設けた変形例も考えられる。

【0054】

図10は、本発明を適用した入力回路の第3の実施例を示す。

【0055】

この実施例の入力回路は、差動入力信号IN,/INをPチャネル差動入力MOSFET MP1、MP2、MP4、MP5とNチャネル差動入力MOSFET MN1、MN2、MN4、MN5の両方で受けるようにしたものである。Pチャネル差動入力MOSFET MP1、MP2、MP4、MP5のドレインはそれぞれ負荷素子R13,R14を介して接地点に接続され、Nチャネル差動入力MOSFET MN1、MN2、MN4、MN5のドレインはそれぞれ負荷素子R11,R12を介して電源電圧端子VDDに接続されている。

【0056】

また、負荷素子R11とR13との間には出力信号の中心電位を設定するためのMOSFET MP8とMN8が、負荷素子R12とR14との間には出力信号の中心電位を設定するためのMOSFET MP9とMN9が、それぞれ直列形態で接続され、MP8,MP9のゲート端子には所定のバイアス電圧Vbiasが印加され、MN8とMN9のゲート端子にはダイオード接続のMN9のドレイン電圧が印加され、MN8のドレイン端子から出力信号が取り出されるように構成されている。

【0057】

なお、この実施例においても、図10の回路における抵抗R1,R2の代わりに、図2に示されている抵抗分割用のMOSFETMP3,MN6,MP4,MN7を用いる変形例、終端抵抗Re1,Re2として外付け抵抗を用いる変形例も考えられる。さらに、負荷素子R11〜R14とバイアス用のMOSFET MP8、MP9、MN8、MN9を省略して、Pチャネル差動入力MOSFETのドレイン端子とNチャネル差動入力MOSFETのドレイン端子を直結した変形例も考えられる。

【0058】

図11は、本発明を適用した入力回路の第4の実施例を示す。

【0059】

この実施例の入力回路は、差動入力信号IN,/INをそれぞれ別個に受ける差動アンプAMP1,AMP2と、これらのアンプの出力を受けて動作する差動アンプAMP3を設けたものである。この実施例は、前段の差動アンプAMP1,AMP2において、負荷MOSFETのうちゲート・ドレイン結合されたMOSFETと逆のMOSFETのドレイン端子の電圧を出力電圧とすることにより、出力信号のバランスが良くなるとともにダイナミックレンジが広くなるという利点がある。

【0060】

この実施例においても、図11の回路における抵抗R1,R2の代わりに、図2に示されている抵抗分割用のMOSFET MP3,MN6,MP4,MN7を用いる変形例、終端抵抗Re1,Re2として外付け抵抗を用いる変形例、図11の回路において図5に示すような負荷MOSFET MP1,MN1と並列なスイッチMOSFET MPSを設けて入力回路をオン/オフ制御可能な構成にする変形例も考えられる。

【0061】

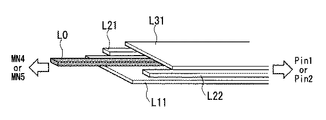

図14および図15には、差動入力MOSFET MN4,MN5に入力信号の高周波成分を伝える容量C1,C2の具体的な構成例が示されている。

【0062】

本実施例においては、図15に示されているような配線間のカップリング容量Cs1〜Cs4を利用して、入力端子Pin1,Pin2と差動入力MOSFET MN3,MN4との間の容量C1,C2を構成している。より具体的には、多層配線技術により形成されるいずれかの中間メタル層Mnからなる配線L0と、それを囲むように同一メタル層および上下のメタル層Mn+1,Mn−1により形成された配線L11,L21,L22,L31との間に寄生するカップリング容量Cs1〜Cs4を、高周波成分を伝える容量C1,C2としている。つまり配線L0を囲むように構成された上層及び下層のメタル層によって形成される金属-絶縁膜-金属構造(MIM構造)によって容量を作り出している。また、本実施例では、Al(アルミニウム)またはCu(銅)を主成分とする導体膜で形成されたメタル配線が用いられている。

【0063】

配線L11とL21,L31との間およびL11とL22,L31との間は、層間絶縁膜に形成されたスルーホールに充填されたビア(VIA)と呼ばれる導電体VIA1〜VIA4により電気的に接続されている。この導電体VIA1〜VIA4は配線方向に沿って設計ルール上の最小間隔で複数個形成されている。導電体VIA1〜VIA4を最小間隔で形成することにより、配線L0と配線L11〜L31との間のカップリング容量の容量値を大きくすることができる。メタル層Mn−1,Mn,Mn+1の組合せとしては、例えば半導体基板主面上に形成された1層目と2層目と3層目のメタル層が考えられるが、これに限定されるものでなく、2層目と3層目と4層目を使用しても良いし、配線L0を2層目と3層目の2つのメタル層で形成し、配線L11,L31を1層目と4層目のメタル層でそれぞれ形成しても良い。

【0064】

配線L11,L21,L22,L31からなるチューブ状の配線の一端はパッドからなる外部入力端子Pin1またはPin2に接続され、芯側の配線L0の一端(上記パッドと逆側)は差動入力MOSFET MN4,MN5のゲート端子に接続される。芯側の配線L0をパッドに接続し、チューブ状の配線をMN4,MN5のゲート端子に接続する構成も可能であるが、チューブ状の配線の場合にはその外側の他の配線あるいは基板との間の寄生容量が大きくなって時定数が設計値からずれたり基板電位等により容量値が変動したり、外部からのノイズがMN4,MN5のゲート端子に飛び込み易くなったりするので、芯側の配線L0をMN4,MN5のゲート端子に接続する方が望ましい。

【0065】

なお、配線L0を配線L11,L21,L22,L31で完全に囲まずに、一部を省略してコの字状に囲むようにしてもよい。その場合、配線L0と基板との間の寄生容量を少なくする観点から、両側の配線L21,L22のいずれか一方を省略するのが最も望ましいが、下方の配線L11または上方の配線L31を省略する場合には上方の配線L31を省略する方が望ましい。

【0066】

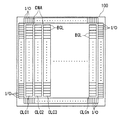

図16〜図22には、差動入力MOSFET MN4,MN5に入力信号の高周波成分を伝える容量C1,C2として図14に示すような配線間のカップリング容量を利用した差動入力回路をゲートアレイに適用した場合のレイアウトおよびデバイス構造の一実施例が示されている。このうち、図16はチップ全体のレイアウトの概略を示す。

【0067】

図16において、符号I/Oが付されているのは入出力バッファセル、BCLが付されているのは内部ロジックを構成する基本論理セルである。基本論理セルは、例えばPチャネルMOSFETとNチャネルMOSFETが対で設けられ、1つあるいは数個のCMOSインバータもしくは多入力CMOS−NORゲート回路または多入力CMOS−NANDゲート回路を構成可能な素子により構成される。

【0068】

入出力バッファセルI/Oは、配線のレイアウトを変更することで、各々図1のような差動入力回路または出力バッファ回路のいずれにも構成可能に設計されている。図16に示されているように、半導体チップ100の周縁部には各辺に沿って複数の入出力バッファセルI/Oが配置されており、これらの入出力バッファセルI/Oに囲まれたチップの中央部に複数の基本論理セルBCLが並んで配置された複数のセル列CLC1〜CLCnが設けられている。各セル列CLC1〜CLCn間に設けられたスペースCNAは、セル間を接続する配線が設けられた配線チャネル領域である。

【0069】

図17は、上記入出力バッファセルI/Oの1つを拡大して示すレイアウト図である。

【0070】

図17に示すように、入出力バッファセルI/Oは、外部端子としてのパッドPAD1,PAD2が形成される領域111と、入力バッファ回路を構成する際に使用される静電保護用ダイオードD1,D2が形成される領域112と、出力バッファ回路を構成するためのPチャネルMOSFET Qp1,Qp2が形成される領域113と、出力バッファ回路を構成する際に使用される静電保護用ダイオードD11,D12が形成される領域114と、出力バッファ回路を構成するためのNチャネルMOSFET Qn1,Qn2が形成される領域115と、プリバッファ回路を構成する際に使用される電源安定化容量C11,C12が形成される領域116と、図1のような差動入力回路IBFT,IBFBを構成する素子が形成される領域117とからなる。更に、パッドPAD1,PAD2の外側に出力バッファ用安定化容量C21,C22が形成される領域110がある。本実施例においては電源を安定化するのに十分な値として例えば出力バッファ用安定化容量は100pF程度を想定している。

【0071】

なお、図17において、各領域112〜117がそれぞれ対をなす素子領域で構成されているのは、差動信号を入出力できるようにするためであり、一方はトゥルー側の信号用、他方はバー側の信号用である。片側の領域のみ使用して回路を構成することでシングルの信号に対応する回路を構成することも可能である。

【0072】

図17に示す入出力バッファセルI/Oを用いて図1のような差動入力回路を形成する場合、出力バッファを構成するためのPチャネルMOSFET Qp1,Qp2や静電保護用ダイオードD11,D12、NチャネルMOSFET Qn1,Qn2が形成される領域113,114,115は不要である。そこで、これらの領域を利用して終端抵抗Re1,Re2と電源電圧VTTに接続されMOSFET MN4,MN5のゲート・バイアス点を与える抵抗R1,R2を形成することができる。具体的には、出力バッファ用のPチャネルMOSFET Qp1,Qp2もしくはNチャネルMOSFET Qn1,Qn2のゲート電極となるポリシリコン層を用いて終端抵抗Re1,Re2と分割抵抗R1,R2を構成することができる。

【0073】

また、電源電圧VTTに接続されMOSFET MN4,MN5のゲート・バイアス点を与える抵抗R1,R2の代わりに、図2に示されているゲート・バイアス点を与えるPチャネルMOSFET MP3,MP4とNチャネルMOSFET MN6,MN7を用いる場合にも、領域113の出力バッファ用のPチャネルMOSFET Qp1,Qp2と領域115のNチャネルMOSFET Qn1,Qn2を利用して形成することができる。

【0074】

この実施例では、出力バッファ用のPチャネルMOSFET Qp1,Qp2のゲート電極となるポリシリコン層を利用して終端抵抗Re1,Re2を形成するとともに、出力バッファ用のPチャネルMOSFET Qp1,Qp2を利用して差動入力MOSFET MN4,MN5のゲート・バイアス点を与えるPチャネルMOSFET MP3,MP4を、また出力バッファ用のNチャネルMOSFET Qn1,Qn2を利用して接地電位に接続され差動入力MOSFETMN4,MN5のゲート・バイアス点を与えるNチャネルMOSFET MN6,MN7を形成するようにしている。

【0075】

さらに、この実施例では、静電保護用ダイオードD11,D12が形成される領域114と出力バッファ回路を構成するNチャネルMOSFET Qn1,Qn2が形成される領域115を利用して、入力信号の高周波成分を通過させる容量C1,C2としてのカップリング容量を構成する図14に示すような同軸ケーブル状の配線L0,L11〜L31が形成される。

【0076】

なお、領域114と115に形成されるのは、同軸ケーブル状をなす部分のみであり、チューブ状の配線L11〜L31はパッドPAD1,PAD2の近傍まで形成される。ただし、領域112と113に形成される入力信号伝達用の配線は、チューブ状でなくてもよく、3層のメタル層のいずれか1つまたは2つのメタル層からなる配線としたり、中間層のメタル層からなる配線L21,L22をL11やL31と同様に横方向に連続したパターンとしてもよい。領域112と113においてもチューブ状を成すように形成しておくことにより、芯側の配線L0の長さを調整することで、カップリング容量の値を変更可能にすることができ、製品に応じて時定数を任意かつ容易に設定することが可能となる。

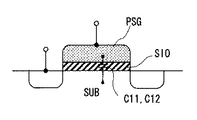

【0077】

特に制限されるものでないが、この実施例では、電源安定化容量C11,C12はいわゆるMOS容量により構成される。MOS容量は、図18に示すように、MOSFETのゲート電極を構成するポリシリコン層PSGを一方の電極とし、半導体基板SUBを他方の電極とし、MOSFETのゲート絶縁膜となる酸化膜SIOを誘電体とする容量である。かかる構成の容量を電源安定化容量C11,C12として用いることにより、比較的厚みの薄いゲート絶縁膜を誘電体とするため小さな面積で大きな容量値が得られるとともに、何ら新たな工程を追加することなく電源安定化容量C11,C12を半導体基板上に形成することができる。本実施例では、電源安定化容量の容量値として20pF〜30pFを想定している。

【0078】

この電源安定化容量C11,C12は、図19に示すように、出力バッファ回路OBFの近傍に配設される電源ライン(VDDライン)とグランドライン(VSSライン)との間に接続され、出力バッファ回路OBFに大きな電流が流されても電源電圧VDDが変動しないように作用する。

【0079】

図20〜図22には、領域115に形成される同軸ケーブル状のカップリング容量を構成する配線L0,L11〜L31の具体的なパターンの例が示されている。このうち図20は1層目のメタル層からなる配線L11を、図21は2層目のメタル層からなる配線L0,L21,L22を、図22は3層目のメタル層からなる配線L31を示す。また、図23は、図20の一点鎖線A−A’に沿った断面を示す。

【0080】

図21に示されているように、各パッドPAD1,PAD2に対応して配線L0がそれぞれ2本ずつ平行に設けられているのは、短い距離で大きな容量値を得るためである。各配線L0,L11〜L31の下端において図の左右両側に広がりさらに上方へ延出する部位が設けられているのは、この部位に前述の差動入力MOSFET MN4,MN5のゲートバイアス点を与えるNチャネルMOSFET MN6,MN7が形成されており、このMOSFET MN6,MN7に配線L0を接続させるためである。

【0081】

図20において、符号121〜124で示されているのはNチャネルMOSFET MN6,MN7のソースもしくはドレイン領域となる拡散層である。また、図20および図23において、符号131で示されているのはNチャネルMOSFET MN6(MN7)のポリシリコンゲート電極であり、このゲート電極には4層目のメタル層M4からなる電源配線(VDDライン)が、3層目のメタル層M3、2層目のメタル層M2、1層目のメタル層M1を経由して接続されている。また、拡散層124aには、4層目のメタル層M4からなる電源配線(VSSライン)が、3層目のメタル層M3、2層目のメタル層M2、1層目のメタル層M1を経由して接続され、拡散層124aには、2層目のメタル層M2と1層目のメタル層M1を経由して配線L0に接続されている。

【0082】

拡散層121〜124とゲート電極131等は、出力バッファ回路を構成する場合には出力用のNチャネルMOSFETとして使用される素子であり、符号115で示される領域には、複数のNチャネルMOSFET用の拡散層とゲート電極が形成されており、出力バッファ回路を構成する場合にはこれら複数のMOSFETが並列に接続されて1つの大きなMOSFETとして動作するようにされる。また、本実施例のように、入力回路を構成する場合には、複数のMOSFETのうち一つまたは数個を利用して前記抵抗分割用のNチャネルMOSFET MN6,MN7が構成される。

【0083】

図示しないが、出力バッファ回路を構成するためのPチャネルMOSFET Qp1,Qp2の領域113にも、予め複数のPチャネルMOSFETが形成されており、出力バッファ回路を構成する場合にはこれらのMOSFETが並列に接続されて1つの大きなMOSFETとして動作するようにされる。従って、入力回路を構成する場合には、そのうち一部のPチャネルMOSFETのゲート電極としてのポリシリコン層を利用して終端抵抗Re1,Re2を形成するとともに、残りの一部の出力バッファ用のPチャネルMOSFETを利用して差動入力MOSFET MN4,MN5のゲートにバイアスを与えるPチャネルMOSFET MP3,MP4とすることができる。

【0084】

また、図20において、L10で示されている配線は上記配線L0に接続されて入力信号の高周波成分を差動入力MOSFET MN4,MN5のゲート端子に伝達するための配線、L12で示されている配線は上記配線L11に接続されて入力信号の低周波成分を差動入力MOSFET MN1,MN2のゲート端子に伝達するための配線である。配線L0と配線L10はビアVIA0にて接続されている。

【0085】

また、図1〜図11には示されていないが、静電保護のため、配線L10は基板表面に形成された拡散層(抵抗)125を介して配線L11に接続されている(図23参照)。この拡散層125と基板100との間のPN接合は、図1に示されている静電保護用のダイオードD1またはD2とみなすことができる。さらに、この実施例では、3層目のメタル層からなる配線L31(L31a〜L31c)は1層目のメタル層からなる配線L11よりも広い幅を有するように構成されている。これにより、配線L31よりも基板100に近い配線L11の幅を広くする場合に比べて、寄生容量を増加させることなく、配線L0と配線L11〜L31間の容量を大きくすることができる。

【0086】

なお、図23に示されているように、3層目のメタル層からなる配線L31が3本の平行配線L31a,L31b,L31cで構成されているのは、配線L31の幅が設計ルールで決まる最大配線幅よりも広くなったためである。ここで、配線L11〜L31は終端抵抗を介して流したい電流量にあわせて配線幅を決定するのであるが、電流密度を小さくしてエレクトロマイグレーションの影響を小さくするためにも、ある程度の配線幅が必要となってくる。配線L31は一つの配線によって構成することも可能であるが、本実施例では配線L31の幅が設計ルールで決定される最大配線幅よりも大きくなったために分割することとした。

【0087】

図20〜図22において、VIA11〜VIA18,VIA21〜VIA28,VIA31〜VIA38は、基板に電源電圧VDDを印加して基板とウェル領域との間や基板と拡散層との間に逆バイアスを与えるための給電用のビアである。

【0088】

以上本発明者によってなされた発明を実施例に基づき具体的に説明したが、本発明は上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。例えば、前記実施例においては、入力信号の低周波成分を増幅する差動入力MOSFET MN1,MN2と、入力信号の高周波成分を増幅する差動入力MOSFET MN3,MN4を、エミッタ共通結合した構成としたが、入力信号の周波数が高い場合には、入力信号の低周波成分を増幅する差動入力MOSFET MN1,MN2を省略した差動入力回路であっても、波形の歪みが小さくジッタの少ない信号を内部回路に供給することができる。

【0089】

以上の説明では主として本発明者によってなされた発明をその背景となった利用分野であるゲートアレイの入出力バッファに適用した場合を説明したが、この発明はそれに限定されるものでなく、伝送速度の高いディジタル信号を受ける半導体集積回路一般に利用することができる。

【0090】

【発明の効果】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0091】

すなわち、本発明に従うと、差動入力回路において、入力信号の低周波成分のみならず高周波成分をも増幅することができるため、入力データ信号の伝送速度が速くなっても伝送されるデータの配列に依存して入力データ信号の振幅が変動したりジッタが増加したりするのを抑えて、データを内部回路へ正確に伝達することができるようになる。また、半導体集積回路においては、容量はインダクタに比べて小さな面積で形成することができるため、チップサイズをそれほど増大させることなく高速のデータ信号を取り込んで波形を歪ませずに内部回路へ伝達することができる。

【0092】

さらに、入力信号の低周波成分を差動入力MOSトランジスタに伝える容量素子として、第1配線と該第1の配線の周囲を囲むように形成されたチューブ状の第2配線との間のカップリング容量を使用するようにしたもので、専用の占有領域を設けることなく高周波成分を伝達する容量素子を形成することができる。

【図面の簡単な説明】

【図1】本発明を適用した差動型入力回路の第1の実施例を示す回路図である。

【図2】第1実施例の入力回路の第1変形例を示す回路図である。

【図3】第1実施例の入力回路の第2変形例を示す回路図である。

【図4】第1実施例の入力回路の第3変形例を示す回路図である。

【図5】第1実施例の入力回路の第4変形例を示す回路図である。

【図6】第1実施例の入力回路の第5変形例を示す回路図である。

【図7】本発明を適用した差動型入力回路の第2の実施例を示す回路図である。

【図8】第2実施例の入力回路の第1変形例を示す回路図である。

【図9】第2実施例の入力回路の第2変形例を示す回路図である。

【図10】本発明を適用した差動型入力回路の第3の実施例を示す回路図である。

【図11】本発明を適用した差動型入力回路の第4の実施例を示す回路図である。

【図12】本実施例の入力回路と従来型の差動入力回路について、ゲイン特性とディレイ特性をシミュレーションによって求めた結果を示す特性図である。

【図13】本実施例の入力回路に対して、伝送線を介して1Gbpsのデータ信号を伝送したときの入出力信号の波形を示す波形図である。

【図14】差動入力MOSFETに入力信号の高周波成分を伝える容量の具体的な構成例を示す一部断面斜視図である。

【図15】図14の容量を構成する配線を切断した断面の構造を示す断面説明図である。

【図16】実施例の差動入力回路をゲートアレイに適用した場合のレイアウト構成例を示す平面図である。

【図17】図16のゲートアレイにおける入出力バッファ部のレイアウト構成例を示す平面図である。

【図18】実施例のゲートアレイの入出力バッファ部における電源安定化容量の構造の一例を示す断面図である。

【図19】実施例のゲートアレイにおける出力バッファと電源安定化容量の接続例を示す回路図である。

【図20】実施例のゲートアレイにおける入力信号の高周波成分を伝える容量を構成する第3メタル層からなる配線のパターン例を示す平面図である。

【図21】実施例のゲートアレイにおける入力信号の高周波成分を伝える容量を構成する第2メタル層からなる配線のパターン例を示す平面図である。

【図22】実施例のゲートアレイにおける入力信号の高周波成分を伝える容量を構成する第1メタル層からなる配線のパターン例を示す平面図である。

【図23】図22のA−A’線に沿った断面構造を示す断面図である。

【図24】半導体集積回路間の差動信号による信号伝送方式を示す回路図および伝送線の出力端と入力端での信号波形を示す波形図である。

【図25】従来の差動入力回路の一例を示す回路図である。

【図26】従来の差動入力回路の他の例を示す回路構成図である。

【符号の説明】

MN1,MN2 低周波成分増幅用差動入力MOSFET

MN4,MN5 高周波成分増幅用差動入力MOSFET

MP1,MP2 負荷MOSFET

MN3 定電流用MOSFET

R1,R2 バイアス用抵抗

Re1,Re2 終端抵抗

D1,D2 保護ダイオード

I/O 入出力バッファ部

BCL 基本論理セル

C11,C12 電源安定化容量

100 半導体チップ(半導体基板)

111 パッド形成領域

112 入力回路用静電保護ダイオード形成領域

113 出力P−MOS形成領域

114 出力バッファ用静電保護ダイオード形成領域

115 出力N−MOS形成領域

116 電源安定化容量形成領域

117 入力回路形成領域

121 MOSFETの拡散層

131 ポリシリコンゲート電極

Claims (21)

- 第1電源電位が供給される第1配線と、

第2電源電位が供給される第2配線と、

第1および第2配線との間に接続された入力回路とを有し、

上記入力回路は、

一対の入力端子と、

上記一対の入力端子に結合された一対の第1容量素子と、

上記一対の入力端子に上記一対の第1容量素子を介してそれぞれ接続された一対のゲート電極と、共通結合された一対のソース電極と、一対のドレイン電極とを有する一対の第1差動入力MOSトランジスタと、

上記第1差動入力MOSトランジスタの一対のドレイン電極と上記第1配線との間に接続された一対の負荷素子と、

上記共通結合された上記第1差動入力MOSトランジスタの一対のソース電極と上記第2配線との間に接続された電流源と、

上記一対の入力端子にそれぞれ接続された一対のゲート電極と、共通結合された一対のソース電極と、一対のドレイン電極とを有する一対の第2差動入力MOSトランジスタと、を含み、

上記一対の負荷素子は、上記第2差動入力MOSトランジスタの一対のドレイン電極のそれぞれと上記第1配線との間に接続され、

上記電流源は、上記第2差動入力MOSトランジスタの共通結合されたソース電極と上記第2配線との間に接続されている半導体集積回路装置。 - 第3電源電位が供給される第3配線と、

上記一対の第1差動入力MOSトランジスタのゲート電極と、それぞれを介して上記第3配線との間に接続された一対の第1抵抗素子をさらに有する請求項1に記載の半導体集積回路装置。 - 第4電源電位が供給される第4配線と、

上記一対の入力端子のそれぞれと上記第4配線との間に結合された一対の第2抵抗素子とをさらに有し、

上記一対の第1抵抗素子の抵抗値は、上記一対の第2抵抗素子のそれより大きくされる請求項2に記載の半導体集積回路装置。 - 上記第1配線と上記第2配線との間に結合された第2容量素子とさらに有し、

上記一対の第1容量素子のおのおのは、金属-絶縁膜-金属から構成され、

上記第2容量素子のそれぞれは、MOS構造で構成される請求項1に記載の半導体集積回路装置。 - 上記一対の第1容量素子のそれぞれは、

半導体基板の主面上の絶縁膜上に形成された導電層からなる第5配線と、

上記第5配線上に形成された第1絶縁層と、

上記第1絶縁層上に設けられた第6配線とを有し、

上記第6配線は対応する差動入力MOSトランジスタのゲート電極に結合され、

上記第5配線は対応する上記一対の入力端子の一方に結合される請求項1に記載の半導体集積回路装置。 - 上記第5配線は、上記第6配線の周囲を囲むように形成され、上記第1絶縁層は、上記第5配線と上記第6配線の間に形成される請求項4に記載の半導体集積回路装置。

- 上記一対の第1容量素子のそれぞれは、上記第6配線上に形成された第2絶縁層と、該第2絶縁層上に形成された第7配線とをさらに含み、

上記第7配線は対応する上記一対の入力端子の一方に結合される請求項4に記載の半導体集積回路装置。 - 上記一対の第1容量素子のそれぞれは、

上記第1絶縁層上に形成された第8配線と、

上記第5配線と上記第8配線との間に接続された第1接続線と、

上記第7配線と上記第8配線との間に接続された第2接続線と、をさらに含む請求項6に記載の半導体集積回路装置。 - 上記一対の第1容量素子のそれぞれは、

上記第1絶縁層上に設けられた第9配線をさらに含み、

上記第8配線と上記第9配線とは、上記第6配線の両サイドに配置され、

上記第5配線と上記第9配線との間に接続された第3接続線と、

上記第7配線と上記第9配線との間に接続された第4接続線と、をさらに含む請求項7に記載の半導体集積回路装置。 - 上記第5配線は、上記第6配線よりも幅広である請求項4に記載の半導体集積回路装置。

- 上記第7配線は、上記第6配線よりも幅広である請求項6に記載の半導体集積回路装置。

- 上記一対の入力端子のおのおのには、差動信号が入力される請求項1に記載の半導体集積回路装置。

- 上記第1電源電位は、上記第2電源電位より大きい請求項1に記載の半導体集積回路装置。

- 第1,第2入力端子と、第1入力回路を有し、

上記第1入力回路は、

第1入力端子に第1容量素子を介してゲート端子が接続された第1MOSトランジスタと、

第2入力端子に第2容量素子を介してゲート端子が接続され上記第1MOSトランジスタとソース共通結合された第2MOSトランジスタと、

上記第1MOSトランジスタのドレイン端子と第1電源電圧端子との間に接続された第1負荷素子と、

上記第2MOSトランジスタのドレイン端子と第1電源電圧端子との間に接続された第2負荷素子と、

上記第1MOSトランジスタと上記第2MOSトランジスタの共通ソース端子と第2電源電圧端子との間に接続された第1電流源と、

第1入力端子にゲート端子が接続された第3MOSトランジスタと、

第2入力端子にゲート端子が接続され、上記第3MOSトランジスタとソース共通結合された第4MOSトランジスタと、を有し、

上記第1負荷素子は、第1電源電圧端子と上記第1MOSトランジスタ及び第3MOSトランジスタのそれぞれのドレイン端子との間に接続され、

上記第2負荷素子は、第1電源電圧端子と上記第2MOSトランジスタ及び第4MOSトランジスタのそれぞれのドレイン端子との間に接続され、

上記第1電流源は、第2電源電圧端子と上記第1MOSトランジスタから上記第4MO Sトランジスタのそれぞれの共通ソース端子との間に接続された半導体集積回路装置。 - 上記入力回路は、第3電源電圧端子と上記第1MOSトランジスタと第2MOSトランジスタのそれぞれのゲート端子との間にそれぞれ接続された第1と第2抵抗素子を含む請求項14に記載の半導体集積回路装置。

- 第3と第4抵抗素子が、第4電源電圧端子と上記一対の入力端子との間にそれぞれ接続され、

上記一対の第1抵抗素子の抵抗値は、上記一対の第2抵抗素子の抵抗値より大きく設定された請求項15に記載の半導体集積回路装置。 - 上記入力回路は、

第1電源電圧端子と上記第1と第2MOSトランジスタのそれぞれのゲート端子との間にそれぞれ接続された第5MOSトランジスタ及び第6MOSトランジスタと、

第2電源電圧端子と上記第1と第2MOSトランジスタのゲート端子との間にそれぞれ接続された第7MOSトランジスタと第8MOSトランジスタと、

を含む請求項14に記載の半導体集積回路装置。 - 上記第1負荷素子と上記第2負荷素子は、MOSトランジスタにより構成されている請求項14に記載の半導体集積回路装置。

- 上記第1電源電位は、上記第2電源電位より大きく、

上記第3電源電位は、上記第2電源電位に上記第1または第2MOSトランジスタのしきい値電圧を加えた電位よりも大きく上記第1電源電位よりも小さい電位である請求項15に記載の半導体集積回路装置。 - 上記入力回路は、

第1入力端子に第1容量素子を介してゲート端子が接続された第9MOSトランジスタと、

第2入力端子に第2容量素子を介してゲート端子が接続され上記第9MOSトランジスタとソース共通結合された第10MOSトランジスタと、

上記第1入力端子にゲート端子が接続された第11MOSトランジスタと、

上記第2入力端子にゲート端子が接続され上記第11MOSトランジスタとソース共通結合された第12MOSトランジスタと、

上記第9MOSトランジスタと上記第11MOSトランジスタのそれぞれのドレイン端子と第1電源電圧端子との間に接続された第3負荷素子と、

上記第10MOSトランジスタと上記第12MOSトランジスタのそれぞれのドレイン端子と第1電源電圧端子との間に接続された第4負荷素子と、

第2電源電圧端子と上記第9から第12MOSトランジスタの共通ソース端子との間に接続された第2電流源と、

をさらに含む請求項14に記載の半導体集積回路装置。 - 上記入力回路は、

上記第1MOSトランジスタのドレイン端子にゲート端子が接続された第13MOSトランジスタと、

上記第10MOSトランジスタのドレイン端子にゲート端子が接続され、上記第13MOSトランジスタとソース共通結合された第14MOSトランジスタと、

上記第13MOSトランジスタのドレイン端子と第1電源電圧端子との間に接続された第5負荷素子と、

上記第14MOSトランジスタのドレイン端子と第1電源電圧端子との間に接続された 第6負荷素子と、

第2電源電圧端子と上記第13MOSトランジスタ及び第14MOSトランジスタの共通ソース端子との間に接続された第3電流源と、

をさらに含む請求項20に記載の半導体集積回路装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003001825A JP4076079B2 (ja) | 2003-01-08 | 2003-01-08 | 半導体集積回路装置および半導体集積回路 |

| US10/751,917 US7053670B2 (en) | 2003-01-08 | 2004-01-07 | Semiconductor integrated circuit device and semiconductor integrated circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003001825A JP4076079B2 (ja) | 2003-01-08 | 2003-01-08 | 半導体集積回路装置および半導体集積回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004215137A JP2004215137A (ja) | 2004-07-29 |

| JP2004215137A5 JP2004215137A5 (ja) | 2006-02-23 |

| JP4076079B2 true JP4076079B2 (ja) | 2008-04-16 |

Family

ID=32767188

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003001825A Expired - Fee Related JP4076079B2 (ja) | 2003-01-08 | 2003-01-08 | 半導体集積回路装置および半導体集積回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7053670B2 (ja) |

| JP (1) | JP4076079B2 (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CA2263061C (en) * | 1999-02-26 | 2011-01-25 | Ki-Jun Lee | Dual control analog delay element |

| US7692453B2 (en) * | 2004-08-11 | 2010-04-06 | Atmel Corporation | Detector of differential threshold voltage |

| JP2006211514A (ja) * | 2005-01-31 | 2006-08-10 | Kawasaki Microelectronics Kk | 出力回路を備えた半導体集積回路 |

| JP4546288B2 (ja) * | 2005-02-28 | 2010-09-15 | 株式会社リコー | 差動出力回路及びその差動出力回路を有する半導体装置 |

| US7190193B1 (en) * | 2005-04-21 | 2007-03-13 | Xilinx, Inc. | Method and apparatus for a differential driver with voltage translation |

| US20070159744A1 (en) * | 2006-01-06 | 2007-07-12 | Ramen Dutta | High voltage pin for low voltage process |

| US7525384B2 (en) * | 2006-10-17 | 2009-04-28 | Avago Technologies Wireless Ip (Singapore) Pte. Ltd. | Transmission line amplifier |

| US7701259B2 (en) * | 2006-12-06 | 2010-04-20 | Broadcom Corporation | Method and system for wide range amplitude detection |

| US7594198B2 (en) * | 2007-02-27 | 2009-09-22 | Taiwan Semiconductor Manufacturing Co., Ltd. | Ultra fine pitch I/O design for microchips |

| US7609093B2 (en) * | 2007-08-03 | 2009-10-27 | Tower Semiconductor Ltd. | Comparator with low supply current spike and input offset cancellation |

| JP5407226B2 (ja) * | 2008-09-01 | 2014-02-05 | 富士通株式会社 | 信号伝送システム評価装置、信号伝送システム評価プログラム、信号伝送システム設計方法 |

| JP5421300B2 (ja) * | 2011-01-19 | 2014-02-19 | 日本電信電話株式会社 | クロック入力インターフェース回路 |

| CN103493375A (zh) | 2011-05-13 | 2014-01-01 | 松下电器产业株式会社 | 信号电位变换电路 |

| JP2014007458A (ja) * | 2012-06-21 | 2014-01-16 | Nec Engineering Ltd | 受信回路 |

| JP6106045B2 (ja) * | 2013-03-22 | 2017-03-29 | 株式会社東芝 | 受光回路 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4577162A (en) * | 1985-04-29 | 1986-03-18 | Motorola, Inc. | Clocked gain stage having differential inputs and outputs |

| US5032744A (en) * | 1989-10-31 | 1991-07-16 | Vlsi Technology, Inc. | High speed comparator with offset cancellation |

| JPH10145348A (ja) * | 1996-09-13 | 1998-05-29 | Nec Corp | クロック抽出回路 |

| JP3697847B2 (ja) * | 1997-08-21 | 2005-09-21 | ソニー株式会社 | 電圧制御発振回路 |

| US5990707A (en) * | 1997-09-05 | 1999-11-23 | Cirrus Logic, Inc. | Method and system for sliced integration of flash analog to digital converters in read channel circuits |

| US6459306B1 (en) * | 1999-07-22 | 2002-10-01 | Lucent Technologies Inc. | Low power differential comparator with stable hysteresis |

| US6529070B1 (en) * | 1999-10-25 | 2003-03-04 | Texas Instruments Incorporated | Low-voltage, broadband operational amplifier |

| TW445714B (en) * | 2000-05-05 | 2001-07-11 | Ind Tech Res Inst | Capacitor-coupled differential logic circuit |

| US6617899B2 (en) * | 2001-05-25 | 2003-09-09 | Infineon Technologies Ag | Ultra high speed clocked analog latch |

| US6628224B1 (en) * | 2002-05-24 | 2003-09-30 | Broadcom Corporation | Distributed averaging analog to digital converter topology |

-

2003

- 2003-01-08 JP JP2003001825A patent/JP4076079B2/ja not_active Expired - Fee Related

-

2004

- 2004-01-07 US US10/751,917 patent/US7053670B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004215137A (ja) | 2004-07-29 |

| US7053670B2 (en) | 2006-05-30 |

| US20040150459A1 (en) | 2004-08-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4076079B2 (ja) | 半導体集積回路装置および半導体集積回路 | |

| US11075671B2 (en) | Configurable, power supply voltage referenced single-ended signaling with ESD protection | |

| KR100304334B1 (ko) | 제어가능한 임피던스를 구비한 집적 회로 | |

| US6670830B2 (en) | Driver circuit, receiver circuit, and signal transmission bus system | |

| CN1671040B (zh) | 低噪声运算放大器 | |

| US7821297B2 (en) | Low power output driver | |

| US9379707B2 (en) | Decoupling circuit and semiconductor integrated circuit | |

| Maundy et al. | A new design topology for low-voltage CMOS current feedback amplifiers | |

| US9595498B2 (en) | Semiconductor memory device having pads | |

| US7304506B2 (en) | Differential output circuit and semiconductor device having the same | |

| US6628158B2 (en) | Integrated circuit and method for minimizing clock skews | |

| US6731164B2 (en) | Capacitor current multiplier capacitive feedback circuit | |

| US20040120087A1 (en) | Semiconductor device including a plurality of power domains | |

| JP3883114B2 (ja) | 半導体装置 | |

| Huang et al. | Differential bidirectional transceiver for on-chip long wires | |

| US7132727B2 (en) | Layout technique for C3MOS inductive broadbanding | |

| US20030034829A1 (en) | Apparatus for on-chip reference voltage generator for receivers in high speed single-ended data link | |

| Jackson et al. | A CMOS mixed signal simultaneous bidirectional signaling I/O | |

| JP2017098926A (ja) | 半導体装置 | |

| US20180342987A1 (en) | Integrated circuit device | |

| JP3455463B2 (ja) | 入力バッファ回路 | |

| KR940008713B1 (ko) | 출력잡음이 감소된 데이타출력버퍼 | |

| KR100567384B1 (ko) | 지터특성과 동작 주파수 대역폭을 개선하기 위한 드라이버및 상기 드라이버를 구비하는 집적회로 | |

| Sansen et al. | Coupling effects in Mixed analog-digital ICs | |

| JPH04157921A (ja) | 半導体集積回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060106 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060106 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080108 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080124 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080124 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4076079 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110208 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110208 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120208 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120208 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130208 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130208 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |