JP4076079B2 - 半導体集積回路装置および半導体集積回路 - Google Patents

半導体集積回路装置および半導体集積回路 Download PDFInfo

- Publication number

- JP4076079B2 JP4076079B2 JP2003001825A JP2003001825A JP4076079B2 JP 4076079 B2 JP4076079 B2 JP 4076079B2 JP 2003001825 A JP2003001825 A JP 2003001825A JP 2003001825 A JP2003001825 A JP 2003001825A JP 4076079 B2 JP4076079 B2 JP 4076079B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- mos transistor

- input

- pair

- terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/0264—Arrangements for coupling to transmission lines

- H04L25/0272—Arrangements for coupling to multiple lines, e.g. for differential transmission

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/003—Changing the DC level

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

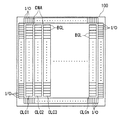

- H10D84/90—Masterslice integrated circuits

- H10D84/903—Masterslice integrated circuits comprising field effect technology

- H10D84/907—CMOS gate arrays

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/0264—Arrangements for coupling to transmission lines

- H04L25/0292—Arrangements specific to the receiver end

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Power Engineering (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Amplifiers (AREA)

- Semiconductor Integrated Circuits (AREA)

- Logic Circuits (AREA)

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003001825A JP4076079B2 (ja) | 2003-01-08 | 2003-01-08 | 半導体集積回路装置および半導体集積回路 |

| US10/751,917 US7053670B2 (en) | 2003-01-08 | 2004-01-07 | Semiconductor integrated circuit device and semiconductor integrated circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003001825A JP4076079B2 (ja) | 2003-01-08 | 2003-01-08 | 半導体集積回路装置および半導体集積回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004215137A JP2004215137A (ja) | 2004-07-29 |

| JP2004215137A5 JP2004215137A5 (enExample) | 2006-02-23 |

| JP4076079B2 true JP4076079B2 (ja) | 2008-04-16 |

Family

ID=32767188

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003001825A Expired - Fee Related JP4076079B2 (ja) | 2003-01-08 | 2003-01-08 | 半導体集積回路装置および半導体集積回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7053670B2 (enExample) |

| JP (1) | JP4076079B2 (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8884680B2 (en) | 2011-05-13 | 2014-11-11 | Panasonic Corporation | Signal electric potential conversion circuit |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CA2263061C (en) * | 1999-02-26 | 2011-01-25 | Ki-Jun Lee | Dual control analog delay element |

| US7692453B2 (en) * | 2004-08-11 | 2010-04-06 | Atmel Corporation | Detector of differential threshold voltage |

| JP2006211514A (ja) * | 2005-01-31 | 2006-08-10 | Kawasaki Microelectronics Kk | 出力回路を備えた半導体集積回路 |

| JP4546288B2 (ja) * | 2005-02-28 | 2010-09-15 | 株式会社リコー | 差動出力回路及びその差動出力回路を有する半導体装置 |

| US7190193B1 (en) * | 2005-04-21 | 2007-03-13 | Xilinx, Inc. | Method and apparatus for a differential driver with voltage translation |

| US20070159744A1 (en) * | 2006-01-06 | 2007-07-12 | Ramen Dutta | High voltage pin for low voltage process |

| US7525384B2 (en) * | 2006-10-17 | 2009-04-28 | Avago Technologies Wireless Ip (Singapore) Pte. Ltd. | Transmission line amplifier |

| US7701259B2 (en) * | 2006-12-06 | 2010-04-20 | Broadcom Corporation | Method and system for wide range amplitude detection |

| US7594198B2 (en) * | 2007-02-27 | 2009-09-22 | Taiwan Semiconductor Manufacturing Co., Ltd. | Ultra fine pitch I/O design for microchips |

| US7609093B2 (en) * | 2007-08-03 | 2009-10-27 | Tower Semiconductor Ltd. | Comparator with low supply current spike and input offset cancellation |

| JP5407226B2 (ja) * | 2008-09-01 | 2014-02-05 | 富士通株式会社 | 信号伝送システム評価装置、信号伝送システム評価プログラム、信号伝送システム設計方法 |

| JP5421300B2 (ja) * | 2011-01-19 | 2014-02-19 | 日本電信電話株式会社 | クロック入力インターフェース回路 |

| JP2014007458A (ja) * | 2012-06-21 | 2014-01-16 | Nec Engineering Ltd | 受信回路 |

| JP6106045B2 (ja) * | 2013-03-22 | 2017-03-29 | 株式会社東芝 | 受光回路 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4577162A (en) * | 1985-04-29 | 1986-03-18 | Motorola, Inc. | Clocked gain stage having differential inputs and outputs |

| US5032744A (en) * | 1989-10-31 | 1991-07-16 | Vlsi Technology, Inc. | High speed comparator with offset cancellation |

| JPH10145348A (ja) * | 1996-09-13 | 1998-05-29 | Nec Corp | クロック抽出回路 |

| JP3697847B2 (ja) * | 1997-08-21 | 2005-09-21 | ソニー株式会社 | 電圧制御発振回路 |

| US5990707A (en) * | 1997-09-05 | 1999-11-23 | Cirrus Logic, Inc. | Method and system for sliced integration of flash analog to digital converters in read channel circuits |

| US6459306B1 (en) * | 1999-07-22 | 2002-10-01 | Lucent Technologies Inc. | Low power differential comparator with stable hysteresis |

| US6529070B1 (en) * | 1999-10-25 | 2003-03-04 | Texas Instruments Incorporated | Low-voltage, broadband operational amplifier |

| TW445714B (en) * | 2000-05-05 | 2001-07-11 | Ind Tech Res Inst | Capacitor-coupled differential logic circuit |

| US6617899B2 (en) * | 2001-05-25 | 2003-09-09 | Infineon Technologies Ag | Ultra high speed clocked analog latch |

| US6628224B1 (en) * | 2002-05-24 | 2003-09-30 | Broadcom Corporation | Distributed averaging analog to digital converter topology |

-

2003

- 2003-01-08 JP JP2003001825A patent/JP4076079B2/ja not_active Expired - Fee Related

-

2004

- 2004-01-07 US US10/751,917 patent/US7053670B2/en not_active Expired - Lifetime

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8884680B2 (en) | 2011-05-13 | 2014-11-11 | Panasonic Corporation | Signal electric potential conversion circuit |

Also Published As

| Publication number | Publication date |

|---|---|

| US20040150459A1 (en) | 2004-08-05 |

| US7053670B2 (en) | 2006-05-30 |

| JP2004215137A (ja) | 2004-07-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4076079B2 (ja) | 半導体集積回路装置および半導体集積回路 | |

| US11075671B2 (en) | Configurable, power supply voltage referenced single-ended signaling with ESD protection | |

| KR100304334B1 (ko) | 제어가능한 임피던스를 구비한 집적 회로 | |

| US6670830B2 (en) | Driver circuit, receiver circuit, and signal transmission bus system | |

| US7821297B2 (en) | Low power output driver | |

| US9379707B2 (en) | Decoupling circuit and semiconductor integrated circuit | |

| Maundy et al. | A new design topology for low-voltage CMOS current feedback amplifiers | |

| US9595498B2 (en) | Semiconductor memory device having pads | |

| US6628158B2 (en) | Integrated circuit and method for minimizing clock skews | |

| CN208093537U (zh) | 半导体装置和电子电路 | |

| US6731164B2 (en) | Capacitor current multiplier capacitive feedback circuit | |

| US20040120087A1 (en) | Semiconductor device including a plurality of power domains | |

| US7304506B2 (en) | Differential output circuit and semiconductor device having the same | |

| JP3883114B2 (ja) | 半導体装置 | |

| KR102676802B1 (ko) | 반도체 장치 | |

| US20030034829A1 (en) | Apparatus for on-chip reference voltage generator for receivers in high speed single-ended data link | |

| Jackson et al. | A CMOS mixed signal simultaneous bidirectional signaling I/O | |

| US10396719B2 (en) | Integrated circuit device | |

| JP3455463B2 (ja) | 入力バッファ回路 | |

| JP2011182266A (ja) | 差動信号受信回路及び半導体装置 | |

| Sansen | Coupling effects in Mixed analog-digital ICs | |

| JPH04157921A (ja) | 半導体集積回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060106 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060106 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080108 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080124 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080124 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4076079 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110208 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110208 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120208 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120208 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130208 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130208 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |