JP4004151B2 - 出力回路 - Google Patents

出力回路 Download PDFInfo

- Publication number

- JP4004151B2 JP4004151B2 JP27899498A JP27899498A JP4004151B2 JP 4004151 B2 JP4004151 B2 JP 4004151B2 JP 27899498 A JP27899498 A JP 27899498A JP 27899498 A JP27899498 A JP 27899498A JP 4004151 B2 JP4004151 B2 JP 4004151B2

- Authority

- JP

- Japan

- Prior art keywords

- output

- transistor

- circuit

- output terminal

- transistors

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

本発明は、CMOSまたはBiCMOSにより構成され、TTLの出力特性を有する出力回路に関するものである。

【0002】

【従来の技術】

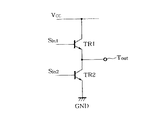

一般的なTTL回路の出力部は、図3に示すような構成を有し、バイポーラトランジスタ、例えば、npnトランジスタTR1とTR2により構成されている。

トランジスタTR1は電源電圧VCCの供給線と出力端子Tout との間に接続され、そのベースに入力される信号Sin1 に応じてオンまたはオフする。トランジスタTR2は出力端子Tout と接地電位GNDとの間に接続され、そのベースに入力される信号Sin2 に応じてオンまたはオフする。

【0003】

ここで、トランジスタTR1とTR2のベース・エミッタ間順方向電圧をVBEとすると、入力信号Sin2 が電圧VBE以上のレベルにあるとき、トランジスタTR2がオンし、出力端子Tout がローレベルVCE2 に保持される。なお、VCE2 はトランジスタTR2の飽和時のコレクタ・エミッタ間電圧である。

入力信号Sin1 がハイレベルにあるとき、トランジスタTR1がオンし、このとき、出力端子Tout はハイレベル、例えば、(VCC−VBE1 )に保持される。ここで、VBE1 はトランジスタTR1のベース・エミッタ間電圧である。

なお、TTL回路の出力部において、回路構成上信号Sin1 とSin2 が同時にハイレベルにあることは禁止されている。

【0004】

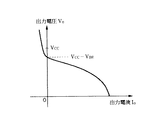

図4は上述したTTL回路の出力部の出力特性を示している。

図示のように、当該出力部において、出力端子Tout に(VCC−VBE)以上の電圧が出力されている場合、高インピーダンス状態となり、それ以外のとき低インピーダンス状態となる。また、図3の回路図において、出力端子Tout がハイレベルまたはローレベルの何れのときにおいても、トランジスタTR1またはTR2の何れかがオンする。即ち、出力端子Tout は出力レベルにかかわらず出力インピーダンスが低く設定されている。このため、当該出力部により比較的に長い伝送線を駆動する場合、伝送線の浮遊容量、負荷回路の入力容量などの容量負荷の充放電を高速に行うことができ、伝送線におけるリンギング(発振状態)の発生を回避できる。

【0005】

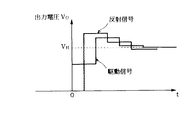

図5は図3に示すTTL回路の出力部の出力特性に基づくBERGERON解析の結果を示しいている。図6は、出力部の駆動信号波形および負荷からの反射信号波形をそれぞれ示している。

【0006】

なお、図6は負荷回路をローレベルからハイレベルに駆動する場合の信号波形を示している。図6に示すように、信号伝送線および負荷回路の電圧レベルの変動でリングングが発生するが、駆動信号および負荷からの反射信号において、リンギングにより生じた振幅の変動は急速に収束し、電圧VH に安定する。

【0007】

【発明が解決しようとする課題】

ところで、上述した従来のTTL回路の出力部においては、バイポーラトランジスタを用いているため、低電圧化した場合、例えば、電源電圧VCCが1.8〜3.3Vの場合、出力電圧VO のハイレベルVH は(VCC−VBE)となり、電源電圧VCCよりもベース・エミッタ間電圧VBEだけ低くなり、十分なハイレベル“H”のロジックを形成しない。このため、現在では、CMOSにおけるpチャネルトランジスタによってバイポーラトランジスタにおける上記電圧降下を防止し、ハイロジック“H”の伝達を実現している。

しかし、このような出力構成とした場合、pチャネルトランジスタのオン特性に極性がないため、大きなリンギングが発生してしまうという不利益がある。

【0008】

図7は、CMOSにより構成された出力部の出力特性およびそれに基づくBERGERON解析の結果を示しいている。図8はCMOSにより構成された出力部の出力信号波形および負荷からの反射信号波形をそれぞれ示している。図7に示すように、バイポーラトランジスタで構成されたTTL回路の出力部とは異なり、出力電圧VO が電源電圧VCCを越えたときでも、出力インピーダンスは大きくならない。このため、図8に示すように、例えば、出力部により負荷をローレベルからハイレベルに駆動する場合、伝送線および負荷回路の電圧レベルの変化により、リンギングが発生し、振幅の大きな反射波が現れる。

このようにCMOSを構成するpチャネルトランジスタのオン特性に極性がないため、反射波の振幅を急速に収束させることができず、立ち上がりからある程度時間が経過したあとでもリンギングが収まらない。このリンギングにより、負荷回路の誤動作が生ずるおそれがある。

【0009】

リンギングを防止するため、種々の対策が講じられてきた。1つの方法として、出力部にダンピング抵抗を付加し、伝送線路とのマッチング(インピーダンス整合)を行うものである。しかしながら、この方法はインピーダンス整合をとるために所定の抵抗値を持つダンピング抵抗を外付けで処理することが一般的であり、また、ICチップ内部でインピーダンスを整合させた場合、スピードの低下が問題となる。

【0010】

もう1つの方法として、出力トランジェントコントロール(出力過渡制御)がある。この方法は、反射信号によるリンギングを避けるため、進行波と反射波によって発生した合成電圧を抑制するために出力のトランジェントを信号の往復伝送時間と同一または遅く制御する。しかし、この方法では回路内部の遅延の増大が問題となり、高速な駆動を必要な場合に使用できない。

【0011】

本発明は、かかる事情に鑑みてなされたものであり、その目的は、CMOSまたはBiCMOSにより構成された出力回路において、オン抵抗を制御することにより出力インピーダンスを整合させ、リンギングの発生を抑制でき、誤動作を防止できる出力回路を提供することにある。

【0012】

【課題を解決するための手段】

上記目的を達成するため、本発明の出力回路は、第1の電圧源と出力端子との間に直列に接続されている第1の整流素子及び第1導電型の第1のMOSトランジスタと、上記第1の電圧源と上記出力端子との間に接続されている第1導電型の第2のMOSトランジスタと、上記第1及び第2のMOSトランジスタの制御端子に接続されている第1の入力端子と、上記出力端子と第2の電圧源との間に直列に接続されている第2導電型の第3のMOSトランジスタ及び第2の整流素子と、上記出力端子と上記第2の電圧源との間に接続されている第2導電型の第4のMOSトランジスタと、上記第3及び第4のMOSトランジスタの制御端子に接続されている第2の入力端子と、を有し、

上記出力端子に接続される信号伝送線の特性インピーダンスと上記第2及び第4の MOS トランジスタのオン抵抗の値とが整合されている。

【0013】

好ましくは、上記信号伝送線の特性インピーダンスが 75 〜 100 Ωの範囲にあり、上記第 2 及び第 4 の MOS トランジスタのオン抵抗が 75 Ω以上である。

【0014】

また好ましくは、上記第 1 及び第 2 の MOS トランジスタが pMOS トランジスタであり、上記第 3 及び第 4 の MOS トランジスタが nMOS トランジスタであり、上記第 1 の整流素子はアノードが上記第 1 の電圧源に接続され、カソードが上記第 1 の MOS トランジスタに接続されているダイオードであり、上記第 2 の整流素子はアノードが上記第 1 の MOS トランジスタに接続され、カソードが上記第 2 の電圧源に接続されているダイオードである。

【0016】

【発明の実施の形態】

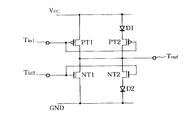

図1は本発明に係る出力回路の一実施形態を示す回路図である。

図示のように、本実施形態の出力回路は、pMOSトランジスタPT1,PT2、nMOSトランジスタNT1,NT2およびダイオードD1,D2により構成されている。

【0017】

pMOSトランジスタPT1のゲートが入力端子Tin1 に接続され、ソースが電源電圧VCCの供給線に接続され、ドレインが出力端子Tout に接続されている。ダイオードD1のアノードが電源電圧VCCの供給線に接続され、カソードがpMOSトランジスタPT2のソースに接続されている。pMOSトランジスタPT2のゲートが入力端子Tin1 に接続され、ドレインが出力端子Tout に接続されている。

【0018】

nMOSトランジスタNT1のゲートが入力端子Tin2 に接続され、ドレインが出力端子Tout に接続され、ソースが接地されている。nMOSトランジスタNT2のゲートが入力端子Tin2 に接続され、ドレインが出力端子Tout に接続され、ソースがダイオードD2のアノードに接続されている。ダイオードD2のカソードが接地されている。

なお、電源電圧VCCの供給線と出力端子Tout との間に直列接続されているダイオードD1とトランジスタPT2が互いに入れ代わってもよく、出力端子Tout と接地線との間に直列接続されているダイオードD2とトランジスタNT2が互いに入れ代わってもよい。

【0019】

このような構成を有する出力回路において、入力端子Tin1 およびTin2 に印加される入力信号に応じて、トランジスタPT1,PT2,NT1,NT2がオン/オフし、これらのトランジスタのオン/オフ状態に応じて出力端子Tout のレベルが制御される。

【0020】

例えば、入力端子Tin1 にローレベルの入力信号が印加されたとき、トランジスタPT1とPT2がオンし、出力端子Tout はほぼ電源電圧VCCレベルに保持される。入力端子Tin2 にハイレベルの入力信号が印加されたとき、トランジスタNT1とNT2がオンし、出力端子Tout はほぼ接地電位GNDに保持される。

入力端子Tin1 にハイレベル、入力端子Tin2 にローレベルの信号が印加されたとき、トランジスタPT1,PT2,NT1およびNT2がともにオフするので、出力端子Tout がハイインピーダンス状態に保持される。なお、入力端子Tin1 にローレベル、入力端子Tin2 にハイレベルの信号が印加されたとき、トランジスタPT1,PT2,NT1およびNT2がともにオンし、これらのトランジスタに貫通電流が流れるので、このような入力信号の組み合わせは禁止される。実際には、入力端子Tin1 とTin2 が互いに接続されて使用される場合が多く、この場合入力信号のレベルが切り換わるときを除き、pチャネル側とnチャネル側の何れか一方のみがオンするので、貫通電流は流れない。

【0021】

以下、本実施形態の出力回路の動作について説明する。

入力端子Tin1 ,Tin2 にローレベルの信号が入力されたとき、トランジスタPT1,PT2がオンし、トランジスタNT1,NT2がオフする。このとき、出力端子Tout はほぼ電源電圧VCCレベルに保持される。即ち、出力端子Tout はハイロジック“H”となる。このときの出力インピーダンスは、トランジスタPT1のオン抵抗、ダイオードD1とトランジスタPT2のオン抵抗との直列回路の合成抵抗により決まる。

【0022】

ダイオードD1の順方向電圧をVF とすると、出力電圧VO が(VCC−VF )より低いとき、ダイオードD1がオンし、出力抵抗は低くなる。この場合、トランジスタPT1およびダイオードD1とトランジスタPT2との直列回路を介して、出力端子Tout に接続されている容量負荷が充電される。さらに、ダイオードD2のサイズを大きく形成することにより、その駆動能力が大きく、容量負荷の充電が高速に行える。

容量負荷が十分に充電された場合、また、反射信号により出力電圧VO が上昇し、(VCC−VF )と等しく、またはそれより高いとき、ダイオードD1は逆バイアス状態にあり、カットオフされる。このとき、トランジスタPT1のみがオンし、出力インピーダンスが大きくなる。

【0023】

通常リンギング発生しやすい条件は、出力端子Tout に接続されている伝送線が比較的に長く、且つ伝送線の特性インピーダンスが75〜100Ωである。このため、トランジスタPT1のオン抵抗を75Ω以上に設定することにより、出力インピーダンスの整合がほぼ整えられ、リンギングの発生を防止できる。

【0024】

次に、出力端子Tout がローレベル、即ち、“L”ロジックの場合について説明する。入力端子Tin1 およびTin2 にハイレベルの信号が入力されたとき、トランジスタNT1,NT2がオンし、トランジスタPT1,PT2がオフする。このとき、出力端子Tout に接続されている伝送線および負荷回路は、トランジスタNT1およびトランジスタNT2とダイオードD2との直列回路を介して放電され、出力電圧VO は低下し、最後にほぼ接地電位GNDに達する。

ダイオードD2のサイズを大きく形成し、その駆動能力を大きくすることによって、伝送線および負荷回路の放電は高速に行える。

【0025】

ここで、ダイオードD2の順方向電圧をダイオードD1と同じくVF とすると、出力電圧VO がVF より高いとき、ダイオードD2がオンし、出力インピーダンスはトランジスタNT1のオン抵抗、直列接続されているダイオードD2とトランジスタNT2のオン抵抗との合成抵抗により決まる。反射波などにより出力電圧VO がが低下し、VF と等しくなり、またはVF より低くなると、ダイオードD2が逆バイアスされ、カットオフされる。このときの出力抵抗はトランジスタNT1のオン抵抗のみとなる。ここで、上述したpMOSトランジスタPT1と同様に、トランジスタNT1のオン抵抗を75Ω以上に設定することにより、出力インピーダンスの整合がほぼ整えられ、リンギングの発生を防止できる。

【0026】

図2は、本実施形態の出力回路の等価回路を示している。当該等価回路において、抵抗R1はトランジスタPT1のオン抵抗、抵抗R2はトランジスタPT2のオン抵抗である。同じように、抵抗R3はトランジスタNT1のオン抵抗、抵抗R4はトランジスタNT2のオン抵抗である。通常、抵抗R1およびR3は75〜100Ωに設定され、抵抗R2およびR4は10〜50Ωに設定される。

【0027】

等価回路におけるスイッチSWは、入力信号Sinに応じて切り換えられる。スイッチSWが抵抗R1,R2側に接続されているとき、出力端子Tout はロジック“H”となる。こととき出力電圧VO に応じてダイオードD1のバイアス状態が制御され、出力インピーダンスの調整が行われる。また、スイッチSWが抵抗R3,R4側に接続されているとき、出力端子Tout はロジック“L”となる。このとき出力電圧VO に応じてダイオードD2のバイアス状態が制御され、出力インピーダンスの調整が行われる。何れの場合においても出力インピーダンスが伝送線および負荷回路の入力インピーダンスと整合するように制御されるので、リンギングの発生を防止できる。

【0028】

以上説明したように、本実施形態によれば、電源電圧VCCの供給線と出力端子Tout 間にトランジスタPT1およびダイオードD1とトランジスタPT2との直列回路を接続し、入力端子Tin1 の入力信号に応じてトランジスタPT1,PT2をオン/オフさせ、出力端子Tout と接地電位間にトランジスタNT1およびダイオードD2とトランジスタNT2との直列回路を接続し、入力端子Tin2 の入力信号に応じてトランジスタNT1,NT2をオン/オフさせ、出力端子Tout の電圧VO に応じてダイオードD1またはD2のバイアス状態を制御し、出力インピーダンスを調整するので、出力インピーダンスの整合を実現でき、リンギングの発生を抑制可能である。

【0029】

【発明の効果】

以上説明したように、本発明の出力回路によれば、CMOSまたはBiCMOSで構成でき、入力インピーダンスを高くでき、且つ従来のTTL回路の出力特性に近い出力特性が得られる。さらに、本発明の出力回路は低電圧化の場合でもTTL回路とほぼ同様な出力特性が得られ、リンギングの発生を抑制可能である。

また、本発明の出力回路は、トランジェントコントロールなどの遅延に影響される回路を必要としないため、高速化できる。さらに出力波形の変化速度は出力電圧に応じて変わり、出力電圧が所定のスレッショルドレベルを越えたとき高速に変化し、それ以降は緩やかに変化するので、EMIノイズの発生を低減できる。

本発明によれば、回路の構成は簡単であり、従来の回路に比べてコストの低減を容易に実現できる利点がある。

【図面の簡単な説明】

【図1】本発明に係る出力回路の一実施形態を示す回路図である。

【図2】図1に示す出力回路の等価回路図である。

【図3】一般的なTTL回路の出力部の構成を示す回路図である。

【図4】TTL回路の出力部の出力特性を示すグラフである。

【図5】TTL回路の出力部の出力特性に基づくBERGERON解析を示すグラフである。

【図6】TTL回路の出力部における駆動信号と反射信号の波形図である。

【図7】CMOS出力回路の出力特性に基づくBERGERON解析を示すグラフである。

【図8】CMOS出力回路における駆動信号と反射信号の波形図である。

【符号の説明】

PT1,PT2…pMOSトランジスタ、

NT1,NT2…nMOSトランジスタ、

D1,D2…ダイオード、

R1,R2,R3,R4…等価抵抗、

VCC…電源電圧、GND…接地電位。

Claims (3)

- 第1の電圧源と出力端子との間に直列に接続されている第1の整流素子及び第1導電型の第1のMOSトランジスタと、

上記第1の電圧源と上記出力端子との間に接続されている第1導電型の第2のMOSトランジスタと、

上記第1及び第2のMOSトランジスタの制御端子に接続されている第1の入力端子と、

上記出力端子と第2の電圧源との間に直列に接続されている第2導電型の第3のMOSトランジスタ及び第2の整流素子と、

上記出力端子と上記第2の電圧源との間に接続されている第2導電型の第4のMOSトランジスタと、

上記第3及び第4のMOSトランジスタの制御端子に接続されている第2の入力端子と、

を有し、

上記出力端子に接続される信号伝送線の特性インピーダンスと上記第2及び第4の MOS トランジスタのオン抵抗の値とが整合されている

出力回路。 - 上記信号伝送線の特性インピーダンスが 75 〜 100 Ωの範囲にあり、上記第 2 及び第 4 の MOS トランジスタのオン抵抗が 75 Ω以上である請求項1に記載の出力回路。

- 上記第 1 及び第 2 の MOS トランジスタが pMOS トランジスタであり、上記第 3 及び第 4 の MOS トランジスタが nMOS トランジスタであり、上記第 1 の整流素子はアノードが上記第 1 の電圧源に接続され、カソードが上記第 1 の MOS トランジスタに接続されているダイオードであり、上記第 2 の整流素子はアノードが上記第 1 の MOS トランジスタに接続され、カソードが上記第 2 の電圧源に接続されているダイオードである請求項 1 又は 2 に記載の出力回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP27899498A JP4004151B2 (ja) | 1998-09-30 | 1998-09-30 | 出力回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP27899498A JP4004151B2 (ja) | 1998-09-30 | 1998-09-30 | 出力回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000114955A JP2000114955A (ja) | 2000-04-21 |

| JP2000114955A5 JP2000114955A5 (ja) | 2005-10-27 |

| JP4004151B2 true JP4004151B2 (ja) | 2007-11-07 |

Family

ID=17604932

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP27899498A Expired - Fee Related JP4004151B2 (ja) | 1998-09-30 | 1998-09-30 | 出力回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4004151B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5447575B2 (ja) * | 2012-04-23 | 2014-03-19 | 株式会社デンソー | 駆動装置 |

-

1998

- 1998-09-30 JP JP27899498A patent/JP4004151B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000114955A (ja) | 2000-04-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100351530B1 (ko) | 언더슈트 억제 전계효과 트랜지스터 스위치 | |

| JPH0865143A (ja) | ノイズの影響を受けないリセット優先レベルシフト回路 | |

| KR900008801B1 (ko) | 논리회로 | |

| US4782252A (en) | Output current control circuit for reducing ground bounce noise | |

| JP2647014B2 (ja) | BiCMOS論理回路 | |

| US4839537A (en) | BicMO logic circuit | |

| US5254885A (en) | Bi-CMOS logic circuit with feedback | |

| US5166551A (en) | High speed output circuit without fluctuation for semiconductor integrated circuits | |

| EP0511643B1 (en) | Output buffer circuit | |

| KR970006874B1 (ko) | 달링톤 BiCMOS 구동기 회로 | |

| JP4004151B2 (ja) | 出力回路 | |

| US6489815B2 (en) | Low-noise buffer circuit that suppresses current variation | |

| GB2305793A (en) | A tri-state driver and circuit | |

| EP0426547B1 (en) | Bi-CMOS circuit | |

| EP0645890B1 (en) | BiCMOS logic circuit | |

| KR940005975B1 (ko) | 출력회로 | |

| US5103119A (en) | Ttl-level bicmos driver | |

| US6847235B2 (en) | Bus driver | |

| JPH03169119A (ja) | 出力回路 | |

| JPH03123220A (ja) | 出力回路 | |

| JPH0358620A (ja) | BiMOS型半導体集積回路 | |

| JP2569861B2 (ja) | BiCMOS集積回路 | |

| KR20040053772A (ko) | 반도체장치 | |

| JP2004072424A (ja) | Mosゲートトランジスタのゲート駆動回路 | |

| JPH0766708A (ja) | 入力バッファゲート |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050826 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050826 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070420 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070424 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070625 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070724 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070821 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100831 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110831 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120831 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120831 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130831 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |