JP3998470B2 - 液晶表示装置および表示システム - Google Patents

液晶表示装置および表示システム Download PDFInfo

- Publication number

- JP3998470B2 JP3998470B2 JP2001390158A JP2001390158A JP3998470B2 JP 3998470 B2 JP3998470 B2 JP 3998470B2 JP 2001390158 A JP2001390158 A JP 2001390158A JP 2001390158 A JP2001390158 A JP 2001390158A JP 3998470 B2 JP3998470 B2 JP 3998470B2

- Authority

- JP

- Japan

- Prior art keywords

- image display

- display elements

- capacitor

- liquid crystal

- diffusion layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

本発明は、液晶表示装置の技術分野に関し、特に、反射型アクティブマトリクス液晶表示装置における素子の微細化に対応するようにトランジスタや負荷容量を配置した液晶表示装置および表示システムに関する。

【0002】

【従来の技術】

近年、様々な分野で液晶表示装置が用いられるようになっている。この液晶表示装置の一種として、半導体基板上にマトリクス状に形成されたトランジスタと画素電極とにより構成される液晶駆動部の上に液晶部を一体に形成したものがある。前記トランジスタに画素信号を入力し、その出力で画素電極を駆動することにより、液晶の配向状態を変化させ、外部から液晶に入射する光の反射状態を、液晶の配向状態に応じて変化させることで、画像を形成するものである。

例えば、特許2995725号公報に、画素トランジスタの動作に悪影響を与えることなく、光キャリアによるドレイン電位のシフトを極力抑制するようにした半導体装置を用いた液晶表示装置が開示されている。

【0003】

図5に、従来の液晶表示装置の概念的な断面図を示す。図5に示すように、液晶表示装置を形成するパネルはシリコン基板100上に形成された液晶駆動部102と、その上に設けられた液晶部104とからなる。

シリコン基板100上に設けられた液晶駆動部102は、ソース106a、ドレイン106b及びゲート106cからなるスイッチング用のトランジスタ106と、拡散層108a及び上部電極108bとからなる負荷容量108と、トランジスタ106のドレイン106bに接続されその上方に設けられた画素電極(反射ミラー電極)110と、から構成される。

【0004】

トランジスタ106は、対応する画素電極110上の液晶の配向状態を制御するものである。走査線によって選択され、ゲート106cに電位が印加されたトランジスタ106がオンになると、映像信号に応じた画素信号がソース106aに入力される。この信号がドレイン106bに伝送され、それにつながる画素電極110および負荷容量108の上部電極108bに印加される。負荷容量108は、トランジスタ106がオフの期間中に画素信号を保持し、画素電極110に印加される電位のシフトを抑制し、液晶に画像を安定して表示させるようにするものである。

画素電極110は、10μm×10μm〜30μm×30μm程度の大きさを有し、その上に配置される液晶の配向を変え画像を表示する画素素子を形成するものである。

【0005】

液晶部104は、画素電極110と透明電極114に挟まれた液晶116と、最上層にガラス板118を有して構成されている。

液晶部104に、ガラス板118表面から入射する入射光を画素電極110で反射する際に、前述したように画素毎にマトリクス状に形成されたトランジスタ106に入力する画素信号を変化させることにより、液晶116の配向状態を変えることで、画像が形成される。

【0006】

図6に、本願発明の完成以前に本発明者自身によって設計された従来の液晶表示装置の液晶駆動部の平面図を示す。図6において、トランジスタ120と、拡散層122a及び上部電極122bから構成される負荷容量122とは交互に並んで配置されている。

液晶の駆動用に、10V〜20V程度の高電圧が画素電極に印加されるため、スイッチトランジスタと負荷容量との間の耐圧は、それに耐え得るような仕様が要求される。

【0007】

【発明が解決しようとする課題】

上述したように、従来、トランジスタと、負荷容量は隣り合って配置されているため、トランジスタのソース、ドレインを構成する拡散層と、負荷容量の下部電極となる拡散層との間には10V〜20V程度の高い電位差が生じる。このため、このような拡散層間の素子分離には、1.5μm〜3μm程度の分離幅が必要になる。

このような広い分離幅が必要であるため、画素サイズが小さくなるに従い、負荷容量の面積確保が難しくなる。このため、高精細化の妨げや、光リーク耐性が低下する等の弊害が発生するという問題がある。

【0008】

本発明は、前記従来の問題に鑑みてなされたものであり、画素サイズが小さくなっても、新たにプロセスを追加する事なく、負荷容量の面積を簡易に増やすことのできる液晶表示装置および表示システムを提供することを課題とする。

【0009】

【課題を解決するための手段】

前記課題を解決するために、本発明の第1の態様は、半導体基板上に形成されたトランジスタと、該トランジスタのドレイン出力によって駆動される画素電極と、前記トランジスタのドレイン出力を保持する容量とを含む複数の画像表示素子が、信号線が延在する第1の方向及び該信号線と略直交するゲート電極が延在する第2の方向に2次元的にアレイ状に配置された画像表示部を含む液晶表示装置であって、

前記容量が、前記半導体基板の表面に形成された容量拡散層と、絶縁膜を介して、該容量拡散層と対向する容量電極とからなり、

前記複数の画像表示素子が、前記第2の方向に順番に隣りあう第1、第2および第3の画像表示素子と、該第1および第2の画像表示素子に対して前記第1の方向に隣りあい、互いに前記第2の方向に隣りあう第4および第5の前記画像表示素子とを含み、

前記第1、第2、第4および第5の画像表示素子の容量拡散層が一体化され、

前記一体化された容量拡散層に所要の電位を供給するためのコンタクトが、前記第1、第2、第4および第5の画像表示素子の容量電極に囲まれた部分に設けられることを特徴とする液晶表示装置を提供する。

【0010】

また、前記第1および第2の画像表示素子のそれぞれの容量拡散層が、該第1および第2の画像表示素子間の境界に沿って、該境界の長さの少なくとも実質的に全体にわたって形成されることが好ましい。

【0011】

また、同様に前記課題を解決するために、本発明の第2の態様は、半導体基板上に形成されたトランジスタと、該トランジスタのドレイン出力によって駆動される画素電極と、前記トランジスタのドレイン出力を保持する容量とを含む複数の画像表示素子が、信号線が延在する第1の方向及び該信号線と略直交するゲート電極が延在する第2の方向に2次元的にアレイ状に配置された画像表示部を含む液晶表示装置であって、

前記容量が、前記半導体基板の表面に形成された容量拡散層と、絶縁膜を介して、該容量拡散層と対向する容量電極とからなり、

前記複数の画像表示素子が、前記第2の方向に順番に隣りあう第1、第2および第3の画像表示素子を含み、

前記第1および第2の画像表示素子のそれぞれの前記容量拡散層が、該第1および第2の画像表示素子間の境界に沿って、該境界の長さの少なくとも実質的に全体にわたって形成されると共に、該境界において一体化されることを特徴とする液晶表示装置を提供する。

【0012】

また、同様に前記課題を解決するために、本発明の第3の態様は、半導体基板上に形成されたトランジスタと、該トランジスタのドレイン出力によって駆動される画素電極と、前記トランジスタのドレイン出力を保持する容量とを含む複数の画像表示素子が、信号線が延在する第1の方向及び該信号線と略直交するゲート電極が延在する第2の方向に2次元的にアレイ状に配置された画像表示部を含む液晶表示装置であって、

前記容量が、前記半導体基板の表面に形成された容量拡散層と、絶縁膜を介して、該容量拡散層と対向する容量電極とからなり、

前記複数の画像表示素子が、前記第2の方向に順番に隣りあう第1、第2および第3の画像表示素子を含み、

前記第1および第2の画像表示素子のそれぞれの容量拡散層が、該第1および第2の画像表示素子間の境界に沿って形成されると共に、該境界において一体化され、

前記第2および第3の画像表示素子のトランジスタが、該第2および第3の画像表示素子間の境界線をまたいで前記第2の方向に延びる共有ゲート電極を共有したことを特徴とする液晶表示装置を提供する。

【0013】

また、前記画像表示部が、前記第1、第2および第3の画像表示素子を含んで前記第2の方向に配置された複数の前記画像表示素子を選択する走査線を有し、該走査線が、前記共有ゲート電極と、該共有ゲート電極に接続され、前記第1および第2の画像表示素子の容量電極の上方を前記第2の方向に延びる配線とからなることが好ましい。

【0014】

また、同様に前記課題を解決するために、本発明の第4の態様は、半導体基板上に形成されたトランジスタと、該トランジスタのドレイン出力によって駆動される画素電極と、前記トランジスタのドレイン出力を保持する容量とを含む複数の画像表示素子が、信号線が延在する第1の方向及び該信号線と略直交するゲート電極が延在する第2の方向に2次元的にアレイ状に配置された画像表示部を含む液晶表示装置であって、

前記容量が、前記半導体基板の表面に形成された容量拡散層と、絶縁膜を介して、該容量拡散層と対向する容量電極とからなり、

前記複数の画像表示素子が、前記第2の方向に順番に隣りあう第1、第2および第3の画像表示素子を含み、

前記第1および第2の画像表示素子のそれぞれの容量拡散層が、該第1および第2の画像表示素子間の境界に沿って形成されると共に、該境界において一体化され、

前記画像表示部が、前記第1、第2および第3の画像表示素子を含んで前記第2の方向に配置された複数の前記画像表示素子を選択する走査線を有し、該走査線が、前記第1および第2の画像表示素子の容量電極の上方を前記第2の方向に延びる配線を含むことを特徴とする液晶表示装置を提供する。

【0015】

また、前記第1および第2の画像表示素子のそれぞれの前記容量電極が、前記第1および第2の画像表示素子間の境界に沿って、該境界の長さの実質的に全体にわたって形成されることが好ましい。

【0016】

また、前記複数の画像表示素子に、前記第1の方向に延びる信号線から画素信号が入力されることが好ましい。

【0017】

また、前記第1の画像表示素子の容量拡散層が、該第1の画像表示素子が形成される範囲全体において同一の導電型を有する前記半導体基板の表面に形成されることが好ましい。

【0018】

また、前記第1の画像表示素子の容量拡散層が第1の導電型を有し、該第1の導電型の前記半導体基板の表面に形成されることが好ましい。

【0019】

また、同様に前記課題を解決するために、本発明の第5の態様は、前記請求項1乃至10のいずれかに記載の液晶表示装置と、該液晶表示装置に光を入射する光源とを有することを特徴とする表示システムを提供する。

【0020】

【発明の実施の形態】

以下、本発明に係る液晶表示装置および表示システムについて、添付の図面に示される好適実施形態を基に、詳細に説明する。

【0021】

本実施形態は、第1の方向及び第2の方向に2次元的にアレイ状に配置された画像表示素子のうち、信号線が延在する第1の方向とは異なる第2の方向に隣り合った画像表示素子の容量の下部電極を構成する拡散層(容量拡散層)を、該隣り合った容量同士で共有するようにしたものである。

そして、本実施形態の液晶表示装置は、信号線の方向である第1の方向とは異なる第2の方向に、容量と容量とが、またトランジスタとトランジスタとがそれぞれ隣り合うようにして、第2の方向に隣り合う画像表示素子(の液晶駆動部)が線対称となるように背面配置に配列したものである。

【0022】

図1は、本発明の実施形態に係る液晶表示装置の(特に液晶駆動部の)概略を示す平面図である。

図1では、複雑になるのを避けるため、上部の液晶部を省略している。さらに、液晶駆動部の中でも、反射電極および後から説明する遮光層を省略し、半導体基板表面およびその近傍に形成されるトランジスタおよび負荷容量、ならびに、その間を接続する配線の配置のみを示す。

図1に示すように、本実施形態の液晶表示装置においては、それぞれの画像表示素子の液晶駆動部が、トランジスタ11とトランジスタ10とが第2の方向(図の左右方向)に隣り合い、また負荷容量24と負荷容量28とが、その下部電極を構成する拡散層20を共有して、第2の方向に隣り合うように配置されている。また、このとき、トランジスタ10と負荷容量24、及び負荷容量28とトランジスタ13は、2つの負荷容量24と28の中間線Sに関して線対称(図の場合、左右対称)となるように背面配置されている。

ここで、破線21aで囲まれた部分のトランジスタ13および負荷容量28を含む画像表示素子を第1の画素表示素子、破線21bで囲まれた部分のトランジスタ10および負荷容量24を含む画像表示素子を第2の画像表示素子、破線21cで示された部分のトランジスタ11と図示されない負荷容量とを含む画像表示素子を第3の画像表示素子とする。これらの第1、第2および第3の画像表示素子は第2の方向に順番に隣りあって配置されている。

【0023】

図1において、第2の画像表示素子のトランジスタ(スイッチトランジスタ)10は、半導体基板30表面に形成された拡散層であるソース10a、ドレイン10bと、その間に挟まれたチャネル部分の半導体基板表面にゲート絶縁膜を介して形成されたポリサイド(多結晶シリコン膜上に金属シリサイド膜が積層された複合膜)からなるゲート10cから構成される。

第2の画像表示素子のトランジスタ10と第3の画像表示素子のトランジスタ11とは、第2および第3の画像表示素子間の境界の両側に、互いに隣接して対称に配置されている。すなわち、トランジスタ10および11それぞれを構成するソース、ドレインおよびチャネルを形成するアクティブ領域がそれぞれの画像表示素子の範囲内の半導体基板表面に形成され、その間を分離するために必要な幅の分離領域15が、画像表示素子間の境界上に形成されている。そして、トランジスタ10および11のゲートは、第2および第3の画像表示素子間の境界をまたいで第2の方向に延びる共通のポリサイドのゲート電極17で形成される。すなわち、トランジスタ10および11が、第2の方向に延びるゲート電極(共有ゲート電極)17を共有する。

一方、第2の画像表示素子のトランジスタのソース10aは、コンタクト12aを通じて、第1の方向(図1では、上下方向)に延在する信号線14に接続されている。ドレイン10bは、コンタクト12bを通じて配線層16に接続され、ここから後述するように上部の画素電極(反射ミラー)に接続されている。また負荷容量24、28を挟んで第2の方向に隣り合うトランジスタのゲート13cは、コンタクト12cを通じて配線19で互いに接続され、前記信号線14と略直交する第2の方向に延びる走査線18を形成している。配線19は、ゲート電極17および負荷容量の上部電極22、26よりも上層に形成され、上部電極22、26の上方を第2の方向に延びている。

【0024】

負荷容量24及び28は、それぞれの下部電極である拡散層を共通の拡散層20として共有している。すなわち、それらを同電位に設定することにより、その間に分離領域を設けることなく、互いに接続できる。負荷容量24は、この拡散層(アクティブ領域)20と上部電極(容量電極)22で構成され、負荷容量28は、拡散層(アクティブ領域)20と上部電極26によって構成される。

具体的には、第1の画像表示素子の負荷容量28を形成する拡散層と第2の画像表示素子の負荷容量24を形成する拡散層とが、それぞれ、第1および第2の画像表示素子間の境界(中間線Sの、第1および第2の拡散層の間にはさまれた部分)に沿って形成されると共に、この境界において、分離領域を設けることなく一体化され、第1および第2の画像表示素子に共有される拡散層(共有拡散層)20が形成されている。

【0025】

また、図1のII−II線に沿った断面図を図2に示す。なお、図1では、図が複雑になるのを避けるため、上部の液晶部は省略されていたが、図2では、液晶部も含めて示す事とする。

図2において、半導体基板30上に、トランジスタ10、11及び負荷容量24、28がそれぞれ隣り合って形成されている。トランジスタ10、11のアクティブ領域(図示した断面ではドレイン拡散層が示されている)相互間、およびこれらのトランジスタのアクティブ領域と負荷容量の拡散層との間は、分離領域15によって分離されている。一方、負荷容量24、28のそれぞれを構成する拡散層は、一体化された拡散層20として形成され、その間に分離領域は形成されない。すなわち、負荷容量24、28は、半導体基板30の表面に形成された拡散層20を、それぞれの下部電極として共有し、その上に、それぞれ上部電極22、26を有して構成される。負荷容量24、28を構成する拡散層20と上部電極22、26との間は、図示されない容量絶縁膜によって絶縁されている。図示した断面では見えていないが、トランジスタ10、11のゲート10cも、負荷容量24、28の上部電極22、26と同じ層のポリサイドで形成されている。ゲート絶縁膜も、容量絶縁膜と同時に形成することができる。

【0026】

トランジスタ10のドレイン10bはコンタクト12b及び配線層16を介して、負荷容量24の上部電極22と接続されている。一方、負荷容量24の下部電極である拡散層20には、図示されないコンタクトを介して所定の電位、例えば接地電位が供給される。これにより、ドレイン10bの出力が、トランジスタ10がオフの期間中、負荷容量24によって保持される。

例えば、p- 型半導体基板の表面にp型の拡散層20が形成される場合には接地電位(GND)が、n型の拡散層20が形成される場合には電源電位(Vdd)が供給される。また、トランジスタ10のドレイン10bは、前記配線層16から、ビア32、金属からなる遮光層36及びビア34を介して、画素電極(反射ミラー)38に接続されている。画素電極38の上には、画素電極38と液晶対向電極(透明電極)42によって挟まれた液晶40が配置されている。

なお、遮光層36は、液晶側からの入射光が下部のトランジスタ10等に達して、半導体素子に悪影響を及ぼさないようにするためのものである。このため、遮光層36は、画素電極38相互間のギャップに対応するように、画像表示素子がアレイ状に配置される領域(画像表示部)全体にわたって格子状に配置される。

【0027】

このように、本実施形態では、容量の下部電極である拡散層を、第2の方向に隣り合った容量24及び28で共有したため、隣り合った2つの容量24及び28の素子分離領域を設ける必要が無い。

一方、この共有された拡散層のそれぞれの画像表示素子が形成される範囲内の部分と対向して形成され、それぞれの画像表示素子の容量を構成する上部電極は、互いに電気的に分離される必要があり、一体化することはできない。しかし、拡散層同士の素子分離に比べて、上部電極22、26を形成するポリサイド間同士の素子分離は容易であり、加工精度の最小寸法まで縮小することができる。従って、従来負荷容量24、28間の分離幅は1.5μm〜3μm必要であったが、本実施形態においては、容量24と容量28の分離幅(図1に符号dで示す)は、0.5μm〜0.6μm程度まで縮小することが可能となった。容量をなるべく大きくするためには、第2の方向に隣りあう2つの画像表示素子の容量のそれぞれの上部電極は、分離に必要な相互間の間隔dを保ちながら、その隣りあう画像表示素子間の境界(中間線Sの、第1および第2の拡散層の間にはさまれた部分)に沿って配置することが好ましい。

【0028】

その結果、この分離幅の減少した分を容量の面積を増加する分に使用する事により、容量値を増加させることができる。具体的には、例えば、10μm×10μmの画素サイズにおいて、従来の方法で設計した場合には、拡散層と上部電極との間の容量の面積は、30μm2 しか得られなかった。これに対し本発明の方法によれば、37.8μm2 の面積を確保することが可能となった。

図1に示された本実施形態では、第2および第3の画像表示素子のトランジスタ10および11がゲート電極17を共有している。そして、このような共有ゲート電極間を、負荷容量24、26の上部電極の上方を延びる配線で接続することによって走査線18を形成している。このような走査線の構成もまた、負荷容量の面積を増大させるために役立っている。

すなわち、まず隣りあうトランジスタが共有ゲート電極17を共有している。このため、図6に示した従来の配置では必要であった、これらのトランジスタのゲート電極間を接続するためのコンタクトを、本実施形態の場合には設ける必要がない。このため、トランジスタを配置するために必要な面積が削減できる。

また、共有ゲート電極間の接続が、負荷容量の上部電極の上方を延びる、上部電極とは異なる層の配線19によってなされている。このため、上部電極の第1の方向(図の縦方向)の寸法を最大化することができる。図1に示されたように、上部電極22、26は、第2および第3の画像表示素子間の境界に沿って、境界の長さの実質的に全体にわたって形成されている。すなわち、上部電極22、26の第1の方向の寸法は、画像表示素子の第1の方向の寸法と実施的に同一である。

また、トランジスタ10と11それぞれのゲート電極間を互いに接続するためのコンタクトを設ける必要がなくなったため、信号線14のパターンを単純化できる。従来、トランジスタのソースに接続される信号線(図6の114)は、ゲート電極へのコンタクトを避けるように引き回していた。これに対して本発明では無駄な引き回しをせずに直線的に配置することが可能となった。これにより、信号線の容量および抵抗の低減が可能となった。走査線も、ポリサイドで形成されるゲート電極の部分を第2の方向に隣りあう2つの画像表示素子で共有させ、しかも、短くかつ単純な形状で形成することができる。従って、第2の方向に配置される複数の画像表示素子全体の、ゲート電極17の部分の長さの合計を小さくできる。しかも、それ以外の部分をゲート電極17よりも上層の、やはり直線的に第2の方向に延びる金属配線19で構成できるため、走査線の容量および抵抗の低減も可能となった。

図1および図2には、画素電極および遮光層を含めて3層の金属配線で表示素子を構成した例を示した。このため、走査線18の金属配線で形成する部分19と信号線14とを、同一の配線層に形成する必要があった。従って、信号線14と走査線18とが交差する部分は、ポリサイドのゲート電極17で形成した。すなわち、走査線18は、それぞれ複数のポリサイドのゲート電極17と金属の配線19とが、コンタクトを通じて交互に直列に接続されることによって構成される。

しかし、4層もしくはそれ以上の金属配線の使用を許すのであれば、信号線14とは別の配線層で配線19を形成することが可能である。この場合には、金属の配線19を、複数の画像表示素子が配置された領域の全体にわたって第2の方向に延ばし、それぞれ隣りあう2つのトランジスタに共有されたポリサイドのゲート電極を、この走査線にコンタクトもしくはコンタクトおよびビアを介して接続することによって、走査線を構成することも可能である。これによって、走査線の抵抗をさらに低減することが可能である。

【0029】

このような液晶表示装置の液晶駆動部は、例えば、概略以下のような工程で形成される。まず、例えばp- 型の半導体基板表面の必要な領域にPウエルおよびNウエル(図示しない)を形成するとともに、トランジスタや容量のアクティブ領域間を電気的に分離するための分離領域15を形成する。次に、容量を構成する拡散層20を、例えばホウ素イオンの注入によって形成する。

続いて、ゲート絶縁膜および容量絶縁膜を兼ねる絶縁膜が、例えば熱酸化によって形成され、多結晶シリコン膜および金属シリサイド膜が堆積され、所要のパターンにパターンニングされることによって、トランジスタのゲート電極と容量の上部電極が形成される。次に、例えばヒ素のイオン注入によって、ゲート電極の両側のアクティブ領域表面にソース、ドレイン拡散層が形成される。その後、全面に絶縁膜が堆積され、平坦化されて第1層間絶縁膜が形成される。そして、第1層間絶縁膜の必要な部分にコンタクト孔が開口され、金属プラグが埋め込まれることによってコンタクト12a、12b、12cが形成された後、アルミニウム合金膜等の金属膜が堆積され、パターニングされて、第1の配線層16が形成される。さらに同様に、第2層間絶縁膜が形成され、ビア32が形成され、第2配線層(遮光層36)が形成される。そしてさらに、第3層間絶縁膜およびビア34、第3配線層(反射電極)38が形成される。

なお、それぞれの画像表示素子の駆動回路をNチャンネルトランジスタとPチャンネルトランジスタとの両方で構成する場合には、容量の下部電極を構成する拡散層20を形成する以前に、それぞれの画像表示素子を形成する領域内の半導体基板表面の所定の位置に、PウエルおよびNウエルを形成しておく必要がある。しかし、一方の導電型のトランジスタのみで駆動回路を構成する場合には、それぞれの画像表示素子を形成する領域内にウエルを形成しておく必要はない。例えば、駆動回路をN型トランジスタのみで形成するのであれば、P- 型半導体基板表面の、第1および第2の方向に配置される複数の画像表示素子を形成する領域全体に共通のPウエルを形成しておけばよい。この場合、容量を構成する拡散層20は、それぞれの画像表示素子が形成される領域全体において同一の導電型を有する、すなわち、Pウエルが形成された、半導体基板の表面に形成されることになる。

【0030】

なお、液晶表示装置1の半導体基板30表面上には、画像表示素子がアレイ状に配置された画像表示部に加えて、その周辺に、外部から画像信号を受け取り、画像表示部に供給するための画素信号や走査信号を生成する信号処理部が設けられている。前述のように、画像表示部の画像表示素子は、高電圧に耐える必要があるため、高電圧仕様の製造工程で形成される。一方、信号処理部には高電圧は印加されない。このため、信号処理部は、上記で説明した画像表示部の形成工程とは別に、通常のCMOS半導体製造工程によって形成される。

【0031】

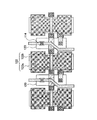

本実施形態では、トランジスタと画素電極および負荷容量を含む画素が、図1に示したように走査線18の方向(図の横方向)に配列されるとともに、信号線14の方向(図の縦方向)にも配列される。すなわち、図3に示すように、画素が第1および第2の方向に2次元的なアレイ状に配置されて、本発明の液晶表示装置の表示部を構成する。

図3において、例えば破線72bで囲まれた部分のトランジスタ50および負荷容量64によって一つの画素分の表示素子の液晶駆動部が形成されている。なお図3では、トランジスタ52のドレインに接続される容量の上部電極、およびその間を接続する配線は省略されている。ここで、それぞれ破線72a、72b、72c、72d、72e、72fで示された画像表示素子を第1、第2、第3、第4、第5、第6の画像表示素子とする。すると、第1、第2、第3の画像表示素子、および第4、第5、第6の画像表示素子は、それぞれが順番に第2の方向(図の左右方向)に互いに隣り合って配置されている。そして、第4、第5、第6の画像表示素子はそれぞれ第1、第2、第3の画像表示素子に対して第1の方向(図の縦方向)に隣り合って配置されている。

【0032】

図3に示すように、本実施形態における液晶表示装置は、図において、縦方向に延びる信号線58の方向である第1の方向、及び横方向に延びる走査線60の方向である第2の方向、の両方の方向に隣り合う画像表示素子について横方向にも縦方向にも負荷容量64、66、68、70が隣合うように配置されている。そして、その容量(負荷容量)64、66、68、70の下部電極を構成する拡散層を共有して、1つの拡散層62としている。

すなわち、例えば図の横方向に隣り合う第1および第2の画像表示素子の負荷容量64、66を構成する拡散層は、それぞれ、この第1および第2の画像表示素子間の境界(図の縦方向の境界)に沿って形成され、この境界において一体化されている。同様に、第4および第5の画像表示素子の負荷容量68、70を構成する拡散層は、それぞれ、第4および第5の画像表示素子間の境界に沿って形成され、この境界において一体化されている。そして、第1および第2の画像表示素子72a、72bの負荷容量64、66を構成する拡散層と、第4および第5の画像表示素子72e、72fの負荷容量68、70を構成する拡散層とは、第1および第2の画像表示装置72a、72bと第4および第5の画像表示装置72e、72fとの間の境界(図の横方向の境界)において一体化されている。従って、第1、第2、第4、第5の4つの画像表示素子の負荷容量64、66、68、70を構成する拡散層は、これらの4つの画像表示素子間の縦方向および横方向の境界において一体化された拡散層(共有拡散層)62として形成されている。この拡散層62は、これらの4つの画像表示素子にわたって形成され、これらの画像表示素子の負荷容量に共有されている。

【0033】

図3に示された液晶表示装置では、画像表示素子の負荷容量を構成する拡散層を第1の方向(図の縦方向)に隣りあう画像表示素子で共有するため、それぞれの画像表示素子の拡散層は、それぞれの画像表示素子の第1の方向の寸法全体にわたって形成される。一方、この拡散層と対向して負荷容量を構成する多結晶シリコンからなる上部電極は、第1の方向に隣りあう画像表示素子の上部電極との間で電気的に分離する必要があるため、画像表示素子の第1の方向の寸法の全体わたって形成することはできない。しかし、それぞれの画像表示素子の負荷容量の上部電極は、分離のために必要な寸法を除いた、それぞれの画像表示素子の第1の方向の寸法の実質的に全体わたって形成される。前述のように、多結晶シリコン同士の分離に必要な分離幅は小さいため、それぞれの画像表示素子の負荷容量の上部電極間を分離しても、大きな容量値を得ることが可能である。

【0034】

また、このとき、トランジスタ50、52、54、56も、前記2つの方向に隣り合うように配置され、各ソース(例えばトランジスタ50についてはソース50a)は信号線58に接続され、各ドレインは各負荷容量の上部電極(例えばトランジスタ50のドレイン50bについては、負荷容量64の上部電極)に接続される。またトランジスタの各ゲート(例えばトランジスタ50のゲート電極50c)を構成するゲート電極59は配線61で互いに接続されて走査線60を形成する。

実際には、図3に示した範囲のみではなく、さらに第1の方向(図の上下)および第2の方向(図の左右)に複数の画像表示素子がアレイ状に配置され、画像表示装置の表示部が形成される。この結果、表示部には、複数の表示素子の負荷容量に共有されて第1の方向に延びる拡散層(共通拡散層)62が、複数、第2の方向に配置されることになる。それぞれの共有拡散層は、第1の方向に配置される複数の画像表示素子全体におよんで、すなわち、画像表示素子のアレイの全体にわたって延びる。

【0035】

図3にはこのような共有拡散層62が1つだけ表示されている。しかし、例えば、図では省略されているが、第3および第6の表示素子72cおよび72fの負荷容量の拡散層と、さらにその左側に配置される表示素子の負荷容量の拡散層とが共有され、さらに、それらの上下方向に配置される複数の画像表示素子の負荷容量の拡散層が共有されることによって、縦方向に延びる第2の共有拡散層が形成される。この共有拡散層は、図3に表示された共有拡散層62の左側に隣りあって配置される。また、第1および第4の表示素子の72a、72dの右側に配置される表示素子の負荷容量の拡散層と、さらにその右側に配置される表示素子の負荷容量の拡散層とが共有され、縦方向に延びる第3の共有拡散層が形成される。これらの共有拡散層は、第2の方向(図の横方向)に、画像表示素子が第2の方向(図の横方向)に配置される周期の2倍の周期で配置される。

そして、これらの第1の方向に延びる複数の共有拡散層の中の、隣りあう2つの共有拡散層の間には、それぞれ、第2の方向に隣りあう2つの表示素子のトランジスタが配置される。例えば、図3に示された共有拡散層62と、その左側に隣りあって配置される第2の共有拡散層との間には、それぞれ第2の方向に隣りあう、第2および第3の表示素子のトランジスタ50、52と、第5および第6の表示素子のトランジスタ54、56が、配置される。

【0036】

図3に示した例では、第1の方向(図の縦方向)に配置された複数の表示素子の負荷容量の下部電極となる拡散層が共有されている。このように、第1および第2の二つの方向において、それぞれ隣り合う画像表示素子の容量を構成する拡散層間に分離領域を設けることなく、共有することにより、画素サイズが小さくなっても負荷容量の面積を確保することを可能としている。この場合、アレイ(画像表示部)の端部に図示しないコンタクトが形成され、所要の電位が供給される。

【0037】

図4は、本発明の他の実施形態に係わる液晶表示装置の概略を示す平面図である。本実施形態では、図3に示した実施形態と同様に、第1および第2の方向の2つの方向の境界において、それぞれ隣りあう画像表示素子の容量を構成する拡散層が一体化され、第1の方向(縦方向)に延びる共有拡散層62が形成されている。しかし、図3の場合と異なり、4つの画像表示素子に囲まれた部分に、より具体的には、4つの画像表示素子の上部電極に囲まれた部分に、この共有拡散層62に所要の電位を供給するコンタクト76が設けられている。それぞれのコンタクト76は、それを取り囲む4つの画像表示素子によって共有され、それら4つの画像表示素子の容量を構成する拡散層に所要の電位を供給する。図4の場合には、第1の方向(図の縦方向)に延びる共有拡散層62全体では、2個の画像表示素子に対して1個の割合でコンタクト76が設けられている。

【0038】

図では省略されているが、コンタクトの底面の半導体基板30表面には、コンタクト形成のための高濃度拡散層が形成される。また、このコンタクトに対して所要の電位を供給する配線が配置される。例えば、配線61と同一層に設けられた配線77およびビアを介して、遮光層に接続し、遮光層を通じて、例えば接地電位を供給することが可能である。

図4では、コンタクト76との接触を防ぐため、容量64、66、68、70それぞれの上部電極の角が切り取られている。このため、アレイの端部にコンタクトを設けた場合に比較して、容量の面積は減少する。しかし、アレイ内にコンタクトを設けることによって、多数配置された画像表示素子のそれぞれの容量の拡散層への所要の電位供給を均一に行い、動作の安定性を高めることが可能である。また、コンタクトを4つの画像表示素子に囲まれた部分に、それらの画像表示素子に対して共通に設けることによって、容量の減少を最小限にとどめることが可能である。

すなわち、この場合であっても、上部電極を、第2の方向に隣りあう画像表示素子間の縦方向の境界に沿って、その境界の長さの実質的に全体にわたって形成することが可能である。

動作上の問題がなければ、コンタクトの数をさらに減らすことも可能である。例えば、2個の画像表示素子毎に1個のコンタクトを設けるのではなく、4個、6個、8個もしくはそれ以上の偶数個の画像表示素子毎に1つのコンタクトを設けることも可能である。この場合にも、コンタクトは、第1および第2の方向に隣りあう画像表示素子の上部電極に囲まれた部分に設けることが、容量の減少を最小限にとどめるために好ましい。

【0039】

第2の方向(図の横方向)には、隣り合う表示素子間で負荷容量の下部電極を形成するアクティブ領域を共有する一方で、第1の方向(図の縦方向)には、負荷容量の下部電極を形成する拡散層を表示画素毎に分離することも可能である。この場合には、それぞれの拡散層毎に所要の電位を供給するためのコンタクトが形成される。

この場合、それぞれの画像表示素子の容量を構成する拡散層を第1の方向(図の縦方向)に隣りあう画像表示素子の拡散層と分離する分離領域を設ける必要がある。このため、拡散層を、第2の方向に隣りあう画像表示素子間の境界全体にわたって、すなわち、画像表示素子の第1の方向の寸法全体にわたって形成することはできない。しかし、なるべく大きな容量値を得るために、分離のために必要な寸法を除いた、境界の画像表示素子の第1の方向の寸法の実質的な全体にわたって、拡散層を形成することが好ましい。

もしくは、第1の方向(図の縦方向)に隣りあう少なくとも2つずつの画像表示素子の容量を構成する拡散層を一体化し、第1および第2の方向で4つもしくはそれ以上の画像表示素子の容量を構成する拡散層に対して、少なくとも1個の共通のコンタクトを設けることが、コンタクト形成による容量減少を最小にするためには好ましい。このように、第2の方向に隣りあう2つの画像表示素子間の境界において拡散層を一体化するとともに、1の方向に隣りあう画像表示素子の拡散層間や上部電極間を相互に分離するための寸法や、複数の拡散層に対して電位を供給する共通のコンタクトを形成するための寸法等、容量の形成およびその使用に必要な必要最小限の寸法を除いて、この境界に沿った領域の実質的な全体を、拡散層や上部電極を配置するために利用して、可能な限り容量を増大させることが好ましい。より具体的には、第2の方向に隣りあう2つの画像表示素子間の、拡散層が一体化される境界に沿った領域には、容量を構成するための拡散層および上部電極と、一体化した拡散層に対して電位を供給する共通のコンタクトおよびそれに付随する構造(コンタクト形成のための高濃度拡散層等)のみを配置することが好ましい。それ以外の、容量の形成およびその使用に対して寄与しない、そして、拡散層もしくは上部電極と同一の層に形成されて、大きな容量の減少を引き起こす構造は、拡散層が一体化される境界に沿った領域には配置しないことが好ましい。ただしもちろん、上部電極の上方を第2の方向に延びる配線19、61のように、拡散層および上部電極とは異なる層には他の構造を配置することが可能である。

4つの画像表示素子の容量を構成する拡散層を一体化した場合、画像表示部に配置される共有拡散層は、それぞれ、第1の方向に隣りあう2個の画像表示素子にわたって延びる。すなわち、第1の方向に、概略、画像表示素子2個分の寸法を有する。6つ、8つ、もしくはそれ以上の偶数個ずつの画像表示素子の容量を構成する拡散層を一体化した場合、それぞれの共有拡散層は、第1の方向に隣りあう3個、4個、もしくはそれ以上の個数の画像表示素子にわたって延び、概略、画像表示素子3個分、4個分、もしくはそれ以上の寸法を有する。

また、以上説明したような液晶表示装置に対し、光を入射する光源を組み合わせることで、表示システムを構成することができる。

【0040】

以上、本発明の液晶表示装置および表示システムについて詳細に説明したが、本発明は、以上の例には限定されず、本発明の要旨を逸脱しない範囲において、各種の改良や変更を行ってもよいのはもちろんである。

例えば、図3に示した配置においては、第2の方向(図の横方向)に隣りあう画像表示素子が線対称になるように背面配置する一方で、第1の方向(図の縦方向)には背面配置を行っていない。しかし、第1および第2の方向の両方に画像表示素子を背面配置することも可能である。

図1、3等に破線で示したそれぞれの画像表示素子の範囲は、半導体基板30の表面上に、それぞれの画像表示素子のトランジスタおよび負荷容量が形成される範囲を示している。これらの構造のさらに上方に配置される画素電極も、通常は、同一の範囲内に設けられる。しかし、配置の都合によっては、トランジスタおよび負荷容量が形成される範囲に対して一定の位置関係でずれた位置に画素電極を配置することも可能である。この場合、第2の方向に隣りあう画像表示素子の容量を構成する拡散層は、トランジスタおよび容量を形成するためにこの隣りあう画像表示素子のそれぞれに与えられる半導体基板表面上の範囲間の境界に沿って形成され、この境界において一体化される。また、第1の方向にも容量の拡散層が一体化される場合には、第1の方向に隣りあう画像表示素子の容量を構成する拡散層は、トランジスタおよび容量を形成するためにこの隣りあう画像表示素子のそれぞれに与えられる半導体基板表面上の範囲間の境界に沿って形成され、この境界において一体化される。さらに、第2の方向に隣りあう画像表示素子のトランジスタは、トランジスタおよび容量を形成するためにこの隣りあう画像表示素子のそれぞれに与えられる半導体基板表面上の範囲間の境界をまたいで、第2の方向に延びるゲート電極を共有する。

【0041】

図1、3に示した例では、それぞれの画像表示素子は、半導体基板30表面上の正方形の範囲内に形成される。しかし、配置の都合によっては、完全な正方形以外の形状の範囲内にそれぞれの画像表示素子を形成することも可能である。言うまでもなく、図1、3に破線で示したそれぞれの画像表示素子の範囲は、理解を容易にするために概念的に記したにすぎず、実際の画像表示装置上の物理的な構造として存在するわけではない。しかし、実際の画像表示装置におけるそれぞれの画像表示素子の範囲、もしくは、それらの間の境界の位置は、実際の画像表示装置に形成されたトランジスタや容量等の配置に基づいて容易に把握することが可能である。

上記の例では、各表示素子毎に1個のNチャンネルトランジスタを設け、そのドレイン出力で画素電極を駆動している。これ以外にも様々な駆動回路を構成することが可能である。例えば、それぞれ1個のNチャンネルトランジスタとPチャンネルトランジスタとを並列に接続して、その出力で画素電極を駆動することも可能である。

【0042】

しかし、この場合には、それぞれの画像表示素子領域内に複数のトランジスタを形成するための面積が必要になるばかりではなく、NチャンネルトランジスタとPチャンネルトランジスタとのそれぞれをその中に形成するためにウエルを形成するための面積も必要になる。また、ウエルを形成するための工程を追加する必要があり、製造コストも上昇する。このような構造の形成に必要な面積を削減し、十分な容量の負荷容量を形成するための面積を確保するとともに、製造コストを低減するためには、一方の導電型のトランジスタ(通常はNチャンネルトランジスタ)のみを使用して駆動回路を構成することが好ましい。

また、例えば、特許2804198号公報に記されたように、各表示素子毎に2個のトランジスタを設け、第1のトランジスタのドレインに、ドレイン出力を保持する負荷容量を接続するとともに、第2のトランジスタのゲートを接続して、この第2のトランジスタを介して画素電極を駆動することも可能である。

【0043】

【発明の効果】

以上説明した通り、本発明によれば、画素サイズを小さくしても、負荷容量の面積を従来よりも大きく確保することが可能となる。また、隣り合うトランジスタのゲート電極を共通にできるため、信号線および走査線を直線的に配置して、容量を低減することが可能となる。

【図面の簡単な説明】

【図1】 本発明の実施形態に係る液晶表示装置の概略を示す平面図である。

【図2】 図1のII−II線に沿った断面図である。

【図3】 本発明の実施形態に係る液晶表示装置の概略を示す平面図である。

【図4】 本発明の他の実施形態に係る液晶表示装置の概略を示す平面図である。

【図5】 従来の液晶表示装置の概略構成を示す断面図である。

【図6】 従来の液晶表示装置の液晶駆動部の概略を示す平面図である。

【符号の説明】

10、11、13、50、52、54、56 トランジスタ

10a、50a ソース

10b、50b ドレイン

10c、13c、50c ゲート

12a、12b、12c、76 コンタクト

14、58 信号線

15 分離領域

16 配線層

17、59 ゲート電極

18、60 走査線

19、61、77 配線

20、62 拡散層

21a、21b、21c、72a、

72b、72c、72d、72e、72f 画像表示素子

22、26 負荷容量上部電極

24、28、64、66、68、70 負荷容量

30 半導体基板

32、34 ビア

36 遮光層

38 画素電極(反射ミラー)

40 液晶

42 液晶対向電極(透明電極)

Claims (11)

- 半導体基板上に形成されたトランジスタと、該トランジスタのドレイン出力によって駆動される画素電極と、前記トランジスタのドレイン出力を保持する容量とを含む複数の画像表示素子が、信号線が延在する第1の方向及び該信号線と略直交するゲート電極が延在する第2の方向に2次元的にアレイ状に配置された画像表示部を含む液晶表示装置であって、

前記容量が、前記半導体基板の表面に形成された容量拡散層と、絶縁膜を介して、該容量拡散層と対向する容量電極とからなり、

前記複数の画像表示素子が、前記第2の方向に順番に隣りあう第1、第2および第3の画像表示素子と、該第1および第2の画像表示素子に対して前記第1の方向に隣りあい、互いに前記第2の方向に隣りあう第4および第5の前記画像表示素子とを含み、

前記第1、第2、第4および第5の画像表示素子の容量拡散層が一体化され、

前記一体化された容量拡散層に所要の電位を供給するためのコンタクトが、前記第1、第2、第4および第5の画像表示素子の容量電極に囲まれた部分に設けられることを特徴とする液晶表示装置。 - 前記第1および第2の画像表示素子のそれぞれの容量拡散層が、該第1および第2の画像表示素子間の境界に沿って、該境界の長さの少なくとも実質的に全体にわたって形成されることを特徴とする請求項1に記載の液晶表示装置。

- 半導体基板上に形成されたトランジスタと、該トランジスタのドレイン出力によって駆動される画素電極と、前記トランジスタのドレイン出力を保持する容量とを含む複数の画像表示素子が、信号線が延在する第1の方向及び該信号線と略直交するゲート電極が延在する第2の方向に2次元的にアレイ状に配置された画像表示部を含む液晶表示装置であって、

前記容量が、前記半導体基板の表面に形成された容量拡散層と、絶縁膜を介して、該容量拡散層と対向する容量電極とからなり、

前記複数の画像表示素子が、前記第2の方向に順番に隣りあう第1、第2および第3の画像表示素子を含み、

前記第1および第2の画像表示素子のそれぞれの前記容量拡散層が、該第1および第2の画像表示素子間の境界に沿って、該境界の長さの少なくとも実質的に全体にわたって形成されると共に、該境界において一体化されることを特徴とする液晶表示装置。 - 半導体基板上に形成されたトランジスタと、該トランジスタのドレイン出力によって駆動される画素電極と、前記トランジスタのドレイン出力を保持する容量とを含む複数の画像表示素子が、信号線が延在する第1の方向及び該信号線と略直交するゲート電極が延在する第2の方向に2次元的にアレイ状に配置された画像表示部を含む液晶表示装置であって、

前記容量が、前記半導体基板の表面に形成された容量拡散層と、絶縁膜を介して、該容量拡散層と対向する容量電極とからなり、

前記複数の画像表示素子が、前記第2の方向に順番に隣りあう第1、第2および第3の画像表示素子を含み、

前記第1および第2の画像表示素子のそれぞれの容量拡散層が、該第1および第2の画像表示素子間の境界に沿って形成されると共に、該境界において一体化され、

前記第2および第3の画像表示素子のトランジスタが、該第2および第3の画像表示素子間の境界線をまたいで前記第2の方向に延びる共有ゲート電極を共有したことを特徴とする液晶表示装置。 - 前記画像表示部が、前記第1、第2および第3の画像表示素子を含んで前記第2の方向に配置された複数の前記画像表示素子を選択する走査線を有し、該走査線が、前記共有ゲート電極と、該共有ゲート電極に接続され、前記第1および第2の画像表示素子の容量電極の上方を前記第2の方向に延びる配線とからなることを特徴とする請求項4に記載の液晶表示装置。

- 半導体基板上に形成されたトランジスタと、該トランジスタのドレイン出力によって駆動される画素電極と、前記トランジスタのドレイン出力を保持する容量とを含む複数の画像表示素子が、信号線が延在する第1の方向及び該信号線と略直交するゲート電極が延在する第2の方向に2次元的にアレイ状に配置された画像表示部を含む液晶表示装置であって、

前記容量が、前記半導体基板の表面に形成された容量拡散層と、絶縁膜を介して、該容量拡散層と対向する容量電極とからなり、

前記複数の画像表示素子が、前記第2の方向に順番に隣りあう第1、第2および第3の画像表示素子を含み、

前記第1および第2の画像表示素子のそれぞれの容量拡散層が、該第1および第2の画像表示素子間の境界に沿って形成されると共に、該境界において一体化され、

前記画像表示部が、前記第1、第2および第3の画像表示素子を含んで前記第2の方向に配置された複数の前記画像表示素子を選択する走査線を有し、該走査線が、前記第1および第2の画像表示素子の容量電極の上方を前記第2の方向に延びる配線を含むことを特徴とする液晶表示装置。 - 前記第1および第2の画像表示素子のそれぞれの前記容量電極が、前記第1および第2の画像表示素子間の境界に沿って、該境界の長さの実質的に全体にわたって形成されることを特徴とする請求項1乃至6のいずれかに記載の液晶表示装置。

- 前記複数の画像表示素子に、前記第1の方向に延びる信号線から画素信号が入力されることを特徴とする請求項1乃至7のいずれかに記載の液晶表示装置。

- 前記第1の画像表示素子の容量拡散層が、該第1の画像表示素子が形成される範囲全体において同一の導電型を有する前記半導体基板の表面に形成されることを特徴とする請求項1乃至8のいずれかに記載の液晶表示装置。

- 前記第1の画像表示素子の容量拡散層が第1の導電型を有し、該第1の導電型の前記半導体基板の表面に形成されることを特徴とする請求項1乃至9のいずれかに記載の液晶表示装置。

- 前記請求項1乃至10のいずれかに記載の液晶表示装置と、該液晶表示装置に光を入射する光源とを有することを特徴とする表示システム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001390158A JP3998470B2 (ja) | 2000-12-25 | 2001-12-21 | 液晶表示装置および表示システム |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000392796 | 2000-12-25 | ||

| JP2000-392796 | 2000-12-25 | ||

| JP2001390158A JP3998470B2 (ja) | 2000-12-25 | 2001-12-21 | 液晶表示装置および表示システム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002277900A JP2002277900A (ja) | 2002-09-25 |

| JP2002277900A5 JP2002277900A5 (ja) | 2005-07-28 |

| JP3998470B2 true JP3998470B2 (ja) | 2007-10-24 |

Family

ID=26606526

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001390158A Expired - Fee Related JP3998470B2 (ja) | 2000-12-25 | 2001-12-21 | 液晶表示装置および表示システム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3998470B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4590839B2 (ja) * | 2003-08-01 | 2010-12-01 | ソニー株式会社 | 半導体基板、液晶表示装置及びプロジェクタ |

| JP5094191B2 (ja) * | 2006-04-18 | 2012-12-12 | キヤノン株式会社 | 反射型液晶表示装置及び液晶プロジェクターシステム |

| JP5251068B2 (ja) * | 2007-10-17 | 2013-07-31 | 株式会社リコー | アクティブマトリクス基板及び電子表示装置 |

| JP5488784B2 (ja) * | 2009-02-23 | 2014-05-14 | 株式会社リコー | 回路基板の製造方法及び画像表示装置 |

| DE112018005383T5 (de) | 2017-09-22 | 2020-06-18 | Sony Corporation | Anzeigeelement, anzeigevorrichtung und elektronische vorrichtung |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3187254B2 (ja) * | 1994-09-08 | 2001-07-11 | シャープ株式会社 | 画像表示装置 |

| JP2995725B2 (ja) * | 1994-11-25 | 1999-12-27 | 日本ビクター株式会社 | 液晶表示装置及び、それの駆動方法 |

| JPH10104663A (ja) * | 1996-09-27 | 1998-04-24 | Semiconductor Energy Lab Co Ltd | 電気光学装置およびその作製方法 |

| JPH1115024A (ja) * | 1997-06-24 | 1999-01-22 | Casio Comput Co Ltd | アクティブマトリクス型表示装置 |

-

2001

- 2001-12-21 JP JP2001390158A patent/JP3998470B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002277900A (ja) | 2002-09-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100596143B1 (ko) | 액정 표시 장치 및 그 제조 방법 | |

| JP4791108B2 (ja) | 画像表示装置 | |

| KR101469028B1 (ko) | 표시 장치 | |

| US7944513B2 (en) | Display device | |

| JP4843719B2 (ja) | アレイ及び製品 | |

| JPH0876088A (ja) | 画像表示装置 | |

| JP3582193B2 (ja) | 液晶表示素子 | |

| JP5906551B2 (ja) | 補助蓄積コンデンサを有するcmos技術における透過型液晶ディスプレイ | |

| JP2008191626A (ja) | 液晶表示装置 | |

| JP4635139B2 (ja) | 能動マトリックス液晶ディスプレイデバイス | |

| JP3687399B2 (ja) | 電気光学装置及びその製造方法 | |

| US6507376B2 (en) | Display device formed on semiconductor substrate and display system using the same | |

| JP3998470B2 (ja) | 液晶表示装置および表示システム | |

| JPH0213928A (ja) | 薄膜トランジスタアレイ | |

| JPWO2009041112A1 (ja) | 表示装置 | |

| JPH10142636A (ja) | アクティブマトリクス型表示回路 | |

| JP2023527254A (ja) | 表示基板及び表示装置 | |

| US6744479B2 (en) | Active matrix display device | |

| JP3286843B2 (ja) | 液晶パネル | |

| JPH0534709A (ja) | 液晶表示装置 | |

| JP2006098641A (ja) | 薄膜半導体装置、電気光学装置、および電子機器 | |

| JP2008180807A (ja) | 電気光学装置およびその電気光学装置を備えた電子機器 | |

| CN111752056B (zh) | 面板及其像素结构 | |

| JP5034434B2 (ja) | 電気光学装置 | |

| JP4442121B2 (ja) | 半導体集積回路及び表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041221 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20041221 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070326 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070417 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070612 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070731 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070807 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3998470 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100817 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110817 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110817 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120817 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120817 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130817 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |