JP3965583B2 - 表示画素及び表示装置 - Google Patents

表示画素及び表示装置 Download PDFInfo

- Publication number

- JP3965583B2 JP3965583B2 JP2003308606A JP2003308606A JP3965583B2 JP 3965583 B2 JP3965583 B2 JP 3965583B2 JP 2003308606 A JP2003308606 A JP 2003308606A JP 2003308606 A JP2003308606 A JP 2003308606A JP 3965583 B2 JP3965583 B2 JP 3965583B2

- Authority

- JP

- Japan

- Prior art keywords

- display

- pixel

- current

- electrode

- display pixel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Electroluminescent Light Sources (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Control Of El Displays (AREA)

Description

特に、アクティブマトリックス駆動方式を適用した発光素子型ディスブレイは、近年普及が著しい液晶表示装置(LCD)に比較して、表示応答速度が速く、視野角依存性もなく、また、高輝度・高コントラスト化、表示画質の高精細化、低消費電力化等が可能であるとともに、液晶表示装置の場合のように、バックライトを必要としないので、一層の薄型軽量化が可能という極めて優位な特徴を有しており、次世代のディスプレイとして研究開発が盛んに行われている。

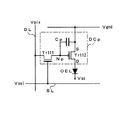

そして、このような構成を有する画素駆動回路DCpにおいては、薄膜トランジスタTr111及びTr112からなる2個のスイッチング手段を所定のタイミングでオン、オフ制御することにより、以下に示すように、有機EL素子OELを発光制御する。

このような駆動制御方法は、各表示画素(薄膜トランジスタTr112のゲート端子)に印加する電圧(階調信号電圧)を調整することにより、有機EL素子OELに流す発光駆動電流の電流値を制御して、所定の輝度階調で発光動作させていることから、電圧印加方式(又は、電圧指定方式)と呼ばれている。

そこで、このような問題点を解決する構成として、いわゆる、電流印加方式(又は、電流指定方式)と呼ばれる駆動制御方法に対応した画素駆動回路の構成が知られている。なお、この電流印加方式に対応した画素駆動回路の構成例については、後述する発明の実施の形態において詳しく説明するが、概略、以下のような構成及び動作(機能)を有するものである。

この容量成分は、上述のように、表示データに応じて供給される電圧又は電流に応じた電荷を保持して発光駆動電流を生成するものであるため、良好な表示状態を得るためには、ある程度大きな容量値を有していることが好ましい。従来、この容量成分は、駆動用トランジスタのゲート−ソース間に形成される寄生容量の他、駆動用トランジスタのゲート電極やソース電極に接続される金属膜による電極を設けて形成される。しかしながら、このような電極は非透過性の金属膜によって形成されものであるため、容量成分の容量値を大きくするために電極部分の面積が増大すると、発光素子の形成面積(発光面積)が相対的に小さくなって、開口率の低下を招き、表示パネルにおける表示画質の劣化が生じるという問題を有していた。

請求項4記載の発明は、請求項1乃至3のいずれかに記載の表示画素において、前記電圧保持手段は、前記第1の導電層のパターン形状に応じて、前記第1及び第2の容量素子の容量値を設定することを特徴とする。

請求項6記載の発明は、請求項1乃至5のいずれかに記載の表示画素において、前記発光素子は、前記発光制御手段により供給される前記駆動電流の電流値に応じて、所定の輝度階調で発光動作する電流制御型の発光素子であることを特徴とする。

請求項7記載の発明は、請求項6記載の表示画素において、前記発光素子は、有機エレクトロルミネッセント素子であることを特徴とする。

請求項11記載の発明は、請求項8乃至10のいずれかに記載の表示装置において、前記電圧保持手段は、前記第1の導電層のパターン形状に応じて、前記第1及び第2の容量素子の容量値を設定することを特徴とする。

請求項13記載の発明は、請求項8乃至12のいずれかに記載の表示装置において、前記発光素子は、前記発光制御手段により供給される前記駆動電流の電流値に応じて、所定の輝度階調で発光動作する電流制御型の発光素子であることを特徴とする。

ここで、画素駆動回路を構成する各回路素子及び配線部は、各表示画素の形成領域(画素領域)の外縁部に沿って配置されている。

<表示画素>

まず、本発明に係る表示画素に適用される画素駆動回路について説明する。

図1は、本発明に係る表示画素(画素駆動回路)の一実施形態を示す回路構成図である。なお、ここで示す画素駆動回路は、上述した電流印加方式に対応した一構成例を示すものにすぎず、同等の機能を有する他の回路構成を適用するものであってもよいことはいうまでもない。

図2は、本実施形態に係る表示画素(画素駆動回路)に適用されるパターンレイアウトの一例を示すレイアウト図であり、図3は、図2に示したパターンレイアウトにおける各回路素子の配置を示す等価回路図である。図4は、本実施形態に係る表示画素(画素駆動回路)を構成する容量素子の構成例を示す概念的な等価回路図及び断面構造図である。ここでは、図1に示した画素駆動回路の回路構成を適宜参照しながら説明する。

次に、本発明に係る表示画素を2次元配列して構成される表示パネルを備えた表示装置について簡単に説明する。

図5は、本発明に係る表示画素を2次元配列した表示パネルを備えた表示装置の一実施形態を示す概略ブロック図であり、図6は、本実施形態に係る表示装置の要部構成を示す概略構成図である。ここで、上述した実施形態に示した表示画素と同等の構成については、同一の符号を付して説明する。

図7は、本実施形態に係る表示画素(画素駆動回路)における発光素子の駆動制御動作を示すタイミングチャートである。ここでは、上述した表示装置(図5、図6)及び表示画素(図1)の構成を適宜参照しながら説明する。

このような一連の駆動制御動作を、図7に示すように、表示パネル110を構成する全ての行の表示画素群について順次繰り返し実行することにより、表示パネル一画面分の表示データが書き込まれて、各表示画素EMが所定の輝度階調で発光し、所望の画像情報を表示パネル110に表示することができる。

DCx 画素駆動回路

SLa、SLb 走査ライン

DL データライン

VL 電源ライン

La 素子間配線部

Lb 半導体層

Lc 配線部

Cx コンデンサ

OEL 有機EL素子

Claims (13)

- 少なくとも、表示データに基づく階調信号を電圧成分として保持する電圧保持手段と、該電圧保持手段に保持された前記電圧成分に基づいて、前記表示データに応じた駆動電流を生成し、該駆動電流を発光素子に供給する制御を行う発光制御手段と、を備えた画素駆動回路を有する表示画素において、

前記発光制御手段は、前記駆動電流を生成して供給する半導体層からなる電流路を有して該電流路の一端が前記発光素子に接続されたトランジスタ素子を有し、

前記電圧保持手段は、前記画素駆動回路を構成する回路素子相互を接続し、前記電流路の他端に接続される配線部を一方の電極とし、前記トランジスタ素子の制御端子に接続されて前記配線部に対向して形成された第1の導電層を他方の電極とする第1の容量素子と、前記第1の導電層を一方の電極とし、前記半導体層を延長して前記第1の導電層に対向して形成された第2の導電層を他方の電極とする第2の容量素子と、からなることを特徴とする表示画素。 - 前記トランジスタ素子は、電界効果型トランジスタであって、

前記配線部は、前記電界効果型トランジスタの電流路を構成する端子電極に一体的に形成された金属導電層であり、前記第1の導電層は、前記電界効果型トランジスタの制御電極に一体的に形成された金属導電層であることを特徴とする請求項1記載の表示画素。 - 前記画素駆動回路は、前記表示データに応じた電流値を有する階調電流が供給され、該階調電流に基づく電荷を、前記電圧成分として前記電圧保持手段に保持することを特徴とする請求項1又は2記載の表示画素。

- 前記電圧保持手段は、前記第1の導電層のパターン形状に応じて、前記第1及び第2の容量素子の容量値を設定することを特徴とする請求項1乃至3のいずれかに記載の表示画素。

- 前記画素駆動回路を構成する各回路素子及び前記配線部は、前記表示画素の形成領域の外縁部に沿って配置されていることを特徴とする請求項1乃至4のいずれかに記載の表示画素。

- 前記発光素子は、前記発光制御手段により供給される前記駆動電流の電流値に応じて、所定の輝度階調で発光動作する電流制御型の発光素子であることを特徴とする請求項1乃至5のいずれかに記載の表示画素。

- 前記発光素子は、有機エレクトロルミネッセント素子であることを特徴とする請求項6記載の表示画素。

- 2次元配列された複数の表示画素を有する表示パネルを備え、前記各表示画素に対して、表示データに基づく階調信号を供給することにより、前記表示パネルに所望の画像情報を表示する表示装置において、

前記各表示画素は、少なくとも、前記階調信号を電圧成分として保持する電圧保持手段と、該電圧保持手段に保持された前記電圧成分に基づいて、前記表示データに応じた駆動電流を生成し、該駆動電流を発光素子に供給する制御を行う発光制御手段と、を備えた画素駆動回路を具備し、

前記発光制御手段は、前記駆動電流を生成して供給する半導体層からなる電流路を有して該電流路の一端が前記発光素子に接続されたトランジスタ素子を有し、

前記電圧保持手段は、前記画素駆動回路を構成する回路素子相互を接続し、前記電流路の他端に接続される配線部を一方の電極とし、前記トランジスタ素子の制御端子に接続されて前記配線部に対向して形成された第1の導電層を他方の電極とする第1の容量素子と、前記第1の導電層を一方の電極とし、前記半導体層を延長して前記第1の導電層に対向して形成された第2の導電層を他方の電極とする第2の容量素子と、からなることを特徴とする表示装置。 - 前記表示装置は、少なくとも、

前記各表示画素を選択状態に設定するための選択信号を印加する走査駆動手段と、

前記選択状態に設定された前記各表示画素に、前記表示データに基づく階調信号を供給する信号駆動手段と、

を備えることを特徴とする請求項8記載の表示装置。 - 前記信号駆動手段は、前記階調信号として、前記表示データに応じた電流値を有する階調電流を前記表示画素に供給し、

前記画素駆動回路は、前記階調電流に基づく電荷を、前記電圧成分として前記電圧保持手段に保持することを特徴とする請求項9記載の表示装置。 - 前記電圧保持手段は、前記第1の導電層のパターン形状に応じて、前記第1及び第2の容量素子の容量値を設定することを特徴とする請求項8乃至10のいずれかに記載の表示装置。

- 前記画素駆動回路を構成する各回路素子及び前記配線部は、前記各表示画素の形成領域の外縁部に沿って配置されていることを特徴とする請求項8乃至11のいずれかに記載の表示装置。

- 前記発光素子は、前記発光制御手段により供給される前記駆動電流の電流値に応じて、所定の輝度階調で発光動作する電流制御型の発光素子であることを特徴とする請求項8乃至12のいずれかに記載の表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003308606A JP3965583B2 (ja) | 2003-09-01 | 2003-09-01 | 表示画素及び表示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003308606A JP3965583B2 (ja) | 2003-09-01 | 2003-09-01 | 表示画素及び表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005077802A JP2005077802A (ja) | 2005-03-24 |

| JP3965583B2 true JP3965583B2 (ja) | 2007-08-29 |

Family

ID=34411036

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003308606A Expired - Fee Related JP3965583B2 (ja) | 2003-09-01 | 2003-09-01 | 表示画素及び表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3965583B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI429327B (zh) * | 2005-06-30 | 2014-03-01 | Semiconductor Energy Lab | 半導體裝置、顯示裝置、及電子設備 |

| JP4939045B2 (ja) | 2005-11-30 | 2012-05-23 | セイコーエプソン株式会社 | 発光装置および電子機器 |

| JP4661557B2 (ja) | 2005-11-30 | 2011-03-30 | セイコーエプソン株式会社 | 発光装置および電子機器 |

| KR101212153B1 (ko) * | 2005-12-30 | 2012-12-13 | 엘지디스플레이 주식회사 | 유기 전계발광소자 및 그 제조방법 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4334045B2 (ja) * | 1999-02-09 | 2009-09-16 | 三洋電機株式会社 | エレクトロルミネッセンス表示装置 |

| JP2002190598A (ja) * | 2000-12-20 | 2002-07-05 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタアレイ基板およびその製造方法 |

| JP4137454B2 (ja) * | 2001-01-17 | 2008-08-20 | 株式会社半導体エネルギー研究所 | 発光装置、電子機器及び発光装置の作製方法 |

-

2003

- 2003-09-01 JP JP2003308606A patent/JP3965583B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005077802A (ja) | 2005-03-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10529280B2 (en) | Display device | |

| JP4144462B2 (ja) | 電気光学装置及び電子機器 | |

| JP5555656B2 (ja) | 画像表示装置およびその制御方法 | |

| JP5152448B2 (ja) | 画素駆動回路及び画像表示装置 | |

| KR100668270B1 (ko) | 전자 장치 및 전자 기기 | |

| US8344975B2 (en) | EL display device with voltage variation reduction transistor | |

| WO2010137298A1 (ja) | 画像表示装置 | |

| TW201009794A (en) | Image display device | |

| JP2010019950A (ja) | 電気光学装置および電子機器 | |

| CN114512099B (zh) | 显示装置 | |

| CN100435191C (zh) | 单位电路及其控制方法、电子装置以及电子机器 | |

| JP3965583B2 (ja) | 表示画素及び表示装置 | |

| JP2004145281A (ja) | 電子回路、電子回路の駆動方法、電気光学装置、電気光学装置の駆動方法及び電子機器 | |

| JP2004145279A (ja) | 電子回路、電子回路の駆動方法、電気光学装置、電気光学装置の駆動方法及び電子機器 | |

| WO2006054189A1 (en) | Active matrix display devices | |

| JP2008083117A (ja) | 表示装置 | |

| JP2010055116A (ja) | 電気光学装置及び電子機器 | |

| JP4458084B2 (ja) | 電気光学装置及び電子機器 | |

| JP2008090276A (ja) | 発光表示デバイス | |

| JP2006072385A (ja) | 電子装置及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050118 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070130 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070202 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070403 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070502 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070515 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 3965583 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110608 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110608 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120608 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120608 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130608 Year of fee payment: 6 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |