JP3931445B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP3931445B2 JP3931445B2 JP25628798A JP25628798A JP3931445B2 JP 3931445 B2 JP3931445 B2 JP 3931445B2 JP 25628798 A JP25628798 A JP 25628798A JP 25628798 A JP25628798 A JP 25628798A JP 3931445 B2 JP3931445 B2 JP 3931445B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- lower electrode

- insulating film

- potential

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 17

- 238000004519 manufacturing process Methods 0.000 title claims description 15

- 238000009792 diffusion process Methods 0.000 claims description 29

- 239000003990 capacitor Substances 0.000 claims description 20

- 239000000758 substrate Substances 0.000 claims description 9

- 229910052788 barium Inorganic materials 0.000 claims description 7

- 238000000151 deposition Methods 0.000 claims description 7

- 229910052797 bismuth Inorganic materials 0.000 claims description 6

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 claims description 4

- 239000007772 electrode material Substances 0.000 claims description 4

- 239000012535 impurity Substances 0.000 claims description 4

- 229910045601 alloy Inorganic materials 0.000 claims description 3

- 239000000956 alloy Substances 0.000 claims description 3

- 230000001590 oxidative effect Effects 0.000 claims description 3

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 claims description 2

- 238000011049 filling Methods 0.000 claims description 2

- 230000004888 barrier function Effects 0.000 claims 3

- 238000000059 patterning Methods 0.000 claims 1

- 239000010408 film Substances 0.000 description 112

- 239000010410 layer Substances 0.000 description 50

- 238000000034 method Methods 0.000 description 49

- 238000006243 chemical reaction Methods 0.000 description 31

- 239000010936 titanium Substances 0.000 description 22

- 239000011229 interlayer Substances 0.000 description 15

- 229910052451 lead zirconate titanate Inorganic materials 0.000 description 15

- 238000003860 storage Methods 0.000 description 15

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 13

- 238000001312 dry etching Methods 0.000 description 13

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 13

- 239000000463 material Substances 0.000 description 12

- 230000010287 polarization Effects 0.000 description 12

- 229910052718 tin Inorganic materials 0.000 description 12

- 230000002265 prevention Effects 0.000 description 11

- 239000010409 thin film Substances 0.000 description 11

- 230000002093 peripheral effect Effects 0.000 description 10

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 9

- 238000005229 chemical vapour deposition Methods 0.000 description 9

- 229910052814 silicon oxide Inorganic materials 0.000 description 9

- 229910052721 tungsten Inorganic materials 0.000 description 9

- 238000004544 sputter deposition Methods 0.000 description 8

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 238000000206 photolithography Methods 0.000 description 7

- 229910052719 titanium Inorganic materials 0.000 description 7

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 7

- 239000010937 tungsten Substances 0.000 description 7

- 238000010438 heat treatment Methods 0.000 description 6

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 6

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 5

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 5

- 229910052745 lead Inorganic materials 0.000 description 5

- 229910052760 oxygen Inorganic materials 0.000 description 5

- 239000001301 oxygen Substances 0.000 description 5

- 229920002120 photoresistant polymer Polymers 0.000 description 5

- 101001071233 Homo sapiens PHD finger protein 1 Proteins 0.000 description 4

- 101000612397 Homo sapiens Prenylcysteine oxidase 1 Proteins 0.000 description 4

- 102100036879 PHD finger protein 1 Human genes 0.000 description 4

- MCMNRKCIXSYSNV-UHFFFAOYSA-N Zirconium dioxide Chemical compound O=[Zr]=O MCMNRKCIXSYSNV-UHFFFAOYSA-N 0.000 description 4

- WOIHABYNKOEWFG-UHFFFAOYSA-N [Sr].[Ba] Chemical compound [Sr].[Ba] WOIHABYNKOEWFG-UHFFFAOYSA-N 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- 238000002425 crystallisation Methods 0.000 description 4

- 230000008025 crystallization Effects 0.000 description 4

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910052726 zirconium Inorganic materials 0.000 description 4

- 229910002113 barium titanate Inorganic materials 0.000 description 3

- 229910052681 coesite Inorganic materials 0.000 description 3

- 229910052906 cristobalite Inorganic materials 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 229910052738 indium Inorganic materials 0.000 description 3

- 229910052741 iridium Inorganic materials 0.000 description 3

- 229910052742 iron Inorganic materials 0.000 description 3

- 238000002955 isolation Methods 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 238000005546 reactive sputtering Methods 0.000 description 3

- 229910052707 ruthenium Inorganic materials 0.000 description 3

- 239000000377 silicon dioxide Substances 0.000 description 3

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 3

- 238000000992 sputter etching Methods 0.000 description 3

- 229910052682 stishovite Inorganic materials 0.000 description 3

- 229910052712 strontium Inorganic materials 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- 229910052905 tridymite Inorganic materials 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 101100166255 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) CEP3 gene Proteins 0.000 description 2

- -1 TiN Chemical class 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 229910052770 Uranium Inorganic materials 0.000 description 2

- 229910052769 Ytterbium Inorganic materials 0.000 description 2

- 229910052787 antimony Inorganic materials 0.000 description 2

- 239000005380 borophosphosilicate glass Substances 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 229910052735 hafnium Inorganic materials 0.000 description 2

- HFGPZNIAWCZYJU-UHFFFAOYSA-N lead zirconate titanate Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ti+4].[Zr+4].[Pb+2] HFGPZNIAWCZYJU-UHFFFAOYSA-N 0.000 description 2

- 229910052748 manganese Inorganic materials 0.000 description 2

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 229910052725 zinc Inorganic materials 0.000 description 2

- 102100021753 Cardiolipin synthase (CMP-forming) Human genes 0.000 description 1

- 101000895518 Homo sapiens Cardiolipin synthase (CMP-forming) Proteins 0.000 description 1

- 229910019695 Nb2O6 Inorganic materials 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 229910010413 TiO 2 Inorganic materials 0.000 description 1

- VNSWULZVUKFJHK-UHFFFAOYSA-N [Sr].[Bi] Chemical compound [Sr].[Bi] VNSWULZVUKFJHK-UHFFFAOYSA-N 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 229910021523 barium zirconate Inorganic materials 0.000 description 1

- DQBAOWPVHRWLJC-UHFFFAOYSA-N barium(2+);dioxido(oxo)zirconium Chemical compound [Ba+2].[O-][Zr]([O-])=O DQBAOWPVHRWLJC-UHFFFAOYSA-N 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 229910002115 bismuth titanate Inorganic materials 0.000 description 1

- 229910052793 cadmium Inorganic materials 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- DQUIAMCJEJUUJC-UHFFFAOYSA-N dibismuth;dioxido(oxo)silane Chemical compound [Bi+3].[Bi+3].[O-][Si]([O-])=O.[O-][Si]([O-])=O.[O-][Si]([O-])=O DQUIAMCJEJUUJC-UHFFFAOYSA-N 0.000 description 1

- NKZSPGSOXYXWQA-UHFFFAOYSA-N dioxido(oxo)titanium;lead(2+) Chemical compound [Pb+2].[O-][Ti]([O-])=O NKZSPGSOXYXWQA-UHFFFAOYSA-N 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000011835 investigation Methods 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 229910052746 lanthanum Inorganic materials 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229910052700 potassium Inorganic materials 0.000 description 1

- 230000003449 preventive effect Effects 0.000 description 1

- 229910052702 rhenium Inorganic materials 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 238000003980 solgel method Methods 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 230000002269 spontaneous effect Effects 0.000 description 1

- PBCFLUZVCVVTBY-UHFFFAOYSA-N tantalum pentoxide Inorganic materials O=[Ta](=O)O[Ta](=O)=O PBCFLUZVCVVTBY-UHFFFAOYSA-N 0.000 description 1

- 229910052716 thallium Inorganic materials 0.000 description 1

- 239000004408 titanium dioxide Substances 0.000 description 1

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 1

- 229910021342 tungsten silicide Inorganic materials 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/55—Capacitors with a dielectric comprising a perovskite structure material

- H01L28/56—Capacitors with a dielectric comprising a perovskite structure material the dielectric comprising two or more layers, e.g. comprising buffer layers, seed layers, gradient layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/55—Capacitors with a dielectric comprising a perovskite structure material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/60—Electrodes

- H01L28/75—Electrodes comprising two or more layers, e.g. comprising a barrier layer and a metal layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/28568—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table the conductive layers comprising transition metals

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

- H10B12/0335—Making a connection between the transistor and the capacitor, e.g. plug

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Semiconductor Memories (AREA)

Description

【発明の属する技術分野】

本発明は、高強誘電体薄膜を用いた素子、特に、大規模集積回路(LSI)に好適な、分極反転型不揮発性メモリ、またはダイナミックランダムアクセスメモリの半導体装置及びその製造方法に関する。

【0002】

【従来の技術】

高強誘電体物質には、数百から数千と極めて大きな比誘電率を持つものがある。従って、それらの高強誘電体の薄膜をキャパシタ絶縁膜に用いれば、大規模集積回路(LSI)に好適な小面積かつ、大容量のキャパシタが得られる。また、高強誘電体物質は自発分極をもち、外部電場によりその方向を反転させることができるので、この特性を用いて、不揮発性メモリが得られる。

【0003】

従来の高強誘電体を用いたメモリは、例えば、特開平5-90606号に記載されている。図22に示すように、層間絶縁膜224の上に順次下部Pt電極225、高強誘電体薄膜226、上部Pt電極227、Ti電極228を形成し、高強誘電体キャパシタを形成していた。なお、図中、221は素子分離膜、222はワード線、223は不純物拡散層、229はアルミニウム配線層を示す。しかし、この技術ではそれぞれの層を独立のマスクで加工する為、寸法精度、合わせ精度の問題がある。そこで、特開平2-288368号に記載されているような構造が提案されている。即ち、図23に示す通り、上部電極層238、高強誘電体膜237、下部電極層236を一括でドライエッチングする方法である。しかし、一括加工によってリーク電流が大きくなってしまう。そこで、特開平3−256358号に記載されているように、図24に示す通り、下部電極のみを加工し、高強誘電体膜、上部電極はセル毎には加工しないでメモリマットの外側などで大きなパタ−ンとして加工し、合わせ余裕の不要な構造とする高集積メモリを実現する方法がある。

【0004】

一方、図25は特開平7−14993号に記載されている別の従来のメモリセル構造である。この構造も下部電極のみを微細に加工し、高強誘電体膜、上部電極はセル毎には加工しない構造であるが、層間絶縁膜とキャパシタ絶縁膜の間に密着層254が介在している点に特徴がある。密着層としてはTiO2、ZrO2、Ta2O5、Si3N4などが効果があると記載されている。

【0005】

また、別の従来のメモリセル構造として、特開平7−169854号に記載されているように、図26に示したとおり下部電極と拡散防止層を反応防止膜のなかに埋め込んでしまう構造が提案されている。この構造は、以下のようなプロセスによって得られる。まず、層間絶縁膜248にコンタクト孔を開け、多結晶シリコン膜246で埋めた後、Ti膜を形成し、このTi膜を下部電極よりも一回り大きな形状に加工すると共に、下部電極を形成する孔を開口する。続いて拡散防止膜249、下部電極251をこの孔の内部に形成する。この高強誘電体膜252堆積時に、前記Ti膜を酸化させ反応防止層のTiO2261を形成する。

【0006】

【発明が解決しようとする課題】

図24に示した構造において、キャパシタ絶縁膜にチタン酸ジルコン酸鉛(PZT)を用いた場合、発明者等の検討によれば、PZTと層間絶縁膜である酸化シリコン膜が直接接する部分で両者の反応が起きてしまうことがわかった。この反応は500℃程度の低温でも起こり、特に700℃以上の温度でPZTを形成すると、酸化シリコン層がPZTと完全に反応し、熔融状態を呈した。この現象は、PZTの主要構成元素である鉛に起因することが明らかになった。

【0007】

図25に示した構造を用いる場合には、発明者等の検討によると、密着層としてのSi3N4は酸化シリコン膜と同様にPZTと反応を起こしてしまうが、TiO2、ZrO2、Ta2O5を密着層に用いれば、この密着層がPZTと酸化シリコン膜の反応防止層としての役割を果たすため、上記のPZTと酸化シリコン膜の反応の問題は解決できることがわかった。しかし、この構造では、高強誘電体膜252の形成時、下部電極の下におかれた拡散防止層249の側面が露出しているため、成膜中に加熱酸化雰囲気を必要とするCVD法などでPZT膜を形成すると、拡散防止層249が酸化されて膜剥がれなどの問題を生じることが明らかとなった。sol-gel法、スパッタリング法、蒸着法などを用いた場合にも、結晶化の熱処理を行う際に拡散防止層249が酸化されて同様の問題を生じることがわかった。拡散防止層249にはTiN 、(Ti、Al)NやWNなどの金属窒化物が広く用いられているが、金属窒化物が酸化されると窒素を放出するためそのうえに形成されている膜の剥がれが顕著になってしまうと考えられる。

【0008】

図26に示した構造では、Tiが酸化される際に堆積膨張が起こるため高強誘電体膜の剥離が生じてしまう。

【0009】

本発明の目的は、高強誘電体膜と絶縁膜との反応を防ぎ、かつ膜剥離を防いだ、半導体装置及びその製造方法を達成することにある。

【0010】

【課題を解決するための手段】

上記目的は、高強誘電体膜と層間絶縁膜との間に反応防止膜を設け、拡散防止膜の側面と高強誘電体膜とが接触しておらず、下部電極の側壁と高強誘電体膜とが接した半導体装置とすることによって達成される。

【0011】

上記の構成とすることで、たとえば反応防止膜としてTiO2を用いる場合には、膜厚が2nm以上あれば、PZT膜の結晶化に必要な700℃程度の急速熱処理時にも、シリコン系層間絶縁膜とキャパシタ絶縁膜に含まれる鉛との反応を防止するのに効果的である。また、拡散防止膜のみを反応防止膜の中に埋め込んでいるので、下部電極の側壁をキャパシタとして利用することも可能となり、DRAMに応用する場合には特に有効である。

【0012】

また、上記目的は、拡散防止膜を層間絶縁膜中にプラグとして埋め込み、キャパシタ絶縁膜と層間絶縁膜の間に反応防止膜を介在させることによって達成される。この構造でも、プラグ上に下部電極を形成することとなるため、下部電極の側面から上面にかけて高強誘電体膜が設けられることとなり、下部電極の側壁をキャパシタとして利用することも可能となり、DRAMに応用する場合には特に有効である。

【0013】

また、上記目的は、層間絶縁膜上に反応防止として機能する反応防止膜を形成し、その後拡散防止膜、高強誘電体膜を形成することによって達成される。拡散防止膜や高強誘電体膜を形成する前に、予め反応防止膜を酸化物として形成しておくので、反応防止膜自体を金属膜の酸化により形成しても堆積膨張による剥離等の問題を引き起こさない。

【0014】

以上、キャパシタ絶縁膜としてPZTを用いた場合についてのべたが、同様の効果はPZT以外の鉛系高強誘電体やBi4Ti3O12、Sr2Bi2Ta5O9などのBi系層状高強誘電体を用いた場合にも見られた。Bi系層状高強誘電体は一般にPb系高強誘電体と比べて結晶化温度が高くなる分、層間絶縁膜との相互拡散も大きくなるため、反応防止膜がより必要とされる。

【0015】

また、従来、鉛やビスマスを含有しない誘電体、例えばチタン酸ストロンチウムバリウム(BST)では、下部電極の下地である酸化シリコン膜との反応は顕著でなく大きな問題とならない考えられていた。しかし、発明者らの検討によると、PbやBiと比べると拡散係数が小さいが、BaやSrも下地SiO2中へ拡散することがわかった。従って、BST系の膜を用いた場合でも、反応防止膜を設ける意義が大きいことがわかった。

【0016】

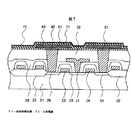

(参考例1)本発明と関連する参考例を図1を用いて説明する。参考例1によるトランジスタを含む素子層上に、公知な方法で形成されたトランジスタを含む素子層上に、公知な方法で形成された拡散防止層51が反応防止層43の中に埋め込まれてある。この上に、下部電極を形成し、所望の形状に加工した後、鉛を含有する高強誘電体薄膜71、上部電極72を形成した。

【0017】

この構造においては、高強誘電体薄膜71と上部電極72は各メモリセルに対応したパターンに分離されてはおらず、複数のメモリセルに渡って連続して存在する。この2層は、記憶装置の動作上必要な最小限の加工(例えばメモリセル領域とそれ以外の領域を分離する部分)にとどめることができ、加工精度への要求が大幅緩和される。

【0018】

また、拡散防止層51は、反応防止層43の中に埋め込まれてあり、高強誘電体薄膜71の結晶化熱処理時に酸化されることがない。

【0019】

図2から図6は、本発明を用いてメモリセルを製造する実施例である。まず、図2に示すように、スイッチ用トランジスタを従来のMOSFET形成工程により形成する。p型半導体基板21にn型不純物拡散層(リン)25、26を形成し、素子間分離酸化膜22、ゲート酸化膜23、ワード線24、絶縁膜27を形成する。続いて表面全体に公知のCVD法を用いて厚さ600nmのSiO228をCVD法により堆積させ、850℃でリフロー後300nmエッチバックすることでワード線による段差を緩和した。

【0020】

次に、ビット線が基板表面のn型拡散層と接触する部分25を公知のホトリソグラフィ法とドライエッチング法を用いて開口する(図3)。次に、ビット線31を形成する。ビット線の材料としては、金属のシリサイドと多結晶シリコンの積層膜を用いた。公知のホトリソグラフィ法とドライエッチング法を用いて加工し、ビット線を所望のパターンとする。 次に、BPSGなどのシリコン酸化膜系の絶縁膜32を堆積させ、平坦化する。この絶縁膜32は、基板表面を平坦化するのに十分な膜厚とする必要がある。本実施例では、絶縁膜32の膜厚を600nmとし、公知の化学機械研磨法により平坦化する方法を用いた。次に、層間絶縁膜上に反応防止層43を形成した。反応防止層としては反応性スパッタリング法によりTiO2膜を50nm堆積する方法と、Ti膜を堆積した後、酸素雰囲気中、750℃、30分の熱処理によりTiを酸化する方法を試み、ともに良好な結果が得られた。

【0021】

次に、図4のように公知のホトリソグラフィ法とドライエッチング法を用いて蓄積容量部が基板と接触するメモリ部コンタクト孔41を開口する。絶縁膜32上とコンタクト孔内側に多結晶シリコン42をCVD法により350nmデポした。次に、ドライエッチング法により多結晶シリコン42を膜厚分エッチバックして、コンタクト孔を埋めた。さらに、膜厚50nm相当のオーバーエッチングを追加して、多結晶シリコンの表面が穴の中に落ち込んでいる構造とする。 次に拡散防止層51としてスパッタリング法を用いて厚さ100nmのTiNを形成し、 CMP法により平坦化してコンタクト孔にTiNを埋め込む。これにより、図5の埋め込み拡散防止層が形成される。

【0022】

次にスパッタリング法により下地電極61として厚さ100nmのPt膜61を被着し(図6)、引き続き、Pt加工用マスクとして厚さ100nmのタングステン62を被着した。ホトレジスト63をマスクにSF6を用いたドライエッチング法によりタングステン63にパターンを転写する。ホトレジスト63を除去した後、タングステン62をマスクに用いたスパッタエッチング法により下部電極61をパターンニングする。

【0023】

タングステンマスクを除去した後、高強誘電体薄膜71を形成する(図7)。本実施例では、反応性蒸着法により、厚さ約100nmのチタン酸ジルコン酸鉛(Pb(Zr0.5Ti0.5)O 3)薄膜形成した後、酸素雰囲気中で650℃、30秒の熱処理を行ない結晶化させた。高強誘電体薄膜の形成には反応性スパッタリング法、あるいは、CVD法を用いてもよい。次に、スパッタリング法により上部電極として厚さ50nmのPt膜72を被着した。あとは層間絶縁膜と配線を施して図1のメモリセルを完成させる。

【0024】

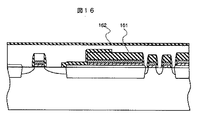

(参考例2)図8は、参考例1をDRAMに用いた場合の参考例を示すものである。本参考例ではキャパシタ下部電極を厚くし、その側壁を利用する事でキャパシタの静電容量を大きくしている。

【0025】

図9から図11を用いて、本発明を用いてメモリセルを製造する方法を説明する。図5に示したように埋め込み拡散防止層を形成するまでの製造工程は実施例1と同じである。

【0026】

図9のようにスパッタリング法により下地電極91を形成する。本実施例では、下地電極としては厚さ400nmのRu膜を用いた。SiO2をマスクに用いたドライエッチング法により下部電極91を加工し、 SiO2マスクを除去して図10に示したような構造を得る。

【0027】

次に、図11に示したようにMOCVD法を用いてBST膜111を30nm堆積した。後は上部電極を形成し、配線を施して図8のメモリセルを完成させる。

【0028】

【発明の実施の形態】

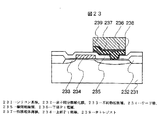

(実施例1)キャパシタの下部電極に対して反応防止層を自己整合的に形成することにより、下部電極とコンタクトプラグの合わせ余裕が不要となり高集積化に適した微細なメモリセルが実現できる、本発明の実施例について図15から図21を用いて説明する。

【0029】

まず、図15に示すように、p型半導体基板21上に素子間分離絶縁膜22、ゲート酸化膜23を形成する。厚さ60nmの多結晶シリコン、厚さ60nmのタングステンシリサイドからなるワード線24、厚さ200nmSi3N4層151を順次堆積し、公知のホトリソグラフィ法とドライエッチング法を用いて加工し、ゲート電極となるワード線所望のパターンとする。ワード線をマスクにイオン打ち込みによりn型不純物拡散層(リン)25、26を形成する。厚さ80nmのSi3N4層をCVD法により被着し、異方性ドライエッチング法により加工して、ワード線側壁の絶縁膜層152を形成する。

【0030】

次に、図16のように厚さ300nmのSiO2161を公知のCVD法を用いて堆積させた後、CMP法により平坦化する。次に、厚さ40nmのSi3N4162を公知のCVD法を用いて堆積させる。

【0031】

公知のホトリソグラフィ法とドライエッチング法を用いてビット線が基板表面のn型拡散層25と接触する部分および、蓄積電極が基板表面のn型拡散層26と接触する部分と周辺回路へのコンタクト孔を開孔する(図17)。CVD法により厚さ100nmのTiNを堆積し、CMP法によりコンタクト孔にTiN181を埋め込む。次に、図18に示したように第一の配線層を形成する。材料としては、W/TiN/Tiの積層膜182を用いた。スパッタリング法によりW/TiN/Tiの積層膜を堆積し、この上に、厚さ50nmのSiO2183を堆積させた後、公知のホトリソグラフィ法とドライエッチング法を用いて加工し、第一の配線層を所望のパターンとする。第一の配線層はビット線および周辺回路の配線に用いられる。膜厚50nmのSiO2をCVD法により堆積し、ドライエッチング法によりエッチバックして、第一の配線層の側壁部にSiO2のサイドウォールスペーサ184を形成し、第一の配線層を絶縁する。

【0032】

次に、BPSGなどのシリコン酸化膜系の絶縁膜191を堆積させ、平坦化する。本実施例では、絶縁膜191の膜厚を250nmとし、CMP法により平坦化した。公知のホトリソグラフィ法とドライエッチング法を用いて蓄積容量部と拡散層を接続するためのメモリ部コンタクト孔を開口する。同時に第一の配線層と第二の配線層をつなぐためのコンタクト孔も開孔する。CVD法により厚さ100nmのTiNを堆積し、CMP法によりコンタクト孔にTiN192を埋め込む。

【0033】

次に、図19に示すとおり、膜厚2nmのTi膜193と膜厚300nmのPt膜194を順次スパッタリング法により堆積し、引き続き、タングステン195を300nm堆積する。ホトレジストをマスクにSF6を用いたドライエッチング法によりタングステン206にパターンを転写する。ホトレジストを除去した後、タングステンをマスクに用いたスパッタエッチング法により下部電極194を加工するより図20に示した構造を得る。スパッタエッチング時にArに酸素を添加することでPtとTiの間の選択性を十分に高くすることが出来る。エッチング後に酸素雰囲気中で700℃、5秒の急速熱処理することによりPt膜194の下にあるTi膜193はPtと合金を作り消失する。そして下部電極の周辺に露出している層間絶縁膜191の上にのみ自己整合的に反応防止膜201が形成される。

【0034】

次に、図21に示すとおり、厚さ20nmのチタン酸ストロンチウムバリウム211、厚さ20nmの二酸化ルテニウム212を順次、MOCVD法により堆積した。ホトレジストをマスクにメモリマット外のプレ−ト電極の不要な部分の二酸化ルテニウム、チタン酸ストロンチウムバリウムを除去した後、層間絶縁膜11と配線12を形成してメモリセルを完成する。本実施例では下部電極材料としてPtを用いたが、RuやIrを用いてもよいことは言うまでもない。

【0035】

(実施例4)

図12にはメモリセルアレイ部とそれに隣接する周辺回路の各一部の要部断面が示されている。図13は本発明のメモリセルと周辺回路の各一部の平面図、図14は本発明のメモリセルと周辺回路の各一部を示す回路図である。図12は図13におけるX−X’断面図である。図12にはメモリセル選択用MISFET、Qtと図13、図14においてQshr、Qp、Qnの符号を付した周辺回路のMISFETが示されている。QshrはDRAMのメモリセル部と周辺回路部のセンスアンプとを分離するシェアードMISFETである。QpはpチャンネルMISFET、QnはnチャンネルMISFETであり、センスアンプ部はQp、Qn2個ずつからなるフリップフロップ回路になっている。

【0036】

図14に示した回路図を用いて、本発明のメモリをDRAMとして用いる場合の読み出し動作を説明する。キャパシタのプレート電極PL1の電位は、常にVcc/2に固定される。一方、キャパシタの蓄積ノードSN1には、揮発情報Vccまたは0が保持される。ビット線対BL1およびBL1Bの電位は、読み出し又は書き換え動作直前まで、Vcc/2に保持される。ビット線対には、記憶情報を検知、増幅するためのセンスアンプSAが接続されている。蓄積ノードSN1の蓄積電圧を検知するため、まず、プリチャージ制御線PCL1の電位をVccから0に下げ、ビット線を電位Vcc/2のフローティング状態とする。同時にシェアードMISFET Qshrをオンにする。次に、ワード線WL1の電位を、0からVchに上げる。ここで、VchはVccにくらべ少なくともトランジスタのしきい電圧だけ高い電位である。この結果、蓄積ノードの電位がVccであった場合には、ビット線BL1の電位がBL1Bの電位すなわちVcc/2よりやや高くなり、一方、0であった場合には、BL1の電位はBL1Bにくらべやや低くなる。この電位差をセンスアンプSA1で検知、増幅することにより、BL1の電位は蓄積ノードの電位に一致してVccまたは0となる。BL1Bの電位はBL1と反対の電位になる。なお、センスアンプを動作させるには、センスアンプpチャネルトランジスタ制御線CSP、センスアンプnチャネルトランジスタ制御線CSNをそれぞれVccおよび0にすれば良い。以上の動作により、選択されたワード線WL1につながるすべてのメモリセルの情報が、それぞれに接続されたビット線に読み出される。このうち一つのメモリセルの情報を選択的にIO線を介して外部に読出すためには、センスアンプ選択線CSL1の電位を0からVchにし、所望のビット線をIO線に接続すれば良い。読み出し動作を終了するには、 CSL1の電位をVchから0に戻した後、ワード線WL1を0に戻せば、蓄積ノードSN1は情報が再書き込みされた状態でビット線から電気的に切り離される。PCL1をVccに、 CSP 、 CSNをそれぞれ0およびVccに戻せば、読み出し動作前の状態となり、動作が終了する。

【0037】

次に、本発明のメモリを高強誘電体不揮発性メモリとして用いる場合の読み出し、書き込み手順について特開平7−21784にもとづいて説明する。

【0038】

まず、読み出し動作であるが、これは上述のDRAMの場合と同じである。

【0039】

高強誘電体不揮発性メモリにおける情報の書き換えでは、蓄積ノードSN1の電位反転と共に、高強誘電体膜の分極反転を行う。書き換え動作において、信号線PCL1をVchから0に下げてからセンスアンプを動作させるまでは、読み出し動作と同様である。次に、IO線に準備した書き換え情報をメモリセルに書き込むため、信号線CLS1を0からVchに上げる。この結果、ビット線対BL1およびBL1Bの電位が反転する。ワード線WL1は活性化された状態にあるので、上記ビット線対電位反転にともなって、所望のメモリセルの蓄積ノード電位および高強誘電体膜の分極方向が反転する。このようにして、情報の書き換えをおこなった後、読み出し動作と同様な手順で書き換え動作を終了する。このような読み出し、書き込み手順よれば、揮発情報と不揮発情報とが常に一致して書き換えられるので、いつ電源をオフしても情報が消失しない。

【0040】

次に、高強誘電体不揮発性メモリにおける電源オン時の不揮発性情報から揮発性情報への変換動作を説明する。電源投入前には、すべての電位は0Vにある。電源オンにともなって、プレートPL1はVcc/2に、センスアンプの信号線CSP、CSNは0およびVccに初期化される。また、信号線PCLの電位は、0からVccに立ち上がり、その結果、ビット線対BL1、BL1Bの電位はVcc/2にプリチャージされる。この時、ワード線電位は0Vを保持し蓄積ノードSN1をフローティング状態として、プレート昇圧時に高強誘電体膜の分極方向が破壊されないようにする。プレートPL1およびビット線対BL1、BL1Bの電位が確実にVcc/2の電位に安定化したら、ワード線WLを順次活性化し、蓄積ノードSN1をプレートPL1と同じVcc/2の電位として、分極情報の保持をより安定化する。以上の初期化動作に引き続き、不揮発性情報から揮発性情報への変換動作に移行する。まず、ワード線がすべて0Vの状態で、PCL1の電位を0Vにし、ビット線をフローティング状態にする。次に、ビット線を0Vにプリチャージし再びフローティング状態にする。その後、ワード線WL1を活性化すれば、蓄積ノードSN1からビット線に電流が流れ、ビット線電位が上昇する。その上昇量は高強誘電体膜の分極方向に依存する。すなわち、ビット線電位上昇後もプレート電位の方が高いので、分極方向は1方向に揃う。上記ワード線活性化により分極の反転を伴う場合の方が、反転を伴わない場合に比べて、実効的な高強誘電体キャパシタ容量が大きく、その結果、ビット線電位上昇量も大きい。この2つの分極状態に対応するビット線電位上昇量の中間値を相補ビット線BL1Bに発生するダミーセルを設け、ビット線対BL1・BL1Bの電位差をセンスアンプSA1により検知、増幅する。センスアンプの働きによりビット線電位がVcc又は0に充電される結果、蓄積ノードSN1には揮発性情報が書き込まれる。最後にワード線を非活性にした後、ビット線電位をVcc/2に戻して一連の動作を終了する。上記動作を各ワード線について順次行えば、不揮発性情報から揮発性情報への変換動作が完了する。この手順によれば、情報読み出し動作に伴う高強誘電体膜の分極の反転を、電源投入時だけにすることができるので、高強誘電体膜の劣化を少なくできる。また、通常使用時に、分極反転に要する時間に起因した読み出し速度の低下もない。しかも、電源をオフした時点での情報を記憶しており、次に電源をオンしたときにそれらの情報を復活させることができる。

【0041】

以上の実施例では、高強誘電体材料として、鉛を含む誘電体を用いて説明したが、高強誘電体膜形成温度において酸化シリコンとの反応が起こる材料の場合には、本発明の適用が有効なことはいうまでもない。とりわけビスマスを含有する材料の場合、鉛同様に激しい反応が起きるために、特に有用である。すなわち、本発明の好ましい適用誘電体材料は、鉛、ビスマスから選ばれた元素を含有する酸化物高強誘電体材料である。上記例であげたPZTの他にこれに該当する材料としては、チタン酸鉛(PbTiO3)、チタン酸ジルコニウム酸バリウム鉛((Ba、Pb)(Zr、Ti)O3)、ニオブ酸バリウム鉛((Ba、Pb)Nb2O6)、タンタル酸ストロンチウムビスマス(SrBi2Ta2O9)、チタン酸ビスマス(Bi4Ti3O12)、チタン酸ジルコニウム酸バリウムストロンチウム(Ba、Sr)(Zr、Ti)O3である。これらを基本構造として持つ誘電体について、すべて本発明は適用できる。すなわち、(A1A2..)(B1B2..)Ox (A1= Pb、Bi; A2=Ca、Sr、Cd、Ba、La、Tl、Na、K; B1、B2..=Ta、Ti、Zr、Hf、Fe、Nb、Sn、U、Al、Mn、W、Yb、Sc、In、Sb、Co、Zn、Li、Mo、Ni )の形で記述される酸化物であればよい。また、これを主成分とする材料に他の元素を混合した場合も本発明に包含される。

【0042】

反応防止層としては、上記実施例では二酸化チタン膜を用いたが、上記B1、B2として挙げた元素、即ち、Ta、Ti、Zr、Hf、Fe、Nb、Sn、U、Al、Mn、W、Yb、Sc、In、Sb、Co、Zn、Li、Mo、Niから選ばれた元素の酸化物を主成分とする膜が有効である。特に、酸化チタン、アルミナ、または、ビスマスシリケイトが効果的である。

【0043】

電極材料は、上記実施例では白金を用いたが、Ru、Ir、Pd、Ni、Ptから選ばれた金属を主成分とする金属および合金、または、V、Cr、Fe、Ru、In、Sn、Re、Ir、Pb、Cu、Pdから選ばれた元素の酸化物を主成分とする酸化物でも実施可能である。

【0044】

また、拡散防止用導電層にTi、Ta、TiN、AlxTi1-xN、 WNの内から選択した一材料、または、複数材料を積層して用いてもよい。

【0045】

反応防止層形成プロセスとしては、実施例中では、スパッタ法と金属薄膜の熱酸化を示したが、酸素含有雰囲気での反応性スパッタリングの他、CVD法、ゾルゲル塗布法による薄膜も適用可能である。

【0046】

【発明の効果】

本発明により、鉛を含む誘電体をキャパシタ絶縁膜として用いても、層間絶縁膜や拡散防止層と反応を抑制できるので、高集積の半導体記憶装置が実現できる。

【図面の簡単な説明】

【図1】参考例1の半導体装置の断面図である。

【図2】参考例1を用いたメモリセルの製造工程を示す第1の断面図である。

【図3】参考例1の工程を示す第2の断面図である。

【図4】参考例1の工程を示す第3の断面図である。

【図5】参考例1の工程を示す第4の断面図である。

【図6】参考例1の工程を示す第5の断面図である。

【図7】参考例1の工程を示す第6の断面図である。

【図8】参考例2の半導体装置の断面図である。

【図9】参考例2のメモリセルの製造工程を示す第1の断面図である。

【図10】参考例2の工程を示す第2の断面図である。

【図11】参考例2の工程を示す第3の断面図である。

【図12】本発明のメモリセルアレイ部とそれに隣接する周辺回路の各一部の要部断面である。

【図13】本発明のメモリセルと周辺回路の各一部の平面図である。

【図14】本発明のメモリセルと周辺回路の各一部を示す回路図である。

【図15】本発明を用いた実施例1のメモリセルの製造工程を示す第1の断面図である。

【図16】本発明を用いた実施例1のメモリセルの製造工程を示す第2の断面図である。

【図17】本発明を用いた実施例1のメモリセルの製造工程を示す第3の断面図である。

【図18】本発明を用いた実施例1のメモリセルの製造工程を示す第4の断面図である。

【図19】本発明を用いた実施例1のメモリセルの製造工程を示す第5の断面図である。

【図20】本発明を用いた実施例1のメモリセルの製造工程を示す第6の断面図である。

【図21】本発明の実施例1の半導体装置の断面図である。

【図22】従来技術による半導体装置の断面図である。

【図23】従来技術による半導体装置の断面図である。

【図24】従来技術による半導体装置の断面図である。

【図25】従来技術による半導体装置の断面図である。

【図26】従来技術による半導体装置の断面図である。

Claims (1)

- トランジスタを有する基板上に、絶縁膜を形成し前記トランジスタの不純物領域に接続するような開口部を前記絶縁膜に形成する工程と、

前記開口部に拡散防止膜を充填する工程と、

前記絶縁膜上と前記拡散防止膜上にTi膜と前記Ti膜上に容量の下部電極材料を堆積する工程と、

前記Ti膜と下部電極材料をパターニングして前記拡散防止膜に接続する前記Ti膜と下部電極を形成する工程と、

前記基板表面を酸化雰囲気で熱処理することにより、下部電極とTiを反応させ合金化するとともに、下部電極以外の露出しているTi膜をTi酸化膜にする工程と、

前記下部電極上およびTi酸化膜上に鉛、バリウム、ビスマスの少なくとも一つの元素を含有する高強誘電体膜を形成する工程と、

前記高強誘電体膜上に、第2の電極を形成する工程とを有することを特徴とする半導体装置の製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP25628798A JP3931445B2 (ja) | 1998-09-10 | 1998-09-10 | 半導体装置の製造方法 |

| TW088113639A TW447114B (en) | 1998-09-10 | 1999-08-10 | Semiconductor device and the manufacturing method thereof |

| KR1019990037619A KR100709130B1 (ko) | 1998-09-10 | 1999-09-06 | 반도체 장치 및 그 제조방법 |

| US09/391,250 US6822276B1 (en) | 1998-09-10 | 1999-09-07 | Memory structure with a ferroelectric capacitor |

| US10/968,077 US20050074936A1 (en) | 1998-09-10 | 2004-10-20 | Method of fabricating a semiconductor device including a reaction barrier film, a diffusion barrier film and a ferroelectric film |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP25628798A JP3931445B2 (ja) | 1998-09-10 | 1998-09-10 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000091509A JP2000091509A (ja) | 2000-03-31 |

| JP2000091509A5 JP2000091509A5 (ja) | 2004-10-21 |

| JP3931445B2 true JP3931445B2 (ja) | 2007-06-13 |

Family

ID=17290566

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP25628798A Expired - Fee Related JP3931445B2 (ja) | 1998-09-10 | 1998-09-10 | 半導体装置の製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US6822276B1 (ja) |

| JP (1) | JP3931445B2 (ja) |

| KR (1) | KR100709130B1 (ja) |

| TW (1) | TW447114B (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100428790B1 (ko) * | 2001-06-26 | 2004-04-28 | 삼성전자주식회사 | 확장된 플레이트 라인을 갖는 강유전체 메모리소자 및 그제조방법 |

| US6734477B2 (en) * | 2001-08-08 | 2004-05-11 | Agilent Technologies, Inc. | Fabricating an embedded ferroelectric memory cell |

| KR100450669B1 (ko) * | 2002-01-30 | 2004-10-01 | 삼성전자주식회사 | 산소 침투 경로 및 캡슐화 장벽막을 구비하는 강유전체메모리 소자 및 그 제조 방법 |

| KR100604871B1 (ko) * | 2004-06-17 | 2006-07-31 | 삼성전자주식회사 | 상보형 불휘발성 메모리 소자와 그 동작 방법과 그 제조 방법과 그를 포함하는 논리소자 및 반도체 장치 |

| JP4798979B2 (ja) * | 2004-09-28 | 2011-10-19 | Okiセミコンダクタ株式会社 | 強誘電体メモリの製造方法 |

| EP1758153A2 (en) * | 2005-08-24 | 2007-02-28 | Tokyo Electron Limited | Perovskite type capacitor and method of manufacturing the same |

| US7960774B2 (en) | 2005-12-05 | 2011-06-14 | Electronics And Telecommunications Research Institute | Memory devices including dielectric thin film and method of manufacturing the same |

| JP6540791B2 (ja) * | 2015-02-27 | 2019-07-10 | 株式会社村田製作所 | 可変容量素子 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02288368A (ja) | 1989-04-28 | 1990-11-28 | Seiko Epson Corp | 半導体装置の製造方法 |

| JP2898686B2 (ja) | 1990-03-06 | 1999-06-02 | 株式会社日立製作所 | 半導体記憶装置およびその製造方法 |

| JPH0590606A (ja) | 1991-09-25 | 1993-04-09 | Seiko Epson Corp | 半導体装置 |

| US5478772A (en) * | 1993-04-02 | 1995-12-26 | Micron Technology, Inc. | Method for forming a storage cell capacitor compatible with high dielectric constant materials |

| JPH0714993A (ja) * | 1993-06-18 | 1995-01-17 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP3256358B2 (ja) | 1993-12-17 | 2002-02-12 | 三井化学株式会社 | 高屈折率プラスチックレンズ用組成物およびレンズ |

| US5416042A (en) * | 1994-06-09 | 1995-05-16 | International Business Machines Corporation | Method of fabricating storage capacitors using high dielectric constant materials |

| JP3623834B2 (ja) * | 1995-01-31 | 2005-02-23 | 富士通株式会社 | 半導体記憶装置及びその製造方法 |

| JP3373525B2 (ja) * | 1995-06-28 | 2003-02-04 | テルコーディア テクノロジーズ インコーポレイテッド | シリコン上に集積された多層強誘電体セルおよびペロブスカイト電子へテロ構造 |

| JP3388089B2 (ja) * | 1996-04-25 | 2003-03-17 | シャープ株式会社 | 不揮発性半導体メモリ素子の製造方法 |

| US6043529A (en) * | 1996-09-30 | 2000-03-28 | Siemens Aktiengesellschaft | Semiconductor configuration with a protected barrier for a stacked cell |

| DE19640246A1 (de) * | 1996-09-30 | 1998-04-02 | Siemens Ag | Halbleiteranordnung mit geschützter Barriere für eine Stapelzelle |

| US6693318B1 (en) * | 1997-12-18 | 2004-02-17 | Infineon Technologies North America | Reduced diffusion of a mobile specie from a metal oxide ceramic |

| JP2000133633A (ja) * | 1998-09-09 | 2000-05-12 | Texas Instr Inc <Ti> | ハ―ドマスクおよびプラズマ活性化エッチャントを使用した材料のエッチング方法 |

| KR100343287B1 (ko) * | 1999-09-21 | 2002-07-15 | 윤종용 | 고집적 강유전체 메모리 소자의 형성 방법 |

| KR100560803B1 (ko) * | 2004-02-04 | 2006-03-13 | 삼성전자주식회사 | 캐패시터를 갖는 반도체 소자 및 그 제조방법 |

-

1998

- 1998-09-10 JP JP25628798A patent/JP3931445B2/ja not_active Expired - Fee Related

-

1999

- 1999-08-10 TW TW088113639A patent/TW447114B/zh not_active IP Right Cessation

- 1999-09-06 KR KR1019990037619A patent/KR100709130B1/ko not_active IP Right Cessation

- 1999-09-07 US US09/391,250 patent/US6822276B1/en not_active Expired - Fee Related

-

2004

- 2004-10-20 US US10/968,077 patent/US20050074936A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| KR100709130B1 (ko) | 2007-04-18 |

| US6822276B1 (en) | 2004-11-23 |

| JP2000091509A (ja) | 2000-03-31 |

| KR20000022925A (ko) | 2000-04-25 |

| US20050074936A1 (en) | 2005-04-07 |

| TW447114B (en) | 2001-07-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5350705A (en) | Ferroelectric memory cell arrangement having a split capacitor plate structure | |

| US5638319A (en) | Non-volatile random access memory and fabrication method thereof | |

| KR100406536B1 (ko) | 산소확산방지막으로서 알루미늄 산화막을 구비하는강유전체 메모리 소자 및 그 제조 방법 | |

| US5990507A (en) | Semiconductor device having ferroelectric capacitor structures | |

| US5905278A (en) | Semiconductor device having a dielectric film and a fabrication process thereof | |

| US6303958B1 (en) | Semiconductor integrated circuit and method for manufacturing the same | |

| JP3724373B2 (ja) | 半導体装置の製造方法 | |

| US5990513A (en) | Yield enhancement technique for integrated circuit processing to reduce effects of undesired dielectric moisture retention and subsequent hydrogen out-diffusion | |

| US6462368B2 (en) | Ferroelectric capacitor with a self-aligned diffusion barrier | |

| JPH10275897A (ja) | 半導体装置の製造方法および半導体装置 | |

| US6750093B2 (en) | Semiconductor integrated circuit and method for manufacturing the same | |

| JP3931445B2 (ja) | 半導体装置の製造方法 | |

| US6724026B2 (en) | Memory architecture with memory cell groups | |

| US20040232457A1 (en) | Memory architecture with series grouped by cells | |

| JP4296375B2 (ja) | 強誘電体メモリ素子の製造方法および強誘電体メモリ装置 | |

| US6720598B1 (en) | Series memory architecture | |

| US6391660B2 (en) | Method for fabricating semiconductor memory device having ferroelectric layer | |

| JP3627814B2 (ja) | 集積回路用コンデンサの構造およびその製造方法 | |

| JPH10178155A (ja) | 半導体メモリセル及びその作製方法、並びに周辺回路用トランジスタ素子及びその作製方法 | |

| JP2004311470A (ja) | 半導体装置の構造およびその製造方法 | |

| JPH10289985A (ja) | キャパシタを有する半導体装置の製造方法 | |

| JP2003282838A (ja) | 強誘電体キャパシタおよびその製造方法、メモリセルアレイ、誘電体キャパシタの製造方法、ならびに、メモリ装置 | |

| JPH10178156A (ja) | 半導体メモリセル及びその作製方法、並びにダミーセル及びその作製方法 | |

| JP4282842B2 (ja) | 半導体装置の製造方法 | |

| JPH10256495A (ja) | 不揮発性半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040727 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040803 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040930 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050104 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050307 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20060417 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20060509 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060614 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20060725 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061003 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061204 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070220 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070305 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110323 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110323 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110323 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110323 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110323 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110323 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120323 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130323 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130323 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140323 Year of fee payment: 7 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |