JP3883854B2 - 表示装置、コンピュータ、ナビゲーションシステム、ゲーム機器、及び携帯情報端末 - Google Patents

表示装置、コンピュータ、ナビゲーションシステム、ゲーム機器、及び携帯情報端末 Download PDFInfo

- Publication number

- JP3883854B2 JP3883854B2 JP2001365324A JP2001365324A JP3883854B2 JP 3883854 B2 JP3883854 B2 JP 3883854B2 JP 2001365324 A JP2001365324 A JP 2001365324A JP 2001365324 A JP2001365324 A JP 2001365324A JP 3883854 B2 JP3883854 B2 JP 3883854B2

- Authority

- JP

- Japan

- Prior art keywords

- display

- sensor

- display device

- light emitting

- emitting element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000003287 optical effect Effects 0.000 claims description 38

- 150000002894 organic compounds Chemical class 0.000 claims description 35

- 239000000758 substrate Substances 0.000 claims description 23

- 239000011368 organic material Substances 0.000 claims description 15

- 239000011521 glass Substances 0.000 claims description 11

- 229910021417 amorphous silicon Inorganic materials 0.000 claims description 9

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 claims description 6

- 150000001875 compounds Chemical class 0.000 claims description 6

- 229910003437 indium oxide Inorganic materials 0.000 claims description 6

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 claims description 6

- 229920003227 poly(N-vinyl carbazole) Polymers 0.000 claims description 5

- 229920000553 poly(phenylenevinylene) Polymers 0.000 claims description 4

- -1 polyphenylene vinylene Polymers 0.000 claims description 4

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 claims description 3

- 229910001887 tin oxide Inorganic materials 0.000 claims description 3

- 239000011787 zinc oxide Substances 0.000 claims description 3

- 229920000642 polymer Polymers 0.000 claims description 2

- 229910000679 solder Inorganic materials 0.000 claims description 2

- 229910052782 aluminium Inorganic materials 0.000 claims 1

- 229920000515 polycarbonate Polymers 0.000 claims 1

- 239000004417 polycarbonate Substances 0.000 claims 1

- 239000000126 substance Substances 0.000 claims 1

- ODHXBMXNKOYIBV-UHFFFAOYSA-N triphenylamine Chemical class C1=CC=CC=C1N(C=1C=CC=CC=1)C1=CC=CC=C1 ODHXBMXNKOYIBV-UHFFFAOYSA-N 0.000 claims 1

- 239000010410 layer Substances 0.000 description 79

- 239000010408 film Substances 0.000 description 37

- 238000000034 method Methods 0.000 description 34

- 239000003990 capacitor Substances 0.000 description 18

- 238000010586 diagram Methods 0.000 description 18

- 238000006243 chemical reaction Methods 0.000 description 14

- 230000006866 deterioration Effects 0.000 description 13

- 238000002347 injection Methods 0.000 description 13

- 239000007924 injection Substances 0.000 description 13

- 239000003086 colorant Substances 0.000 description 10

- 239000000463 material Substances 0.000 description 8

- 230000003071 parasitic effect Effects 0.000 description 6

- 238000005401 electroluminescence Methods 0.000 description 5

- 230000007423 decrease Effects 0.000 description 4

- 230000005525 hole transport Effects 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 238000002161 passivation Methods 0.000 description 4

- 238000005070 sampling Methods 0.000 description 4

- 230000006870 function Effects 0.000 description 3

- 230000005283 ground state Effects 0.000 description 3

- 239000002861 polymer material Substances 0.000 description 3

- 229910000838 Al alloy Inorganic materials 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000001514 detection method Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 229920000767 polyaniline Polymers 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- POILWHVDKZOXJZ-ARJAWSKDSA-M (z)-4-oxopent-2-en-2-olate Chemical compound C\C([O-])=C\C(C)=O POILWHVDKZOXJZ-ARJAWSKDSA-M 0.000 description 1

- 229910001316 Ag alloy Inorganic materials 0.000 description 1

- 229910000881 Cu alloy Inorganic materials 0.000 description 1

- MKYBYDHXWVHEJW-UHFFFAOYSA-N N-[1-oxo-1-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)propan-2-yl]-2-[[3-(trifluoromethoxy)phenyl]methylamino]pyrimidine-5-carboxamide Chemical compound O=C(C(C)NC(=O)C=1C=NC(=NC=1)NCC1=CC(=CC=C1)OC(F)(F)F)N1CC2=C(CC1)NN=N2 MKYBYDHXWVHEJW-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 1

- ZLMJMSJWJFRBEC-UHFFFAOYSA-N Potassium Chemical compound [K] ZLMJMSJWJFRBEC-UHFFFAOYSA-N 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000010406 cathode material Substances 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 229920000547 conjugated polymer Polymers 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 239000007772 electrode material Substances 0.000 description 1

- 125000005678 ethenylene group Chemical group [H]C([*:1])=C([H])[*:2] 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920002098 polyfluorene Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 229910052700 potassium Inorganic materials 0.000 description 1

- 239000011591 potassium Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

Images

Description

【発明の属する技術分野】

本発明は、発光素子を配列して画像表示部が形成された表示装置に関する。特に本発明は、有機エレクトロルミネセンス材料を用いて形成された発光素子が備えられた表示装置に関する。

【0002】

【従来の技術】

発光素子は、蛍光又は燐光が得られる有機化合物を含む薄膜(有機化合物層)を、陽極と陰極から成る一対の電極間に挟んだ構造をもって形成されている。その発光機構は、陰極から注入された電子と、陽極から注入された正孔が発光性物質を含む発光層で再結合して分子励起子を形成し、その分子励起子が基底状態に戻る時に光を放出する現象として捉えられている。発光輝度は10V以下の印加電圧であっても数千〜数万cd/m2を得ることができ、有機化合物材料やそのドーパントを適宜選択することにより青色から赤色までの発光が可能である。従って、原理的には表示装置などへの応用が十分可能であると考えられている。

【0003】

この種の表示装置として、薄膜トランジスタ(以下、TFTという)を用いて発光素子を駆動する方式が考えられている。これは、アクティブマトリクス駆動方式と呼ばれ、TFTにより個々の画素に設けられた発光素子を制御している。特に、多結晶シリコン膜を用いたTFTは、アモルファスシリコン膜を用いたTFTよりも電界効果移動度が高いので高速動作が可能となっている。そのため、TAB方式やCOG方式により実装されていた駆動回路を画素と同一の基板上に作り込むことが可能となっている。

【0004】

【発明が解決しようとする課題】

しかしながら、発光素子を用いた表示装置は、発光素子の劣化により、発光輝度が低下するという問題点を有していた。これは、発光素子の構成部材である有機化合物層又は有機化合物材料や陰極材料が、水分、酸素、光、熱により劣化するものと考えられている。劣化のモードは一様でなく、表示装置の構造や作製条件、さらに動作環境によって変わるので、その防止策を図るのは困難な状況にある。

【0005】

表示装置として捉えられるこの劣化は、表示される画像が暗くなり、不鮮明になることで視認することができる。

【0006】

表示装置には大きく分けて四つのカラー化表示方式があり、R(赤)G(緑)B(青)に対応した三種類の発光素子を形成する方式、白色発光の発光素子とカラーフィルターを組み合わせた方式、青色又は青緑発光の発光素子と蛍光体(蛍光性の色変換層:CCM)とを組み合わせた方式、陰極(対向電極)に透明電極を使用してRGBに対応した発光素子を重ねる方式(RGBスタッキング法)がある。

【0007】

有機化合物層を構成する有機材料は、有機化合物層の発光する色によって異なる。そのため、R(赤)G(緑)B(青)に対応した三種類の発光素子を用いたカラー化表示方式において、RGBに対応した三種類の発光素子が有する有機化合物層は、それぞれ異なる速度で劣化することがある。この場合、時間が経つにつれRGBに対応した発光素子の輝度がそれぞれ異なってしまい、表示装置に所望の色を有する画像を表示することができなくなる。

【0008】

本発明は、このような問題点を鑑みなされたものであり、発光素子が劣化しても、表示装置における輝度の低下を抑え、鮮明で所望のカラー表示を行うことが可能な表示装置を提供することを目的とする。

【0009】

【課題を解決するための手段】

上記問題点を解決するために、本発明の表示装置は、発光素子を配列して画像表示部における輝度を検知して、所定の値に補正するためのセンサ部を有する。センサ部は画像表示部に設けられる画素と同じ構成のセンサ用画素と、その画素の輝度を検知するフォトセンサから成っている。

【0010】

センサ用画素に設けられる発光素子(以下、センサ用発光素子と呼ぶ)は、表示部の画素(表示用画素)が有する発光素子(以下、表示用発光素子と呼ぶ)と同じ構成を有し、同じ工程により作製されるものである。

【0011】

そして任意に選ばれた表示用発光素子に入力される信号と同じ信号が、センサ用発光素子に入力される。なお、ここで言う入力という動作は、発光素子の有する電極の一つに該信号の電位が与えられ、発光素子の有する電極の一つに与えられた該信号の電位ともう一つの電極に与えられている一定の電位との電位差である発光素子駆動電圧が有機化合物層に加えられることを示している。

【0012】

よってセンサ用発光素子と、任意に選ばれた表示用発光素子とでは、有機化合物層に加えられている電圧がほぼ同じとなり、そのため有機化合物層の劣化する速度をほぼ等しくすることができる。よってセンサ用発光素子の輝度と表示用発光素子の輝度とは、時間を経てもほぼ等しい状態を保ち、より正確な補正を可能としている。

【0013】

一方センサ用発光素子が発する光は、センサ部に設けられた光センサによって検知する。光センサにより、センサ用発光素子の輝度の情報を電気信号に変換し、表示装置に設けられた補正回路によって表示用発光素子の輝度が補正される。この時同時にセンサ用発光素子の輝度も補正する。

【0014】

適用される光センサは特に限定されないが、フォトダイオード又はフォトトランジスタなど光電効果を利用した固体素子が適用される。

【0015】

本発明は上記構成によって、表示装置において発光素子が劣化しても、画像表示部の輝度の低下を抑え、鮮明な画像表示を長期間にわたって実現することができる。

【0016】

本発明の表示装置は、白色発光の表示用発光素子を用いたカラー表示方式、又はRGBのそれぞれの色に対応する表示用発光素子を用いたカラー表示方式のどちらにも対応することができる。RGBのそれぞれの色に対応する表示用発光素子を用いたカラー表示方式の場合、RGBのそれぞれの色に対応するセンサ用画素をセンサ部に設けることが好ましい。しかし本発明はこの構成に限定されず、RGBのうちの1つ又は2つの色に対応するセンサ用画素をセンサ部に設けても良い。特に有機化合物層の劣化が著しい色に対応するセンサ用画素をセンサ部に設けることは、所望の色を有する画像を表示するのに有効である。

【0017】

また、表示用発光素子とセンサ用発光素子とは、同じ条件で同時に形成することが好ましい。上記構成によって、表示用発光素子とセンサ用発光素子との劣化する速度を同じにすることができ、輝度の補正をより正確に且つ精密に行うことができる。したがって、光センサが検知するセンサ用発光素子の輝度が、表示用発光素子の輝度により等しくなり、表示用発光素子の輝度の変化をより正確に検知し、表示用発光素子の輝度を所望の値に補正することが可能になる。

【0018】

なお、表示部の一部をセンサ部として用いることも可能である。つまり、表示部が有する画素のうち、任意に選択された1つ又は複数の画素をセンサ用画素とし、他の画素を表示用画素とすることも可能である。この場合、センサ部が表示部に含まれない場合に比べて、センサ部を設けるスペースを省くことができるので、表示装置の小型軽量化に寄与することができる。

【0019】

なお、発光素子の構成に限定はなく、代表的には、陽極及び陰極と区別される一対の電極間に有機化合物層が設けられた構造が適用される。有機化合物層の構成は、正孔輸送層/発光層/電子輸送層、電極上に正孔注入層/正孔輸送層/発光層/電子輸送層、または正孔注入層/正孔輸送層/発光層/電子輸送層/電子注入層など様々な形態が適用される。即ち、一対の電極間に設けられる全ての層を総称して有機化合物層と呼ぶ。よって上述した正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等は、全て有機化合物層に含まれる。

【0020】

このような発光素子における発光は広義の意味におけるエレクトロルミネッセンス(Electro Luminescence)を含み、一重項励起状態から基底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)とを含んでいる。

【0021】

また、本発明でいう表示装置とは、表示用パネル及び表示用モジュールを総称していう。表示パネルは基板上に形成された発光素子を、該基板とカバー材の間に封入したものであり、該表示用パネルにICを実装したものを表示用モジュールとする。

【0022】

【発明の実施の形態】

以下、本発明の実施の態様について、図面を参照しながら説明を行う。

【0023】

図1に、本発明の表示装置に含まれる表示装置の上面図を示す。なお本実施の形態では、デジタル方式で駆動するカラー表示用の表示装置について説明する。しかし、本発明の表示装置の駆動方法はデジタル方式に限定されることはなく、アナログ方式で駆動することも可能である。また本実施の形態では、カラー表示の表示装置について説明するが、本発明の表示装置はカラー表示だけではなく、モノクロ表示を行うことも可能である。

【0024】

表示部101、ソース信号線駆動回路102、ゲート信号線駆動回路103、センサ部106が図1に示すように設けられている。ソース信号線駆動回路102はシフトレジスタ102a、ラッチ(A)102b、ラッチ(B)102cを有している。

【0025】

センサ部106は、RGBにそれぞれ対応したセンサ用画素104(Rセンサ用画素104a、Gセンサ用画素104b、Bセンサ用画素104c)を有している。なお本実施の形態では、RGBに対応した三種類の発光素子を用いたカラー化表示方式の表示装置について示しているが、本発明はこれに限定されない。白色発光の発光素子を用いたカラー化表示方式を用いることも可能である。また本実施の形態では、センサ部106がRGBにそれぞれ対応した3つのセンサ用画素を有しているが、本発明はこれに限定されない。RGBのうち、1つ又は2つの色に対応するセンサ用画素のみを設けるようにしても良い。

【0026】

表示部101及びセンサ部106の詳しい回路図を図2に示す。表示部101はソース信号線(S1〜Sx)、電源供給線(V1〜Vx)、ゲート信号線(G1〜Gy)が設けられている。

【0027】

表示部101は複数の表示用画素105を有している。表示用画素105は、ソース信号線(S1〜Sx)のいずれか1つと、電源供給線(V1〜Vx)のいずれか1つと、ゲート信号線(G1〜Gy)のいずれか1つとを有している。そして表示用画素105は、Rの表示を行う表示用画素と、Gの表示を行う表示用画素と、Bの表示を行う表示用画素とがある。

【0028】

Rの表示を行う表示用画素のうち、任意に選ばれた表示用画素(p、q)はソース信号線Sp(pは1〜xの任意の数)、電源供給線Vp、ゲート信号線Gq(qは1〜yの任意の数)を含んでいる。そしてRセンサ用画素104aは、Rの表示を行う表示用画素(p、q)と同じく、ソース信号線Sp、電源供給線Vp、ゲート信号線Gqを含んでいる。

【0029】

また図示しないが、Gセンサ用画素104bも同様に、任意に選ばれたGの表示を行う表示用画素が含んでいるのと同じソース信号線、電源供給線、ゲート信号線を含んでいる。そして同じく図示しないが、Bセンサ用画素104cも同様に、任意に選ばれたBの表示を行う表示用画素が含んでいるのと同じソース信号線、電源供給線、ゲート信号線を含んでいる。

【0030】

図3にセンサ用画素104a〜104cの詳しい構成を示す。点線で囲まれた領域がセンサ用画素104である。センサ用画素104はソース信号線S(S1〜Sxのいずれか1つ)、電源供給線V(V1〜Vxのいずれか1つ)、ゲート信号線G(G1〜Gyのいずれか1つ)を含んでいる。

【0031】

またセンサ用画素104(104a〜c)はスイッチング用TFT130、電流制御用TFT131、センサ用発光素子132を有している。また図3ではコンデンサ133を有しているが、コンデンサ133を設けない構成にしても良い。

【0032】

センサ用発光素子132は陽極と陰極と、陽極と陰極との間に設けられた有機化合物層とからなる。陽極が電流制御用TFT131のドレイン領域と接続している場合、言い換えると陽極が画素電極の場合、対向電極である陰極は所定の電位(対向電位)に保たれる。逆に陰極が電流制御用TFT131のドレイン領域と接続している場合、言い換えると陰極が画素電極の場合、対向電極である陽極は所定の電位(対向電位)に保たれる。後述する表示用画素との違いはセンシングに必要なだけの光量を出すだけの大きさを備えていることである。

【0033】

スイッチング用TFT130のゲート電極はゲート信号線Gに接続されている。そしてスイッチング用TFT130のソース領域とドレイン領域は、一方がソース信号線Sに、もう一方が電流制御用TFT131のゲート電極に接続されている。

【0034】

電流制御用TFT131のソース領域とドレイン領域は、一方が電源供給線Vに、もう一方がセンサ用発光素子132に接続されている。コンデンサ133は電流制御用TFT131のゲート電極と電源供給線Vとに接続して設けられている。

【0035】

図4に表示用画素105の詳しい構成を示す。点線で囲まれた領域が表示用画素105である。表示用画素105はソース信号線S(S1〜Sxのいずれか1つ)、電源供給線V(V1〜Vxのいずれか1つ)、ゲート信号線G(G1〜Gyのいずれか1つ)を含んでいる。

【0036】

また表示用画素105はセンサ用画素104と同様に、スイッチング用TFT140、電流制御用TFT141、表示用発光素子142を有している。表示用発光素子142は図3で示したセンサ用発光素子132と同じ構成を有している。具体的には、表示用発光素子142とセンサ用発光素子132とは、一対の電極間に有機化合物層をそれぞれ有しており、一対の電極を構成している材料、有機化合物層の積層構造が、少なくともそれぞれ同じである。特にセンサ用発光素子132と表示用発光素子142の発する光の色が同じ場合、該有機化合物層を構成している材料(有機材料)も同じである。

【0037】

表示用発光素子142は陽極と陰極と、陽極と陰極の間に設けられた有機化合物層とからなる。陽極が電流制御用TFT141のドレイン領域と接続している場合、言い換えると陽極が画素電極の場合、対向電極である陰極は所定の電位(対向電位)に保たれる。逆に陰極が電流制御用TFT141のドレイン領域と接続している場合、言い換えると陰極が画素電極の場合、対向電極である陽極は所定の電位(対向電位)に保たれる。

【0038】

また図4ではコンデンサ143を有しているが、コンデンサ143を設けない構成にしても良い。

【0039】

スイッチング用TFT140のゲート電極はゲート信号線Gに接続されている。そしてスイッチング用TFT140のソース領域とドレイン領域は、一方がソース信号線Sに、もう一方が電流制御用TFT141のゲート電極に接続されている。

【0040】

電流制御用TFT141のソース領域とドレイン領域は、一方が電源供給線Vに、もう一方が表示用発光素子142に接続されている。コンデンサ143は電流制御用TFT141のゲート電極と電源供給線Vとに接続して設けられている。

【0041】

次に本実施の形態の表示装置の駆動方法を図1を参照して説明する。ソース信号線駆動回路102において、シフトレジスタ102aにクロック信号(CLK)およびスタートパルス(SP)が入力される。シフトレジスタ102aは、これらのクロック信号(CLK)およびスタートパルス(SP)に基づきタイミング信号を順に発生させ、後段の回路へタイミング信号を順次供給する。

【0042】

なおシフトレジスタ102aからのタイミング信号を、バッファ等(図示せず)によって緩衝増幅し、後段の回路へ緩衝増幅したタイミング信号を順次供給しても良い。タイミング信号が供給される配線には、多くの回路あるいは素子が接続されているために負荷容量(寄生容量)が大きい。この負荷容量が大きいために生ずるタイミング信号の立ち上がりまたは立ち下がりの”鈍り”を防ぐために、このバッファが設けられる。

【0043】

シフトレジスタ102aからのタイミング信号は、ラッチ(A)102bに供給される。ラッチ(A)102bは、nビットデジタルビデオ信号(n bit digital video signals)を処理する複数のステージのラッチを有している。ラッチ(A)102bは、前記タイミング信号が入力されると同時に、画像情報を有するnビットのデジタルのビデオ信号(デジタルビデオ信号)を順次書き込み、保持する。

【0044】

ラッチ(A)102bにデジタルビデオ信号を取り込む際に、ラッチ(A)102bが有する複数のステージのラッチに、順にデジタルビデオ信号を入力しても良い。しかし本発明はこの構成に限定されない。ラッチ(A)102bが有する複数のステージのラッチをいくつかのグループに分け、各グループごとに並行して同時にデジタルビデオ信号を入力する、いわゆる分割駆動を行っても良い。なおこのときのグループの数を分割数と呼ぶ。例えば4つのステージごとにラッチをグループに分けた場合、4分割で分割駆動すると言う。

【0045】

ラッチ(A)102bの全てのステージのラッチにデジタルビデオ信号の書き込みが一通り終了するまでの時間を、ライン期間と呼ぶ。すなわち、ラッチ(A)102b中で一番左側のステージのラッチにデジタルビデオ信号の書き込みが開始される時点から、一番右側のステージのラッチにデジタルビデオ信号の書き込みが終了する時点までの時間間隔がライン期間である。実際には、上記ライン期間に水平帰線期間が加えられた期間をライン期間に含むことがある。

【0046】

1ライン期間が終了すると、ラッチ(B)102cにラッチシグナル(Latch Signal)が供給される。この瞬間、ラッチ(A)102bに書き込まれ保持されているデジタルビデオ信号は、ラッチ(B)102cに一斉に送出され、ラッチ(B)102cの全ステージのラッチに書き込まれ、保持される。

【0047】

デジタルビデオ信号をラッチ(B)102cに送出し終えたラッチ(A)102bは、シフトレジスタ102aからのタイミング信号に基づき、再びデジタルビデオ信号の書き込みを順次行う。

【0048】

この2順目の1ライン期間中には、ラッチ(B)102bに書き込まれ、保持されているデジタルビデオ信号がソース信号線に入力される。

【0049】

一方、ゲート信号線駆動回路103は、それぞれシフトレジスタ、バッファ(いずれも図示せず)を有している。また場合によっては、ゲート信号線駆動回路103が、シフトレジスタ、バッファの他にレベルシフトを有していても良い。

【0050】

ゲート信号線駆動回路103において、シフトレジスタ(図示せず)からのタイミング信号がバッファ(図示せず)に供給され、対応するゲート信号線(走査線とも呼ぶ)に供給される。ゲート信号線には、1ライン分のスイッチング用TFTのゲート電極が接続されており、1ライン分全てのスイッチング用TFTを同時にONにしなくてはならないので、バッファは大きな電流を流すことが可能なものが用いられる。

【0051】

なおソース信号線駆動回路102とゲート信号線駆動回路103の数、構成及びその駆動方法は、本実施の形態で示した構成に限定されない。

【0052】

図5に、本発明の表示装置を、デジタル方式で駆動させて表示を行った場合のタイミングチャートを示す。

【0053】

まず、1フレーム期間(F)をn個のサブフレーム期間(SF1〜SFn)に分割する。なお、画素部の全ての画素が1つの画像を表示する期間を1フレーム期間(F)と呼ぶ。

【0054】

表示装置は1秒間に60以上のフレーム期間を設けることが好ましい。1秒間に表示される画像の数を60以上にすることで、視覚的にフリッカ等の画像のちらつきを抑えることが可能になる。

【0055】

1フレーム期間をさらに複数に分割した期間をサブフレーム期間(SF)と呼ぶ。階調数が多くなるにつれて1フレーム期間におけるサブフレーム期間の数も増える。

【0056】

サブフレーム期間はアドレス期間(Ta)とサステイン期間(Ts)とに分けられる。アドレス期間とは、1サブフレーム期間中、全ての画素にデジタルビデオ信号を入力する期間である。サステイン期間(点灯期間とも呼ぶ)とは、アドレス期間において画素に入力されたデジタルビデオ信号によって、発光素子を発光又は非発光の状態にし、表示を行う期間を示している。

【0057】

SF1〜SFnが有するアドレス期間(Ta)をそれぞれTa1〜Tanとする。SF1〜SFnが有するサステイン期間(Ts)をそれぞれTs1〜Tsnとする。

【0058】

電源供給線(V1〜Vx)の電位は所定の電位(電源電位)に保たれている。

【0059】

まずアドレス期間Taにおいて、表示用発光素子142及びセンサ用発光素子132の対向電極の電位は、電源電位と同じ高さに保たれている。

【0060】

そしてゲート信号線G1にゲート信号が入力され、表示用画素105が有するスイッチング用TFT140及びセンサ用画素104が有するスイッチング用TFT130のうち、ゲート信号線G1に接続されている全てのスイッチング用TFTがON(オン)の状態になる。ここで、TFTがオンの状態になることをTFTが駆動すると呼ぶ。

【0061】

そしてゲート信号線G1に接続されている全てのスイッチング用TFTがONになった状態で、ソース信号線駆動回路102からソース信号線(S1〜Sx)にデジタルビデオ信号が入力される。デジタルビデオ信号は「0」または「1」の情報を有しており、「0」と「1」のデジタルビデオ信号は、一方がHi(High)、一方がLo(Low)の電圧を有する信号である。

【0062】

そしてソース信号線(S1〜Sx)に入力されたデジタルビデオ信号は、ONの状態のスイッチング用TFTを介して、該スイッチング用TFTのソース領域又はドレイン領域に接続された電流制御用TFTのゲート電極に入力される。

【0063】

次にゲート信号線G2にゲート信号が入力される。ゲート信号線G2に接続されているスイッチング用TFT1501全てがONの状態になる。そして表示用画素105が有するスイッチング用TFT140及びセンサ用画素104が有するスイッチング用TFT130のうち、ゲート信号線G2に接続されている全てのスイッチング用TFTをONの状態にする。

【0064】

そしてゲート信号線G2に接続されている全てのスイッチング用TFTがONにされた状態で、ソース信号線駆動回路102からソース信号線(S1〜Sx)にデジタルビデオ信号が入力される。ソース信号線(S1〜Sx)に入力されたデジタルビデオ信号は、ONの状態のスイッチング用TFTを介して、該スイッチング用TFTのソース領域又はドレイン領域に接続された電流制御用TFTのゲート電極に入力される。

【0065】

上述した動作をゲート信号線Gyまで繰り返し、全ての表示用画素105及びセンサ用画素104にデジタルビデオ信号が入力される。全ての表示用画素105及びセンサ用画素104にデジタルビデオ信号が入力されるまでの期間がアドレス期間である。なおn個のサブフレーム期間がそれぞれ有するアドレス期間(Ta1〜Tan)の長さは全て同じである。

【0066】

アドレス期間Taが終了すると同時にサステイン期間となる。サステイン期間において、全ての発光素子の対向電極の電位は、電源電位が画素電極に与えられたときに発光素子が発光する程度に、電源電位との間に電位差を有する高さになる。

【0067】

そしてサステイン期間において、表示用画素105及びセンサ用画素104が有する全てのスイッチング用TFTは、オフの状態となる。そして表示用画素105及びセンサ用画素104に入力されたデジタルビデオ信号が、各画素が有する電流制御用TFTのゲート電極に入力される。

【0068】

本実施の形態では、デジタルビデオ信号が「0」の情報を有していた場合、電流制御用TFTはオフの状態になる。よって発光素子の画素電極は対向電極の電位に保たれたままである。その結果、「0」の情報を有するデジタルビデオ信号が入力された画素において、発光素子は発光しない。

【0069】

逆に本実施の形態では、「1」の情報を有していた場合、電流制御用TFTはオンの状態になる。よって電源電位が発光素子の画素電極に与えられる。その結果、「1」の情報を有するデジタルビデオ信号が入力された画素が有する発光素子は発光する。

【0070】

このように、画素に入力されるデジタルビデオ信号の有する情報によって、発光素子が発光または非発光の状態になり、画素は表示を行う。

【0071】

サステイン期間が終了すると同時に、1つのサブフレーム期間が終了する。そして次のサブフレーム期間が出現し、再びアドレス期間に入り、全画素にデジタルビデオ信号を入力したら、再びサステイン期間に入る。なお、サブフレーム期間の出現する順序は任意である。

【0072】

以下、残りのサブフレーム期間においても同様の動作を繰り返し、表示を行う。n個のサブフレーム期間が終了したら、1フレーム期間が終了する。

【0073】

また本発明において、n個のサステイン期間Ts1、…、Tsnの長さの比は、Ts1:Ts2:Ts3:…:Ts(n−1):Tsn=20:2-1:2-2:…:2-(n-2):2-(n-1)で表される。

【0074】

各画素の階調は、1フレーム期間においてどのサブフレーム期間を選択して発光させるかによって決まる。例えば、n=8のとき、全部のサステイン期間で発光した場合の画素の輝度を100%とすると、Ts1とTs2において画素が発光した場合には75%の輝度が表現でき、Ts3とTs5とTs8を選択した場合には16%の輝度が表現できる。

【0075】

なお本実施の形態では、アドレス期間において対向電極の電位を電源電位と同じ電位に保っていたため、発光素子は発光しなかった。しかし本発明はこの構成に限定されない。画素電極に電源電位が与えられたときに発光素子が発光する程度の電位差を、対向電位と電源電位との間に常に設け、アドレス期間においても表示期間と同様に表示を行うようにしても良い。ただしこの場合、サブフレーム期間全体が実際に表示を行う期間となるので、サブフレーム期間の長さを、SF1:SF2:SF3:…:SF(n−1):SFn=20:2-1:2-2:…:2-(n-2):2-(n-1)となるように設定する。上記構成により、アドレス期間を発光させない駆動方法に比べて、高い輝度の画像が得られる。

【0076】

上述したように、表示用発光素子が発光又は非発光状態になることで画像が表示部に表示されるのと同時に、センサ用発光素子も表示用発光素子と同じく発光又は非発光状態になる。

【0077】

次にセンサ部106が有する光センサ(図示せず)136が、センサ用発光素子132の輝度を検知する仕組みについて説明する。

【0078】

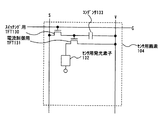

光センサとしてはアモルファスシリコンで構成されたものを用いるとよい、ただし、アモルファスシリコンだけでなく他の光センサでも本発明は実施可能である。アモルファスシリコンを用いた光センサとしては以下のようなものがある。図10にその断面構造を示す。この光センサはガラス基板上にアモルファスシリコンを成膜し、さらにNi電極を成膜し、絶縁膜を付けた後、コンタクト部分を開口し、はんだパッドをつけている。

【0079】

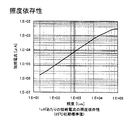

このアモルファスシリコンを用いた光センサの特性を図11に示す。このような光センサでは100cd/m 2 の発光に対して0.1μA〜1μAの電流が得られる。

【0080】

この光センサを用いた構成として図12に示すような回路を構成する(図12中、光センサを受光ダイオードと表記)。この回路は電流を電圧に変換するためオペアンプを用いている。オペアンプは電流誤差を低減するためFET入力のオペアンプを用いるのがよい。ここではオペアンプを用いているが電流検出は別の方式を用いてもかまわない。検出結果を出力配線FLに出している。これは補正回路に入力される。

【0081】

図6に補正回路201のブロック図を示す。補正回路201は表示部101又はセンサ部106と同じ基板上に設けられていても良く、またICチップ上に設けてFPC等によりセンサ部106と接続しても良い。

【0082】

補正回路201はA/D変換回路202、演算回路203、補正メモリ204、D/A変換回路205を有している。なお、図6には補正メモリ204が演算回路203の一部である場合の構成を示したが、補正メモリ204が演算回路203と別個に設けられていても良い。

【0083】

センサ出力配線FLからセンサ出力信号がA/D変換回路202に入力され、デジタルのセンサ出力信号に変換されて出力される。A/D変換回路202から出力されたデジタルのセンサ出力信号は、演算回路203に入力される。

【0084】

補正メモリ204には、センサ用発光素子132が理想の輝度を有しているときに、演算回路203に入力されるデジタルのセンサ出力信号のデータ(補正基準データ)が記憶されている。

【0085】

演算回路203は、実際に演算回路203に入力されたデジタルのセンサ出力信号と、補正メモリ204に記憶されている補正基準データとを比較する。そして比較した実際のセンサ出力信号と補正基準データとの差から、表示用発光素子142及びセンサ用発光素子132が理想の輝度を得るために必要な電源供給線Vの電位(電源電位)の高さを算出する。そして、演算回路203は、その電源電位の高さの情報を有するデジタルの補正信号をD/A変換回路205に入力する。

【0086】

D/A変換回路205に入力されたデジタルの補正信号は、アナログに変換され、発光素子用電源206に入力される。発光素子用電源206は、入力されたアナログの補正信号によって定められた高さの電源電位を、電源供給線(V1〜Vx)に与える。発光素子の輝度が低下した場合には、それを補うように電源供給線の電源電位を調整し、輝度を向上させるように補正が働く。

補正回路は以上に限らず他の方式を用いてもよい。

【0087】

なおRGBに対応する3種類の発光素子を用いた表示装置の場合、補正回路201及び発光素子用電源206は補正したい色ごとに設ける必要がある。つまりRGBそれぞれの色について補正を行う場合、補正回路201及び発光素子用電源206はそれぞれ3つづつ必要となる。

【0088】

また、発光の色が白色、青色、青緑色等の単色である発光素子を用いた表示装置の場合、補正回路201及び発光素子用電源206は1つづつ設けても良いし、補正したい色ごとに設けても良い。有機化合物層は、有機化合物層に照射する光の波長によっても劣化の速度が異なる。そのため、白色発光の発光素子とカラーフィルターとを用いた表示装置の場合、補正したい色ごとに補正回路201及び発光素子用電源206を設けることで、より正確に各色に対応する発光素子の輝度を補正することができ、より鮮明で、なおかつ所望の色の画像を表示することができる。

【0089】

本発明は上記構成によって、表示装置において有機化合物層が劣化しても、表示用発光素子142及びセンサ用発光素子132が理想の輝度を有することができ、鮮明でなおかつ所望のカラー表示を行うことが可能になる。

【0090】

なお本実施の形態では、センサ部はRGBそれぞれの色に対応したセンサ用画素を1つづつ有していたが、本発明はこれに限定されない。各色に対応したセンサ用画素は複数存在していても良い。

【0091】

【実施例】

以下、本発明の実施例について説明する。

【0092】

(実施例1)

本実施例では、アナログ方式で駆動する本発明の表示装置について、図7〜図9を用いて説明する。

【0093】

図7に、本発明の表示装置の一部である表示装置の上面図を示す。本実施例では、カラー表示の表示装置について説明するが、本発明の表示装置はカラー表示だけではなく、モノクロ表示を行うことも可能である。

【0094】

表示部301、ソース信号線駆動回路302、ゲート信号線駆動回路303、センサ部306が図7に示すように設けられている。ソース信号線駆動回路302はシフトレジスタ302a、レベルシフト302b、サンプリング回路302cを有している。

【0095】

センサ部306は、RGBにそれぞれ対応したセンサ用画素304(Rセンサ用画素304a、Gセンサ用画素304b、Bセンサ用画素304c)を有している。なお本実施例では、RGBに対応した三種類の発光素子を用いたカラー化表示方式の表示装置について示しているが、本実施例はこれに限定されない。白色発光の発光素子を用いたカラー化表示方式を用いることも可能である。また本実施例では、センサ部306がRGBにそれぞれ対応した3つのセンサ用画素を有しているが、本発明はこれに限定されない。RGBのうち、1つ又は2つの色に対応するセンサ用画素のみを設けるようにしても良い。

【0096】

表示部301及びセンサ部306の詳しい構成は、デジタル方式で駆動する場合と同じなので図2を参照する。なお、図7の表示部301、センサ部306、Rセンサ用画素304a、Gセンサ用画素304b、Bセンサ用画素304cは、それぞれ図2の表示部101、センサ部106、Rセンサ用画素104a、Gセンサ用画素104b、Bセンサ用画素104cに相当する。

【0097】

表示部301は複数の表示用画素を有している。なお本実施例の表示用画素は、図2で示すところの表示用画素105に相当する。表示用画素は、ソース信号線(S1〜Sx)のいずれか1つと、電源供給線(V1〜Vx)のいずれか1つと、ゲート信号線(G1〜Gy)のいずれか1つとを有している。そして表示用画素は、Rの表示を行う表示用画素と、Gの表示を行う表示用画素と、Bの表示を行う表示用画素とがある。

【0098】

Rの表示を行う任意に選ばれた表示用画素(p、q)は、ソース信号線Sp(pは1〜xの任意の数)、電源供給線Vp、ゲート信号線Gq(qは1〜yの任意の数)を含んでいる。そしてRセンサ用画素304aは、表示用画素(p、q)と同じく、ソース信号線Sp、電源供給線Vp、ゲート信号線Gqを含んでいる。

【0099】

また、Gセンサ用画素304bも同様に、任意に選ばれたGの表示を行う表示用画素が含んでいるのと同じソース信号線、電源供給線、ゲート信号線を含んでいる。また、Bセンサ用画素304cも同様に、任意に選ばれたBの表示を行う表示用画素が含んでいるのと同じソース信号線、電源供給線、ゲート信号線を含んでいる。

【0100】

表示用画素とセンサ用画素304の構成は、デジタル方式で駆動する場合の図3及び図4と同じであるので、説明は実施の形態を参照する。

【0101】

次に本実施例の表示装置の駆動方法について説明する。

【0102】

図7を参照する。ソース信号線駆動回路302において、シフトレジスタ302aにクロック信号(CLK)およびスタートパルス(SP)が入力される。シフトレジスタ302aは、これらのクロック信号(CLK)およびスタートパルス(SP)に基づきタイミング信号を順に発生させ、後段の回路へタイミング信号を順次供給する。

【0103】

シフトレジスタ302aからのタイミング信号は、レベルシフト302bにおいて電圧の振幅を大きくされ、サンプリング回路302cに入力される。そしてタイミング信号に同期して、サンプリング回路302cが有するアナログスイッチによってアナログの画像情報を有する信号(アナログビデオ信号)がサンプリングされ、対応するソース信号線に入力される。

【0104】

なおソース信号線駆動回路302は、バッファを有していても良い。タイミング信号が供給される配線には、多くの回路あるいは素子が接続されているために負荷容量(寄生容量)が大きい。この負荷容量が大きいために生ずるタイミング信号の立ち上がりまたは立ち下がりの”鈍り”を防ぐためには、バッファが有効である。

【0105】

一方、ゲート信号線駆動回路303は、それぞれシフトレジスタ、バッファ(いずれも図示せず)を有している。また場合によっては、ゲート信号線駆動回路303が、シフトレジスタ、バッファの他にレベルシフトを有していても良い。

【0106】

ゲート信号線駆動回路303において、シフトレジスタ(図示せず)からのタイミング信号がバッファ(図示せず)に供給され、対応するゲート信号線(走査線とも呼ぶ)に供給される。ゲート信号線には、1ライン分のスイッチング用TFTのゲート電極が接続されており、1ライン分全てのスイッチング用TFTを同時にONにしなくてはならないので、バッファは大きな電流を流すことが可能なものが用いられる。

【0107】

なおソース信号線駆動回路302とゲート信号線駆動回路303の数、構成及びその駆動方法は、本実施例で示した構成に限定されない。

【0108】

次に本発明の表示装置をアナログ方式で駆動させた場合のタイミングチャートを図8に示す。1つのゲート信号線がゲート信号によって選択されてから、その次に別のゲート信号線が選択されるまでの期間を1ライン期間(L)と呼ぶ。また1つの画像が表示されてから次の画像が表示されるまでの期間が1フレーム期間(F)に相当する。ゲート信号線がy本ある場合、1フレーム期間中にy個のライン期間(L1〜Ly)が設けられる。

【0109】

まず電源供給線(V1〜Vx)は所定の電源電位に保たれている。そして対向電極の電位も所定の電位に保たれている。対向電極の電位は、電源電位が画素電極に与えられたとき発光素子が発光する程度に、電源電位との間に電位差を有している。

【0110】

第1のライン期間(L1)においてゲート信号線G1にはゲート信号線駆動回路303から選択信号が入力される。そして、ソース信号線(S1〜Sx)に順にサンプリングされたアナログビデオ信号が入力される。ゲート信号線G1に接続された全てのスイッチング用TFTは選択信号によってオンの状態になるので、ソース信号線に入力されたアナログビデオ信号は、スイッチング用TFTを介して電流制御用TFTのゲート電極に入力される。

【0111】

電流制御用TFTのチャネル形成領域を流れる電流の量は、そのゲート電極に入力される信号の電位の高さ(電圧)によって制御される。よって、発光素子の画素電極の電位の高さは、電流制御用TFTのゲート電極に入力されたアナログビデオ信号の電位の高さによって決まる。そして発光素子はアナログビデオ信号の電位に制御されて発光する。

【0112】

上述した動作を繰り返し、にソース信号線(S1〜Sx)へのアナログビデオ信号の入力が終了すると、第1のライン期間(L1)が終了する。なお、ソース信号線(S1〜Sx)へのアナログビデオ信号の入力が終了するまでの期間と水平帰線期間とを合わせて1つのライン期間としても良い。そして次に第2のライン期間(L2)となりゲート信号線G2に選択信号が入力される。そして第1のライン期間(L1)と同様にソース信号線(S1〜Sx)に順にアナログビデオ信号が入力される。

【0113】

そして全てのゲート信号線(G1〜Gy)に選択信号が入力されると、全てのライン期間(L1〜Ly)が終了する。全てのライン期間(L1〜Ly)が終了すると、1フレーム期間が終了する。1フレーム期間中において全ての画素が表示を行い、1つの画像が形成される。なお全てのライン期間(L1〜Ly)と垂直帰線期間とを合わせて1フレーム期間としても良い。

【0114】

以上のように、ソース信号線に入力されるアナログビデオ信号の電位によって発光素子の輝度が制御され、その輝度の制御によって階調表示がなされる。

【0115】

次に、センサ部306から出力されるセンサ出力信号によって、表示用発光素子及びセンサ用発光素子の輝度がどのように補正されるかについて、図9を用いて説明する。なお、図7に示したセンサ用画素において、光センサがセンサ用発光素子の輝度を検知し、センサ出力信号がセンサ出力配線に入力されるまでの過程は、実施の形態で示したデジタル駆動の表示装置の場合と同じなので説明は省略する。

【0116】

サンプル期間において、光センサで検知されたセンサ用発光素子の輝度の情報を有するセンサ出力信号は、センサ出力配線FLを介してビデオ信号補正回路に入力される。

【0117】

図9にビデオ信号補正回路401のブロック図を示す。ビデオ信号補正回路401は表示部301又はセンサ部306と同じ基板上に設けても良く、またICチップ上に設けてFPC等によりセンサ部306と接続していても良い。

【0118】

ビデオ信号補正回路401はA/D変換回路402、演算回路403、補正メモリ404、D/A変換回路405を有している。なお、図9には補正メモリ404が演算回路403の一部である場合の構成を示したが、補正メモリ404が演算回路403と別個に設けられていても良い。

【0119】

シグナルジェネレータ406はデジタルの画像情報を有する信号(デジタルビデオ信号)を生成し、演算回路403に入力している。なお、シグナルジェネレータ406から出力される画像情報を有する信号(ビデオ信号)がアナログだった場合、A/D変換回路によってデジタルのビデオ信号に変換してから、演算回路403に入力するようにする。

【0120】

センサ出力配線FLからセンサ出力信号がA/D変換回路402に入力され、デジタルのセンサ出力信号に変換されて出力される。A/D変換回路402から出力されたデジタルのセンサ出力信号は、演算回路403に入力される。

【0121】

補正メモリ404には、表示用発光素子及びセンサ用発光素子が理想の輝度を有しているときに、演算回路403に入力されるデジタルのセンサ出力信号のデータ(補正基準データ)が記憶されている。

【0122】

演算回路403は、実際に演算回路403に入力されたデジタルのセンサ出力信号と、補正メモリ404に記憶されている補正基準データとを比較する。そして比較した実際のセンサ出力信号と補正基準データとの差をもとに、シグナルジェネレータ406から演算回路403に入力されたデジタルビデオ信号を補正する。なおこの時、補正後のデジタルビデオ信号は、アナログに変換された際に表示用発光素子及びセンサ用発光素子が理想の輝度を得るために必要な電位を有していることが重要である。

【0123】

なお演算回路403には、各色に対応したセンサ出力信号が入力されている。例えば本実施例の場合、Rセンサ用画素304aと、Gセンサ用画素304bと、Bセンサ用画素304cとからそれぞれ出力されている3つのセンサ出力信号が、演算回路403に入力されている。演算回路403では、各色に対応する画素(表示用画素及びセンサ用画素)に所望の高さの電位を有するアナログビデオ信号がサンプリングされて入力されるように、デジタルビデオ信号を補正する。

【0124】

次に演算回路403から、補正後のデジタルビデオ信号がD/A変換回路405に入力する。D/A変換回路405に入力された補正後のデジタルビデオ信号は、アナログに変換され、アナログビデオ信号としてソース信号線駆動回路302のサンプリング回路302cに入力される。アナログビデオ信号は、表示用発光素子及びセンサ用発光素子が理想の輝度を得るために必要な電位を有している。

【0125】

本発明は上記構成によって、表示装置において有機化合物層が劣化しても、表示用発光素子及びセンサ用発光素子が理想の輝度を有することができ、鮮明で所望のカラー表示を行うことが可能になる。

【0126】

なお本実施の形態では、センサ部はRGBそれぞれの色に対応したセンサ用画素を1つづつ有していたが、本発明はこれに限定されない。各色に対応したセンサ用画素は複数存在していても良い。

【0127】

また本実施例のアナログ駆動の表示装置では、表示部に入力されるアナログビデオ信号の電位をビデオ信号補正回路において補正することで、発光素子の輝度を補正している。しかし本発明はこれに限定されない。ビデオ信号補正回路においてアナログビデオ信号の電位を補正するのに加えて、デジタル駆動の表示装置と同様に、電源電位を補正する補正回路を設けても良い。

【0128】

(実施例2)

図13はTFTで構成した表示装置と本発明の光センサを組み合わせた例である。一般にTFTを搭載した表示装置の基板の厚さは0.7mm程度である。また光センサもほぼ同じくらいのガラス基板のうえに作られるのが一般的である。その場合に合計の厚さが問題となるため、本実施例ではTFT側および光センサのガラスを削った例である。TFT基板は一部分を削り、その部分に光センサ(図中、受光ダイオードと表記)をはめ込んでいる。

【0129】

このような対策をおこなうことによって表示装置の厚さを低減することが可能となる。またこの例では端子の引き出しはTFT基板に配線を印刷し、そこにワイヤーボンディングで接続をおこなっている。ここでは図示しないが、1つのチップ上に複数の光センサを製作し、TFT基板に実装することも可能である。そのような手段を図ることによって、実装面積の縮小が可能となる。

【0130】

(実施例3)

図14は光センサの引き出しをFPC(フレキシブルプリントサーキット)でおこなったものである。図14で示すようにFPCに装着した光センサ(図中、受光ダイオードと表記)を実施例2に示したようなTFT基板のくぼみ部分に装着している。このようにFPCを使うことによって、TFT基板の配線を減らすことが可能となる。

【0131】

また、本実施例では、光センサとTFTに間にカラーフィルターをはさんでいる。このようカラーフィルターを内蔵することによって他の色の干渉を防ぐことが可能となる。

【0132】

(実施例4)

ここで表示装置における表示部のさらに詳細な断面構造を図15に、上面構造を図16(A)に、回路図を図16(B)に示す。図15、図16(A)及び図16(B)では共通の符号を用いるので互いに参照すれば良い。

【0133】

図15において、基板3501上に設けられたスイッチング用TFT3502は公知の方法で形成されたnチャネル型TFTを用いる。本実施例ではダブルゲート構造としているが、構造及び作製プロセスに大きな違いはないので説明は省略する。但し、ダブルゲート構造とすることで実質的に二つのTFTが直列に接続した構造となり、オフ電流値を低減することができるという利点がある。なお、本実施例ではダブルゲート構造としているが、シングルゲート構造でも構わないし、トリプルゲート構造やそれ以上のゲート本数を持つマルチゲート構造でも構わない。また、公知の方法で形成されたpチャネル型TFTを用いて形成しても構わない。

【0134】

また、電流制御用TFT3503は公知の方法で形成されたnチャネル型TFTを用いる。スイッチング用TFT3502のドレイン配線35は配線36によって電流制御用TFT3503のゲート電極37に電気的に接続されている。また、38で示される配線は、スイッチング用TFT3502のゲート電極39a、39bを電気的に接続するゲート配線である。

【0135】

電流制御用TFT3503は表示用発光素子を流れる電流量を制御するための素子であるため、多くの電流が流れ、熱による劣化やホットキャリアによる劣化の危険性が高い素子でもある。そのため、電流制御用TFT3503のドレイン側に、ゲート絶縁膜を介してゲート電極に重なるようにLDD領域を設け、熱による劣化やホットキャリアによる劣化を防ぐ構造にしても良い。

【0136】

また、本実施例では電流制御用TFT3503をシングルゲート構造で図示しているが、複数のTFTを直列につなげたマルチゲート構造としても良い。さらに、複数のTFTを並列につなげて実質的にチャネル形成領域を複数に分割し、熱の放射を高い効率で行えるようにした構造としても良い。このような構造は熱による劣化対策として有効である。

【0137】

また、図16(A)に示すように、電流制御用TFT3503のゲート電極37を含む配線36は3504で示される領域で、電流制御用TFT3503のドレイン配線40と絶縁膜を介して重なる。このとき、3504で示される領域では保持容量(コンデンサ)が形成される。保持容量3504は、電源供給線3506と電気的に接続された半導体膜3520、ゲート絶縁膜と同一層の絶縁膜(図示せず)及び配線36との間で形成される。また、配線36、第1層間絶縁膜と同一の層(図示せず)及び電源供給線3506で形成される容量も保持容量として用いることが可能である。この保持容量3504は電流制御用TFT3503のゲート電極37にかかる電圧を保持するためのコンデンサとして機能する。なお、電流制御用TFT3503のドレインは電源供給線(電源線)3506に接続され、常に一定の電圧が加えられている。

【0138】

スイッチング用TFT3502及び電流制御用TFT3503の上には第1パッシベーション膜41が設けられ、その上に樹脂絶縁膜でなる平坦化膜42が形成される。平坦化膜42を用いてTFTによる段差を平坦化することは非常に重要である。後に形成される有機化合物層は非常に薄いため、段差が存在することによって発光不良を起こす場合がある。従って、有機化合物層をできるだけ平坦面に形成しうるように画素電極を形成する前に平坦化しておくことが望ましい。

【0139】

また、43は反射性の高い導電膜でなる画素電極(表示用発光素子の陰極)であり、電流制御用TFT3503のドレイン領域に電気的に接続される。画素電極43としてはアルミニウム合金膜、銅合金膜または銀合金膜など低抵抗な導電膜またはそれらの積層膜を用いることが好ましい。勿論、他の導電膜との積層構造としても良い。

【0140】

また、絶縁膜(好ましくは樹脂)で形成されたバンク44a、44bにより形成された溝(画素に相当する)の中に発光層45が形成される。なお図16(A)では、保持容量3504の位置を明確にするために一部バンクを省略しており、バンク44a、44bしか図示していないが、電源供給線3506とソース配線34を一部覆うように、画素間に設けられている。また、ここでは二画素しか図示していないが、R(赤)、G(緑)、B(青)の各色に対応した発光層を作り分けても良い。発光層とする有機材料としてはπ共役ポリマー系材料を用いる。代表的なポリマー系材料としては、ポリパラフェニレンビニレン(PPV)系、ポリビニルカルバゾール(PVK)系、ポリフルオレン系などが挙げられる。

【0141】

なお、PPV系有機材料としては様々な型のものがあるが、例えば「H. Shenk,H.Becker,O.Gelsen,E.Kluge,W.Kreuder,and H.Spreitzer,“Polymers for Light Emitting Diodes”,Euro Display,Proceedings,1999,p.33-37」や特開平10−92576号公報に記載されたような材料を用いれば良い。

【0142】

具体的な発光層としては、赤色に発光する発光層にはシアノポリフェニレンビニレン、緑色に発光する発光層にはポリフェニレンビニレン、青色に発光する発光層にはポリフェニレンビニレン若しくはポリアルキルフェニレンを用いれば良い。膜厚は30〜150nm(好ましくは40〜100nm)とすれば良い。

【0143】

但し、以上の例は発光層として用いることのできる有機材料の一例であって、これに限定する必要はまったくない。発光層、電荷輸送層または電荷注入層を自由に組み合わせて有機化合物層(発光及びそのためのキャリアの移動を行わせるための層)を形成すれば良い。

【0144】

例えば、本実施例ではポリマー系材料を発光層として用いる例を示したが、低分子系有機材料を用いても良い。また、電荷輸送層や電荷注入層として炭化珪素等の無機材料を用いることも可能である。これらの有機材料や無機材料は公知の材料を用いることができる。

【0145】

本実施例では発光層45の上にPEDOT(ポリチオフェン)またはPAni(ポリアニリン)でなる正孔注入層46を設けた積層構造の有機化合物層としている。そして、正孔注入層46の上には透明導電膜でなる陽極47が設けられる。本実施例の場合、発光層45で生成された光は上面側に向かって(TFTの上方に向かって)放射されるため、陽極は透光性でなければならない。透明導電膜としては酸化インジウムと酸化スズとの化合物や酸化インジウムと酸化亜鉛との化合物を用いることができるが、耐熱性の低い発光層や正孔注入層を形成した後で形成するため、可能な限り低温で成膜できるものが好ましい。

【0146】

陽極47まで形成された時点で表示用発光素子3505が完成する。なお、ここでいう表示用発光素子3505は、画素電極(陰極)43、発光層45、正孔注入層46及び陽極47で形成されたコンデンサを指す。図16(A)に示すように画素電極43は画素の面積にほぼ一致するため、画素全体が発光素子として機能する。従って、発光の利用効率が非常に高く、明るい画像表示が可能となる。

【0147】

ところで、本実施例では、陽極47の上にさらに第2パッシベーション膜48を設けている。第2パッシベーション膜48としては窒化珪素膜または窒化酸化珪素膜が好ましい。この目的は、外部と表示用発光素子とを遮断することであり、有機材料の酸化による劣化を防ぐ意味と、有機材料からの脱ガスを抑える意味との両方を併せ持つ。これにより表示装置の信頼性が高められる。

【0148】

以上のように本発明の表示装置は図15のような構造の画素からなる表示部を有し、オフ電流値の十分に低いスイッチング用TFTと、ホットキャリア注入に強い電流制御用TFTとを有する。従って、高い信頼性を有し、且つ、良好な画像表示が可能な表示装置が得られる。

【0149】

なお、本実施例の構成は、実施の形態、実施例1と自由に組み合わせて実施することが可能である。

【0150】

(実施例5)

本実施例では、実施例4に示した表示部において、表示用発光素子3505の構造を反転させた構造について説明する。説明には図17を用いる。なお、図15の構造と異なる点は表示用発光素子3505の部分と電流制御用TFT3503だけであるので、その他の説明は省略することとする。実装する光センサは反対側に実装をおこなう。

【0151】

本実施例では、画素電極(陽極)50として透明導電膜を用いる。具体的には酸化インジウムと酸化亜鉛との化合物でなる導電膜を用いる。勿論、酸化インジウムと酸化スズとの化合物でなる導電膜を用いても良い。

【0152】

そして、絶縁膜でなるバンク51a、51bが形成された後、溶液塗布によりポリビニルカルバゾールでなる発光層52が形成される。その上にはカリウムアセチルアセトネート(acacKと表記される)でなる電子注入層53、アルミニウム合金でなる陰極54が形成される。この場合、陰極54がパッシベーション膜としても機能する。こうして表示用発光素子3701が形成される。

【0153】

本実施例の場合、発光層52で発生した光は、矢印で示されるようにTFTが形成された基板の方に向かって放射される。

【0154】

なお、本実施例の構成は、実施の形態、実施例1の構成と自由に組み合わせて実施することが可能である。

【0155】

(実施例6)

本実施例では、図16(B)に示した回路図とは異なる構造の画素とした場合の例について図18(A)〜(C)に示す。なお、本実施例において、3801はスイッチング用TFT3802のソース配線の一部であるソース信号線、3803はスイッチング用TFT3802のゲート配線の一部であるゲート信号線、3804は電流制御用TFT、3805はコンデンサ、3806、3808は電源供給線、3807は表示用発光素子とする。

【0156】

図18(A)は、二つの画素間で電源供給線3806を共通とした場合の例である。即ち、二つの画素が電源供給線3806を中心に線対称となるように形成されている点に特徴がある。この場合、電源供給線の本数を減らすことができるため、表示部をさらに高精細化することができる。

【0157】

また、図18(B)は、電源供給線3808をゲート信号線3803と平行に設けた場合の例である。なお、図18(B)では電源供給線3808とゲート信号線3803とが重ならないように設けた構造となっているが、両者が異なる層に形成される配線であれば、絶縁膜を介して重なるように設けることもできる。この場合、電源供給線3808とゲート信号線3803とで専有面積を共有させることができるため、表示部をさらに高精細化することができる。

【0158】

また、図18(C)は、図18(B)の構造と同様に電源供給線3808をゲート信号線3803と平行に設け、さらに、二つの画素を電源供給線3808を中心に線対称となるように形成する点に特徴がある。また、電源供給線3808をゲート信号線3803のいずれか一方と重なるように設けることも有効である。この場合、電源供給線の本数を減らすことができるため、表示部をさらに高精細化することができる。

【0159】

なお、本実施例の構成は、実施の形態、実施例1〜4の構成と自由に組み合わせて実施することが可能である。

【0160】

(実施例7)

本実施例では、電流制御用TFTのゲート電極にかかる電圧を保持するための保持容量を省略する構成について説明する。電流制御用TFTがnチャネル型TFTであって、ゲート絶縁膜を介してゲート電極に重なるように設けられたLDD領域を有している場合、この重なり合った領域には一般的にゲート容量と呼ばれる寄生容量が形成される。本実施例ではこの寄生容量を保持容量の代わりとして積極的に用いる点に特徴がある。

【0161】

この寄生容量のキャパシタンスは、上記ゲート電極とLDD領域とが重なり合った面積によって変化するため、その重なり合った領域に含まれるLDD領域の長さによって決まる。

【0162】

また、実施例6に示した図18(A),(B),(C)の構造においても同様に、保持容量を省略することは可能である。

【0163】

なお、本実施例の構成は、実施例実施例1〜6の構成と自由に組み合わせて実施することが可能である。

【0164】

(実施例8)

本発明は、センサ用画素において光センサがセンサ用発光素子の発する光の輝度だけを検知するという構成に限定されない。センサ用画素が有する光センサはセンサ用発光素子の輝度の他に、表示装置の外部からの光(外光)の輝度を検知し、その外光の輝度に合わせて、発光素子の輝度の補正を行っても良い。例えば外光の輝度が高い場合発光素子の輝度を低くするように補正し、逆に外光の輝度が低い場合発光素子の輝度を高くするように補正する。

【0165】

上記構成によって、周囲の明るさに関わらず、表示装置に鮮明な画像を表示することができる。

【0166】

(実施例9)

本発明を実施して形成された表示装置は、自発光型であるため液晶ディスプレイに比べて明るい場所での視認性に優れ、しかも視野角が広い。従って、様々な電子機器に用いることができる。例えば、TV放送等を大画面で鑑賞するには対角30インチ以上(典型的には40インチ以上)のエレクトロルミネッセンス表示装置(表示装置を筐体に組み込んだディスプレイ)に本発明の表示装置を用いるとよい。

【0167】

なお、エレクトロルミネッセンス表示装置には、パソコン用ディスプレイ、TV放送受信用ディスプレイ、広告表示用ディスプレイ等の全ての情報表示用ディスプレイが含まれる。また、その他にも様々な電子機器に本発明の表示装置を用いることができる。

【0168】

その様な本発明の電子機器としては、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはデジタルビデオディスク(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。特に、斜め方向から見ることの多い携帯情報端末は視野角の広さが重要視されるため、表示装置を用いることが望ましい。それら電子機器の具体例を図19、図20に示す。

【0169】

図19(A)はエレクトロルミネッセンス表示装置であり、筐体2001、支持台2002、表示装置2003、センサ部2004等を含む。本発明は表示装置2003及びセンサ部2003に用いることができる。表示装置は自発光型であるためバックライトが必要なく、液晶ディスプレイよりも薄い表示装置とすることができる。

【0170】

図19(B)はビデオカメラであり、本体2101、表示装置2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106、センサ部2107等を含む。本発明は表示装置2102及びセンサ部2107に用いることができる。

【0171】

図19(C)は頭部取り付け型の表示装置の一部(右片側)であり、本体2201、信号ケーブル2202、頭部固定バンド2203、スクリーン部2204、光学系2205、表示装置2206、センサ部2207等を含む。本発明は表示装置2206及びセンサ部2207に用いることができる。

【0172】

図19(D)は記録媒体を備えた画像再生装置(具体的にはDVD再生装置)であり、本体2301、記録媒体(DVD等)2302、操作スイッチ2303、表示装置(a)2304、表示装置(b)2305、センサ部2306等を含む。表示装置(a)2304は主として画像情報を表示し、表示装置(b)2305は主として文字情報を表示するが、本発明はこれら表示装置(a)、(b)2304、2305及びセンサ部2306に用いることができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。

【0173】

図19(E)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体2401、表示装置2402、アーム部2403、センサ部2404を含む。本発明は表示装置2402及びセンサ部2404に用いることができる。なお図23(E)では、センサ部2404をアーム部2403に設けたが、本発明はこれに限定されなく、表示装置2402と並べて設けても良い。

【0174】

図19(F)はパーソナルコンピュータであり、本体2501、筐体2502、表示装置2503、キーボード2504、センサ部2505等を含む。本発明は表示装置2503及びセンサ部2505に用いることができる。

【0175】

なお、将来的に有機材料の発光輝度が高くなれば、出力した画像情報を含む光をレンズ等で拡大投影してフロント型若しくはリア型のプロジェクターに用いることも可能となる。

【0176】

また、上記電子機器はインターネットやCATV(ケーブルテレビ)などの電子通信回線を通じて配信された情報を表示することが多くなり、特に動画情報を表示する機会が増してきている。有機材料の応答速度は非常に高いため、表示装置は動画表示に好ましい。

【0177】

また、表示装置は発光している部分が電力を消費するため、発光部分が極力少なくなるように情報を表示することが望ましい。従って、携帯情報端末、特に携帯電話や音響再生装置のような文字情報を主とする電子機器に表示装置を用いる場合には、非発光部分を背景として文字情報を発光部分で形成するように駆動することが望ましい。

【0178】

ここで図20(A)は携帯電話であり、本体2601、音声出力部2602、音声入力部2603、表示装置2604、操作スイッチ2605、アンテナ2606、センサ部2607を含む。本発明は表示装置2604及びセンサ部2607に用いることができる。なお、表示装置2604は黒色の背景に白色の文字を表示することで携帯電話の消費電力を抑えることができる。

【0179】

また、図20(B)は音響再生装置、具体的にはカーオーディオであり、本体2701、表示装置2702、操作スイッチ2703、2704、センサ部2705を含む。本発明は表示装置2702及びセンサ部2705に用いることができる。また、本実施例では車載用オーディオを示すが、携帯型や家庭用の音響再生装置に用いても良い。なお、表示装置2704は黒色の背景に白色の文字を表示することで消費電力を抑えられる。これは携帯型の音響再生装置において特に有効である。

【0180】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。また、本実施例の電子機器は実施の形態、実施例1〜実施例8に示したいずれの構成の表示装置を用いても良い。

【0181】

【発明の効果】

本発明によって、表示装置を駆動するデバイスの構造、有機化合物層を構成する有機材料の特性、電極の材料、作成工程における条件、表示装置の駆動方法等により、有機化合物層の劣化する速度が左右されても、鮮明でなおかつ所望の色を有する画像を表示することが可能な表示装置を提供することができる。

【0182】

また、表示用発光素子とセンサ用発光素子とは、同じ条件で、同時に形成することで、表示用発光素子とセンサ用発光素子とが有する有機化合物層の劣化する速度をより同じくすることができ、センサ用発光素子の輝度を表示用発光素子とより同じにすることができる。したがって、光センサが検知するセンサ用発光素子の輝度が、表示用発光素子の輝度により等しくなり、表示用発光素子の輝度の変化をより正確に検知し、所望の輝度に補正することが可能になる。

【図面の簡単な説明】

【図1】 本発明の表示装置の上面概略図。

【図2】 本発明の表示装置の回路図。

【図3】 本発明の表示装置のセンサ用画素の回路図。

【図4】 本発明の表示装置の表示用画素の回路図。

【図5】 本発明の表示装置をデジタル方式で駆動させたときのタイミングチャート図。

【図6】 本発明の表示装置の補正回路のブロック図。

【図7】 本発明の表示装置の上面概略図。

【図8】 本発明の表示装置をアナログ方式で駆動させたときのタイミングチャート図。

【図9】 本発明の表示装置のビデオ信号補正回路のブロック図。

【図10】 本発明の光センサの断面図。

【図11】 本発明の光センサの特性図。

【図12】 本発明の光センサの応用図。

【図13】 本発明の光センサの実装図。

【図14】 本発明の光センサの実装図。

【図15】 本発明の表示装置の表示用画素の断面図。

【図16】 本発明の表示装置の表示用画素の上面図及び回路図。

【図17】 本発明の表示装置の表示用画素の断面図。

【図18】 本発明の表示装置の表示用画素の回路図。

【図19】 本発明の表示装置を用いた電子機器の図。

【図20】 本発明の表示装置を用いた電子機器の図。

【符号の説明】

101 表示部

102 ソース信号線駆動回路

102a シフトレジスタ

102b ラッチ(A)

102c ラッチ(B)

103 ゲート信号線駆動回路

104 センサ部

104a Rセンサ用画素

104b Gセンサ用画素

104c Bセンサ用画素

105 表示用画素

Claims (17)

- 表示部とセンサ部とを有し、

前記表示部は複数の表示用画素を有し、

前記センサ部は1つ又は複数のセンサ用画素を有し、

前記複数の表示用画素と前記1つ又は複数のセンサ用画素には同一構造の発光素子が設けられ、

前記表示部と前記1つ又は複数のセンサ用画素は同一ガラス基板上に設けられ、

前記表示部及びセンサ部が設けられている側とは逆側の前記ガラス基板に形成された凹部に、発光素子の輝度を検知する光センサが設けられ、

前記光センサを流れる電流によって、前記複数の表示用画素がそれぞれ有する発光素子の輝度を調節する制御手段が備えられていることを特徴とする表示装置。 - 表示部とセンサ部とを有し、

前記表示部は複数の表示用画素を有し、

前記センサ部は1つ又は複数のセンサ用画素を有し、

前記複数の表示用画素と前記1つ又は複数のセンサ用画素には同一構造の発光素子が設けられ、

前記表示部と前記1つ又は複数のセンサ用画素は同一ガラス基板上に設けられ、

前記表示部及びセンサ部が設けられている側とは逆側の前記ガラス基板に形成された凹部に、発光素子の輝度を検知する光センサが設けられ、

前記光センサは、FPC(フレキシブルプリントサーキット)によって実装されており、

前記光センサを流れる電流によって、前記複数の表示用画素がそれぞれ有する発光素子の輝度を調節する制御手段が備えられていることを特徴とする表示装置。 - 表示部とセンサ部とを有し、

前記表示部は複数の表示用画素を有し、

前記センサ部は1つ又は複数のセンサ用画素を有し、

前記複数の表示用画素と前記1つ又は複数のセンサ用画素には同一構造の発光素子が設けられ、

前記表示部と前記1つ又は複数のセンサ用画素は同一ガラス基板上に設けられ、

前記表示部及びセンサ部が設けられている側とは逆側の前記ガラス基板に形成された凹部に、発光素子の輝度を検知する光センサが設けられ、

前記光センサは、FPC(フレキシブルプリントサーキット)によって実装されており、

前記光センサと前記ガラス基板との間にはカラーフィルターが設けられ、

前記光センサを流れる電流によって、前記複数の表示用画素がそれぞれ有する発光素子の輝度を調節する制御手段が備えられていることを特徴とする表示装置。 - 請求項1乃至請求項3のいずれか1項において、

前記発光素子は、赤色、青色又は緑色に発光する発光素子であることを特徴とする表示装置。 - 請求項1乃至請求項4のいずれか1項において、

前記光センサは、オペアンプの反転入力端子と接続され、

前記オペアンプの出力と前記反転入力端子とが接続され、

前記オペアンプの出力は、前記発光素子の輝度を調節する制御手段の入力部と接続されていることを特徴とする表示装置。 - 請求項1乃至請求項5のいずれか1項において、

前記光センサはアモルファスシリコンフォトダイオードであることを特徴とする表示装置。 - 請求項1乃至請求項5のいずれか1項において、

前記光センサは、ガラス基板上に形成されたアモルファスシリコンと、

前記アモルファスシリコン上に形成されたNi電極と、

前記Ni電極上に形成された絶縁膜と、

前記絶縁膜上に形成され、前記Ni電極とコンタクトするはんだパッドとを有することを特徴とする表示装置。 - 請求項1乃至請求項7のいずれか1項において、

前記光センサによって、前記センサ用画素の有する発光素子の輝度を検知することを特徴とする表示装置。 - 請求項1乃至請求項7のいずれか1項において、

前記光センサによって、前記センサ用画素の有する発光素子の輝度及び外光の輝度を検知することを特徴とする表示装置。 - 請求項1乃至請求項9のいずれか1項において、前記発光素子は、陽極と陰極との間に有機化合物層が備えられ、前記有機化合物層は低分子系有機物質またはポリマー系有機物質で形成されていることを特徴とする表示装置。

- 請求項10において、

前記低分子系有機物質は、Alq3(トリス−8−キノリライト−アルミニウム)またはTPD(トリフェニルアミン誘導体)からなることを特徴とする表示装置。 - 請求項10において、

前記ポリマー系有機物質は、PPV(ポリフェニレンビニレン)、PVK(ポリビニルカルバゾール)またはポリカーボネートからなることを特徴とする表示装置。 - 請求項10乃至請求項12のいずれか1項において、

前記陽極は、酸化インジウムと酸化亜鉛との化合物、または酸化インジウムと酸化スズとの化合物でなる導電膜であることを特徴とする表示装置。 - 請求項1乃至請求項13のいずれか1項に記載の前記表示装置を用いることを特徴とするコンピュータ。

- 請求項1乃至請求項13のいずれか1項に記載の前記表示装置を用いることを特徴とするナビゲーションシステム。

- 請求項1乃至請求項13のいずれか1項に記載の前記表示装置を用いることを特徴とするゲーム機器。

- 請求項1乃至請求項13のいずれか1項に記載の前記表示装置を用いることを特徴とする携帯情報端末。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001365324A JP3883854B2 (ja) | 2001-11-29 | 2001-11-29 | 表示装置、コンピュータ、ナビゲーションシステム、ゲーム機器、及び携帯情報端末 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001365324A JP3883854B2 (ja) | 2001-11-29 | 2001-11-29 | 表示装置、コンピュータ、ナビゲーションシステム、ゲーム機器、及び携帯情報端末 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003167550A JP2003167550A (ja) | 2003-06-13 |

| JP2003167550A5 JP2003167550A5 (ja) | 2005-08-04 |

| JP3883854B2 true JP3883854B2 (ja) | 2007-02-21 |

Family

ID=19175360

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001365324A Expired - Fee Related JP3883854B2 (ja) | 2001-11-29 | 2001-11-29 | 表示装置、コンピュータ、ナビゲーションシステム、ゲーム機器、及び携帯情報端末 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3883854B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8441209B2 (en) | 2009-03-18 | 2013-05-14 | Semiconductor Energy Laboratory Co., Ltd. | Lighting device having variable current source |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2004090487A1 (ja) | 2003-03-26 | 2004-10-21 | Semiconductor Energy Laboratory Co., Ltd. | 多方向からの光を検出する光センサ、携帯通信機器及び表示方法 |

| JP5162807B2 (ja) * | 2003-08-29 | 2013-03-13 | セイコーエプソン株式会社 | 電気光学装置及び電子機器 |

| JP2005099714A (ja) | 2003-08-29 | 2005-04-14 | Seiko Epson Corp | 電気光学装置、電気光学装置の駆動方法および電子機器 |

| JP4836402B2 (ja) * | 2003-09-29 | 2011-12-14 | 東北パイオニア株式会社 | 自発光型表示装置 |

| US7295192B2 (en) * | 2004-05-04 | 2007-11-13 | Au Optronics Corporation | Compensating color shift of electro-luminescent displays |

| JP5087820B2 (ja) * | 2004-05-25 | 2012-12-05 | 株式会社Jvcケンウッド | 表示装置 |

| JP2006106672A (ja) * | 2004-05-25 | 2006-04-20 | Victor Co Of Japan Ltd | 表示装置 |

| CN101184732B (zh) | 2005-03-28 | 2012-05-16 | 株式会社半导体能源研究所 | 蒽衍生物、发光元件用材料、发光元件、发光装置和电子器件 |

| JP2007156044A (ja) * | 2005-12-05 | 2007-06-21 | Sony Corp | 自発光表示装置、階調値/劣化率変換テーブル更新装置及びプログラム |

| JP2007240800A (ja) * | 2006-03-08 | 2007-09-20 | Sony Corp | 自発光表示装置、エージング装置及びプログラム |

| JP2007242830A (ja) * | 2006-03-08 | 2007-09-20 | Sony Corp | 表示装置及び表示装置の製造方法 |

| JP2007240798A (ja) * | 2006-03-08 | 2007-09-20 | Sony Corp | 自発光表示装置、階調値/劣化量変換テーブル更新装置、入力表示データ補正装置及びプログラム |

| CN101506163B (zh) * | 2006-08-30 | 2012-05-02 | 株式会社半导体能源研究所 | 合成蒽衍生物的方法和蒽衍生物、发光元件、发光装置、电子装置 |

| JP5179805B2 (ja) * | 2006-08-30 | 2013-04-10 | 株式会社半導体エネルギー研究所 | アントラセン誘導体、発光素子および発光装置 |

| US7723722B2 (en) | 2007-03-23 | 2010-05-25 | Semiconductor Energy Laboratory Co., Ltd. | Organic compound, anthracene derivative, and light-emitting element, light-emitting device, and electronic device using anthracene derivative |

| US8736587B2 (en) * | 2008-07-10 | 2014-05-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| ATE517088T1 (de) | 2008-09-19 | 2011-08-15 | Semiconductor Energy Lab | Carbazolderivat und herstellungsverfahren dafür |

| JP4770906B2 (ja) * | 2008-10-07 | 2011-09-14 | ソニー株式会社 | 表示装置 |

| GB0819447D0 (en) * | 2008-10-23 | 2008-12-03 | Cambridge Display Tech Ltd | Optical sensor array |

| TWI585955B (zh) | 2008-11-28 | 2017-06-01 | 半導體能源研究所股份有限公司 | 光感測器及顯示裝置 |

| JP5740132B2 (ja) | 2009-10-26 | 2015-06-24 | 株式会社半導体エネルギー研究所 | 表示装置及び半導体装置 |

| CN102915172B (zh) * | 2011-08-03 | 2017-02-08 | 中兴通讯股份有限公司 | 一种管理显示屏的方法及装置 |

| KR20170101128A (ko) | 2016-02-26 | 2017-09-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 유기 화합물, 발광 소자, 발광 장치, 전자 기기, 및 조명 장치 |

-

2001

- 2001-11-29 JP JP2001365324A patent/JP3883854B2/ja not_active Expired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8441209B2 (en) | 2009-03-18 | 2013-05-14 | Semiconductor Energy Laboratory Co., Ltd. | Lighting device having variable current source |

| US9426848B2 (en) | 2009-03-18 | 2016-08-23 | Semiconductor Energy Laboratory Co., Ltd. | Lighting device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003167550A (ja) | 2003-06-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3883854B2 (ja) | 表示装置、コンピュータ、ナビゲーションシステム、ゲーム機器、及び携帯情報端末 | |

| JP4620140B2 (ja) | 表示装置 | |

| JP4145495B2 (ja) | 表示装置、コンピュータ、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置、ゲーム機器、携帯情報端末、及び画像再生装置 | |

| JP4869497B2 (ja) | 表示装置 | |

| KR100786546B1 (ko) | 전자 디바이스 | |

| KR100773823B1 (ko) | 발광장치 | |

| KR100986250B1 (ko) | 발광장치 | |

| US6765549B1 (en) | Active matrix display with pixel memory | |

| JP4034122B2 (ja) | 発光装置及び素子基板 | |

| JP4869491B2 (ja) | 発光装置 | |

| JP2003323157A (ja) | 発光装置の駆動方法及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20041129 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041227 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060807 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060829 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061023 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061114 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061115 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091124 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091124 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101124 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101124 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111124 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111124 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121124 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121124 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131124 Year of fee payment: 7 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |