JP3772622B2 - 薄膜積層コンデンサおよびその実装方法 - Google Patents

薄膜積層コンデンサおよびその実装方法 Download PDFInfo

- Publication number

- JP3772622B2 JP3772622B2 JP2000026527A JP2000026527A JP3772622B2 JP 3772622 B2 JP3772622 B2 JP 3772622B2 JP 2000026527 A JP2000026527 A JP 2000026527A JP 2000026527 A JP2000026527 A JP 2000026527A JP 3772622 B2 JP3772622 B2 JP 3772622B2

- Authority

- JP

- Japan

- Prior art keywords

- thin film

- multilayer capacitor

- substrate

- electrode layer

- dielectric layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000010409 thin film Substances 0.000 title claims description 100

- 239000003990 capacitor Substances 0.000 title claims description 74

- 238000000034 method Methods 0.000 title claims description 16

- 239000010408 film Substances 0.000 claims description 60

- 239000000758 substrate Substances 0.000 claims description 47

- 229910000679 solder Inorganic materials 0.000 claims description 34

- 239000002994 raw material Substances 0.000 claims description 12

- 230000001681 protective effect Effects 0.000 claims description 11

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 claims description 10

- 239000004020 conductor Substances 0.000 claims description 6

- VILCJCGEZXAXTO-UHFFFAOYSA-N 2,2,2-tetramine Chemical compound NCCNCCNCCN VILCJCGEZXAXTO-UHFFFAOYSA-N 0.000 claims description 4

- FAGUFWYHJQFNRV-UHFFFAOYSA-N tetraethylenepentamine Chemical compound NCCNCCNCCNCCN FAGUFWYHJQFNRV-UHFFFAOYSA-N 0.000 claims description 4

- 230000015572 biosynthetic process Effects 0.000 description 8

- 239000000463 material Substances 0.000 description 8

- 239000003985 ceramic capacitor Substances 0.000 description 7

- 238000004544 sputter deposition Methods 0.000 description 6

- 239000000919 ceramic Substances 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 230000006355 external stress Effects 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- 238000005520 cutting process Methods 0.000 description 3

- 239000007789 gas Substances 0.000 description 3

- 229960001124 trientine Drugs 0.000 description 3

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- 229910010413 TiO 2 Inorganic materials 0.000 description 2

- 230000005587 bubbling Effects 0.000 description 2

- 239000012159 carrier gas Substances 0.000 description 2

- 239000002003 electrode paste Substances 0.000 description 2

- 238000010030 laminating Methods 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 229910052594 sapphire Inorganic materials 0.000 description 2

- 239000010980 sapphire Substances 0.000 description 2

- 229910002367 SrTiO Inorganic materials 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000010304 firing Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 238000001552 radio frequency sputter deposition Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000000859 sublimation Methods 0.000 description 1

- 230000008022 sublimation Effects 0.000 description 1

- 150000005671 trienes Chemical class 0.000 description 1

- 238000009966 trimming Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/30—Stacked capacitors

- H01G4/306—Stacked capacitors made by thin film techniques

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

- Wire Bonding (AREA)

Description

【発明の属する技術分野】

この発明は薄膜積層コンデンサおよびその実装方法に関し、特にたとえば、小型で比較的大容量の薄膜積層コンデンサおよびその実装方法に関する。

【0002】

【従来の技術】

近年、電子部品の分野においては、回路の高密度化に伴い、コンデンサなどの一層の小型化および高性能化が望まれている。小型のコンデンサとして積層セラミックコンデンサなどがあるが、このような積層セラミックコンデンサを作製するには、所定の大きさにカットされた誘電体セラミックグリーンシートが準備される。このセラミックグリーンシート上に電極ペーストを印刷し、乾燥後にセラミックグリーンシートの積層、圧着を行い、さらに所定の大きさにカットして焼成することにより、チップが得られる。このチップに外部電極ペーストを塗布し、焼き付けることにより、積層セラミックコンデンサが得られる。

【0003】

しかしながら、このような方法で積層セラミックコンデンサを作製する場合、セラミック原料粉末粒径よりも誘電体層を薄くすることは不可能であり、その他誘電体層の欠陥によるショートや電極切れの問題から、現状では誘電体層の厚み3μm以下のものを作製することは困難であり、積層セラミックコンデンサの小型、大容量化には限界があった。

【0004】

このような問題を解決するために、たとえば特開昭56−144523号公報には、基板上にスパッタリング法で誘電体部分を作製する積層セラミックコンデンサが提案されている。ここでは、Al2 O3 ,SiO2 ,TiO2 ,BaTiO3 の薄膜および電極をスパッタリング法で作製する方法が開示されている。

【0005】

【発明が解決しようとする課題】

しかしながら、Al2 O3 ,SiO2 ,TiO2 などは、材料そのものの誘電率が低いので、コンデンサとしての容量を上げようとすると、膜厚を非常に薄くする必要があり、リーク電流、絶縁耐圧など、電子デバイスとしての信頼性に問題がでてくる。そこで、BaTiO3 のほか、SrTiO3 ,(Ba,Sr)TiO3 ,PbTiO3 ,Pb(Zr,Ti)O3 ,Pb(Mg,Nb)O3 などのような、材料としての誘電率の高いものを用いることが考えられる。しかしながら、これらの誘電率の高い材料を用いて薄膜状態で高誘電率を得ようとすると、MOCVD法などの成膜方法を用い、高温成膜で薄膜の結晶性を向上させる必要があるが、これらの高誘電率を有する材料は固体の昇華を利用したものが多く、積層する際に高誘電率材料を再現性よく得ることが難しい。

【0006】

また、これらの薄膜は機械的強度が低いため、セラミックグリーンシートを積層した従来の積層セラミックコンデンサのようにチップ部品として使用する場合、基板側を配線基板に取り付けようとすると、薄膜側を保持して移動させる必要があり、薄膜積層コンデンサが破損しやすいという問題がある。このような問題を解決するために、基板と反対側の薄膜面に半田バンプを形成し、基板側を保持して配線基板上に薄膜積層コンデンサを移動し、半田バンプで配線基板上に取り付けることが考えられる。

【0007】

しかしながら、薄膜積層コンデンサの小型化、低背化を進めるためには、基板を可能な限り薄くし、半田バンプの厚みもなるべく小さくする必要がある。そのため、実装する際に薄膜積層コンデンサが配線基板に接触すると、外部応力によって基板そのものが破損する可能性がある。さらに、低背化の観点から、半田バンプで支持された薄膜積層コンデンサは、配線基板とほぼ平行の位置関係を保っていることが望ましい。

【0008】

それゆえに、この発明の主たる目的は、小型かつ薄型であって、大容量を得ることができ、配線基板上に実装する際にも破損しにくい薄膜積層コンデンサを提供することである。

また、この発明の目的は、このような薄膜積層コンデンサを配線基板上に実装するための薄膜積層コンデンサの実装方法を提供することである。

【0009】

【課題を解決するための手段】

この発明は、基板、および基板に形成された複数の誘電体層と電極層との積層体を含む薄膜積層コンデンサにおいて、電極層は誘電体層によって電気的に分割される第1の電極層と第2の電極層とを含み、電極層の面上において部分的に形成された誘電体層を介して第1の電極層と第2の電極層とが交互に積層され、電極層の面上であって誘電体層が形成されていない部分には導体膜が形成され、誘電体層の形成されていない部分において複数の第1の電極層が互いに電気的に接続されるとともに、誘電体層の形成されていない部分において複数の第2の電極層が互いに電気的に接続され、積層体の基板と反対側の面に、電極層と電気的に接続する3つ以上の外部接続用の半田バンプが形成されたことを特徴とする、薄膜積層コンデンサである。

このような薄膜積層コンデンサにおいて、誘電体層の形成されていない部分において複数の第1の電極層が導体膜を介して互いに電気的に接続されるとともに、誘電体層の形成されていない部分において複数の第2の電極層が導体膜を介して互いに電気的に接続された構造とすることができる。

また、積層体の面上に開口部を有する保護膜が形成され、開口部において電極層に接続される半田によって半田バンプを形成することができる。

また、この発明は、基板、および基板に形成された複数の誘電体層と電極層との積層体を含む薄膜積層コンデンサにおいて、誘電体層は、少なくともBaまたはSrを含む酸化物薄膜であり、トリエチレンテトラミンあるいはテトラエチレンペンタミンを付加したジピバロイルメタネト錯体を原料としてMOCVD法を用いて成膜されたものであり、積層体の基板と反対側の面に3つ以上の外部接続用の半田バンプが形成されたことを特徴とする、薄膜積層コンデンサである。

また、この発明は、上述のいずれかに記載の薄膜積層コンデンサを配線基板上に実装する薄膜積層コンデンサの実装方法であって、半田バンプが配線基板上の配線に接続されることを特徴とする、薄膜積層コンデンサの実装方法である。

【0010】

基板上に形成された誘電体層と電極層との積層体上に3つ以上の半田バンプを形成することにより、基板と反対側の積層体面を配線基板上に取り付けることができる。そのため、基板側を保持して薄膜積層コンデンサを配線基板上に移動させることができる。また、3つ以上の半田バンプを配線基板上の配線に接続することにより、配線基板に平行な状態で薄膜積層コンデンサを実装することができ、実装時の低背化を図ることができる。また、半田バンプにより配線基板に平行な状態で薄膜積層コンデンサを実装することができるため、薄膜積層コンデンサと配線基板との接触を防止することができ、外部応力による薄膜積層コンデンサの破損を防止することができる。

また、誘電体層を介して第1の電極層と第2の電極層とを積層することにより、第1の電極層と第2の電極層との対向面積が大きくなり、大容量のコンデンサとすることができる。

さらに、保護膜を形成することにより、積層体を保護することができる。そして、保護膜に開口部を形成することにより、積層体上に半田をのせることができ、半田バンプとして使用することができる。このとき、開口部および半田バンプは円形に形成することが望ましく、また半田バンプに使用される半田量は厳密に制御されていることが望ましい。

また、誘電体層は、少なくともBaまたはSrを含む材料で形成され、トリエチレンテトラミンあるいはテトラエチレンペンタミンを付加したジピバロイルメタネト錯体[M(DPM)2 (teraene)2 ,M(DPM)2 (triene)2 ;M=Ba,Sr]を原料としてMOCVD法を用いて成膜する場合、材料の融点以上の温度で使用することができ、通常のバブリング法を用いて気化搬送することが可能となる。それにより、誘電体の成膜時に再現性が向上し、高誘電率薄膜を積層することが可能となる。

さらに、このような薄膜積層コンデンサを用いて、半田バンプで配線基板上に取り付けることにより、基板側を保持して移動させることができるため、薄膜積層コンデンサの破損を防ぐことができる。

【0011】

この発明の上述の目的,その他の目的,特徴および利点は、図面を参照して行う以下の発明の実施の形態の詳細な説明から一層明らかとなろう。

【0012】

【発明の実施の形態】

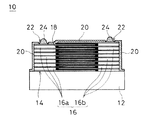

図1は、この発明の薄膜積層コンデンサの一例を示す断面図解図である。薄膜積層コンデンサ10は、基板12を含む。基板12としては、たとえばサファイアR面基板などが用いられる。基板12上には、積層体14が形成される。積層体14は、電極層16と誘電体層18とを積層することによって形成される。電極層16としては、たとえばPtなどが用いられ、スパッタリング法などによって形成される。また、誘電体層18としては、少なくともBaまたはSrを含む酸化物薄膜が用いられ、たとえば(Ba,Sr)TiO3 などが用いられる。この誘電体層18は、MOCVD法などによって形成される。電極層16は、誘電体層18によって分割された複数の第1の電極層16aと複数の第2の電極層16bとで形成されている。

【0013】

第1の電極層16aは基板12の長さ方向の一方側に形成され、第2の電極層16bは基板12の長さ方向の他方側に形成される。そして、基板12の中央部において、誘電体層18を介して第1の電極層16aと第2の電極層16bとが交互に積層される。これらの第1の電極層16aおよび第2の電極層16bは、スパッタリング法などによって複数層形成される。したがって、誘電体層18が形成されていない部分において、複数の第1の電極層16aが互いに電気的に接続され、複数の第2の電極層16bが互いに電気的に接続される。

【0014】

積層体14の外周面には、保護膜20が形成される。保護膜20としては、たとえばシリコン酸化膜などが用いられ、プラズマCVD法などによって形成される。積層体14の基板12と反対側の面上において、保護膜20には、たとえば4つの円形の開口部22が形成される。これらの開口部22によって、第1の電極層16aと第2の電極層16bとが露出し、この部分に半田をのせることにより、半田バンプ24が形成される。このとき、保護膜20の開口部22にのせられる半田の量は、厳しく制御されることが望ましい。

【0015】

このような薄膜積層コンデンサ10では、MOCVD法やスパッタリング法などによって電極層16や誘電体層18を形成することにより、非常に薄い積層体14を得ることができる。このような薄い積層体14を形成する場合には、基板14も薄くすることができ、全体として小型で薄型の薄膜積層コンデンサ10を得ることができる。このように、小型で薄型の薄膜積層コンデンサであっても、誘電体層18を挟んで第1の電極層16aと第2の電極層16bとが交互に積層されることにより、これらの電極層の対向面積が大きくなり、大容量のコンデンサとすることができる。

【0016】

また、誘電体層18を作製する際に、少なくともBaまたはSrを含む材料が用いられ、トリエチレンテトラミンあるいはテトラエチレンペンタミンを付加したジピバロイルメタネト錯体を原料とすることにより、融点以上の温度で使用することができ、通常のバブリング法を用いて気化搬送することが可能となる。そのため、誘電体成膜時の再現性が向上し、高誘電率薄膜を積層することが可能となる。

【0017】

さらに、積層体14上に半田バンプ24が形成されているため、この半田バンプ24を配線基板上に形成された配線に接続して、薄膜積層コンデンサ10を配線基板に実装することができる。したがって、実装時において、基板12側を保持して薄膜積層コンデンサ10を移動させることができ、移動時における積層体14の破損を防ぐことができる。このような基板12側を保持した移動が可能であるため、マウントの自動化も容易である。

【0018】

また、半田バンプ24が4つ形成されていることにより、薄膜積層コンデンサ10と配線基板とを平行な位置関係となるように、薄膜積層コンデンサ10を実装することができる。そのため、薄膜積層コンデンサ10を実装したときに、低背化を図ることができる。さらに、薄膜積層コンデンサ10と配線基板とを平行にすることができるため、薄膜積層コンデンサ10が配線基板に接触することを防止することができ、外部応力による薄膜積層コンデンサ10の破損を防ぐことができる。

【0019】

【実施例】

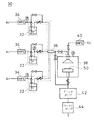

(Ba,Sr)TiO3 薄膜(以後、BST薄膜という。)を作製するため、図2に示すようなMOCVD装置30を準備した。MOCVD装置30は、3つの原料タンク32を含み、ここに原料融液が充填される。これらの原料タンク32には、マスフローコントローラ34を介して、搬送ガスとしてのArガスが送り込まれる。搬送ガスによって原料融液は気化し、混合器36に搬送されて混合される。混合された原料は、成膜チャンバ38内に送り込まれる。このとき、マスフローコントローラ40を介して、O2 ガスも送り込まれる。成膜チャンバ38内は、ブースタポンプ42およびロータリポンプ44によって低圧状態にされる。この状態で、基板50に混合材料ガスが当てられることにより、基板50上にBST薄膜が形成される。なお、原料タンク32から成膜チャンバ38までの点線で囲まれた部分は高温に保たれ、原料が気化した状態のまま成膜チャンバ38まで搬送される。

【0020】

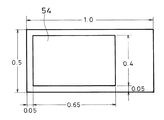

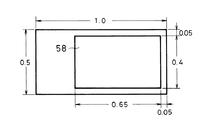

このMOCVD装置30を用いて、BST薄膜を形成するため、厚さ0.1mm、2インチ角のサファイアR面基板を準備した。そして、表1に示す条件で、メタルマスクを用いて、図3に示すようなパターンのBST薄膜52を形成した。成膜時間は75分で、膜厚は120nmである。なお、図3において、点線は切断部を示し、切りしろは0.1mmである。また、図3〜図7中に記載されている寸法の単位はmmである。

【0021】

【表1】

【0022】

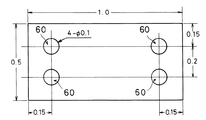

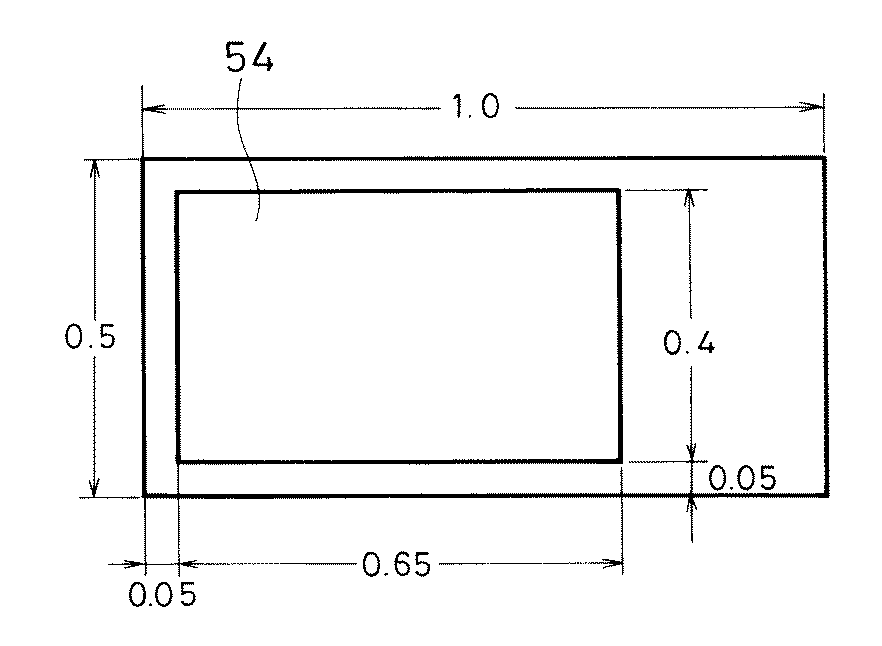

なお、BST薄膜52を成膜する前に、図4に示すパターンで、スパッタリング法によってPt膜54を形成した。なお、図4〜図7については、図3の点線で示された切断部で切断した後の寸法を示してある。Pt成膜に使用したのはRFスパッタ装置であり、成膜時間は100秒で、膜厚は約150nmである。

【0023】

【表2】

【0024】

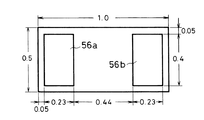

基板50上に図4に示すようなパターンのPt膜54を形成し、その上に図3に示すようなパターンのBST薄膜52を形成することにより、切断後の基板50の長さ方向の一方側のみにおいて、Pt膜54がBST薄膜52から露出した状態となる。この状態で、図5に示すようなパターンで、表2の条件でPt膜56a,56bを形成した。成膜時間は80秒で、膜厚はBST薄膜52と同様に120nmになるようにした。したがって、基板50の長さ方向の一端側において、Pt膜54とPt膜56aとが電気的に接続される。

【0025】

次に、表2に示す条件で、図6に示すようなパターンのPt膜58を形成した。成膜時間は90秒である。したがって、切断後の基板50の長さ方向の他方側において、Pt膜56bとPt膜58とが電気的に接続される。そして、その上に、図3に示すパターンとなるように、BST薄膜52を形成した。したがって、基板50の長さ方向の一方側でPt膜56aがBST膜52から露出し、他方側でPt膜58がBST薄膜52から露出した状態となる。また、基板50の長さ方向の一方側において、Pt膜58の端部で下層のBST薄膜52と上層のBST薄膜52とが連結される。

【0026】

このように、基板50上に、Pt膜54・BST薄膜52・Pt膜56a,56b・Pt膜58・BST薄膜52・・・BST薄膜52・Pt膜56a,56bを順次形成し、最後にPt膜54またはPt膜58を形成した。このようにして、15層のBST薄膜52を有する薄膜積層体を作製した。得られた薄膜積層体を酸素雰囲気中において650℃で3時間熱処理した。次に、表3に示す条件で、誘電体層および電極層の全面を覆うように、プラズマCVD法を用いて、保護膜としてシリコン酸化膜を成膜した。

【0027】

【表3】

【0028】

さらに、図7に示す4つの開口部60を有するレジストを形成し、イオントリミングにより、開口部のシリコン酸化膜を取り除き、図3の点線部分でカットした。そののち、シリコン酸化膜を取り除いた部分に半田をのせ、半田バンプを形成した。その結果、図1に示すような構造の薄膜積層コンデンサを3735個得ることができた。

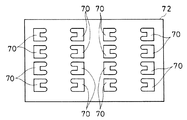

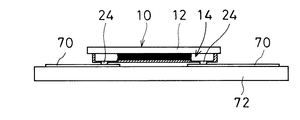

【0029】

次に、図8に示すように配線層70をメタライズした配線基板72を準備した。この配線基板72では、薄膜積層コンデンサの半田バンプに対応する間隔で配線層70が形成されている。そして、図9に示すように、リフロー半田を用いて、薄膜積層コンデンサを配線層70に接合した。このようにして、100個の薄膜積層コンデンサを配線基板72に接合し、1kHzにおける静電容量およびtanδを測定した。その結果を表4に示す。

【0030】

【表4】

【0031】

表4からわかるように、BST薄膜が15層の薄膜積層コンデンサで、0.1μF以上の静電容量が得られている。また、この特性値からBST薄膜の比誘電率を算出すると、600以上となり、高誘電率のBST膜が再現性よく得られていることがわかる。

【0032】

また、この薄膜積層コンデンサを配線基板に接合した場合の高さは約0.12mmであり、非常に低背なコンデンサが得られている。この薄膜積層コンデンサのBST薄膜層を1層増やしても、全体としての厚みは270nm増えるにすぎず、さらに積層数を増やすことにより、大容量の薄膜積層コンデンサを得ることが可能になる。

【0033】

【発明の効果】

この発明によれば、小型かつ薄型で、大容量の薄膜積層コンデンサを得ることができる。また、この薄膜積層コンデンサを配線基板上に実装する際に、基板側を保持して配線基板上に移動させることができ、移動時の薄膜積層コンデンサの破損を防止することができる。さらに、薄膜積層コンデンサと配線基板とが接触することなく、平行な位置関係で実装することができ、外部応力による薄膜積層コンデンサの破損を防止することができる。

【図面の簡単な説明】

【図1】この発明の薄膜積層コンデンサの一例を示す断面図解図である。

【図2】この発明の薄膜積層コンデンサを作製するためのMOCVD装置を示す図解図である。

【図3】実施例において作製するBST薄膜のパターンを示す図である。

【図4】実施例において作製するPt膜のパターンの1つを示す図である。

【図5】実施例において作製するPt膜のパターンの他の1つを示す図である。

【図6】実施例において作製するPt膜のさらに他の1つを示す図である。

【図7】実施例において作製する保護膜の成膜パターンを示す図である。

【図8】実施例で作製した薄膜積層コンデンサを実装する配線基板上の配線層パターンを示す平面図である。

【図9】図8に示す配線基板に薄膜積層コンデンサを実装したときの正面図解図である。

【符号の説明】

10 薄膜積層コンデンサ

12 基板

14 積層体

16 電極層

16a 第1の電極層

16b 第2の電極層

18 誘電体層

20 保護膜

22 開口部

24 半田バンプ

Claims (5)

- 基板、および前記基板に形成された複数の誘電体層と電極層との積層体を含む薄膜積層コンデンサにおいて、

前記電極層は前記誘電体層によって電気的に分割される第1の電極層と第2の電極層とを含み、前記電極層の面上において部分的に形成された前記誘電体層を介して前記第1の電極層と前記第2の電極層とが交互に積層され、

前記電極層の面上であって前記誘電体層が形成されていない部分には導体膜が形成され、

前記誘電体層の形成されていない部分において複数の前記第1の電極層が互いに電気的に接続されるとともに、前記誘電体層の形成されていない部分において複数の前記第2の電極層が互いに電気的に接続され、

前記積層体の前記基板と反対側の面に、前記電極層と電気的に接続する3つ以上の外部接続用の半田バンプが形成されたことを特徴とする、薄膜積層コンデンサ。 - 前記誘電体層の形成されていない部分において複数の前記第1の電極層が前記導体膜を介して互いに電気的に接続されるとともに、前記誘電体層の形成されていない部分において複数の前記第2の電極層が前記導体膜を介して互いに電気的に接続された、請求項1に記載の薄膜積層コンデンサ。

- 前記積層体の面上に開口部を有する保護膜が形成され、前記開口部において前記電極層に接続される半田によって前記半田バンプが形成された、請求項1または請求項2に記載の薄膜積層コンデンサ。

- 基板、および前記基板に形成された複数の誘電体層と電極層との積層体を含む薄膜積層コンデンサにおいて、

前記誘電体層は、少なくともBaまたはSrを含む酸化物薄膜であり、トリエチレンテトラミンあるいはテトラエチレンペンタミンを付加したジピバロイルメタネト錯体を原料としてMOCVD法を用いて成膜されたものであり、

前記積層体の前記基板と反対側の面に3つ以上の外部接続用の半田バンプが形成されたことを特徴とする、薄膜積層コンデンサ。 - 請求項1ないし請求項4のいずれかに記載の薄膜積層コンデンサを配線基板上に実装する薄膜積層コンデンサの実装方法であって、

前記半田バンプが前記配線基板上の配線に接続されることを特徴とする、薄膜積層コンデンサの実装方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000026527A JP3772622B2 (ja) | 2000-02-03 | 2000-02-03 | 薄膜積層コンデンサおよびその実装方法 |

| US09/773,642 US6462933B2 (en) | 2000-02-03 | 2001-01-31 | Thin film multilayer capacitor and mounting method therefor |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000026527A JP3772622B2 (ja) | 2000-02-03 | 2000-02-03 | 薄膜積層コンデンサおよびその実装方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001217142A JP2001217142A (ja) | 2001-08-10 |

| JP3772622B2 true JP3772622B2 (ja) | 2006-05-10 |

Family

ID=18552249

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000026527A Expired - Lifetime JP3772622B2 (ja) | 2000-02-03 | 2000-02-03 | 薄膜積層コンデンサおよびその実装方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6462933B2 (ja) |

| JP (1) | JP3772622B2 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3502988B2 (ja) * | 2001-07-16 | 2004-03-02 | Tdk株式会社 | 多端子型の積層セラミック電子部品 |

| JP5030349B2 (ja) * | 2001-09-28 | 2012-09-19 | 株式会社アルバック | 誘電体膜の作製方法 |

| JP3882718B2 (ja) * | 2002-08-29 | 2007-02-21 | 株式会社村田製作所 | 薄膜積層電子部品の製造方法 |

| US7573698B2 (en) * | 2002-10-03 | 2009-08-11 | Avx Corporation | Window via capacitors |

| US7016175B2 (en) * | 2002-10-03 | 2006-03-21 | Avx Corporation | Window via capacitor |

| DE10313891A1 (de) * | 2003-03-27 | 2004-10-14 | Epcos Ag | Elektrisches Vielschichtbauelement |

| EP1610599A1 (en) * | 2003-03-28 | 2005-12-28 | TDK Corporation | Multilayer substrate and method for producing same |

| US7218504B2 (en) * | 2004-03-02 | 2007-05-15 | Intel Corporation | Capacitor device and method |

| DE102005028498B4 (de) * | 2005-06-20 | 2015-01-22 | Epcos Ag | Elektrisches Vielschichtbauelement |

| DE102005037875B3 (de) * | 2005-08-10 | 2007-03-29 | Siemens Ag | Verfahren zur Herstellung von Vielschichtbauelementen in Dünnschicht-Technologie |

| US8414962B2 (en) | 2005-10-28 | 2013-04-09 | The Penn State Research Foundation | Microcontact printed thin film capacitors |

| JP5051166B2 (ja) | 2009-03-27 | 2012-10-17 | Tdk株式会社 | 薄膜デバイス |

| JP5407775B2 (ja) | 2009-03-31 | 2014-02-05 | Tdk株式会社 | 薄膜コンデンサの製造方法及び薄膜コンデンサ |

| JP5730872B2 (ja) | 2009-07-23 | 2015-06-10 | プロテウス デジタル ヘルス, インコーポレイテッド | 固体薄膜コンデンサ |

| JP5158061B2 (ja) | 2009-11-30 | 2013-03-06 | Tdk株式会社 | 薄膜コンデンサ |

| KR101823174B1 (ko) | 2013-06-14 | 2018-01-29 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 실장 기판 |

| US10607779B2 (en) * | 2016-04-22 | 2020-03-31 | Rohm Co., Ltd. | Chip capacitor having capacitor region directly below external electrode |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| NL6910723A (ja) * | 1968-07-24 | 1970-01-27 | ||

| EP0917165B1 (en) * | 1997-11-14 | 2007-04-11 | Murata Manufacturing Co., Ltd. | Multilayer capacitor |

-

2000

- 2000-02-03 JP JP2000026527A patent/JP3772622B2/ja not_active Expired - Lifetime

-

2001

- 2001-01-31 US US09/773,642 patent/US6462933B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US6462933B2 (en) | 2002-10-08 |

| JP2001217142A (ja) | 2001-08-10 |

| US20010015884A1 (en) | 2001-08-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3772622B2 (ja) | 薄膜積層コンデンサおよびその実装方法 | |

| US12170174B2 (en) | Multi-layer ceramic electronic component, multi-layer ceramic electronic component mounting substrate, and multi-layer ceramic electronic component package | |

| KR100568306B1 (ko) | 박막형 다층 세라믹 캐패시터 및 그 제조방법 | |

| US20010015250A1 (en) | Laminated ceramic electronic components and manufacturing method therefor | |

| US11636981B2 (en) | Multi-layer ceramic electronic component, multi-layer ceramic electronic component mounting substrate, multi-layer ceramic electronic component package, and method of producing a multi-layer ceramic electronic component | |

| JPH07122455A (ja) | セラミック積層電子部品の製造方法 | |

| JP2000340448A (ja) | 積層セラミックコンデンサ | |

| JP3210440B2 (ja) | 積層セラミックコンデンサの製造方法 | |

| JPH0786743A (ja) | 多層セラミック基板の製造方法 | |

| JP4000050B2 (ja) | セラミック積層体の製法 | |

| JP3460620B2 (ja) | セラミック積層電子部品の製造方法 | |

| JPH0786083A (ja) | 積層セラミックコンデンサの製造方法 | |

| JP2004289085A (ja) | 薄膜積層電子部品及びその製造方法 | |

| JP2003045740A (ja) | 積層型電子部品 | |

| JP4412837B2 (ja) | 積層型電子部品およびその製法 | |

| JP2000243650A (ja) | 積層セラミックコンデンサおよびその製造方法 | |

| JP2023034395A (ja) | セラミック電子部品およびその製造方法 | |

| JPH0590067A (ja) | 積層磁器コンデンサの製造方法 | |

| JP3496184B2 (ja) | 積層セラミック電子部品の製造方法 | |

| JP7778583B2 (ja) | キャリア基体付きセラミック電子部品、セラミック電子部品の実装構造、および、電子部品連 | |

| JPH06349674A (ja) | 金属膜支持体及びセラミックグリーンシート供給体並びに電子部品用セラミック積層体 | |

| JP2002198250A (ja) | 積層型電子部品 | |

| US20230187132A1 (en) | Multilayer ceramic electronic component, manufacturing method thereof, circuit board, and package | |

| KR102926212B1 (ko) | 적층 세라믹 전자 부품, 적층 세라믹 전자 부품 실장 기판 및 적층 세라믹 전자 부품 포장체, 및 적층 세라믹 전자 부품의 제조 방법 | |

| WO2025127052A1 (ja) | 積層セラミックコンデンサおよび実装構造体 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20041019 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20041116 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050111 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060124 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060206 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3772622 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090224 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100224 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110224 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110224 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120224 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130224 Year of fee payment: 7 |

|

| EXPY | Cancellation because of completion of term |