JP3737838B2 - 同期回路 - Google Patents

同期回路 Download PDFInfo

- Publication number

- JP3737838B2 JP3737838B2 JP14344295A JP14344295A JP3737838B2 JP 3737838 B2 JP3737838 B2 JP 3737838B2 JP 14344295 A JP14344295 A JP 14344295A JP 14344295 A JP14344295 A JP 14344295A JP 3737838 B2 JP3737838 B2 JP 3737838B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- phase

- frequency

- output

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000001360 synchronised effect Effects 0.000 title claims description 17

- 230000000737 periodic effect Effects 0.000 claims description 12

- 238000001914 filtration Methods 0.000 claims description 5

- 230000010363 phase shift Effects 0.000 description 11

- 238000010586 diagram Methods 0.000 description 8

- 230000000694 effects Effects 0.000 description 5

- 230000008901 benefit Effects 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 238000001228 spectrum Methods 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 230000002411 adverse Effects 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 230000005405 multipole Effects 0.000 description 1

- 230000036316 preload Effects 0.000 description 1

- 230000000750 progressive effect Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 238000010079 rubber tapping Methods 0.000 description 1

- 230000002123 temporal effect Effects 0.000 description 1

- 238000011144 upstream manufacturing Methods 0.000 description 1

- 238000004804 winding Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/04—Synchronising

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/04—Synchronising

- H04N5/12—Devices in which the synchronising signals are only operative if a phase difference occurs between synchronising and synchronised scanning devices, e.g. flywheel synchronising

- H04N5/126—Devices in which the synchronising signals are only operative if a phase difference occurs between synchronising and synchronised scanning devices, e.g. flywheel synchronising whereby the synchronisation signal indirectly commands a frequency generator

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/16—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop

- H03L7/22—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using more than one loop

- H03L7/23—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using more than one loop with pulse counters or frequency dividers

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

- Synchronizing For Television (AREA)

Description

【産業上の利用分野】

本発明は電圧制御発振器の同期入力信号への位相ロックに関する。

【0002】

【従来の技術】

テレビジョン受像機のラスタ走査回路は、水平ライン及び垂直フィールドを表わす水平及び垂直同期成分を含む受信ビデオ信号の同期成分又はシンク(sync)に同期させられる。標準規格NTSCビデオ信号は、例えば、fH、1fH又は1Hとして示される15734Hzの水平ライン周波数で、262.5水平ライン毎のの二つの連続フィールドによって画成される。二つのフィールドの水平ラインは、29.97Hzのレートで繰り返す完全な525ラインのビデオフレームを形成するため、連続的な表示によってインターレースされる。

【0003】

テレビジョン受像機の画質を改善する努力には、ビデオ信号のある262.5ラインに割り当てられた時間中に525ラインの全フレームが表示される順次走査形、又は、ノンインターレース形表示装置の開発が含まれる。この装置は、ビデオ信号と同期して動作する間にビデオ信号周波数の2倍、又は、2fHに一致する表示周波数で水平ラインが走査されることを必要とする。かかるテレビジョン受像機は、入力同期信号から得られたパルス間に正確に水平トリガパルスを効果的に挿入し、ビデオ信号の水平周波数の2倍の表示周波数で水平トリガ信号を発生させることが必要である。同様に、ビデオ信号周波数の別の倍数で1fHビデオ信号を表示させてもよい。例えば、1fH又は2fHビデオ信号は、4fH表示走査周波数で表示させることが可能であり、或いは、他の倍数を使用してもよい。

【0004】

表示周波数信号を発生する回路は、受信入力信号の同期成分に追従する逓倍位相ロックループを有する利点がある。逓倍位相ロックループにおいて、例えば、受信ビデオ信号にロックされた水平トリガ信号を発生させるため、電圧制御発振器は、典型的には、入力信号の数倍の周波数で動作させられる。電圧制御発振器の出力は、例えば、少なくとも一つのカウンタ又はフリップフロップを分周器として使用して、上記倍数によって、即ち、1fHまでカウントダウンされる。分周器からのカウントダウンされた1fH信号は、ビデオ信号の同期成分に応答し、ビデオ信号の同期成分と発振器の間の位相アライメントの関数として出力電圧を発生する位相比較器に帰還される。位相比較器の出力は、発振器の周波数を制御するチューニング電圧を供給し、テレビジョン受像機がビデオ信号の同期成分をシークし、ロックすることを可能にさせる。

【0005】

入力ビデオ信号が安定であると仮定すると、位相比較器は、ループがロックされたときチューニング電圧を発生し、チューニング電圧の平均又は直流電流成分は安定化する。しかし、チューニング電圧は、例えば、チューニング電圧をフィルタリングするため使用された回路に依存してランプ状又は鋸歯状に同期信号のレートで周期的に変化する場合がある。たとえ、カウントダウンされた1fH信号がビデオ同期信号と同位相で正確に維持されても、鋸歯は同期入力信号の周期内で発振器出力周波数を変調する。トリガ信号は、位相ロック制御の基本である1fH帰還信号よりも高い周波数の出力信号を発生する分周器回路内の点でタップすることにより、1fH信号の倍数で上記回路から発生させることが可能である。チューニング電圧のAC成分によって誘起される発振器周波数の鋸歯状変調には、このように高い周波数のパルスは、制御された1fHの周波数のパルス間に対称的に生じないという望ましくない点がある。

【0006】

かかる発振器周波数の周期的な変動の影響は、電圧制御発振器が32fHで動作する場合に関して評価できる。発振器の出力は、位相比較器に対し1fHの帰還信号を発生させるため32で分周される。発振器の周波数は、ノンインターレース形水平走査に使用される偏向回路を制御する2fHの信号を発生させるため16で分周される。32fHの出力周波数がチューニング電圧変調に起因して1fHのサイクル中に変化するとき、2fHの交互の水平ラインは、長さが一致しない。交互のラインは長さが異なり、垂直方向に揃えられていないので、表示の乱れの影響が生じる。かかる乱れの影響は、ノンインターレース表示においては非常に望ましくない影響であり、偏向回路の共振の影響によって増大される傾向がある。

【0007】

【発明が解決しようとする課題】

位相比較器の出力は、典型的には、発振器の出力周波数が1fHレートで変調される範囲を減少させ得るローパスフィルタを介して発振器に結合される。しかし、広範囲のフィルタリングは、位相ロックループの応答及び追従性能を低下させる。その上、複数の位相ロックループが縦続される場合があり、第1の位相ロックループは、同期入力信号から2fHのトリガ信号を発生し、偏向回路に関連付けられた第2の位相ロックループは、発生された2fHのトリガ信号に走査を同期させる。しかし、上記二つの位相ロックループには相反する要求があり、他のシステムパラメータの中の幾つかを犠牲にしなければ、1fH成分の十分な減衰は得られない。

【0008】

【課題を解決するための手段】

同期回路において、発振器は、同期入力信号の周波数よりも高い、入力信号の周波数の整数倍の周波数の出力信号を発生する。制御回路は、入力信号と、出力信号を表わす帰還信号とに応答し、入力及び出力信号間の位相又は周波数の差を示す制御信号を発生する。発振器は、出力信号を入力信号に同期的に追従させるため制御信号に応答する。制御信号にはその周期的な変動に従って発振器の出力信号が同期的な追従条件から偏差を生ずる傾向のある周期的変動が現れる。出力信号の位相は、上記偏差を打ち消すため、対応する制御信号の周期的な変動の位相に対し偏移される。

【0009】

【実施例】

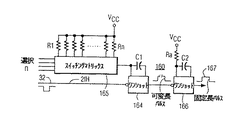

図1は本発明の一実施例による、特にテレビジョン受像機のための同期回路22を示す。同期回路22は、同期周波数の同期入力信号26に応答する第1の位相ロックループ24と、第1の位相ロックループ24からの出力167に応答する第2の位相ロックループ54を含む。同期入力信号26は、周波数1fHで 再現する標準ビデオ信号の水平走査成分又は同期である。ノンインターレース走査を得るため、同期回路22は、入力同期周波数の倍数、例えば、同期周波数の2倍、又は、2fH周波数でトリガ出力32を発生する。この目的のため、制御可能発振器34又はVCOは、32fHのように同期周波数のかなり大きい倍数の第1の周波数で出力信号を発生する。少なくとも一台の分周器42は、例えば、例示された2fHのような同期周波数の種々の倍数のトリガ信号を得るため、分割周期に亘って発振器34の出力をカウントダウンする。同期周波数の他の特定の倍数は、テレビジョン受像機の走査又は他の目的に使用することができる。

【0010】

2台の分周器42、44が例示した実施例に設けられている。位相選別分周器42は、発振器34の32fH出力から2fHの信号を発生するため、16分周するロード可能なカウンタ74を有する。もう一方の分周器44は、位相ロックループ24の入力信号26と位相比較するため帰還される1fH信号48を得るため、カウンタ72を用いて32分周する。2fHの出力信号32は、テレビジョン受像機の偏向回路52に結合される。例えば、偏向回路52は、図示していないがテレビジョン受像機の水平偏向巻線とフライバック変圧器に関連付けられ、第2の位相ロックループ54にトリガ又は基準信号を供給する。

【0011】

同期入力信号26と、発振器の出力36の周波数を分周して得られた帰還位相ロック信号48は、位相ロック信号48と、同期信号26を比較するため機能する位相比較器58に入力を印加する。位相ロックループ24は、二つの入力の位相アライメントの程度を表わす平均値を有するチューニング電圧62を発生する。位相比較器58とフィルタ68は、図3の(b)に示す如く、同期周波数の周期的成分と、直流電流成分又は平均値65とを有する出力波形を発生する。二つの入力信号26、48が位相及び周波数において調整され続ける場合、直流電流成分65は一定に維持される。信号26、48の中の何れか一方が、位相又は周波数において他方に先行、或いは、後続する場合、直流電流成分65は変化する。位相比較チューニング電圧62は、発振器34の制御を行うために一般的にローパス関数である伝達関数G(s)を有するフィルタ68を用いて発生される。上記の方法において、位相ロックループ24は、発振器の周波数及び位相を入力同期信号26にロック又は追従させようとし、かつ、ロック又は追従させ続ける。

【0012】

各分周器42、44は、繰り返し循環する分割周期を有する。16分周の分周器42は、4ビットの2進カウンタ74を有する。32分周の分周器44は、5ビットの2進カウンタ72を有する。32分周のカウンタは、位相比較器58と発振器34の動作によって1fH入力信号に同期されるが、16分周カウンタ74は、二つのカウンタの分割サイクルが32fH発振器36の同一周期に始まることを保証するためプリセットされる必要がある。このプリセットは、32分周カウンタ72の1fH出力をカウンタ74に結合するか、或いは、図1に示す如く、1fHライン49とカウンタプリセットトリガライン152を直接的に接続することにより行われる。次いで、カウンタ74の分割周期がカウンタ72の分割周期と同一の32fH周期で始まるが、16分周カウンタ74は、32分周カウンタ72の分割周期毎に2分割周期で循環する。これにより、上述の1fH変調問題が生じる可能性がある。

【0013】

本発明の特徴を実施する場合、カウンタ74は、並列にロードすることが可能であり、位相偏移回路142は、16分周カウンタ74の分割周期の位相を同期信号26の位相に対し偏移させ、トリガ信号32を発生するために使用される2fH周期の位相を調節するため設けられている。これにより、1fH入力周波数での同期回路22の2fHのカウントダウンされた出力32の変調を除去する利点が得られる。次いで、出力信号32は、元の同期入力26と正確な位相関係のあるドライブ信号167を得るよう遅延アライメントブロック160によって調節される。2fHドライブ信号は、次の位相ロックループ54への同期入力として使用される。位相ロックループ54は、通常のものであり、位相比較器258と、ローパスフィルタ268と、偏向回路52をドライブする制御形発振器234と、偏向回路52から位相比較器258への2fHフライバック帰還とにより構成される。他の遅延ブロック264が、例えば、水平方向の画像センタリングの位相を調節するため帰還信号路に挿入される場合がある。

【0014】

同期回路22の動作は、図2の(a)、(b)、及び、図3の(a)乃至(h)のタイミングチャートから評価することができる。インターレースビデオ信号フィールドに割り当てられた標準ビデオ信号は、連続的な垂直期間の間に第1及び第2の連続的なフィールドを含む。図2の(a)において、別の水平ラインm、m+2が夫々同期入力信号26の1fHパルスの間に伝送され、偶数及び奇数の番号が付けられたラインのフィールドは、完全なフレームを得るよう交互の垂直期間中に連続的な表示によってインターリーブされる。しかし、ノンインターレース走査の場合、水平走査レートは、図2の(b)においてドライブ信号167によって示される如く、ビデオの水平同期レートの2倍であることが必要である。図2の(a)及び(b)に示される如く、1fHパルスと2fHパルスは、アライメントされている。これらの信号は理想化され、その上、特定の実施例において、例えば、表示装置内のビデオを水平方向にセンタリングする手段として1fH入力に対し2fH信号を偏移させるために適当である。

【0015】

偏向回路に対する水平トリガパルスは、パルス間で同一の間隔によって分離されることが必要である。しかし、位相比較器58は、図3の(b)に示される如く、平均値65付近で1fHのレートで周期的に変化するチューニング電圧62を発生する。フィルタ68は、位相比較器の動作によって発生される周期的な成分を減少させるが、通常は、周期的成分を完全には除去しない。その上、広範囲のフィルタリングには、位相ロックループの応答を変化させる望ましくない点がある。かくして、チューニング電圧62は、図3の(c)に拡大して示されている如く、発振器34の出力36のパルス幅に周期的な1fHの変動を生じさせる。発振器34の出力36のパルス102は、例えば、チューニング電圧62がその平均65よりもかなり大きいとき、1fH周期全体の平均パルス幅より長い。チューニング電圧62が平均よりもかなり小さい場合に発生するパルス104は短くなる。上記変動は位相ロックループ24が1fHの同期入力信号26に同期し続けるよう機能する32分周カウンタ72の周期に悪影響を与えることはない。その理由は、信号26の周期全体に亘る長いパルスと短いパルスが32回のサイクルで平均化されるからである。

【0016】

16分周カウンタ74が32分周カウンタ72のカウントサイクルの先頭で始まるカウントサイクルで作動されるならば、変動周期がカウンタ74の1回の分割サイクルを超えて及ぶので、16分周カウンタ74はパルス幅の1fHの変動による影響を受ける。カウンタ74は、最初の2fHの分割周期の間、平均周期よりも長いパルス102を優先してカウントし、次いで、平均よりも短いパルス104を次の周期でカウントする。たとえ、位相ロックループ24が1fHで正確にロックされても、2fHの信号32は、図3の(d)に示す如く、対称性がなく、間隔Δt1は間隔Δt2よりも短い。水平走査をトリガするために、図3の(d)に示すような特徴を有する信号32を使用することにより、図4及び5の(a)に示す結果が得られる。連続的な2fHの水平走査ラインL1及びL2は、持続時間と表示位置が一致しない。図5の(a)に示すような周波数スペクトルは、所望の2fH信号に加えて、不必要な1fH及び3fHの周波数成分を発生する。図4に示す如く、実際的な影響は、ライン毎にラスタを分離することである。

【0017】

図1を参照するに、本発明の面によれば、ラスタラインの分離は、同期入力信号26に対して16分周の分周周期の位相を偏移させるための位相偏移回路142を設けることによって解決される。より詳細には、その間にカウンタ74が分割周期を通してカウントする16分周の周期は、1fH信号26、28に対し、かつ、位相ロックループ24の動作によって入力信号26に同期された32分周カウンタの分割周期に対してシフトされる。このシフトの量は、幾分長い方の32fHパルス102及び幾分短い方の32fHパルス104が分割周期毎に分類される点まで、16分周の分割周期を1fH信号26、28に対し移動させるのに十分な量であるので、図3の(e)において出力信号32によって示される如く、連続的な2fHの分割周期は実質的に時間的に一致する。換言すると、2fHの分割周期は、チューニング電圧62と帰還信号48に対し十分にシフトされるので、チューニング電圧62のACゼロ電位ライン65の周りのチューニング電圧62の平均値は、連続的な16分周のカウントサイクル又は分割周期の各々の間で同一である。図3の(a)乃至(h)には、上記の位相又は時間シフトが間隔t1−t2によって表わされている。

【0018】

1fH周期に対する16分周の位相シフトの範囲は、32fHサイクルの所定のカウント数に設定してもよい。この数は、16分周の周期と1fHの同期信号周期との間に最適な位相関係を得るため選択される。図5の(b)に示す如く、32fH周期、又は、最適な位相に最も近いカウントに対する位相を選択することにより、2fH水平トリガ周波数の1fHの変調は、18dB程度に著しく減少することが分かった。

【0019】

図1は図6乃至8と共に本発明の一実施例を示す図であり、この実施例において、16分周カウンタ74の分割周期の位相は、特定のカウント数の32fHサイクルによって、32分周カウンタ72の分割周期、及び、入力同期信号26に対しシフトされ得る。位相偏移回路142は、カウンタ72からの1fH信号49と、16分周カウンタ74のプリセット入力152の間に結合されたタイミング回路110を含む。位相偏移回路142は、16分周カウンタ74が2fHトリガ信号32上に出力パルスを発生するカウントを与え、かくして、分周サイクルの位相が決まる。図示した実施例において、上記カウントは、テレビジョン受像機のマイクロプロセッサ又はコントローラ115の出力からタイミング回路110を介して、例えば、1fH信号のエッジで16分周カウンタ74にカウントを予めロードすることにより設定される。カウンタ74は、次いで、もう一度予めロードされるまでの2分割周期又は2回の16カウントの進行の間に循環することが許容される。あらゆる特定のカウントは、2fH信号の所望の位相シフトを得るため必要に応じて16分の1の分解能でプリロードすることが可能である。16分周カウンタ74は、かくして、1fH信号の各サイクルでリセットされ、カウンタ74はカウンタ72に同期された状態を維持し、同時に、2fHの出力信号32は位相シフトのため対称的に形成される。

【0020】

プリロードされるカウントを設定するためマイクロプロセッサ115を使用することは一例に過ぎない。ハードワイヤジャンパー線、回路スイッチ又は他の手段は、位相選択入力132をカウンタ74の入力153に供給するため利用することができる手段である。2fHの分割周期の位相を同期信号26又は48の位相に対し偏移させる位相偏移回路142が図6により詳細に示され、かかるチューニング電圧62の平均値は、2fH出力信号32の連続的な周期の間で同一である。タイミング回路110は、32fH信号と同期し、各1fHサイクルの間にカウンタ74を予めロードする。32fHの発振器出力信号は、インバータ、ドライバ117を介して、2台の縦続されたD形フリップフロップ121、123のクロック入力と、4ビット2進カウンタ74とに結合される。カウンタ74は、カウンタ74の並列入力153に連結された4ビットバス132を介して、マイクロプロセッサ115により並列にロード、又は、プリセットされる。或いは、図示されていないシリアルバスの構成を利用することも可能である。第1のフリップフロップ121のD−入力は、インバータ119を介して、帰還された1fHの同期入力信号49に結合されているので、1fH周波数の状態の変化は、32fH信号の次の周期でフリップフロップ121の出力に現われ、その出力は、縦続内の次のフリップフロップ123のD−入力に結合されている。第2のフリップフロップ123の出力は、NANDゲート134の一方の入力に結合され、そのもう一方の入力は、インバータ136を介してフリップフロップのD−入力に結合されている。

【0021】

32番目のカウント時に、図3の(h)及び図6において信号49として示す如く、32分周カウンタ72の出力はハイになり、第1のフリップフロップ121の入力は、1カウント後のNANDゲート134の出力と同様にローになる。2進カウンタ74は、次いで、予め選択されたスタートカウントを用いてバス132からロードされる。1fHの信号49は、多数の32fHサイクルの間で状態を変化させないが、カウンタロード信号は、一つの32fHクロックサイクル後にハイになり、2進カウンタ74は電圧制御発振器からの32fHパルスをカウントし得るようになる。カウンタ74は、1fH信号49の次の立ち上がりエッジでもう一度プリロードされるまで、32パルス、即ち、2fHの2分割周期の間をカウントする。

【0022】

2進カウンタ74は、本発明の実施例によれば16分周カウンタとして動作する。2進カウンタ74の4出力は、少なくとも一つ、しかし、典型的には、多数の隣合う32fHのクロックサイクルの間にパルス出力を供給するゲート回路143に入力として結合される。ゲート回路143は、NANDゲート144と、NORゲート148を含み、それらの出力は別のNANDゲート154に結合されている。発振器34のカウントされた出力の16分周又は2fHレートで出力を供給するだけではなく、ゲート回路143は、各2fH周期中の3回の32fHクロックサイクルの間にローになる2fHの出力パルスを供給する。かかるパルス幅は、図7の論理表に示された如くの論理配置に起因して得られる。

【0023】

2進カウンタ74は、あらゆる4ビットの数にロードされてもよく、連続的に循環し続けることが可能である。バス132から2進カウンタ74にロードされるスタートカウントを選択することにより、各2fH周期中の3回のローレベルのサイクル位相位置は、2fH分割周期中に生じる32fHの16個のカウント位置の中の何処に置いてもよい。

【0024】

テレビジョン受像機のセットアップ機能の一部として、所望の位相偏移が同期信号26のタイミングエッジに対し2fH出力信号32のタイミングエッジとして選択されるので、チューニング電圧62の平均値は、トリガ信号32の連続的な2fH周期全体で等しい。発振器34の個々の32fHパルスは幅の変化が許容されるが、2fH分割周期は時間的に同一である。その理由は、長い方及び短い方のパルス102、104は、最初の周期で長い方のパルスが支配的にカウントされ、次の周期に短い方のパルスが支配的にカウントされるのではなく、連続的な周期に略等しく分配されるからである。この結果、連続的な2fH周期の各々の間隔は、実質的に同一である。図5の(b)に示す如く、出力信号32の周波数スペクトルは、不所望な変調が実質的に補正されている。上述の如く、1fH周波数の変調は除去されるが、2fH信号32上の位相位置の変化は、1fH周期に対し動かされている。第2の位相ロックループ54に結合された偏向回路52が入力信号26に同期したステップで動作するよう、例えば、1fH信号でアライメントされた2fHパルスを用いて2fH信号と同期入力信号の間で特定の位相関係を維持する利点が得られる。本発明の別の特徴によれば、2fH出力信号32の位相関係は、図1に概略的に示され、図8の特定の実施例に示される如く、遅延アライメント回路160を用いて同期入力信号26に対し調節可能である。図8において、遅延は、例えば、カウンタ74への入力153として結合された同一の4ビットデータ信号を用いて16分周カウンタ74のプリロードカウントの設定と整合された方法で設定される。遅延アライメント回路160は、縦続した2台のワンショト164、166からなる。第1のワンショット164は、fH出力信号32と、第2の位相ロックループ54に供給される2fHドライブ信号167のエッジ間の時間的シフト又は遅延を制御する。第2のワンショット166は、ドライブ信号167のパルス幅を制御する。

【0025】

ワンショット164は、例えば、図1のタイミング回路110を介してマイクロプロセッサ115によって制御された選択可能な遅延を提供する。遅延量は、トリガ出力信号32は予め設定可能な2進カウンタ74によってシフトされる32fHサイクルの数と整合するセットアップ機能として選択してもよい。例えば、ワンショット164の調節可能な遅延は、分周器142内で組み込まれる遅延に起因した画像のシフトを補償するよう設定される。

【0026】

ワンショット164のパルス幅は、キャパシタC1と、スイッチングマトリックス165を介してワンショット164に結合された抵抗R1−Rnの中から選択された一つの抵抗の時定数によって定められる。図示した例において、16台の抵抗R1−Rnの中の一つがタイミング回路110からの4ビット入力によって選択される。ワンショット166のパルス幅は、キャパシタC2と抵抗Raの値により第2の位相ロックループ54で使用するのに適当な幅に固定される。

【0027】

図示し、かつ、説明したような逓倍位相ロックループ24において、出力信号32とドライブ信号167は、受信したビデオ同期信号26の第1の倍数で発生される。電圧制御発振器34は、受信した信号周波数の第1の倍数よりも大きい第2の倍数でクロック信号36を供給する。上述の位相アライメントを得るため、分周器74の分割周期の間に位相シフトを挿入することにより、出力信号32の変調は妨げられる。ドライブ信号167の位相は、必要とされるドライブ位相に修正される。

【0028】

遅延回路及び分周器が、互いに、及び、ローパスフィルタと発振器に対し異なる配置で結合された本発明の幾つかの構成を図1及び9乃至11に示す。図12の(a)−(f)は、図9及び10において符号が付けられた点での信号A−Fのタイミングを示す図であり、図3の(a)−(h)及び図1と対比できる。

図9及び10において、位相ロックループ210、330の各々は、1fH同期信号Dに直列に結合された位相比較器201と、ローパスフィルタ202と、VCO203とを有し、加えて分周器204と対称的な発振器の出力を保証するために必要とされる遅延回路205とを含む位相比較器201への帰還路を有する。VCO203には、図示されていない走査回路と同一の周波数で動作し、1fH同期信号Dに同期された対称性のある2fHドライブ信号を発生する利点がある。位相比較器201の出力Eはローパスフィルタ202に結合され、ローパスフィルタ202の出力FはVCO203に対する制御信号又はチューニング電圧である。何れの場合でも、VCO203の出力Aは、対称性のある2fH信号であり、交番サイクルの間隔ta−tb及びtb−tcは、同一である。図9において、遅延アライメント回路206は、図1の第2の位相ロックループ54のような別の回路をドライブするために必要とされるドライブ位相を得るため出力Aを調節する。

【0029】

図9−11において、対応する回路素子を識別するために同一の参照番号が使用されている。図10における本発明の回路は、2fH位相ロックループ220に同一の遅延及び帰還機能を提供するが、一つの遅延、即ち、帰還路に挿入された遅延回路205だけを必要とする。遅延回路205を分周器204の上流に置くことにより、第2の位相ロックループ回路54に結合された出力信号は、位相が正しく、かつ、同時に帰還信号B2は、対称性のある発振器動作を得るためVCO203の出力Aに対し位相が適切に調節される場合がある。

【0030】

図12の(a)−(f)に示す如く、VCO203の出力Aは、何れの場合も対称性があるが、例えば、間隔tc−tdによって、同期入力D及びVCO203のチューニング電圧Fとは位相がずれている。図9及び12の(d)において、1fHの帰還信号は同期入力Dと位相がずれている。図10及び12の(e)において、帰還信号B2は、対称性があるだけではなく、同期入力Dと位相が合っている。次いで、分周器204は、位相比較器201への入力のため発振器周波数を分周する。VCO203を帰還路に沿った信号C又はB2と位相をずらせて動作させることにより、両方の回路は、対称性、即ち、1fH変調のない2fH信号を発生し、両方の回路は、回路をロックし続ける位相比較器201に位相比較信号Cを供給する。

【0031】

図11の位相ロックループに示すような本発明の他の構成は、対称性のある出力でVCOを動作させるため帰還路ではなく、むしろチューニング電圧又は制御信号Fの経路に遅延を発生させる。図11において、アナログ遅延回路207は、この目的のためにローパスフィルタ202の出力に結合されている。ローパスフィルタと遅延機能は、例えば、多極伝達関数を有する一つのアナログ回路内に作成してもよい。

【0032】

図示した本発明の全ての構成において、位相ロックループは、1fHの入力水平同期信号と発振器の出力信号の間の位相又は周波数差を表わす発振器制御信号チューニング電圧を発生し、ここで、出力信号の周波数は、入力信号の周波数よりも高く、入力信号の周波数の整数倍である。位相検波器は、フィルタリング後でさえ、周期的、即ち、1fHレートの変動を示すチューニング電圧を発生する。発振器の制御入力に印加されたとき、チューニング電圧は、同期した追従条件、即ち、発振器の出力信号のその平均周期からの偏差を生じさせる。かくして、チューニング電圧の1fHの周期的変動により、2fHの発振器出力は平均周期から1fHの変動を生じる。この変動は、同期入力信号のより大きい別の倍数で走査ドライブを提供する他の発振器にも発生する可能性がある。位相ロックループによって供給される周波数制御のため、発振器の出力の平均周期は入力同期信号の平均周期に依然として追従する。

【0033】

チューニング電圧の周期的な変動の位相に対し発振器の出力信号の位相を制御することにより、発振器の出力の偏差は打ち消される。図1において、これは、そこから分周器42がカウントダウンを開始する32fHのVCO34の適当なサイクルを選択して、2fH出力信号の位相を直接偏移させることによって実現される。発振器の偏差は、図9及び10においては発振器帰還信号の位相を偏移させることにより、図11においては位相検波器201によって発生されるチューニング電圧の位相を直接偏移させることにより打ち消される。

【図面の簡単な説明】

【図1】テレビジョン受像機に適用された本発明の同期回路の素子を示す略ブロック図である。

【図2】(a)及び(b)はノンインターレース表示テレビジョン受像機のビデオ同期と水平走査トリガ信号を比較するタイミングチャートである。

【図3】(a)乃至(h)は、図1の回路によって発生された水平同期信号、チューニング電圧、発振器出力及びトリガ信号を比較するタイミングチャートである。

【図4】ラスタ分離の影響を表わす表示例の図である。

【図5】(a)及び(b)は、夫々、図3の(d)に示された信号と、本発明の特徴に従って補正された信号を表わす周波数スペクトルである。

【図6】2fHトリガ信号をビデオ同期信号に対し偏移させる回路の一例を示す詳細な回路図である。

【図7】図6に従う回路の出力を示す論理表である。

【図8】2fHトリガ信号の位相を再配置する遅延アライメント回路の一例を示すブロック図である。

【図9】帰還路に第1の遅延及び出力に第2の遅延を有する同期回路の第1の新規な構成例を示すブロック図である。

【図10】分周器の前の帰還路に遅延を有する第2の新規の構成例を示すブロック図である。

【図11】ローパスフィルタと遅延回路の組合せを含む第3の新規の構成例を示すブロック図である。

【図12】(a)乃至(f)は、図9及び10の回路によって発生された水平同期信号と、チューニング電圧と、発振器出力及びトリガ信号を比較するタイミングチャートである。

【符号の説明】

22 同期回路

24,54,210,220,230 位相ロックループ

26 同期入力信号

32 トリガ出力信号

34,203,234 VCO(制御可能発振器)

36 クロック信号

42,44,204 分周器

48 1fH信号(帰還位相ロック信号)

49 1fHライン

52 偏向回路

58,201,258 位相比較器

62 チューニング電圧

65 直流電流成分

68 フィルタ

72,74 カウンタ

102,104 パルス

110 タイミング回路

115 マイクロプロセッサ

117,119,136 インバータ

121,123 D形フリップフロップ

132 位相選択入力

134,144,154 NANDゲート

142 位相偏移回路

143 ゲート回路

148 NORゲート

152 カウンタプリセットトリガライン

153 カウンタの入力

160 遅延アライメント回路

164,166 ワンショット

167 位相ロックループの出力

201 位相検波器

202,268 ローパスフィルタ

205,264 遅延回路

207 アナログ遅延回路

Claims (1)

- 同期入力信号を位相ロックループで出力される位相ロック信号と比較して、同期周波数で周期的に変動するチューニング信号を出力する位相比較手段と、

前記チューニング信号に含まれる周期的に変動する成分を低減するためのフィルタリング手段と、

前記フィルタリング手段の出力を受け、前記同期周波数の整数倍の周波数であって、該周波数が前記チューニング信号の変動につれて変動する出力信号を出力する発振手段と、

前記発振手段からの前記出力信号を前記同期周波数の整数倍と同じ数で分周し、前記位相ロック信号を発生する分周手段と、

前記発振手段の前記出力信号の変動の平均周期が前記チューニング信号の周期的な変動により作用されないように、前記同期入力信号に対して前記分周手段からの前記位相ロック信号を遅延する手段を有する位相偏移手段と、

を備えることを特徴とする同期回路。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US08/257980 | 1994-06-10 | ||

| US08/257,980 US5565928A (en) | 1994-06-10 | 1994-06-10 | Circuit for generating a scan at a multiple of a synchronizing signal |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH08279927A JPH08279927A (ja) | 1996-10-22 |

| JP3737838B2 true JP3737838B2 (ja) | 2006-01-25 |

Family

ID=22978592

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP14344295A Expired - Fee Related JP3737838B2 (ja) | 1994-06-10 | 1995-06-09 | 同期回路 |

Country Status (9)

| Country | Link |

|---|---|

| US (1) | US5565928A (ja) |

| EP (1) | EP0692908B1 (ja) |

| JP (1) | JP3737838B2 (ja) |

| KR (1) | KR100379313B1 (ja) |

| CN (1) | CN1062096C (ja) |

| DE (1) | DE69531913T2 (ja) |

| MY (1) | MY113714A (ja) |

| SG (1) | SG45102A1 (ja) |

| TW (1) | TW449977B (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| SE520064C2 (sv) * | 1997-03-18 | 2003-05-20 | Telia Ab | Förbättringar av, eller med avseende på, MPEG-2 bredbandsmultimediaterminaler för audiovisuell kommunikation, eller distribution |

| EP0869619B1 (fr) * | 1997-04-02 | 2006-07-05 | Koninklijke Philips Electronics N.V. | Circuit intégré comportant une boucle de contrôle de phase |

| US6263034B1 (en) * | 1998-03-25 | 2001-07-17 | Vitesse Semiconductor Corporation | Circuit and technique for digital reduction of jitter transfer |

| JP3270406B2 (ja) * | 1998-12-08 | 2002-04-02 | エヌイーシーマイクロシステム株式会社 | ポジション制御回路 |

| JP3324647B2 (ja) * | 1999-08-23 | 2002-09-17 | 日本電気株式会社 | 水平同期信号に対する位相同期ループ回路 |

| US6798257B1 (en) * | 2001-03-21 | 2004-09-28 | Cisco Technology, Inc. | Method and apparatus for providing multiple clock signals on a chip using a second PLL library circuit connected to a buffered reference clock output of a first PLL library circuit |

| KR102546646B1 (ko) * | 2018-08-28 | 2023-06-23 | 매그나칩 반도체 유한회사 | 오실레이터 주파수 컨트롤러를 포함하는 디스플레이 구동 ic |

| TWI666871B (zh) * | 2019-01-17 | 2019-07-21 | 瑞昱半導體股份有限公司 | 二倍頻裝置及方法 |

| CN110530292A (zh) * | 2019-09-19 | 2019-12-03 | 北京天远三维科技股份有限公司 | 一种基于无线同步的扫描系统及扫描方法 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3891800A (en) * | 1971-03-16 | 1975-06-24 | Philips Corp | Line time base in a television receiver |

| JPH06101860B2 (ja) * | 1986-04-11 | 1994-12-12 | ソニー株式会社 | 時間軸補正装置 |

| JPH0832059B2 (ja) * | 1987-03-09 | 1996-03-27 | 株式会社日立製作所 | ディジタルテレビジョン信号処理装置 |

| US4791488A (en) * | 1987-08-12 | 1988-12-13 | Rca Licensing Corporation | Line-locked clock signal generation system |

| CA2038778C (en) * | 1990-03-26 | 1995-10-24 | Ronald Eugene Fernsler | Synchronized horizontal scanning at horizontal frequency multiples |

| US5121086A (en) * | 1991-04-09 | 1992-06-09 | Zenith Electronics Corporation | PLL including static phase error responsive oscillator control |

| JPH05207327A (ja) * | 1992-01-27 | 1993-08-13 | Mitsubishi Electric Corp | 水平同期回路 |

-

1994

- 1994-06-10 US US08/257,980 patent/US5565928A/en not_active Expired - Lifetime

-

1995

- 1995-03-28 TW TW084103015A patent/TW449977B/zh not_active IP Right Cessation

- 1995-05-31 EP EP95108283A patent/EP0692908B1/en not_active Expired - Lifetime

- 1995-05-31 DE DE69531913T patent/DE69531913T2/de not_active Expired - Fee Related

- 1995-06-02 MY MYPI95001453A patent/MY113714A/en unknown

- 1995-06-06 SG SG1995000597A patent/SG45102A1/en unknown

- 1995-06-09 JP JP14344295A patent/JP3737838B2/ja not_active Expired - Fee Related

- 1995-06-09 KR KR1019950015118A patent/KR100379313B1/ko not_active IP Right Cessation

- 1995-06-10 CN CN95105626A patent/CN1062096C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| DE69531913D1 (de) | 2003-11-20 |

| EP0692908B1 (en) | 2003-10-15 |

| MY113714A (en) | 2002-05-31 |

| TW449977B (en) | 2001-08-11 |

| EP0692908A3 (ja) | 1996-02-07 |

| CN1130321A (zh) | 1996-09-04 |

| JPH08279927A (ja) | 1996-10-22 |

| SG45102A1 (en) | 1998-01-16 |

| KR100379313B1 (ko) | 2003-06-28 |

| EP0692908A2 (en) | 1996-01-17 |

| KR960003292A (ko) | 1996-01-26 |

| US5565928A (en) | 1996-10-15 |

| DE69531913T2 (de) | 2004-05-06 |

| CN1062096C (zh) | 2001-02-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4679005A (en) | Phase locked loop with frequency offset | |

| JP3737838B2 (ja) | 同期回路 | |

| JP3703544B2 (ja) | インターレース形ビデオの垂直パン装置 | |

| KR200204617Y1 (ko) | Lcd모니터의 수직화면 제어장치 | |

| US5977836A (en) | Method and apparatus for controlling an output frequency of a phase locked loop | |

| JP3655275B2 (ja) | 水平偏向システム | |

| US5223931A (en) | Synchronized scanning at horizontal frequency | |

| US4660080A (en) | Synchronization circuit responsive to time-multiplexed signals | |

| US5329367A (en) | Horizontal blanking | |

| KR100360958B1 (ko) | Hout 위치 제어 회로 및 멀티 싱크 모니터 | |

| CA2038778C (en) | Synchronized horizontal scanning at horizontal frequency multiples | |

| JPH1023293A (ja) | 同期発生装置と画像表示装置 | |

| JPS62216588A (ja) | 水平位相シフト回路 | |

| GB2262408A (en) | Horizontal blanking for multiple rate scanning | |

| JPH10191093A (ja) | デジタル水平フライバック制御回路 | |

| MXPA95002546A (en) | Synchronized exploration circuit | |

| GB2183122A (en) | Synchronizing signal generating apparatus for PAL system | |

| JPH04188961A (ja) | 位相可変型位相同期回路 | |

| JPH04351083A (ja) | マルチダウンコンバータ用同期信号発生回路 | |

| KR19980064261A (ko) | 디지탈 수평 귀선 제어 회로 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050105 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050208 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20050506 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20050511 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050808 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20051011 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20051028 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081104 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091104 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |