JP3674881B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP3674881B2 JP3674881B2 JP06883396A JP6883396A JP3674881B2 JP 3674881 B2 JP3674881 B2 JP 3674881B2 JP 06883396 A JP06883396 A JP 06883396A JP 6883396 A JP6883396 A JP 6883396A JP 3674881 B2 JP3674881 B2 JP 3674881B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- wiring

- output

- input

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Bipolar Transistors (AREA)

- Semiconductor Integrated Circuits (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Bipolar Integrated Circuits (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、たとえばモノリシックマイクロ波IC(MMIC)などに利用できる、電力増幅用の縦型構造トランジスタを同一基板上に複数個含む構成の半導体装置に関する。

【0002】

【従来の技術】

最近、マイクロ波帯での電力増幅用トランジスタの需要が高まっている。中でも、ヘテロジャンクションバイポーラトランジスタ(以下HBTと略す)に代表される縦型構造トランジスタが高効率増幅を実現する手段として注目されている。その理由は、現在実用化されているGaAsFETに比較して、HBT等は、高い利得と低いアウトプットコンダクタンスを持つからである。

【0003】

上記縦型構造トランジスタは、一般に知られているように、高電流密度で動作するため、必然的に発熱密度が高くなる。したがって、適正に動作させるためには、基板表面に形成された接合部(pn接合部)の発熱を、効率良く半導体基板外へ逃がさなければならない。

【0004】

そこで、本願発明者らは、半導体基板上に、エミッタ突起電極を基板表面より突出した状態にしてトランジスタが設けられた縦型構造トランジスタおよびこれを用いた集積回路等の半導体装置を提案している(例えば、H.Sato etal.、Bump Heat Sink technology”15th Annual GaAs IC Symposium Technical Digest p337−340)。これを、第1従来例という。かかる第1従来例による場合は、基板表面より突出したエミッタ突起電極にて放熱する構造であるため、基板表面に形成された接合部の発熱を更に効率良く逃がすことができる上、引き出し線のインダクタンスおよび寄生容量等を低減でき、マイクロ波帯での電力増幅用として実用に供することができる。但し、適当な出力を確保するためには、単位トランジスタを並列に接続する必要があるが、上記文献ではその並列接続の具体的方式については開示されていない。

【0005】

また、本願発明者らは、並列接続の具体的方式に関し、図9に示すように上記のような縦型構造トランジスタ40を相互に接続する方式を提案している(特開平6−104274号)。この提案を第2従来例という。この第2従来例では、フィンガー状のトランジスタ素子真性動作部の長手方向を、集合トランジスタの入力側と出力側とを結んだ線(エミッタトップ型でエミッタ接地を用いた際にはベース側とコレクタ側とを結んだ線)と垂直になして配置している。これは、図9および図10に示すようなトランジスタ配置を取り易くするためである。

【0006】

更に、並列接続の具体的方式についての別の従来例としては、図11に示す方式のものが提案されている(U.S.patent 5、321、279)。これを、第3従来例という。この第3従来例でも、フィンガー状のトランジスタ素子真性動作部の長手方向を、集合トランジスタの入力側と出力側とを結んだ線(エミッタトップ型でエミッタ接地を用いた際にはベース側とコレクタ側とを結んだ線)と垂直になして配置している。また、第3従来例ではバンプによる放熱は試みられていない。

【0007】

【発明が解決しようとする課題】

ところで、上記第1、第2従来例においては、次のような(a)〜(e)の問題があった。

【0008】

(a)図9のような配列では、各単位トランジスタから見た、入力側インピーダンスと出力側インピーダンスとに著しい不均一が生じる。また、入力側および出力側のそれぞれから見て、トランジスタ配置が左右対称でないため、電力分配/結合に不均一が生じる。その結果、電力合成効率が低下し、所望の出力が出にくくなるという問題があった。

【0009】

(b)また、CADでトランジスタのデザイン配置作業を行う際、枝のデザインが場所毎に違うためデザイン作業が複雑な上、パターンの自動生成に著しく不利となる。

【0010】

(c) また、図10のような配列を採ろうとすると、大出力化のために、さらにベース配線62やコレクタ配線63の枝を伸ばした際、枝と枝との距離はおのずと限界があるので、枝の幅を狭くした部分が生ずる。すると、部分的に電気抵抗の高いところができ、発熱が大きくなって信頼性の低下を引き起こす。また、上述した入力側インピーダンスと出力側インピーダンスとの著しい不均一性や電力分配/結合での不均一性の問題がさらに顕著になる。

【0011】

(d)また、単に、複数個の縦型トランジスタが基板中心に向かうにつれて相互のトランジスタ間隔を広くするように配置するだけでは、特に集積回路になった際、十分な均熱化が達成できない。その結果、比較的大きなチップ面積を必要とし、工期がかかると共にコスト高になるという問題があった。

【0012】

(e)また、大出力化のために並列数を増やしたトランジスタでは、出力インピーダンスが低下する。通常、低損失化のためチップ外に設けられる出力整合回路としてのアンテナ系では50Ωに設定されており、この50Ωに変換する際、必要とされる変換比が大きくなり、結果として変換損失が大きくなるという問題があった。

【0013】

一方、第3従来例においては、次のような(f)および(g)の問題があった。

【0014】

(f)図11のような配列では、接続できるユニットトランジスタ数におのずと限界があり、大出力化が困難になるという問題がある。

【0015】

(g)また、図11のようなトランジスタ配列を1集団として、これをさらに並列接続することも考えられるが、その場合には占有面積が大きくなりコスト高になるという問題があった。

【0016】

このように種々の問題が生ずるため、従来においては、マイクロ波/ミリ波帯での電力増幅用として高出力、高性能の縦型構造トランジスタを用いたMMICなどの半導体装置を、低コストで実用に供することが困難であった。

【0017】

本発明は、このような従来技術の課題を解決すべくなされたものであり、マイクロ波/ミリ波帯での電力増幅用として実用に供することのできる、縦型構造トランジスタ集合体による高出力かつ高性能な半導体装置を提供することを目的とする。

【0018】

【課題を解決するための手段】

本発明の半導体装置は、縦型構造トランジスタがアレイ状に配設されると共に並列接続された半導体装置において、該縦型構造トランジスタが、そのフィンガー状のトランジスタ素子真性動作部の長手方向をトランジスタアレイにおける列方向と平行になし、かつ、列方向のトランジスタ間隔を中央部から離れるに伴って小さくして配置されており、列方向に延びる交互に配列された入力用幹配線および出力用幹配線と、該入力用幹配線から行方向に延びる入力用枝配線と、該出力用幹配線から該入力用枝配線の間に行方向に延びる出力用枝配線とを備える配線に対し、トランジスタアレイが、その行方向において複数個の縦型構造トランジスタ毎に入力用幹配線および出力用幹配線によって挟まれ、かつ、その挟まれた複数個の縦型構造トランジスタの各々が該入力用枝配線および該出力用枝配線にて挟まれており、更に、該トランジスタアレイの列方向の一方側を入力側となし、かつ、他方側を出力側としてあり、そのことにより上記目的が達成される。

【0019】

本発明の半導体装置において、前記トランジスタアレイが、列方向のトランジスタ間隔を中央部から離れるに伴って小さくして配置されていることに加えて、入力側のトランジスタ間隔を対応する位置における出力側のトランジスタ間隔よりも大きくなしてある構成とするのが好ましい。

【0020】

本発明の半導体装置において、前記入力用幹配線および出力用幹配線によって行方向に挟まれた縦型構造トランジスタを1ブロックとして、各ブロック間の離隔間隔がトランジスタアレイの中心部から行方向に離れるに伴って小さくなっている構成とするのが好ましい。

【0021】

本発明の半導体装置において、前記配線の出力側に略三角形のメタルパターンが設けられている構成とするのが好ましい。

【0022】

本発明の半導体装置において、前記トランジスタアレイが、フィンガー状のトランジスタ素子真性動作部の直上と該真性動作部のフィンガー長手方向と直交する方向に位置する非真性動作部とに跨るようにバンプ電極を具備する構成や、縦型構造トランジスタがエミッタトップ型またはコレクタトップ型であって、トランジスタアレイがトップ層の接合部における電極に対し、そのトップ層電極の上面から、そのトップ層の長さ方向とは垂直な方向の両側に向かう状態で引き出し電極がアーチ状に引き出され、該引き出し電極の上にバンプ電極を有する構成とすることができる。また、前記縦型構造トランジスタがエミッタトップ型であり、かつ、エミッタ接地の場合は、該トランジスタアレイの列方向の一方側が前記配線のベース側であり、列方向の他方側が該配線のコレクタ側である。

【0023】

以下に、本発明の作用につき説明する。

【0024】

本発明の半導体装置にあっては、縦型構造トランジスタが、そのフィンガー状のトランジスタ素子真性動作部の長手方向を、トランジスタアレイにおける列方向と平行になしてあり、かつ、配線が、列方向に延びる交互に配列された入力用幹配線および出力用幹配線と、該入力用幹配線から行方向に延びる入力用枝配線と、該出力用幹配線から該入力用枝配線の間に行方向に延びる出力用枝配線とを備え、トランジスタアレイの列方向の一方側を入力側となし、かつ、他方側を出力側としてあるので、幹配線や枝配線の配置が容易にできる。その結果、上記(a)、(b)、(f)および(g)の各問題が解決される。

【0025】

また、列方向のトランジスタ間隔を中央部から離れるに伴って小さくして配置されているので、列方向における設計を各行方向に適用すればよく、また、トランジスタアレイの中央部に熱がこもり難くなる。その結果、上記(c)および(d)の各問題が解決される。

【0026】

また、トランジスタアレイが、列方向の間隔を中央部から離れるに伴って小さくして配置されていることに加えて、入力側の間隔を対応する位置における出力側の間隔よりも大きくなしてある構成とすることにより、入力側の放熱がされ難い状態を改善できる。その結果、上記(d)の問題が解決される。

【0027】

また、配線の出力側にメタルパターンが設けられた構成とすることにより、出力側のインピーダンスを等価的に上昇させ得る。その結果、上記(e)の問題が解決される。

【0028】

【発明の実施の形態】

以下、図面を参照して本発明に係る半導体装置の実施形態を説明する。

【0029】

図1は、本実施形態に係る半導体装置の基本構成を示す平面図である。この半導体装置は、半絶縁性GaAs基板1の上に、縦型構造トランジスタ3を用いてマイクロ波電力増幅用のnpnエミッタトップ型HBT2が形成されている。このHBT2は、携帯電話用3段パワーアンプMMICを構成するものである。

【0030】

上記HBT2は、複数の縦型構造トランジスタ3がアレイ状に配設され、かつ、並列接続されている。この構成のHBT2のトランジスタ配置において、図2に示すように、フィンガー状のトランジスタ素子真性動作部(図中に黒く着色した部分)の長手方向を、トランジスタアレイの入力側(左側)と出力側(右側)とを結んだ線(縦型構造トランジスタ3がエミッタトップ型でエミッタ接地を用いた場合にはベース側とコレクタ側とを結んだ線)と平行にして各縦型構造トランジスタ3が配置されている。

【0031】

トランジスタアレイの並列接続用の配線は、図1に示すように、左を入力側、右を出力側になるように配置した場合、トランジスタアレイの行方向において、3個×8個のトランジスタ素子真性動作部毎に分割する入力用幹配線4および出力用幹配線5を有する。入力用幹配線4は、図1の左側において入力主線6に接続され、一方の出力用幹配線5は同右側において出力主線7に接続されている。また、入力用幹配線4からは行方向に延びる入力用枝配線8が分岐され、出力用幹配線5からは行方向に延びる出力用枝配線9が分岐されている。入力用枝配線8は出力用枝配線9の間に入り込むように設けられている。全体としては、枝配線8、9に3個のトランジスタ3を配置したものを8列、これを1ブロックとして、4ブロックが、それぞれ幹配線4、5によって分割されて、トランジスタアレイおよび配線が配置されている。

【0032】

上記列方向のトランジスタ間隔は、トランジスタアレイの中心から離れるに従って小さくなるように配置されている。この配置の場合は、トランジスタアレイ中央部分に熱がこもる現象を、軽減緩和することができる。その理由は、トランジスタ間隔を同一にした場合はトランジスタの放熱路の重なり部分が中央部で高密度となるが、本発明の間隔にすることで、放熱路の重なり部分を中央部で減少させることが可能となるからである。

【0033】

この場合において、第2従来例との相違は以下の通りである。第2従来例の場合には、中央部でのユニットトランジスタの粗密を、トランジスタ個々の配置を変化させている。具体的には、図10に示すように、左下から2行2列、2行3列、2行4列、3行2列、3行4列、4行2列、4行3列、4行4列、の計8個のユニットトランジスタの配置を微妙に変化させている。これに対して、本発明ではトランジスタ個々の配置を変化させるのではなく、枝配線に付属したユニットトランジスタ全体を平行移動させている。これによって、本発明による場合には、配列の設計を容易に実現できる。

【0034】

また、本発明においては、列方向のトランジスタ間隔において、トランジスタアレイの中心から左右に相対応する列方向のトランジスタ間隔を比べた場合、入力側の列方向間隔が出力側の列方向間隔に比較して大きくなっている。具体的には、図3に即して説明すると、Aがトランジスタアレイの中心部、その左右にBとb、Cとc、Dとdが各々相対応する列方向間隔であるが、それぞれの間隔は、A=78μm、B=77μm、b=73μm、C=73μm、c=68μm、D=63μm、d=58μmとなっている。

【0035】

このように列方向のトランジスタ間隔において、トランジスタアレイの中心から左右に相対応する列方向の間隔を比べた場合、入力側の列方向間隔が出力側の列方向間隔に比較して大きいことは、特に集積回路になった際、十分な均熱化を達成する効果をもつ。この理由を以下に説明する。一般に、パワートランジスタは常に基板(半導体チップ)1の中心部に位置するとは限らない。特に、本発明で形成しようとするような大電力のパワートランジスタの場合、多段のパワーアンプの最終段に使用される。また、最終段の出力整合回路は、低損失化のために半導体チップ外に設けられる場合が多い。このため、図1に示すようにパワートランジスタは基板1の中央部から外れ、トランジスタの出力側は、入力側に比較してチップ周辺部に近く、チップ周辺部には出力用バンプ11の他、接地用バンプ21も具備しているため、これらを経由しての放熱も行われる。一方、入力側は、HBT2が存在しないうえ、入力用、その他のI/O用、接地用のバンプ20も数多くあるので一見放熱がよさそうであるが、最終的に放熱の経路となるバンプ20までの距離が遠いうえに前段のトランジスタからの放熱もあり、実際には放熱されにくい。したがって、この問題は、複数個の縦型構造トランジスタが基板中心に向かうにつれて相互のトランジスタ間隔が広くなることに加え、入力側の列方向間隔が、出力側の列方向間隔に比較して大きくとることにより解決できる。特に、集積回路になった際、これによる均熱化の効果が大きい。また、この効果は、通常のワイヤボンド構造やPHS(plated heat sink)構造でも有効であるが、特に、トランジスタアレイ内の熱分布が下地や周辺バンプの熱伝導状況に左右されやすいバンプ放熱構造の場合には、有効性が顕著である。

【0036】

この列方向における入力側のトランジスタ間隔を出力側のトランジスタ間隔に比較して大きくする場合の放熱性は、下地によって変動する。この場合、トランジスタ間隔は、上記数値を変更すべきである。本願発明者らの検討によると、例えば厚さ0.5mmの同時焼成AlN基板LCC(リードレスチップキャリア)を用い、プリント基板上に半田付け実装している場合、上記数値の各々において、±5μm以内での微調整により放熱性の良好な結果が得られている。

【0037】

また、幹配線についても、中央部の幹配線を最も太く、中央から離れるに従って幹配線を徐々に細くし、上述した各ブロックの間隔を調整している。具体的には、図3に即して説明すると、トランジスタアレイ中央部に位置する出力用幹配線5は幅60μm、トランジスタアレイ中央部から離れた2本の入力用幹配線4はそれぞれ幅45μmとなっている。このようにすることにより、トランジスタアレイ中央部分に熱がこもる現象を軽減緩和する効果を、さらに徹底することができる。

【0038】

また、1ブロックの構成が、各ブロックにおいて同様になった構造となっている。上記構造をとることにより、CADでトランジスタのデザイン配置作業を行う際、枝のデザインが場所毎に違う問題が解決され、パターンの自動生成が著しく有利になる。また、入力側、出力側のそれぞれから見て、トランジスタ配置は対称になっている。つまり、入力側と出力側とを結ぶ線(左右方向の線)に対して、上下対称になっている。これによっても、CADでトランジスタのデザイン配置作業を行う際において、パターンの自動生成がより有利になる。また、入力側、出力側のそれぞれから見たトランジスタ配置が対称であるため、電力分配/結合に不均一が生じない。

【0039】

上述した各ブロックが幹配線によって分割された構造は、フィンガー状のトランジスタ素子真性動作部の長手方向を、トランジスタアレイの入力側と出力側とを結んだ線(エミッタトップ型でエミッタ接地を用いた際にはベース側とコレクタ側とを結んだ線)と平行にして、トランジスタを配置することにより、とり易くなる。

【0040】

また、入力用枝配線と出力用枝配線とを交互に入り込ませた構成であるので、配線の交差部が無く、特性劣化を防ぐ効果がある。また、繰り返し形状となるため、CADによるパターンの自動生成に有利である。

【0041】

また、このような全体的な構成により、各単位トランジスタから見た、入力側インピーダンスと出力側インピーダンスとの均一が著しく緩和される。また、上述した全体の結果として、同一出力のパワートランジスタが、従来法に比較して著しく小型にできるので、入出力でのパワー合成が不要になり、チップコストを低廉化できる。

【0042】

図4は、出力側(エミッタトップ型でエミッタ接地を用いた際にはコレクタ側)に、略三角形のメタルパターン10を具備する様子を示す。このメタルパターン10は、たとえば略2等辺三角形であり、長辺は1160μm、高さは400μmとなっている。このようなメタルパターン10を具備する構成とした場合は、トランジスタアレイ出口のインピーダンスを等価的に上昇させるインピーダンス変換機能をもつ。

【0043】

一般に、大出力化のため、並列数を増やしたトランジスタでは、出力インピーダンスが低下するが、上記略三角形のメタルパターン10によって、パワートランジスタの出力端での出力インピーダンスが等価的に上昇する。これにより、後段での変換比の負担を軽減でき、アンテナ系に適用しても変換損失を低減できる。

【0044】

また、メタルパターン10における略2等辺三角形の頂点には図1に示すように円形の出力バンプ(直径:60μmφ)11を具備している。なお、出力バンプ11は図1では1個だが、図5に示すように同型の出力バンプ11を2個設けるようにしてもよく、更に多く設けるようにしてもよい。また、図6に示すように、小型の出力バンプ(直径:20μmφ)11aを多数、たとえば18個程度配置してもよい。図5の場合では、出力バンプの1個当たりの電流量を低減し、出力バンプでの電圧降下を低減できる効果をもつ。一方、図6の場合では、表皮効果を低減できるので、出力バンプでの電圧降下を低減できる効果がさらに大きい。好ましくは、出力バンプの直径としては、表皮探さをδとすると、δの数倍以上あればよい。上記表皮探さδは、

δ=(2ρ/ωμ)1/2

但し、ρ:導体の抵抗率

ω:角周波数

μ:透磁率

なので、例えば本実施形態のようにAuをバンプ材料に使用した場合、例えば900MHz帯であれば表皮深さδ=2.6μm程度となり、実際にはバンプ直径はバンプの加工精度の下限で決まる。

【0045】

図7は、トップ層であるエミッタメタル(突起電極)を相互に接続するエミッタ配線を示す図であり、図中ハッチングにて示す部分がエミッタ配線である。このエミッタ配線12は、フリップチップ実装する場合には、別の基板表面に形成される。かかるエミッタ配線12にてエミッタメタルが相互に接続され、トランジスタ相互間の熱伝達を容易にしていると共に、交差配線によらず、つまり浮遊容量を増加させる事なく、外部の接地メタル13と電気的に接続され、オンウエハ状態での通電動作試験を可能にしている。

【0046】

この半導体装置の作製方法は以下のとおりである。

【0047】

まず、半絶縁性のGaAs基板1の上に、A1GaAs/GaAs系からなるnpnエミッタトップ型HBT2を形成する。この形成には、例えば電子通信学会技術研究報告ED90−135の論文に記載の技術を用いることができる。本実施形態で用いたHBT2の構造は、サブコレクタ層(前記論文中ではBufferと記載)として、材質をn+−GaAs、不純物濃度を5×1018cm-3、厚みを500nmとした以外は、論文と同一である。

【0048】

次に、各メサエッチング工程、各電極金属形成/アロイ後、層間絶縁膜としてポリイミドを用い、ベース電極、コレクタ電極上をカバーし、エミッタ直上部に開口する。なお、ベースおよびコレクタへのコンタクト部は、後述するように、メタルからなる下層配線を用いて引き出され、離れた場所にそれぞれの引き出し用電極(図示せず)が設けられる。

【0049】

次に、トランジスタ素子の直上に、Ti/Pt/Auからなる電極をパターン形成する。この工程は下層配線を形成する工程を兼ねており、同時に下層配線が形成され、引き出し用電極となる。この下層配線は、幹配線や枝配線の所定のものに用いられる。

【0050】

次に、SiNxをパッシベーション兼MIM膜として堆積し、フォトリソグラフィ法と緩衝フッ酸エッチングとによって、バンプ電極を設ける部分及び上層配線とのコンタクトをとる部分のSiNx膜を開口する。

【0051】

次に、平坦化レジスト層としてポジフォトレジストAを塗布し、フォトリソグラフィによって、上層配線を設けるべき領域のポジフォトレジストA膜を開口する。

【0052】

次に、上層配線の一部であるTi/Auを全面に蒸着し、メッキ用電極とする。

【0053】

次に、上層配線メッキ用レジストとしてノボラック系ポジフォトレジストBを塗布し、フォトリソグララフィ技術を用いて、上層配線を設ける部分のみ開口する。

【0054】

次に、メッキ法により、Auからなる上層配線(厚み10μm)を形成する。この上層配線は、幹配線や枝配線の所定のものに用いられる。

【0055】

次に、上層配線メッキ用レジス卜(ポジフォトレジストB)を除去し、引き続き、下層配線以外の平坦化レジスト(ポジフォトレジストA)の上に露出したAuをエッチング除去し、引き続き、下層配線以外の平坦化レジストの上に露出したTiを、緩衝フッ酸エッチングによって除去する。

【0056】

次に、第2の平坦化レジスト層としてポジフォトレジストを塗布し、フォトリソグラフィによって、バンプを設けるべき領域を開口する。

【0057】

次に、バンプの一部であるTi/Auを全面に蒸着し、メッキ用電極とする。

【0058】

次に、バンプメッキ用レジストとしてノボラック系ポジフォトレジストを塗布し、フォトリソグラフィ技術を用いて、バンプ配線を設ける部分のみ開口する。次に、メッキ法により、Auからなるバンプ(高さ20μm)11、20、21を形成する。

【0059】

次に、バンプメッキ用レジストを除去し、引き続き、第2の平坦化レジスト上に露出したバンプ以外のAuをエッチング除去し、引き続き、第2の平坦化レジスト上に露出したバンプ以外のTiを、緩衝フッ酸エッチングによって除去する。

【0060】

次に、第3の平坦化レジストを塗布した。

【0061】

次に、通常の方法により、ラッピングおよびダイシングを行い、半導体チップを完成した。

【0062】

このようにして作製された半導体チップを、図7のようにエミッタメタルがパターン形成されたAlN基板に対して、フリップチップボンダを用いてフリップチップ実装した。ボンディング時にはパルスヒート方式を用い、トランジスタ素子にかかる熱を極力低減した。ボンディング時のバンプつぶれ量は10μmとなるよう圧力(2.2kg)とヒート温度(385℃、5sec)を調節した。

【0063】

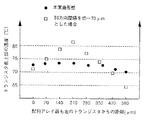

図8は、本実施形態の半導体装置における温度分布(●印)を、トランジスタアレイの間隔を均一に分布させた従来例の場合(□印)と比較して示す図である。この温度分布の測定箇所は、図7の破線にて示す部分である。この図より理解されるように、従来例のばあいは、トランジスタアレイの中央部でピーク温度となっている。これに対して、本実施形態の場合は、トランジスタアレイの総寸法が同じでも、アレイ内のピーク温度を低減し、温度分布を均一にする効果がある。

【0064】

なお、本実施形態では縦型構造トランジスタがコレクタ、ベース及びエミッタをこの順番で半導体基板上に形成したエミッタトップ型であって、トランジスタアレイが、トップ層の接合部における電極に対し、そのトップ層電極の上面から、そのトップ層の長さ方向とは垂直な方向の両側に向かう状態で引き出し電極がアーチ状に引き出され、該引き出し電極の上にバンプ電極を有する構成であるが、本発明はこれに限らず、エミッタ、ベース及びコレクタをこの順番で半導体基板上に形成したコレクタトップ型であって、バンプ電極を同様にした構成でもよい。なお、サブコレクタ層はコレクタトップ型の場合には省略され、代わりにエミッタ直下にサブエミッタが設けられる。また、トランジスタアレイが、フィンガー状のトランジスタ素子真性動作部の直上と該真性動作部のフィンガー長手方向と直交する方向に位置する非真性動作部とに跨るようにバンプ電極を具備する構成としてもよい。また、半導体層の導電型を実施形態の導電型から反転させてもよい。

【0065】

また、本発明は、バイポーラトランジスタの構造についても、エミッタのみがバンドギャップの大きい、いわゆるシングルヘテロバイポーラトランジスタ(SHBT)や、コレクタにもワイドバンドギャップ材料を用いた、いわゆるダブルヘテロバイポーラトランジスタ(DHBT)でも良い。また、O+、B+、H+イオン等を外部ベース直下に注入してCbcを低減する方法や、イオン注入による素子間分離法を組み合わせて適用することも可能である。

【0066】

本実施形態では能動素子としてHBTを用いたが、用いる素子はこれに限らず、例えば縦型構造素子では、通常のバイポーラトランジスタ、サイリスタ、HET(Hot E1ectron Transistor)、共鳴トンネルトランジスタ等でもよく、また、横型構造素子との組み合わせ{例えばHBTとHEMT(High E1ectron Mobility Transistor)、HBTとFETとの組み合わせ}、あるいは発光、受光素子との組み合わせも可能なことは言うまでもない。

【0067】

本実施形態では携帯電話用3段パワーアンプMMICを例に挙げて説明しているが、本発明はこれに限らず、例えばパワートランジスタ、超高速用集積回路等にも応用できることは言うまでもない。

【0068】

本実施形態においては、バンプ電極はエミッタ電極としての役割も果たしているが、例えば、大電力を扱うMMICや超高速集積回路等の用途によっては、バンプ電極がエミッタ(ソース)であると都合が悪い場合がある。このような場合は、バンプ電極を、ベース(ゲート)あるいはコレクタ(ドレイン)に接続するか、電極としては使用せず、絶縁膜を介する等の方法で熱放散の用途のみに用いてもよい。

【0069】

用いられる半導体チップとしては、本実施形態(GaAs)に限定されるものでなく、InP、SiC、GaP等他の化合物半導体で構成されていてもよく、C、Si等の元素半導体であってもよい。

【0070】

また、トランジスタ素子自体も、例えばA1GaAs/GaAs系、InGaP/GaAs系、InGaAs(P)/InA1As系、InGaAs(P)/InP系等、他の格子整合系でも良く、またInGaAs/(A1)GaAs/InP等の格子不整合系であっても良いことは言うまでもない。

【0071】

本実施形態では、フリップチップ用基板として、メタルパターンを具備するAlN基板を用いたが、熱伝導率の良好な材料であれば他の材料を用いてもよいことは言うまでもない。また、本実施形態に用いるフリップチップ用基板は必ずしも平面単板である必要はなく、いわゆるスルーホールやビアホールを具備する基板を使用してもよく、また、積層基板等の平面以外の構造の基板を使用してもよい。要は、バンプを経由しての接続に対応する部分が平坦である基板であればよい。

【0072】

また、ボンディングするフリップチップ用基板1枚に対して複数のチップをボンディングすることも可能である。この際、すべてのチップがフリップチップ実装される必要はなく、むしろ、用途によっては、例えばワイヤボンド等の方法を用いて実装したチップと混在させてもよい。

【0073】

なお、この実施形態では素子基板(チップ)の裏面側からの放熱を特に図らなかったが、当然ながら、チップの裏面を薄く削って伝熱用はんだ、ケースキャップ等を経由して放熱する手段と組み合わせてもよい。

【0074】

【発明の効果】

以上詳述したように本発明による場合には、縦型構造トランジスタが、そのフィンガー状のトランジスタ素子真性動作部の長手方向を、トランジスタアレイにおける列方向と平行になしてあり、かつ、配線が、列方向に延びる交互に配列された入力用幹配線および出力用幹配線と、該入力用幹配線から行方向に延びる入力用枝配線と、該出力用幹配線から該入力用枝配線の間に行方向に延びる出力用枝配線とを備え、トランジスタアレイの列方向の一方側を入力側となし、かつ、他方側を出力側としてあるので、幹配線や枝配線の配置が容易にできる。よって、CADによるパターンの自動生成が容易になる。また、トランジスタの配置が対称となるので、電力合成効率を向上させ得る。また、接続できるトランジスタ数を増大化できるので大出力化が可能となり、図11のようなトランジスタ構造ではないので、トランジスタの接続を増大してもトランジスタの占有面積が著しく増加せず、コスト高になりにくい。

【0075】

また、列方向のトランジスタ間隔を中央部から離れるに伴って小さくして配置されているので、列方向における設計を各行方向に適用すればよく、また、トランジスタアレイの中央部に熱がこもり難くなる。その結果、発熱に伴う信頼性の低下を防止でき、またトランジスタ間隔を熱影響のないように基板を著しく大きくする必要がないので、コストの低廉化が図れる。

【0076】

また、トランジスタアレイが、列方向の間隔を中央部から離れるに伴って小さくして配置されていることに加えて、入力側の間隔を対応する位置における出力側の間隔よりも大きくなしてある構成とすることにより、入力側の放熱され難い状態を改善できる。その結果、トランジスタ間隔を熱影響のないように基板を著しく大きくする必要がないので、コストの低廉化がより図れる。

【0077】

また、配線の出力側にメタルパターンが設けられた構成とすることにより、出力側のインピーダンスを上昇させ得る。その結果、変換損失を小さくすることが可能になる。

【図面の簡単な説明】

【図1】本実施形態に係る半導体装置の基本構成を示す平面図である。

【図2】本実施形態に係る半導体装置の真性動作部を黒く着色して示す図である。

【図3】本実施形態に係る半導体装置におけるトランジスタの列方向間隔および行方向間隔を説明するための図(平面図)である。

【図4】本実施形態に係る半導体装置において出力側にメタルパターンを設けた状態を示す平面図である。

【図5】本発明における出力パンプの設置の他の例を示す図である。

【図6】本発明における出力パンプの設置の他の例を示す図である。

【図7】本実施形態に係る半導体装置において設けられたエミッタ配線を示す図(平面図)である。

【図8】本実施形態に係る半導体装置に温度分布を示す図である。

【図9】第2従来例の構成を示す平面図である。

【図10】第2従来例の説明に用いる平面図である。

【図11】第3従来例の構成を示す平面図である。

【符号の説明】

1 半絶縁性GaAs基板

3 縦型構造トランジスタ

2 npnエミッタトップ型HBT

4 入力用幹配線

5 出力用幹配線

8 入力用枝配線

9 出力用枝配線

10 メタルパターン

11、11a 出力バンプ

20 入力用、その他のI/O用、接地用のバンプ

21 接地用バンプ

【発明の属する技術分野】

本発明は、たとえばモノリシックマイクロ波IC(MMIC)などに利用できる、電力増幅用の縦型構造トランジスタを同一基板上に複数個含む構成の半導体装置に関する。

【0002】

【従来の技術】

最近、マイクロ波帯での電力増幅用トランジスタの需要が高まっている。中でも、ヘテロジャンクションバイポーラトランジスタ(以下HBTと略す)に代表される縦型構造トランジスタが高効率増幅を実現する手段として注目されている。その理由は、現在実用化されているGaAsFETに比較して、HBT等は、高い利得と低いアウトプットコンダクタンスを持つからである。

【0003】

上記縦型構造トランジスタは、一般に知られているように、高電流密度で動作するため、必然的に発熱密度が高くなる。したがって、適正に動作させるためには、基板表面に形成された接合部(pn接合部)の発熱を、効率良く半導体基板外へ逃がさなければならない。

【0004】

そこで、本願発明者らは、半導体基板上に、エミッタ突起電極を基板表面より突出した状態にしてトランジスタが設けられた縦型構造トランジスタおよびこれを用いた集積回路等の半導体装置を提案している(例えば、H.Sato etal.、Bump Heat Sink technology”15th Annual GaAs IC Symposium Technical Digest p337−340)。これを、第1従来例という。かかる第1従来例による場合は、基板表面より突出したエミッタ突起電極にて放熱する構造であるため、基板表面に形成された接合部の発熱を更に効率良く逃がすことができる上、引き出し線のインダクタンスおよび寄生容量等を低減でき、マイクロ波帯での電力増幅用として実用に供することができる。但し、適当な出力を確保するためには、単位トランジスタを並列に接続する必要があるが、上記文献ではその並列接続の具体的方式については開示されていない。

【0005】

また、本願発明者らは、並列接続の具体的方式に関し、図9に示すように上記のような縦型構造トランジスタ40を相互に接続する方式を提案している(特開平6−104274号)。この提案を第2従来例という。この第2従来例では、フィンガー状のトランジスタ素子真性動作部の長手方向を、集合トランジスタの入力側と出力側とを結んだ線(エミッタトップ型でエミッタ接地を用いた際にはベース側とコレクタ側とを結んだ線)と垂直になして配置している。これは、図9および図10に示すようなトランジスタ配置を取り易くするためである。

【0006】

更に、並列接続の具体的方式についての別の従来例としては、図11に示す方式のものが提案されている(U.S.patent 5、321、279)。これを、第3従来例という。この第3従来例でも、フィンガー状のトランジスタ素子真性動作部の長手方向を、集合トランジスタの入力側と出力側とを結んだ線(エミッタトップ型でエミッタ接地を用いた際にはベース側とコレクタ側とを結んだ線)と垂直になして配置している。また、第3従来例ではバンプによる放熱は試みられていない。

【0007】

【発明が解決しようとする課題】

ところで、上記第1、第2従来例においては、次のような(a)〜(e)の問題があった。

【0008】

(a)図9のような配列では、各単位トランジスタから見た、入力側インピーダンスと出力側インピーダンスとに著しい不均一が生じる。また、入力側および出力側のそれぞれから見て、トランジスタ配置が左右対称でないため、電力分配/結合に不均一が生じる。その結果、電力合成効率が低下し、所望の出力が出にくくなるという問題があった。

【0009】

(b)また、CADでトランジスタのデザイン配置作業を行う際、枝のデザインが場所毎に違うためデザイン作業が複雑な上、パターンの自動生成に著しく不利となる。

【0010】

(c) また、図10のような配列を採ろうとすると、大出力化のために、さらにベース配線62やコレクタ配線63の枝を伸ばした際、枝と枝との距離はおのずと限界があるので、枝の幅を狭くした部分が生ずる。すると、部分的に電気抵抗の高いところができ、発熱が大きくなって信頼性の低下を引き起こす。また、上述した入力側インピーダンスと出力側インピーダンスとの著しい不均一性や電力分配/結合での不均一性の問題がさらに顕著になる。

【0011】

(d)また、単に、複数個の縦型トランジスタが基板中心に向かうにつれて相互のトランジスタ間隔を広くするように配置するだけでは、特に集積回路になった際、十分な均熱化が達成できない。その結果、比較的大きなチップ面積を必要とし、工期がかかると共にコスト高になるという問題があった。

【0012】

(e)また、大出力化のために並列数を増やしたトランジスタでは、出力インピーダンスが低下する。通常、低損失化のためチップ外に設けられる出力整合回路としてのアンテナ系では50Ωに設定されており、この50Ωに変換する際、必要とされる変換比が大きくなり、結果として変換損失が大きくなるという問題があった。

【0013】

一方、第3従来例においては、次のような(f)および(g)の問題があった。

【0014】

(f)図11のような配列では、接続できるユニットトランジスタ数におのずと限界があり、大出力化が困難になるという問題がある。

【0015】

(g)また、図11のようなトランジスタ配列を1集団として、これをさらに並列接続することも考えられるが、その場合には占有面積が大きくなりコスト高になるという問題があった。

【0016】

このように種々の問題が生ずるため、従来においては、マイクロ波/ミリ波帯での電力増幅用として高出力、高性能の縦型構造トランジスタを用いたMMICなどの半導体装置を、低コストで実用に供することが困難であった。

【0017】

本発明は、このような従来技術の課題を解決すべくなされたものであり、マイクロ波/ミリ波帯での電力増幅用として実用に供することのできる、縦型構造トランジスタ集合体による高出力かつ高性能な半導体装置を提供することを目的とする。

【0018】

【課題を解決するための手段】

本発明の半導体装置は、縦型構造トランジスタがアレイ状に配設されると共に並列接続された半導体装置において、該縦型構造トランジスタが、そのフィンガー状のトランジスタ素子真性動作部の長手方向をトランジスタアレイにおける列方向と平行になし、かつ、列方向のトランジスタ間隔を中央部から離れるに伴って小さくして配置されており、列方向に延びる交互に配列された入力用幹配線および出力用幹配線と、該入力用幹配線から行方向に延びる入力用枝配線と、該出力用幹配線から該入力用枝配線の間に行方向に延びる出力用枝配線とを備える配線に対し、トランジスタアレイが、その行方向において複数個の縦型構造トランジスタ毎に入力用幹配線および出力用幹配線によって挟まれ、かつ、その挟まれた複数個の縦型構造トランジスタの各々が該入力用枝配線および該出力用枝配線にて挟まれており、更に、該トランジスタアレイの列方向の一方側を入力側となし、かつ、他方側を出力側としてあり、そのことにより上記目的が達成される。

【0019】

本発明の半導体装置において、前記トランジスタアレイが、列方向のトランジスタ間隔を中央部から離れるに伴って小さくして配置されていることに加えて、入力側のトランジスタ間隔を対応する位置における出力側のトランジスタ間隔よりも大きくなしてある構成とするのが好ましい。

【0020】

本発明の半導体装置において、前記入力用幹配線および出力用幹配線によって行方向に挟まれた縦型構造トランジスタを1ブロックとして、各ブロック間の離隔間隔がトランジスタアレイの中心部から行方向に離れるに伴って小さくなっている構成とするのが好ましい。

【0021】

本発明の半導体装置において、前記配線の出力側に略三角形のメタルパターンが設けられている構成とするのが好ましい。

【0022】

本発明の半導体装置において、前記トランジスタアレイが、フィンガー状のトランジスタ素子真性動作部の直上と該真性動作部のフィンガー長手方向と直交する方向に位置する非真性動作部とに跨るようにバンプ電極を具備する構成や、縦型構造トランジスタがエミッタトップ型またはコレクタトップ型であって、トランジスタアレイがトップ層の接合部における電極に対し、そのトップ層電極の上面から、そのトップ層の長さ方向とは垂直な方向の両側に向かう状態で引き出し電極がアーチ状に引き出され、該引き出し電極の上にバンプ電極を有する構成とすることができる。また、前記縦型構造トランジスタがエミッタトップ型であり、かつ、エミッタ接地の場合は、該トランジスタアレイの列方向の一方側が前記配線のベース側であり、列方向の他方側が該配線のコレクタ側である。

【0023】

以下に、本発明の作用につき説明する。

【0024】

本発明の半導体装置にあっては、縦型構造トランジスタが、そのフィンガー状のトランジスタ素子真性動作部の長手方向を、トランジスタアレイにおける列方向と平行になしてあり、かつ、配線が、列方向に延びる交互に配列された入力用幹配線および出力用幹配線と、該入力用幹配線から行方向に延びる入力用枝配線と、該出力用幹配線から該入力用枝配線の間に行方向に延びる出力用枝配線とを備え、トランジスタアレイの列方向の一方側を入力側となし、かつ、他方側を出力側としてあるので、幹配線や枝配線の配置が容易にできる。その結果、上記(a)、(b)、(f)および(g)の各問題が解決される。

【0025】

また、列方向のトランジスタ間隔を中央部から離れるに伴って小さくして配置されているので、列方向における設計を各行方向に適用すればよく、また、トランジスタアレイの中央部に熱がこもり難くなる。その結果、上記(c)および(d)の各問題が解決される。

【0026】

また、トランジスタアレイが、列方向の間隔を中央部から離れるに伴って小さくして配置されていることに加えて、入力側の間隔を対応する位置における出力側の間隔よりも大きくなしてある構成とすることにより、入力側の放熱がされ難い状態を改善できる。その結果、上記(d)の問題が解決される。

【0027】

また、配線の出力側にメタルパターンが設けられた構成とすることにより、出力側のインピーダンスを等価的に上昇させ得る。その結果、上記(e)の問題が解決される。

【0028】

【発明の実施の形態】

以下、図面を参照して本発明に係る半導体装置の実施形態を説明する。

【0029】

図1は、本実施形態に係る半導体装置の基本構成を示す平面図である。この半導体装置は、半絶縁性GaAs基板1の上に、縦型構造トランジスタ3を用いてマイクロ波電力増幅用のnpnエミッタトップ型HBT2が形成されている。このHBT2は、携帯電話用3段パワーアンプMMICを構成するものである。

【0030】

上記HBT2は、複数の縦型構造トランジスタ3がアレイ状に配設され、かつ、並列接続されている。この構成のHBT2のトランジスタ配置において、図2に示すように、フィンガー状のトランジスタ素子真性動作部(図中に黒く着色した部分)の長手方向を、トランジスタアレイの入力側(左側)と出力側(右側)とを結んだ線(縦型構造トランジスタ3がエミッタトップ型でエミッタ接地を用いた場合にはベース側とコレクタ側とを結んだ線)と平行にして各縦型構造トランジスタ3が配置されている。

【0031】

トランジスタアレイの並列接続用の配線は、図1に示すように、左を入力側、右を出力側になるように配置した場合、トランジスタアレイの行方向において、3個×8個のトランジスタ素子真性動作部毎に分割する入力用幹配線4および出力用幹配線5を有する。入力用幹配線4は、図1の左側において入力主線6に接続され、一方の出力用幹配線5は同右側において出力主線7に接続されている。また、入力用幹配線4からは行方向に延びる入力用枝配線8が分岐され、出力用幹配線5からは行方向に延びる出力用枝配線9が分岐されている。入力用枝配線8は出力用枝配線9の間に入り込むように設けられている。全体としては、枝配線8、9に3個のトランジスタ3を配置したものを8列、これを1ブロックとして、4ブロックが、それぞれ幹配線4、5によって分割されて、トランジスタアレイおよび配線が配置されている。

【0032】

上記列方向のトランジスタ間隔は、トランジスタアレイの中心から離れるに従って小さくなるように配置されている。この配置の場合は、トランジスタアレイ中央部分に熱がこもる現象を、軽減緩和することができる。その理由は、トランジスタ間隔を同一にした場合はトランジスタの放熱路の重なり部分が中央部で高密度となるが、本発明の間隔にすることで、放熱路の重なり部分を中央部で減少させることが可能となるからである。

【0033】

この場合において、第2従来例との相違は以下の通りである。第2従来例の場合には、中央部でのユニットトランジスタの粗密を、トランジスタ個々の配置を変化させている。具体的には、図10に示すように、左下から2行2列、2行3列、2行4列、3行2列、3行4列、4行2列、4行3列、4行4列、の計8個のユニットトランジスタの配置を微妙に変化させている。これに対して、本発明ではトランジスタ個々の配置を変化させるのではなく、枝配線に付属したユニットトランジスタ全体を平行移動させている。これによって、本発明による場合には、配列の設計を容易に実現できる。

【0034】

また、本発明においては、列方向のトランジスタ間隔において、トランジスタアレイの中心から左右に相対応する列方向のトランジスタ間隔を比べた場合、入力側の列方向間隔が出力側の列方向間隔に比較して大きくなっている。具体的には、図3に即して説明すると、Aがトランジスタアレイの中心部、その左右にBとb、Cとc、Dとdが各々相対応する列方向間隔であるが、それぞれの間隔は、A=78μm、B=77μm、b=73μm、C=73μm、c=68μm、D=63μm、d=58μmとなっている。

【0035】

このように列方向のトランジスタ間隔において、トランジスタアレイの中心から左右に相対応する列方向の間隔を比べた場合、入力側の列方向間隔が出力側の列方向間隔に比較して大きいことは、特に集積回路になった際、十分な均熱化を達成する効果をもつ。この理由を以下に説明する。一般に、パワートランジスタは常に基板(半導体チップ)1の中心部に位置するとは限らない。特に、本発明で形成しようとするような大電力のパワートランジスタの場合、多段のパワーアンプの最終段に使用される。また、最終段の出力整合回路は、低損失化のために半導体チップ外に設けられる場合が多い。このため、図1に示すようにパワートランジスタは基板1の中央部から外れ、トランジスタの出力側は、入力側に比較してチップ周辺部に近く、チップ周辺部には出力用バンプ11の他、接地用バンプ21も具備しているため、これらを経由しての放熱も行われる。一方、入力側は、HBT2が存在しないうえ、入力用、その他のI/O用、接地用のバンプ20も数多くあるので一見放熱がよさそうであるが、最終的に放熱の経路となるバンプ20までの距離が遠いうえに前段のトランジスタからの放熱もあり、実際には放熱されにくい。したがって、この問題は、複数個の縦型構造トランジスタが基板中心に向かうにつれて相互のトランジスタ間隔が広くなることに加え、入力側の列方向間隔が、出力側の列方向間隔に比較して大きくとることにより解決できる。特に、集積回路になった際、これによる均熱化の効果が大きい。また、この効果は、通常のワイヤボンド構造やPHS(plated heat sink)構造でも有効であるが、特に、トランジスタアレイ内の熱分布が下地や周辺バンプの熱伝導状況に左右されやすいバンプ放熱構造の場合には、有効性が顕著である。

【0036】

この列方向における入力側のトランジスタ間隔を出力側のトランジスタ間隔に比較して大きくする場合の放熱性は、下地によって変動する。この場合、トランジスタ間隔は、上記数値を変更すべきである。本願発明者らの検討によると、例えば厚さ0.5mmの同時焼成AlN基板LCC(リードレスチップキャリア)を用い、プリント基板上に半田付け実装している場合、上記数値の各々において、±5μm以内での微調整により放熱性の良好な結果が得られている。

【0037】

また、幹配線についても、中央部の幹配線を最も太く、中央から離れるに従って幹配線を徐々に細くし、上述した各ブロックの間隔を調整している。具体的には、図3に即して説明すると、トランジスタアレイ中央部に位置する出力用幹配線5は幅60μm、トランジスタアレイ中央部から離れた2本の入力用幹配線4はそれぞれ幅45μmとなっている。このようにすることにより、トランジスタアレイ中央部分に熱がこもる現象を軽減緩和する効果を、さらに徹底することができる。

【0038】

また、1ブロックの構成が、各ブロックにおいて同様になった構造となっている。上記構造をとることにより、CADでトランジスタのデザイン配置作業を行う際、枝のデザインが場所毎に違う問題が解決され、パターンの自動生成が著しく有利になる。また、入力側、出力側のそれぞれから見て、トランジスタ配置は対称になっている。つまり、入力側と出力側とを結ぶ線(左右方向の線)に対して、上下対称になっている。これによっても、CADでトランジスタのデザイン配置作業を行う際において、パターンの自動生成がより有利になる。また、入力側、出力側のそれぞれから見たトランジスタ配置が対称であるため、電力分配/結合に不均一が生じない。

【0039】

上述した各ブロックが幹配線によって分割された構造は、フィンガー状のトランジスタ素子真性動作部の長手方向を、トランジスタアレイの入力側と出力側とを結んだ線(エミッタトップ型でエミッタ接地を用いた際にはベース側とコレクタ側とを結んだ線)と平行にして、トランジスタを配置することにより、とり易くなる。

【0040】

また、入力用枝配線と出力用枝配線とを交互に入り込ませた構成であるので、配線の交差部が無く、特性劣化を防ぐ効果がある。また、繰り返し形状となるため、CADによるパターンの自動生成に有利である。

【0041】

また、このような全体的な構成により、各単位トランジスタから見た、入力側インピーダンスと出力側インピーダンスとの均一が著しく緩和される。また、上述した全体の結果として、同一出力のパワートランジスタが、従来法に比較して著しく小型にできるので、入出力でのパワー合成が不要になり、チップコストを低廉化できる。

【0042】

図4は、出力側(エミッタトップ型でエミッタ接地を用いた際にはコレクタ側)に、略三角形のメタルパターン10を具備する様子を示す。このメタルパターン10は、たとえば略2等辺三角形であり、長辺は1160μm、高さは400μmとなっている。このようなメタルパターン10を具備する構成とした場合は、トランジスタアレイ出口のインピーダンスを等価的に上昇させるインピーダンス変換機能をもつ。

【0043】

一般に、大出力化のため、並列数を増やしたトランジスタでは、出力インピーダンスが低下するが、上記略三角形のメタルパターン10によって、パワートランジスタの出力端での出力インピーダンスが等価的に上昇する。これにより、後段での変換比の負担を軽減でき、アンテナ系に適用しても変換損失を低減できる。

【0044】

また、メタルパターン10における略2等辺三角形の頂点には図1に示すように円形の出力バンプ(直径:60μmφ)11を具備している。なお、出力バンプ11は図1では1個だが、図5に示すように同型の出力バンプ11を2個設けるようにしてもよく、更に多く設けるようにしてもよい。また、図6に示すように、小型の出力バンプ(直径:20μmφ)11aを多数、たとえば18個程度配置してもよい。図5の場合では、出力バンプの1個当たりの電流量を低減し、出力バンプでの電圧降下を低減できる効果をもつ。一方、図6の場合では、表皮効果を低減できるので、出力バンプでの電圧降下を低減できる効果がさらに大きい。好ましくは、出力バンプの直径としては、表皮探さをδとすると、δの数倍以上あればよい。上記表皮探さδは、

δ=(2ρ/ωμ)1/2

但し、ρ:導体の抵抗率

ω:角周波数

μ:透磁率

なので、例えば本実施形態のようにAuをバンプ材料に使用した場合、例えば900MHz帯であれば表皮深さδ=2.6μm程度となり、実際にはバンプ直径はバンプの加工精度の下限で決まる。

【0045】

図7は、トップ層であるエミッタメタル(突起電極)を相互に接続するエミッタ配線を示す図であり、図中ハッチングにて示す部分がエミッタ配線である。このエミッタ配線12は、フリップチップ実装する場合には、別の基板表面に形成される。かかるエミッタ配線12にてエミッタメタルが相互に接続され、トランジスタ相互間の熱伝達を容易にしていると共に、交差配線によらず、つまり浮遊容量を増加させる事なく、外部の接地メタル13と電気的に接続され、オンウエハ状態での通電動作試験を可能にしている。

【0046】

この半導体装置の作製方法は以下のとおりである。

【0047】

まず、半絶縁性のGaAs基板1の上に、A1GaAs/GaAs系からなるnpnエミッタトップ型HBT2を形成する。この形成には、例えば電子通信学会技術研究報告ED90−135の論文に記載の技術を用いることができる。本実施形態で用いたHBT2の構造は、サブコレクタ層(前記論文中ではBufferと記載)として、材質をn+−GaAs、不純物濃度を5×1018cm-3、厚みを500nmとした以外は、論文と同一である。

【0048】

次に、各メサエッチング工程、各電極金属形成/アロイ後、層間絶縁膜としてポリイミドを用い、ベース電極、コレクタ電極上をカバーし、エミッタ直上部に開口する。なお、ベースおよびコレクタへのコンタクト部は、後述するように、メタルからなる下層配線を用いて引き出され、離れた場所にそれぞれの引き出し用電極(図示せず)が設けられる。

【0049】

次に、トランジスタ素子の直上に、Ti/Pt/Auからなる電極をパターン形成する。この工程は下層配線を形成する工程を兼ねており、同時に下層配線が形成され、引き出し用電極となる。この下層配線は、幹配線や枝配線の所定のものに用いられる。

【0050】

次に、SiNxをパッシベーション兼MIM膜として堆積し、フォトリソグラフィ法と緩衝フッ酸エッチングとによって、バンプ電極を設ける部分及び上層配線とのコンタクトをとる部分のSiNx膜を開口する。

【0051】

次に、平坦化レジスト層としてポジフォトレジストAを塗布し、フォトリソグラフィによって、上層配線を設けるべき領域のポジフォトレジストA膜を開口する。

【0052】

次に、上層配線の一部であるTi/Auを全面に蒸着し、メッキ用電極とする。

【0053】

次に、上層配線メッキ用レジストとしてノボラック系ポジフォトレジストBを塗布し、フォトリソグララフィ技術を用いて、上層配線を設ける部分のみ開口する。

【0054】

次に、メッキ法により、Auからなる上層配線(厚み10μm)を形成する。この上層配線は、幹配線や枝配線の所定のものに用いられる。

【0055】

次に、上層配線メッキ用レジス卜(ポジフォトレジストB)を除去し、引き続き、下層配線以外の平坦化レジスト(ポジフォトレジストA)の上に露出したAuをエッチング除去し、引き続き、下層配線以外の平坦化レジストの上に露出したTiを、緩衝フッ酸エッチングによって除去する。

【0056】

次に、第2の平坦化レジスト層としてポジフォトレジストを塗布し、フォトリソグラフィによって、バンプを設けるべき領域を開口する。

【0057】

次に、バンプの一部であるTi/Auを全面に蒸着し、メッキ用電極とする。

【0058】

次に、バンプメッキ用レジストとしてノボラック系ポジフォトレジストを塗布し、フォトリソグラフィ技術を用いて、バンプ配線を設ける部分のみ開口する。次に、メッキ法により、Auからなるバンプ(高さ20μm)11、20、21を形成する。

【0059】

次に、バンプメッキ用レジストを除去し、引き続き、第2の平坦化レジスト上に露出したバンプ以外のAuをエッチング除去し、引き続き、第2の平坦化レジスト上に露出したバンプ以外のTiを、緩衝フッ酸エッチングによって除去する。

【0060】

次に、第3の平坦化レジストを塗布した。

【0061】

次に、通常の方法により、ラッピングおよびダイシングを行い、半導体チップを完成した。

【0062】

このようにして作製された半導体チップを、図7のようにエミッタメタルがパターン形成されたAlN基板に対して、フリップチップボンダを用いてフリップチップ実装した。ボンディング時にはパルスヒート方式を用い、トランジスタ素子にかかる熱を極力低減した。ボンディング時のバンプつぶれ量は10μmとなるよう圧力(2.2kg)とヒート温度(385℃、5sec)を調節した。

【0063】

図8は、本実施形態の半導体装置における温度分布(●印)を、トランジスタアレイの間隔を均一に分布させた従来例の場合(□印)と比較して示す図である。この温度分布の測定箇所は、図7の破線にて示す部分である。この図より理解されるように、従来例のばあいは、トランジスタアレイの中央部でピーク温度となっている。これに対して、本実施形態の場合は、トランジスタアレイの総寸法が同じでも、アレイ内のピーク温度を低減し、温度分布を均一にする効果がある。

【0064】

なお、本実施形態では縦型構造トランジスタがコレクタ、ベース及びエミッタをこの順番で半導体基板上に形成したエミッタトップ型であって、トランジスタアレイが、トップ層の接合部における電極に対し、そのトップ層電極の上面から、そのトップ層の長さ方向とは垂直な方向の両側に向かう状態で引き出し電極がアーチ状に引き出され、該引き出し電極の上にバンプ電極を有する構成であるが、本発明はこれに限らず、エミッタ、ベース及びコレクタをこの順番で半導体基板上に形成したコレクタトップ型であって、バンプ電極を同様にした構成でもよい。なお、サブコレクタ層はコレクタトップ型の場合には省略され、代わりにエミッタ直下にサブエミッタが設けられる。また、トランジスタアレイが、フィンガー状のトランジスタ素子真性動作部の直上と該真性動作部のフィンガー長手方向と直交する方向に位置する非真性動作部とに跨るようにバンプ電極を具備する構成としてもよい。また、半導体層の導電型を実施形態の導電型から反転させてもよい。

【0065】

また、本発明は、バイポーラトランジスタの構造についても、エミッタのみがバンドギャップの大きい、いわゆるシングルヘテロバイポーラトランジスタ(SHBT)や、コレクタにもワイドバンドギャップ材料を用いた、いわゆるダブルヘテロバイポーラトランジスタ(DHBT)でも良い。また、O+、B+、H+イオン等を外部ベース直下に注入してCbcを低減する方法や、イオン注入による素子間分離法を組み合わせて適用することも可能である。

【0066】

本実施形態では能動素子としてHBTを用いたが、用いる素子はこれに限らず、例えば縦型構造素子では、通常のバイポーラトランジスタ、サイリスタ、HET(Hot E1ectron Transistor)、共鳴トンネルトランジスタ等でもよく、また、横型構造素子との組み合わせ{例えばHBTとHEMT(High E1ectron Mobility Transistor)、HBTとFETとの組み合わせ}、あるいは発光、受光素子との組み合わせも可能なことは言うまでもない。

【0067】

本実施形態では携帯電話用3段パワーアンプMMICを例に挙げて説明しているが、本発明はこれに限らず、例えばパワートランジスタ、超高速用集積回路等にも応用できることは言うまでもない。

【0068】

本実施形態においては、バンプ電極はエミッタ電極としての役割も果たしているが、例えば、大電力を扱うMMICや超高速集積回路等の用途によっては、バンプ電極がエミッタ(ソース)であると都合が悪い場合がある。このような場合は、バンプ電極を、ベース(ゲート)あるいはコレクタ(ドレイン)に接続するか、電極としては使用せず、絶縁膜を介する等の方法で熱放散の用途のみに用いてもよい。

【0069】

用いられる半導体チップとしては、本実施形態(GaAs)に限定されるものでなく、InP、SiC、GaP等他の化合物半導体で構成されていてもよく、C、Si等の元素半導体であってもよい。

【0070】

また、トランジスタ素子自体も、例えばA1GaAs/GaAs系、InGaP/GaAs系、InGaAs(P)/InA1As系、InGaAs(P)/InP系等、他の格子整合系でも良く、またInGaAs/(A1)GaAs/InP等の格子不整合系であっても良いことは言うまでもない。

【0071】

本実施形態では、フリップチップ用基板として、メタルパターンを具備するAlN基板を用いたが、熱伝導率の良好な材料であれば他の材料を用いてもよいことは言うまでもない。また、本実施形態に用いるフリップチップ用基板は必ずしも平面単板である必要はなく、いわゆるスルーホールやビアホールを具備する基板を使用してもよく、また、積層基板等の平面以外の構造の基板を使用してもよい。要は、バンプを経由しての接続に対応する部分が平坦である基板であればよい。

【0072】

また、ボンディングするフリップチップ用基板1枚に対して複数のチップをボンディングすることも可能である。この際、すべてのチップがフリップチップ実装される必要はなく、むしろ、用途によっては、例えばワイヤボンド等の方法を用いて実装したチップと混在させてもよい。

【0073】

なお、この実施形態では素子基板(チップ)の裏面側からの放熱を特に図らなかったが、当然ながら、チップの裏面を薄く削って伝熱用はんだ、ケースキャップ等を経由して放熱する手段と組み合わせてもよい。

【0074】

【発明の効果】

以上詳述したように本発明による場合には、縦型構造トランジスタが、そのフィンガー状のトランジスタ素子真性動作部の長手方向を、トランジスタアレイにおける列方向と平行になしてあり、かつ、配線が、列方向に延びる交互に配列された入力用幹配線および出力用幹配線と、該入力用幹配線から行方向に延びる入力用枝配線と、該出力用幹配線から該入力用枝配線の間に行方向に延びる出力用枝配線とを備え、トランジスタアレイの列方向の一方側を入力側となし、かつ、他方側を出力側としてあるので、幹配線や枝配線の配置が容易にできる。よって、CADによるパターンの自動生成が容易になる。また、トランジスタの配置が対称となるので、電力合成効率を向上させ得る。また、接続できるトランジスタ数を増大化できるので大出力化が可能となり、図11のようなトランジスタ構造ではないので、トランジスタの接続を増大してもトランジスタの占有面積が著しく増加せず、コスト高になりにくい。

【0075】

また、列方向のトランジスタ間隔を中央部から離れるに伴って小さくして配置されているので、列方向における設計を各行方向に適用すればよく、また、トランジスタアレイの中央部に熱がこもり難くなる。その結果、発熱に伴う信頼性の低下を防止でき、またトランジスタ間隔を熱影響のないように基板を著しく大きくする必要がないので、コストの低廉化が図れる。

【0076】

また、トランジスタアレイが、列方向の間隔を中央部から離れるに伴って小さくして配置されていることに加えて、入力側の間隔を対応する位置における出力側の間隔よりも大きくなしてある構成とすることにより、入力側の放熱され難い状態を改善できる。その結果、トランジスタ間隔を熱影響のないように基板を著しく大きくする必要がないので、コストの低廉化がより図れる。

【0077】

また、配線の出力側にメタルパターンが設けられた構成とすることにより、出力側のインピーダンスを上昇させ得る。その結果、変換損失を小さくすることが可能になる。

【図面の簡単な説明】

【図1】本実施形態に係る半導体装置の基本構成を示す平面図である。

【図2】本実施形態に係る半導体装置の真性動作部を黒く着色して示す図である。

【図3】本実施形態に係る半導体装置におけるトランジスタの列方向間隔および行方向間隔を説明するための図(平面図)である。

【図4】本実施形態に係る半導体装置において出力側にメタルパターンを設けた状態を示す平面図である。

【図5】本発明における出力パンプの設置の他の例を示す図である。

【図6】本発明における出力パンプの設置の他の例を示す図である。

【図7】本実施形態に係る半導体装置において設けられたエミッタ配線を示す図(平面図)である。

【図8】本実施形態に係る半導体装置に温度分布を示す図である。

【図9】第2従来例の構成を示す平面図である。

【図10】第2従来例の説明に用いる平面図である。

【図11】第3従来例の構成を示す平面図である。

【符号の説明】

1 半絶縁性GaAs基板

3 縦型構造トランジスタ

2 npnエミッタトップ型HBT

4 入力用幹配線

5 出力用幹配線

8 入力用枝配線

9 出力用枝配線

10 メタルパターン

11、11a 出力バンプ

20 入力用、その他のI/O用、接地用のバンプ

21 接地用バンプ

Claims (7)

- 縦型構造トランジスタがアレイ状に配設されると共に並列接続された半導体装置において、

該縦型構造トランジスタが、そのフィンガー状のトランジスタ素子真性動作部の長手方向をトランジスタアレイにおける列方向と平行になし、かつ、列方向のトランジスタ間隔を中央部から離れるに伴って小さくして配置されており、

列方向に延びる交互に配列された入力用幹配線および出力用幹配線と、該入力用幹配線から行方向に延びる入力用枝配線と、該出力用幹配線から該入力用枝配線の間に行方向に延びる出力用枝配線とを備える配線に対し、トランジスタアレイが、その行方向において複数個の縦型構造トランジスタ毎に入力用幹配線および出力用幹配線によって挟まれ、かつ、その挟まれた複数個の縦型構造トランジスタの各々が該入力用枝配線および該出力用枝配線にて挟まれており、

更に、該トランジスタアレイの列方向の一方側を入力側となし、かつ、他方側を出力側としてある半導体装置。 - 前記トランジスタアレイが、列方向のトランジスタ間隔を中央部から離れるに伴って小さくして配置されていることに加えて、入力側のトランジスタ間隔を対応する位置における出力側のトランジスタ間隔よりも大きくなしてある請求項1に記載の半導体装置。

- 前記入力用幹配線および出力用幹配線によって行方向に挟まれた縦型構造トランジスタを1ブロックとして、各ブロック間の離隔間隔がトランジスタアレイの中心部から行方向に離れるに伴って小さくなっている請求項1または2に記載の半導体装置。

- 前記配線の出力側にメタルパターンが設けられている請求項1、2または3に記載の半導体装置。

- 前記トランジスタアレイが、フィンガー状のトランジスタ素子真性動作部の直上と該真性動作部のフィンガー長手方向と直交する方向に位置する非真性動作部とに跨るようにバンプ電極を具備する請求項1〜4のいずれか一つに記載の半導体装置。

- 前記縦型構造トランジスタがエミッタトップ型またはコレクタトップ型であって、トランジスタアレイが、トップ層の接合部における電極に対し、そのトップ層電極の上面から、そのトップ層の長さ方向とは垂直な方向の両側に向かう状態で引き出し電極がアーチ状に引き出され、該引き出し電極の上にバンプ電極を有する請求項1〜4のいずれか一つに記載の半導体装置。

- 前記縦型構造トランジスタがエミッタトップ型であり、かつ、エミッタ接地の場合に、トランジスタアレイの列方向の一方側が前記配線のベース側であり、列方向の他方側が該配線のコレクタ側である請求項6に記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP06883396A JP3674881B2 (ja) | 1996-03-25 | 1996-03-25 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP06883396A JP3674881B2 (ja) | 1996-03-25 | 1996-03-25 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH09260502A JPH09260502A (ja) | 1997-10-03 |

| JP3674881B2 true JP3674881B2 (ja) | 2005-07-27 |

Family

ID=13385105

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP06883396A Expired - Fee Related JP3674881B2 (ja) | 1996-03-25 | 1996-03-25 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3674881B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE60337036D1 (de) * | 2003-08-28 | 2011-06-16 | Hitachi Ltd | Halbleiterbauelement und verfahren zu seiner herstellung |

| US8159048B2 (en) * | 2004-01-30 | 2012-04-17 | Triquint Semiconductor, Inc. | Bipolar junction transistor geometry |

| TWI747145B (zh) * | 2019-03-19 | 2021-11-21 | 日商村田製作所股份有限公司 | 半導體裝置及放大器模組 |

-

1996

- 1996-03-25 JP JP06883396A patent/JP3674881B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH09260502A (ja) | 1997-10-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6028348A (en) | Low thermal impedance integrated circuit | |

| US7511315B2 (en) | Semiconductor device and manufacturing method therefor | |

| JP4955384B2 (ja) | 半導体装置 | |

| US20210313293A1 (en) | Rf amplifier devices and methods of manufacturing | |

| JP3084541B2 (ja) | 縦型構造トランジスタ | |

| US11356070B2 (en) | RF amplifiers having shielded transmission line structures | |

| US11837457B2 (en) | Packaging for RF transistor amplifiers | |

| US11670605B2 (en) | RF amplifier devices including interconnect structures and methods of manufacturing | |

| CN115527971A (zh) | 半导体装置以及功率放大器模块 | |

| JPH0945692A (ja) | 縦型構造トランジスタ及びその製造方法、並びに半導体装置 | |

| JP2839795B2 (ja) | 半導体装置 | |

| JP3674881B2 (ja) | 半導体装置 | |

| US11876032B2 (en) | Semiconductor device | |

| JP2003077930A (ja) | 半導体装置及びその製造方法 | |

| US20220321071A1 (en) | Rf amplifier devices and methods of manufacturing including modularized designs with flip chip interconnections | |

| US20220157808A1 (en) | Semiconductor device | |

| JP3264517B2 (ja) | 縦型構造へテロ接合バイポーラトランジスタ | |

| JP2006114732A (ja) | 半導体装置及びその製造方法、並びに半導体モジュール | |

| CN113809036A (zh) | 半导体装置 | |

| JP3268064B2 (ja) | 半導体装置 | |

| US10332805B2 (en) | Semiconductor structure with strain reduction | |

| JP3229185B2 (ja) | 半導体チップ、その製造方法、半導体素子、および半導体装置 | |

| JPH10144801A (ja) | 半導体装置 | |

| JP3243454B2 (ja) | 縦型構造トランジスタ | |

| US20220190124A1 (en) | Power amplifier |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040604 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050422 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050422 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |