JP3671140B2 - 電気・電子回路装置 - Google Patents

電気・電子回路装置 Download PDFInfo

- Publication number

- JP3671140B2 JP3671140B2 JP2000264178A JP2000264178A JP3671140B2 JP 3671140 B2 JP3671140 B2 JP 3671140B2 JP 2000264178 A JP2000264178 A JP 2000264178A JP 2000264178 A JP2000264178 A JP 2000264178A JP 3671140 B2 JP3671140 B2 JP 3671140B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- logic output

- electric

- voltage

- terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Logic Circuits (AREA)

- Storage Device Security (AREA)

- Read Only Memory (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

【発明の属する技術分野】

この発明は、たとえば、LSI(large scale integrated circuit)等の集積回路に適用して好適であり、電気・電子製品のハードウエアの改造、およびソフトウエアの改竄や2次利用等を有効に防止し得る電気・電子回路装置に関する。

【0002】

【従来の技術】

電気・電子製品のフールプルーフおよびフェイルセーフ等の観点から、電気・電子製品のハードウエアの改造やソフトウエアの改竄等が、ユーザ側において行えないことが望ましい。

【0003】

そこで、従来、これら電気・電子製品のハードウエアの改造、およびソフトウエアの改竄や2次利用等を防止するために、製品の筐体に特殊なねじを用いたり、ソフトウエア的に改竄や2次利用を防止する工夫がなされている。

【0004】

しかしながら、これらの工夫は、電気・電子製品のハードウエアの改造、およびソフトウエアの改竄や2次利用等を防止し得る一定の効果はあるものの、その防止効果が十分ではない。

【0005】

【発明が解決しようとする課題】

この発明はこのような課題を考慮してなされたものであり、簡単な構成で、電気・電子製品のハードウエアの改造、およびソフトウエアの改竄や2次利用等を物理的に防止することを可能とする電気・電子回路装置を提供することを目的とする。

【0006】

また、この発明は、たとえば、ユーザが一度使用したとき、フィールドでの2次使用を不可能とする電気・電子回路装置を提供することを目的とする。

【0016】

【課題を解決するための手段】

この電気・電子回路装置の電源入力端子に電圧が印加されたとき、論理出力が一定の論理出力に不可逆的に固定される論理出力設定回路と、この論理出力設定回路の出力側に読み書き制御入力が接続される電気的に書き込み消去が可能な記憶装置とを有し、前記記憶装置の前記読み書き制御入力に、読み書き制御用端子が接続され、前記電源入力端子に電圧が印加される前には、前記記憶装置にのみ電源が供給された状態で前記読み書き制御用端子を利用して前記記憶装置に対する読み書き制御が可能とされ、前記電源入力端子に電圧が印加されて、前記論理出力設定回路が一定の論理出力に不可逆的に固定された場合に、前記記憶装置の書き込み消去を不可能とし、読み出しのみを可能とするように構成されている(請求項1記載の発明)。

【0017】

この発明によれば、論理出力設定回路の論理出力により、電気的に書き込み消去が可能な記憶装置の動作を規定することができる可能性が得られる。

【0018】

前記論理出力設定回路では、前記論理出力設定回路の出力と前記読み書き制御用端子とを論理積回路の入力に接続し、前記論理積回路の出力を前記記憶装置の前記読み書き制御入力に接続している(請求項2記載の発明)。

【0021】

前記論理出力設定回路は、前記電源入力端子に印加された電圧に基づいて不可逆的に遮断される遮断素子を有し、前記論理出力設定回路は、前記遮断素子が遮断されることにより電流が供給されなくなり、一定の論理出力に不可逆的に固定されている(請求項3記載の発明)。

【0022】

この場合においても、前記電源入力端子と前記遮断素子との間に昇圧回路を設けることで、前記電源入力端子に印加される電圧が比較的に低電圧であっても、昇圧回路の比較的に高電圧な出力により遮断素子を容易に遮断することができる可能性が得られる(請求項4記載の発明)。

【0023】

また、この請求項4記載の発明において、昇圧回路を、前記電源入力端子に電圧が印加されたときから一定期間動作状態とするパワーオンリセット回路により駆動する構成とすることで、昇圧回路の電力消費を一定期間に制限できることから好ましい(請求項5記載の発明)。

【0024】

特定の外部端子に電圧が印加されたとき、論理出力が一定の論理出力に不可逆的に固定される論理出力設定回路と、この論理出力設定回路の出力側に接続される電気的に書き込み消去が可能な記憶装置と、前記論理出力設定回路に設けられ、前記特定の外部端子に印加された電圧に基づいて不可逆的に遮断される遮断素子と、前記特定の外部端子と前記遮断素子との間に設けられている昇圧回路とを有し、前記遮断素子は、前記特定の外部端子に電圧が印加されたときに前記昇圧回路の出力により遮断され、前記昇圧回路には、前記遮断素子が遮断されたことを検出して、前記昇圧回路の電力消費を低減あるいは無くする電力消費制限回路が接続されている(請求項6記載の発明)。

【0025】

特定の外部端子に電圧が印加されたとき、論理出力が一定の論理出力に不可逆的に固定される論理出力設定回路と、この論理出力設定回路の出力側に接続される電気的に書き込み消去が可能な記憶装置と、前記論理出力設定回路に設けられ、前記特定の外部端子に印加された電圧に基づいて不可逆的に遮断される遮断素子と、前記特定の外部端子と前記遮断素子との間に設けられている昇圧回路とを有し、前記特定の外部端子に電圧が印加されたときから一定期間前記昇圧回路を動作状態とするパワーオンリセット回路を含み、前記遮断素子は、前記パワーオンリセット回路により動作状態とされた前記昇圧回路の出力により遮断され、前記昇圧回路には、前記遮断素子が遮断されたことを検出して、前記昇圧回路の電力消費を低減あるいは無くする電力消費制限回路が接続されている(請求項7記載の発明)。

【0026】

請求項7記載の発明において、該電気・電子回路装置が集積回路により構成されるとき、前記遮断素子は、シリコン配線パターンにより形成することができる(請求項8記載の発明)。

【0027】

請求項1〜8記載の発明において、前記電気・電子回路装置は集積回路により構成されている(請求項9記載の発明)。

【0030】

【発明の実施の形態】

以下、この発明の一実施の形態について図面を参照して説明する。

【0031】

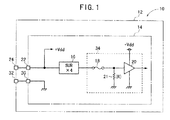

図1は、この発明の電気・電子回路装置の一実施の形態が適用されたLSI等の集積回路(IC)10の構成を示している。この集積回路10は、プラスチックパッケージ12内に、基本的にはシリコンウェハーからなるICチップ14が搭載された構成とされている。

【0032】

ICチップ14上には、供給される電圧を所望の高い電圧に昇圧する昇圧回路であるステップアップレギュレータ回路(以下、SUR回路という。)16と、このSUR回路16に直列に接続される遮断素子であるフューズ18と、このフューズ18に直列に接続されるバッファ20と、フューズ18とバッファ20の共通接点と接地(グラウンド)間に接続される抵抗値がR(ここでは、R=100[Ω])の抵抗器21等が集積されている。

【0033】

集積回路10において、フューズ18と抵抗器21とバッファ20とは、論理出力設定回路34を構成する。

【0034】

なお、後に説明する集積回路10C、10D、10E、10F、10G、および電気・電子回路10A、10Bにおいても、フューズ18と抵抗器21とバッファ20とは、論理出力設定回路34を構成する。

【0035】

また、以下の説明においては、理解の容易化のために、SUR回路16とバッファ20の入力インピーダンス(入力抵抗)はそれぞれ無限大、出力インピーダンス(出力抵抗)はそれぞれゼロ値であるものとする。

【0036】

上記のSUR回路16は、基本的には、発振器と、これに接続されるトランスとこのトランスに接続されて直流を出力する平滑回路と、この平滑回路の出力を前記発振器にもどして発振強度を調節するフィードバック回路とを備えるスイッチングレギュレータの構成とされている。

【0037】

SUR回路16の入力端子は、端子であるボンディングパッド(以下、単にパッドまたは端子ともいう。)22に接続され、このパッド22は、金線あるいはアルミニウム線等のボンディングワイヤを介して特定の端子である外部電源入力端子24に接続されている。この実施の形態において、外部電源入力端子24に外部から印加される電圧Vdd(電源Vddともいう。)は、たとえば、Vdd=+3[V]とされている。

【0038】

この図1例の集積回路10において、SUR回路16は4倍の利得を有するように設計され、入力ノードに印加される電圧Vdd=+3[V]を+12[V]の電圧に昇圧して出力ノードに発生させる。

【0039】

バッファ20は、入力電圧がゼロ[V]のローレベルLの電圧であるときには、論理出力としてローレベルL(L=0[V])を発生し、入力電圧が、たとえば、+2.1[V]以上のハイレベルの電圧であるときには、論理出力としてハイレベルH(H=+3[V])を発生する。

【0040】

ICチップ14の接地は、接地端子であるパッド30、ボンディングワイヤを介して外部接地端子32に接続されている。

【0041】

なお、以下に説明する各回路においては、バッファ20や図示していない論理回路の電圧(電源)Vddと接地の記号は、繁雑となるので原則として省略する。

【0042】

この実施の形態の集積回路10は、基本的には、以上のように構成される。

【0043】

図2は、遮断素子であるフューズ18の具体的な構成例を示している。このフューズ18は、細い線幅とされたポリシリコン配線パターン18pを含み、一定以上の電流が流れると溶解し断線(溶断あるいは遮断)するように、線幅Wfと長さLfと厚みが決定されている。この実施の形態においては、溶断電流(遮断電流ともいう。)Ifが、If=120[mA]になるように設定加工されている。

【0044】

図1例の集積回路10において、上述したように、フューズ18と抵抗器21およびバッファ20は、論理出力設定回路34を構成する。この論理出力設定回路34の出力段であるバッファ20の出力端子には、種々の論理回路を接続することが可能である。

【0045】

このように構成される集積回路10に対して、図3に示すように、特定の端子あるいは特定の外部端子とされる外部電源入力端子24と、外部接地端子32との間に電圧Vdd=+3[V]の外部直流電源38が接続されたとき、外部電源入力端子24および端子22(図1参照)を通じてSUR回路16の入力端子に電圧Vdd=+3[V]が印加され、SUR回路16の出力側にその4倍の昇圧電圧+12[V]が発生する。

【0046】

これにより、フューズ18には、この昇圧電圧+12[V]を抵抗器21の抵抗値Rで割った電流I=12[V]÷100[Ω]=120[mA]=Ifが流れ、フューズ18は溶断される。

【0047】

この場合、電圧Vddの外部直流電源38が投入されてからフューズ18が溶断されるまでの僅かな時間は、バッファ20からハイレベルH(H=+3[V])が出力されているが、フューズ18が溶断されるとフューズ18の端子間が開放され、バッファ20の入力は、抵抗器21を通じて接地レベル、すなわちローレベルLに固定される。したがって、バッファ20の出力レベルは、フューズ18が溶断された後以降、永久にローレベルL(L=0[V])に固定される。

【0048】

換言すれば、この実施の形態にかかる集積回路10は、特定の端子(特定の外部端子)である外部電源入力端子24に印加された電圧Vddに基づいて不可逆的に遮断される遮断素子であるフューズ18を有し、このフューズ18が遮断されたとき、バッファ20の出力レベルにより論理出力設定回路34の論理出力が一定の論理出力、この場合、ローレベルLに不可逆的に固定されることになる。

【0049】

このように構成される集積回路10が、たとえば、メーカーあるいは工場からフィールドにおけるユーザに渡り、ユーザ側で集積回路10に最初に集積回路10に通電したとき、言い換えれば、ユーザが一度使用したとき、論理出力設定回路34を構成するバッファ20の固定論理出力によりこのバッファ20の出力側に接続される図示していない論理回路の論理状態が物理的に固定されることになる。

【0050】

このため、このように構成される集積回路10によれば、バッファ20の出力側に接続される論理回路のユーザ側での使用、いわゆる2次使用ができなくなるという機能を有する。

【0051】

なお、図1例では、電気・電子回路装置として集積回路10に適用した例を説明しているが、この発明は、集積回路10に限らず、ディスクリート部品により構成した電気・電子回路装置にも適用することができる。

【0052】

また、図1例では、SUR回路16を用いてフューズ18を溶断する構成としているが、図4に示すように、外部直流電源(電圧源)38のみによりフューズ18を直接溶断する電気・電子回路装置10Aの構成とすることも可能であり、また、図5に示すように、外部直流電流源39により直接溶断する電気・電子回路装置10Bのように構成とすることも可能である。なお、図4例および図5例の電気・電子回路装置10A、10Bにおいては、繁雑さを回避するためと理解の容易化のために、図1例の集積回路10に示したものと対応するものには同一の符号を付けている。図5例の電気・電子回路装置10Bでは、外部電源入力端子24とフューズ18との間に電流ブースターを設けて構成することもできる。

【0053】

なお、以降、図面により説明する回路あるいは装置においては、その図面よりも前に掲載した図面により説明した回路あるいは装置に示したものと同一なものあるいは対応するものには、同一の符号を付けてその詳細な説明は省略する。

【0054】

図6は、動作説明用の仮想的な集積回路10Cの構成を示している。

【0055】

この集積回路10Cでは、半導体チップ14Cを構成する論理出力設定回路34のバッファ20の出力がアンド回路(論理積回路)40の一方の入力ノードに接続され、アンド回路40の他方の入力ノードが、ボンディングパッド42を介してプラスチックパッケージ12の外部端子44に接続されている。また、アンド回路40の出力が電気的に書き込み消去が可能な記憶装置であるフラッシュメモリ46の読み書き制御用入力であるリード・ライト(読出書込)イネーブルポートR/Wに接続されている。

【0056】

このフラッシュメモリ46のアドレスポート、データポートおよび他のコントロールポートには、図示していないアドレスバス、データバスおよびコントロールバスを通じてCPU(central processing unit)および(または)DMA(direct memory access)ICが接続されている。

【0057】

この図6例の仮想的な集積回路10Cにおいて、フラッシュメモリ46のリード・ライトイネーブルポートR/Wに、論理レベル(ハイレベル)Hが供給されたとき、フラッシュメモリ46に対して書き込みと消去が可能となり(書込モードという。)、論理レベル(ローレベル)Lが供給されたとき、フラッシュメモリ46は読出モードとなり読出専用メモリとして機能する。

【0058】

バッファ20の出力レベルが仮想的にハイレベルHであると仮定するとき、アンド回路40の一方の入力ノードがハイレベルHとなるので、パッケージ12Cの外部端子44に供給されるリード・ライト(読出書込)コマンド信号R/Wは、そのまま、アンド回路40の他方の入力ノードを介してフラッシュメモリ46に対する書込モードあるいは読出モードを選択するコマンド信号となる。このとき、外部端子44は、外部書込読出イネーブル端子(読み書き制御用外部端子)として機能する。

【0059】

上述したように、それぞれが外部端子である外部電源入力端子24と外部接地端子32との間に電圧Vdd=+3[V]の外部直流電源38が接続されると、SUR回路16の出力高電圧によりフューズ18が溶断され、バッファ20の出力側に接続されるアンド回路40の一方の入力ノードがローレベルLに不可逆的に固定されるので、アンド回路40の出力端子に接続されているフラッシュメモリ46のリード・ライトイネーブルポートR/Wは読出モードに固定される。これ以降、読み書き制御用外部端子44に供給されるリード・ライトコマンド信号R/Wは無効となる。

【0060】

このような回路構成を有する集積回路10Cでは、特定の外部端子である外部電源入力端子24に電圧が印加される前には、バッファ20の出力を仮想的にハイレベルHにできることを条件として、読み書き制御用外部端子44に供給するリード・ライトコマンド信号R/Wを利用してフラッシュメモリ46に対しての読み書き制御が可能であるが、外部電源入力端子24に一度外部直流電源38が接続されると電圧Vddによりフューズ18が溶断される。フューズ18が溶断されると、論理出力設定回路34の論理出力がローレベルLに不可逆的に固定され、2度とフラッシュメモリ46への再書き込みができなくなる。これ以降、フラッシュメモリ46は読出専用メモリとしてのみ使用することができる。

【0061】

ところで、この図6例の仮想的な集積回路10Cにおいては、パッケージ12Cの外部電源入力端子24と外部接地端子32との間に一度外部直流電源38が接続されると、フラッシュメモリ46には2度と書込ができなくなるので、工場などでの初期書込時には、ユーザから見えない形での特殊な書込構造を備える必要がある。

【0062】

そのため、パッケージに組み立てる前のウエハーの段階では、アンド回路40の出力ノードに接続されているフラッシュメモリ46のリード・ライトイネーブルポートR/Wにプローブ用の内部パッドを設け、さらに、フラッシュメモリ46にのみ電源が供給されるような内部パッドを設けることにより、書込制御を行うことなどが考えられるが、組み立てられた状態のいわゆる半導体パッケージ12の最終製品状態で、工場側で初期書込制御ができることがより生産性が高いと考えられる。

【0063】

図7は、読み書き制御用外部端子50によりパッケージング後でも初期書込の制御を可能とした集積回路10Dの構成を示している。

【0064】

すなわち、この集積回路10Dでは、半導体チップ14Dの中のSUR回路16とフューズ18との間に1回路2接点の半導体スイッチ52を設け、可動接点が接続される共通接点52aをフューズ18に接続し、一方の固定接点52bをSUR回路16の出力に接続し、他方の固定接点52cを外部電源入力端子24に接続されているパッド22に接続している。さらに、このスイッチ52の共通接点52aを切り換えるための切換制御端子52dを読み書き制御用内部端子としてのパッド54に接続し、このパッド54とパッケージ12Dの初期読み書き制御用外部端子50とをワイヤボンディングにより接続している。なお、スイッチ52の切換制御端子52dとパッド54との共通接続点と接地との間には、抵抗値が100[kΩ]のプルダウン抵抗器56が接続されている。

【0065】

ここで、スイッチ52は、切換制御端子52dにハイレベルHが加えられているときに、共通接点52aと固定接点52cとが接続され、切換制御端子52dがローレベルLとされているときに、共通接点52aとSUR回路16の出力側の固定接点52bとが接続されるように構成されている。

【0066】

このように構成される集積回路10Dは、以下に詳しく説明するように、ICチップ14Dのパッケージング前にはそれぞれが内部端子であるパッド22、30、42、54を利用して初期書込が可能であり、ICチップ14Dのパッケージング後にはそれぞれが外部端子である端子24、32、44、50を利用して初期書込が可能である。

【0067】

すなわち、工場等で初期書込を行う際、まず、初期読み書き制御用外部端子50にハイレベルHを印加した状態で外部電源入力端子24に外部直流電源Vdd=3[V]を印加する。これにより、スイッチ52の共通接点52aは、SUR回路16の出力側ではない固定接点52c側に直ちに接続される。

【0068】

そして、フューズ18には、外部電源入力端子24、パッド22およびスイッチ52を介して電源電圧Vdd=+3[V]が印加される。このとき、フューズ18に流れる電流は、電源電圧Vddを抵抗器21の抵抗値Rで割った3[V]÷100[Ω]=30mAとなる。フューズ18のポリシリコンのパターンは、30mAでは遮断しなく、120mAで遮断するように加工しているので、フューズ18は断線することなく、バッファ20の入力には電源電圧VddのハイレベルHが入力される。

【0069】

これによりアンド回路40のバッファ20の出力側ノードがハイレベルHとされるので、フラッシュメモリ46の読み書き制御入力ポートであるリード・ライトイネーブルポートR/Wは、読み書き制御用外部端子44に供給されるコマンド信号R/Wのレベルがそのまま供給され、たとえば、コマンド信号R/WがハイレベルHとされることで、フラッシュメモリ46に対して書込処理を行うことができる。

【0070】

なお、初期読み書き制御用外部端子50は、この集積回路10Dの例のようにパッケージ12Dの外部端子であるが、ICチップ14上のパッド54だけ設け、初期読み書き制御用外部端子50をパッケージ12Dの外側には出さない、いわゆるボンディングオプションとすることにより、読み書き制御用外部端子50を、完全にユーザから見えなくすることができる。この場合、パッド54は、初期読み書き制御用内部端子として機能するので、工場での初期書込時には、ICチップ14のウエハーテスト工程前後のパッド54、42、22、30等に対するプロービングにより行うことができる。

【0071】

図8は、スイッチ52の具体例の回路構成を示している。このスイッチ52は、電力消費の少ないCMOS(PMOS+NMOS)トランジスタによるトランスミッションゲート61、62とインバータ63からなるマルチプレクサの構成とされている。

【0072】

図9は、図8に示すスイッチ52の動作を表す真理値表64を示しており、切換制御端子52dに加えられるハイレベルHあるいはローレベルLの制御入力をD、固定接点52cへの入力をA、固定接点52bへの入力をB、共通接点52aに現れる出力をCとするときの、制御入力Dに対する入力A,Bおよび出力Cの論理関係を示している。すなわち、制御入力DがハイレベルHであるときには、入力Aが出力Cとされ、制御入力DがローレベルLであるときには、入力Bが出力Cとされる。

【0073】

このように構成される集積回路10Dは、たとえば、記憶装置がカートリッジを採用する携帯型ゲーム機等の前記カードリッジの中に組み込むことができる。このように構成した場合、カートリッジ内にソフトウエア格納用のメモリとしてフラッシュメモリを使用したとき、そのフラッシュメモリの内容を、ユーザ側で書き換えて2次使用がなされるのを未然に防止することができる。なお、カートリッジ式記憶装置において、ROM(読出専用メモリ)ではなくフラッシュメモリを用いる利点は、たとえば、需要に合わせて出荷の直前にソフトウエアを書き込めるようにすることで、特定ソフトウエアが書き込まれたカートリッジの在庫の最小化、ひいては販売の高効率化が図られるからである。

【0074】

図10は、さらに他の実施の形態の集積回路10Eの構成を示している。この集積回路10Eは、図7例の集積回路10Dではフューズ18の遮断後にも、集積回路10Dの通常通電中にはSUR回路16に電源電圧Vddがかかり、このSUR回路16での電力消費が定常的に発生するという問題を解決した回路である。すなわち、集積回路10Dを携帯用機器などバッテリ駆動の機器に使用した場合にはバッテリにより動作時間が短くなることから好ましくないという要請に応えるためのものである。

【0075】

この図10例の集積回路10Eは、パッケージ12Eに設けられている外部電源入力端子24を通じて外部直流電源38(電源Vdd)を投入後、一定時間だけSUR回路16を動作させるようにした回路で、通常使用中のSUR回路16での電力消費を節約した例を示している。

【0076】

具体的に、この集積回路10Eでは、パッド22とSUR回路16との間に上記スイッチ52と同一構成の半導体スイッチ66を設けるとともに、このスイッチ66の切換制御端子66dとパッド22との間に、この切換制御端子66dに切換制御信号Prを供給するパワーオンリセット回路(POR回路)68を設けている。このPOR回路68とスイッチ66とは、電力消費制限回路を構成する。

【0077】

図11は、POR回路68の具体例を示している。外部電源入力端子24を通じてパッド22に電源電圧Vddが印加されると、外付けの電解コンデンサ等のコンデンサ72に徐々に電荷が蓄積され、シュミットトリガタイプのバッファ73の入力ノードでは、抵抗器70と抵抗器71の抵抗値R1とR2の比で決まる中間電圧{Vdd×R2/(R1+R2)}まで時定数で決まる一定時間(コンデンサ72の容量Cで決定することができる。)を要して到達する。

【0078】

シュミットトリガタイプのバッファ73は、スイッチ66のチャタリングを防止する機能を有する。

【0079】

この場合、図12のタイムチャートに示すように、スイッチ66の切換制御端子66dには、外部電源入力端子24に電源Vddが投入された時点t0から一定時間(パワーオンリセット期間ともいう。)Td経過後の時点t1にローレベルLからハイレベルHに遷移するパワーオンリセット信号である切換制御信号Prが発生する。

【0080】

ここで、スイッチ66は、電源Vddの投入後一定時間Tdの間は、共通接点66aと固定接点66bとが切換制御信号PrのローレベルLによって接続され、切換制御信号PrがハイレベルHになったとき、共通接点66aが接地電位となっている固定接点66cに切り換えられる。

【0081】

この集積回路10Eにおいては、フューズ18が断線に至るまでの時間をパワーオンリセット期間Tdより短い期間に設定加工しておくことで、フューズ18の遮断をこのパワーオンリセット期間Td内に行い、なおかつパワーオンリセット期間Td経過後、換言すればパワーオンリセットの解除後に、SUR回路16の入力ノードがスイッチ66を通じて接地されるので、パワーオンリセット期間Tdの解除後には、SUR回路16による電力消費をなくすことができる。

【0082】

万が一、最初のパワーオンリセット期間Tdの通電によりフューズ18を遮断できなかった場合でも、2度目、3度目の通電時には、フューズ18を遮断できる可能性が高い。このような場合においても、各パワーオンリセット期間Td経過後においては、通常動作中のSUR回路16での電力消費をなくすことができる。

【0083】

図13は、さらに他の例のPOR回路68Aの構成を示している。このPOR回路68Aでは、デジタル回路であるプリセットダウンカウンタ76を用いている。電源投入後に、カウンタ76は、クロック発生器78で発生するクロックパルスをプリセット数だけ計数したとき、ローレベルLからハイレベルHに立ち上がる切換制御信号Pr(図12参照)を発生する。この図13例のPOR回路68Aでは、図11例のアナログ回路のPOR回路68に比較して、クロック発生器78が必要となるが、クロックパルスによりSUR回路16を動作させる時間の計測が正確に行える他、電解コンデンサなどの形状の大きい外付け部品となるコンデンサCが不要となる利点がある。

【0084】

なお、スイッチ66を構成する代わりに、POR回路68、68Aからのパワーオンリセット信号である切換制御信号Prを直接SUR回路16に入力させ、このSUR回路16の内部回路で動作を停止させる(電力消費を止める)ように構成することもできる。

【0085】

図14は、さらに低消費電力化を進めた回路例を示している。この図14例の集積回路10Fでは、パッケージ12F中に収容されているICチップ14F中、フューズ18とバッファ20の共通接続点とスイッチ66の切換制御端子66dとの間に帰還ループを構成するインバータ80を接続する構成としている。電源Vddを投入した後、フューズ18が遮断するまでの期間は、電源Vddが固定接点66bおよび共通接点66aを介してSUR回路16の入力ノードに供給され、このSUR回路16から高電圧がフューズ18に印加される。

【0086】

フューズ18が遮断すると、バッファ20の入力ノード、すなわち、インバータ80の入力ノードは抵抗器21によりローレベルLに遷移し、インバータ80の出力レベルはローレベルLからハイレベルHに遷移する。この帰還ループにより、スイッチ66が切り換えられ、フューズ18が遮断した後は、SUR回路16の入力ノードは共通接点66a、固定接点66cを介して接地レベルに固定されることになり、SUR回路16が永久に停止し、このSUR回路16での電力消費が発生しない。このように、インバータ80とスイッチ66とは、フューズ18が遮断されたことを検出して、SUR回路16の電力消費を低減あるいは無くする電力消費制限回路として機能する。

【0087】

ただし、この図14例の集積回路10Fでは、電源Vddの投入時に、フューズ18が溶断するまでは、消費電力の比較的に大きいSUR回路16が動作することになる。

【0088】

実際上、フューズ18は、必ずしも1回の通電で溶断する必要がなく、2回以上の通電により溶断してもよい。そこで、この電力消費の比較的に大きいSUR回路16の動作時間を制限するためと、一旦フューズ18が溶断したときには、SUR回路16に電源Vddが永久的に供給されないようにするための両条件を満たす回路を図15に示す。

【0089】

この図15例の集積回路10Gは、図10のPOR回路68と集積回路10Eと図14のインバータ80とを合わせた回路であり、POR回路68の出力とインバータ80の出力を2入力とし、出力がスイッチ66の切換制御端子66dに接続されるオア回路82を挿入している。

【0090】

この集積回路10Gによれば、パッケージ12Gに設けられている外部電源入力端子24を通じての電源Vddの投入時における一定期間であるパワーオンリセット期間Tdでは、POR回路68の制御の下にスイッチ66の固定接点66bと共通接点66aが接続された状態となりSUR回路16が図10例の集積回路10Eと同様に動作しフューズ18に対して溶断用の電流を供給する。

【0091】

そして、一旦、フューズ18が溶断した後は、電源Vddの投入直後に帰還ループを構成するインバータ80のハイレベルHの出力によりスイッチ66の共通接点66aが接地レベルとなっている固定接点66cに接続されてSUR回路16への通電が回避される。このように、この図15例の集積回路10Gによれば、低消費電力化とフューズ18への初期通電期間の一定化を図ることができる。

【0092】

なお、この発明は、上述の実施の形態に限らず、この発明の要旨を逸脱することなく、種々の構成を採り得ることはもちろんである。

【0093】

【発明の効果】

以上説明したように、この発明によれば、電気・電子回路装置の特定の端子に電圧が印加されたときあるいは電流が供給されたとき、論理出力設定回路の論理出力が一定の論理出力に不可逆的に構成されるようにしているので、この電気・電子回路装置を利用すれば、簡単な構成で、電気・電子製品のハードウエアの改造、およびソフトウエアの改竄や2次利用等を物理的に防止することができる。

【0094】

ここで、特定の端子を、たとえば電源入力端子とすることにより、ユーザがフィールドにおいて一度使用したとき、その電気・電子回路装置に含まれる、たとえば、記憶装置等のフィールドでの2次使用を不可能とすることができる。

【0095】

さらに、この発明の効果を具体的に説明すると、この発明の電気・電子回路装置を組み込んだ記憶装置を有する製品を、たとえば、LSIとして製造するメーカ内では、特殊な治工具等によりLSI内蔵のフラッシュメモリ等の記憶装置に対するプログラムのインストール、チップの出荷テスト、製品の動作試験等を行うことが可能である。その一方、市場に出荷された後のユーザサイドでのLSI等のハードウエアの改造、記憶装置に記憶されたソフトウエアの改竄、2次利用などの不正の可能性のある行為を物理的に阻止することができる。この発明によれば、このような仕組みを電気・電子回路装置に組み込むことができる。

【図面の簡単な説明】

【図1】この発明の一実施の形態が適用された集積回路の構成を示す回路ブロック図である。

【図2】フューズの具体的な構成説明に供されるパターン図である。

【図3】集積回路に電源を供給した状態を示す模式図である。

【図4】この発明の他の実施の形態の構成を示す回路ブロック図である。

【図5】この発明のさらに他の実施の形態の構成を示す回路ブロック図である。

【図6】動作説明に供される仮想的な集積回路例の構成を示す回路ブロック図である。

【図7】フューズの遮断前には外部端子入力により記憶装置を書込可能にできる構成を有する集積回路の構成を示す回路ブロック図である。

【図8】図7例中、マルチプレクサの構成例を示す回路図である。

【図9】図8例のマルチプレクサの動作を示す真理値表を示す図である。

【図10】パワーオンリセット回路の採用によりフューズ遮断後の低消費電力化を図った集積回路例の構成を示す回路ブロック図である。

【図11】パワーオンリセット回路の一例の構成を示す回路図である。

【図12】図10例の集積回路の動作説明に供されるタイムチャートである。

【図13】パワーオンリセット回路の他の例の構成を示す回路図である。

【図14】フューズ遮断後の低消費電力化を図った他の集積回路例の構成を示す回路ブロック図である。

【図15】図10例の回路と図14例の回路とを合成した集積回路例の構成を示す回路ブロック図である。

【符号の説明】

10、10C、10D、10E、10F、10G…集積回路

10A、10B…電気・電子回路装置

12、12C、12D、12E、12F、12G…パッケージ

14…ICチップ

16…ステップアップレギュレータ回路(SUR回路、昇圧回路)

18…フューズ(遮断素子) 18p…ポリシリコン配線パターン

20…バッファ 21、56、70、71…抵抗器

22、30、42、54…パッド 24…外部電源入力端子

32…外部接地端子 34…論理出力設定回路

38…外部直流電源 40…アンド回路

44…外部端子 46…フラッシュメモリ(記憶装置)

52、66…半導体スイッチ

61、62…トランスミッションゲート

63、80…インバータ

68、68A…パワーオンリセット回路(POR回路)

72…コンデンサ

73…シュミットトリガタイプのバッファ

76…カウンタ 78…クロック発生器

Claims (9)

- 電気・電子回路装置の電源入力端子に電圧が印加されたとき、論理出力が一定の論理出力に不可逆的に固定される論理出力設定回路と、

この論理出力設定回路の出力側に読み書き制御入力が接続される電気的に書き込み消去が可能な記憶装置とを有し、

前記記憶装置の前記読み書き制御入力に、読み書き制御用端子が接続され、

前記電源入力端子に電圧が印加される前には、前記記憶装置にのみ電源が供給された状態で前記読み書き制御用端子を利用して前記記憶装置に対する読み書き制御が可能とされ、

前記電源入力端子に電圧が印加されて、前記論理出力設定回路が一定の論理出力に不可逆的に固定された場合に、前記記憶装置の書き込み消去を不可能とし、読み出しのみを可能とする

ことを特徴とする電気・電子回路装置。 - 請求項1記載の電気・電子回路装置において、

前記論理出力設定回路の出力と前記読み書き制御用端子とを論理積回路の入力に接続し、前記論理積回路の出力を前記記憶装置の前記読み書き制御入力に接続した

ことを特徴とする電気・電子回路装置。 - 請求項1又は2記載の電気・電子回路装置において、

前記論理出力設定回路は、前記電源入力端子に印加された電圧に基づいて不可逆的に遮断される遮断素子を有し、

前記論理出力設定回路は、前記遮断素子が遮断されることにより電流が供給されなくなり、一定の論理出力に不可逆的に固定される

ことを特徴とする電気・電子回路装置。 - 請求項3記載の電気・電子回路装置において、

前記電源入力端子と前記遮断素子との間に昇圧回路が設けられている

ことを特徴とする電気・電子回路装置。 - 請求項4記載の電気・電子回路装置において、

前記電源入力端子に電圧が印加されたときから一定期間前記昇圧回路を動作状態とするパワーオンリセット回路を含む

ことを特徴とする電気・電子回路装置。 - 特定の外部端子に電圧が印加されたとき、論理出力が一定の論理出力に不可逆的に固定される論理出力設定回路と、

この論理出力設定回路の出力側に接続される電気的に書き込み消去が可能な記憶装置と、

前記論理出力設定回路に設けられ、前記特定の外部端子に印加された電圧に基づいて不可逆的に遮断される遮断素子と、

前記特定の外部端子と前記遮断素子との間に設けられている昇圧回路とを有し、

前記遮断素子は、前記特定の外部端子に電圧が印加されたときに前記昇圧回路の出力により遮断され、

前記昇圧回路には、前記遮断素子が遮断されたことを検出して、前記昇圧回路の電力消費を低減あるいは無くする電力消費制限回路が接続される

ことを特徴とする電気・電子回路装置。 - 特定の外部端子に電圧が印加されたとき、論理出力が一定の論理出力に不可逆的に固定される論理出力設定回路と、

この論理出力設定回路の出力側に接続される電気的に書き込み消去が可能な記憶装置と、

前記論理出力設定回路に設けられ、前記特定の外部端子に印加された電圧に基づいて不可逆的に遮断される遮断素子と、

前記特定の外部端子と前記遮断素子との間に設けられている昇圧回路とを有し、

前記特定の外部端子に電圧が印加されたときから一定期間前記昇圧回路を動作状態とするパワーオンリセット回路を含み、

前記遮断素子は、前記パワーオンリセット回路により動作状態とされた前記昇圧回路の出力により遮断され、

前記昇圧回路には、前記遮断素子が遮断されたことを検出して、前記昇圧回路の電力消費を低減あるいは無くする電力消費制限回路が接続される

ことを特徴とする電気・電子回路装置。 - 請求項3〜7のいずれか1項に記載の電気・電子回路装置において、

該電気・電子回路装置が集積回路により構成され、

前記遮断素子が、シリコン配線パターンにより形成されている

ことを特徴とする電気・電子回路装置。 - 請求項1〜8のいずれか1項に記載の電気・電子回路装置において、

前記電気・電子回路装置は集積回路により構成されている

ことを特徴とする電気・電子回路装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000264178A JP3671140B2 (ja) | 1999-08-31 | 2000-08-31 | 電気・電子回路装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP24593399 | 1999-08-31 | ||

| JP11-245933 | 1999-08-31 | ||

| JP2000264178A JP3671140B2 (ja) | 1999-08-31 | 2000-08-31 | 電気・電子回路装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001142783A JP2001142783A (ja) | 2001-05-25 |

| JP3671140B2 true JP3671140B2 (ja) | 2005-07-13 |

Family

ID=26537480

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000264178A Expired - Fee Related JP3671140B2 (ja) | 1999-08-31 | 2000-08-31 | 電気・電子回路装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3671140B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4706626B2 (ja) * | 2006-11-30 | 2011-06-22 | 株式会社デンソー | 電子制御装置 |

| JP5186925B2 (ja) * | 2008-01-11 | 2013-04-24 | 株式会社リコー | 半導体装置及びその製造方法 |

| WO2010095612A1 (ja) | 2009-02-23 | 2010-08-26 | ソニー株式会社 | メモリ装置 |

| JP6639268B2 (ja) * | 2016-02-29 | 2020-02-05 | 日本放送協会 | 記憶装置 |

-

2000

- 2000-08-31 JP JP2000264178A patent/JP3671140B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001142783A (ja) | 2001-05-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100798286B1 (ko) | 회로 장치 | |

| US7196950B2 (en) | Non-volatile semiconductor storage device performing ROM read operation upon power-on | |

| KR100998836B1 (ko) | 전기적으로 1회 프로그래밍가능하고 1회 소거가능한 퓨즈 | |

| US5566107A (en) | Programmable circuit for enabling an associated circuit | |

| EP1895544B1 (en) | Electrical fuse circuit, memory device and electronic part | |

| KR100607180B1 (ko) | 반도체 메모리 장치의 파워 업 리셋 회로 | |

| US5432741A (en) | Circuit for permanently disabling EEPROM programming | |

| US7852697B2 (en) | Integrated circuit feature definition using one-time-programmable (OTP) memory | |

| JP3671140B2 (ja) | 電気・電子回路装置 | |

| JP3971565B2 (ja) | 半導体装置及び半導体装置初期設定方法 | |

| KR100361658B1 (ko) | 반도체 메모리 장치 및 이 장치의 전압 레벨 조절방법 | |

| JP6603606B2 (ja) | 半導体装置 | |

| JP3763081B2 (ja) | 入力バッファ | |

| US20040184316A1 (en) | Programmable circuit and its method of operation | |

| KR100342452B1 (ko) | 제품 사양 재설정 기능을 갖는 반도체 집적 회로 및 그 제품 사양 설정 방법 | |

| KR100316520B1 (ko) | 오동작방지장치를내장한마이크로콘트롤러 | |

| KR101842143B1 (ko) | 안티퓨즈 제어 회로 | |

| JPH11328991A (ja) | メモリ素子用アンチヒューズ安定化装置 | |

| JPH05101201A (ja) | オプシヨン設定回路 | |

| KR100728974B1 (ko) | 반도체 메모리 장치의 퓨즈 연결 제어 회로 | |

| KR20140069650A (ko) | 집적회로 및 집적회로의 동작방법 | |

| KR20030049667A (ko) | 퓨즈박스 내의 전류소모를 최소화한 반도체장치 | |

| EP1102174A1 (en) | Semiconductor device with non-volatile mode register | |

| JPH0319199A (ja) | 電源選択回路 | |

| JP2004088458A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040810 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041008 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20041124 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050121 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20050215 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050408 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050418 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090422 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090422 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090422 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090422 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100422 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110422 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120422 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130422 Year of fee payment: 8 |

|

| LAPS | Cancellation because of no payment of annual fees |