JP3661890B2 - 画像データ送信方法及び画像データ受信方法 - Google Patents

画像データ送信方法及び画像データ受信方法 Download PDFInfo

- Publication number

- JP3661890B2 JP3661890B2 JP34778095A JP34778095A JP3661890B2 JP 3661890 B2 JP3661890 B2 JP 3661890B2 JP 34778095 A JP34778095 A JP 34778095A JP 34778095 A JP34778095 A JP 34778095A JP 3661890 B2 JP3661890 B2 JP 3661890B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- image data

- bits

- bit

- synchronization

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/14—Digital output to display device ; Cooperation and interconnection of the display device with other functional units

- G06F3/147—Digital output to display device ; Cooperation and interconnection of the display device with other functional units using display panels

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N7/00—Television systems

- H04N7/24—Systems for the transmission of television signals using pulse code modulation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N7/00—Television systems

- H04N7/24—Systems for the transmission of television signals using pulse code modulation

- H04N7/52—Systems for transmission of a pulse code modulated video signal with one or more other pulse code modulated signals, e.g. an audio signal or a synchronizing signal

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N7/00—Television systems

- H04N7/24—Systems for the transmission of television signals using pulse code modulation

- H04N7/52—Systems for transmission of a pulse code modulated video signal with one or more other pulse code modulated signals, e.g. an audio signal or a synchronizing signal

- H04N7/54—Systems for transmission of a pulse code modulated video signal with one or more other pulse code modulated signals, e.g. an audio signal or a synchronizing signal the signals being synchronous

- H04N7/56—Synchronising systems therefor

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Theoretical Computer Science (AREA)

- General Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Compression Of Band Width Or Redundancy In Fax (AREA)

- Compression Or Coding Systems Of Tv Signals (AREA)

- Two-Way Televisions, Distribution Of Moving Picture Or The Like (AREA)

- Time-Division Multiplex Systems (AREA)

- Dc Digital Transmission (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Facsimiles In General (AREA)

Description

【目次】

以下の順序で本発明を説明する。

発明の属する技術分野

従来の技術(図6及び図7)

発明が解決しようとする課題(図8及び図9)

課題を解決するための手段(図5)

発明の実施の形態(図1〜図5)

(1)実施例の構成

(1−1)画像表示システムの構成

(1−2)画像データ変換の規則

(2)実施例の動作

(3)実施例の効果

(4)他の実施例

発明の効果

【0002】

【発明の属する技術分野】

本発明は画像データ送信方法及び画像データ受信方法に関し、例えばコンピユータで処理する画像を表示する液晶表示装置に代表されるデジタル制御の表示装置に画像データを伝送する際に適用し得る。

【0003】

【従来の技術】

図6に示すように、この種の液晶表示装置1は、一般に、コンピユータで処理するデジタルの3原色画像データS1〜S6をそれぞれの原色毎にアナログ化した画像信号S10〜S12が伝送される。液晶表示装置1は、この画像信号S10〜S12をアナログデジタルコンバータ5〜7によつてデジタルの画像データS13〜S18に戻してリアルタイムで画像の表示状態を制御している。

【0004】

この方法は、表示画素数及び階調の増加に応じて高速、多ビツトのアナログデジタルコンバータが必要になるため、液晶表示装置の製造コストが増大するという欠点があつた。このため、図7に示すように、コンピユータ内で並列に処理されている画像データS21〜S26を並列で液晶表示装置10に伝送する方法が一部で採用されている。

【0005】

【発明が解決しようとする課題】

ところで、図8に示すように、複数の芯線を束ねた伝送ケーブル13で画像データS27〜S32を並列に伝送する場合は、伝送された画像データS27〜S32間の相互干渉によつてスキユー(同期ずれ)やクロストークが発生する。このため、伝送ケーブル13の伝送容量及び伝送距離が制限されると共に、伝送ケーブル13やコネクタが大型化するという問題があつた。

これを避けるため、画像データを直列化して伝送することが考えられる。この方法によれば、画像データのスキユーやクロストークを排除して画像データを伝送することができる。

【0006】

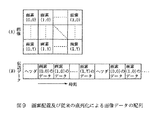

ところが、図9(B)に示すように、従来の直列化では、1枚の画像のそれぞれの画素(0,0) 〜(X,Y) の画像データを単純にあるビツト数で1ワードとなる直列の画像データに変換していた。因みに、図9(A)に示すように、1枚の画像は、水平及び垂直方向にそれぞれX個及びY個の画素で構成されている。

この変換方法では、ヘツダと呼ばれる制御データを画像データに付加して、受信した直列の画像データを再び画素毎の画像データに戻すときのワード同期を確立する必要があつた。

【0007】

ところが、このヘツダの1ワードは、画像データの1ワードを構成するビツト数と異なるビツト数で構成されていた。このため、液晶表示装置内の画像制御回路は、直列の画像データからワード長さが異なるヘツダを識別して取り出す必要があるため、複雑な構成となるという欠点がある。

【0008】

この方法では、ヘツドを取り出すとき画像データが中断され、安定して受信できないという問題があつた。さらにデジタルの画像データを並列に伝送する方法でも、画像データを伝送するケーブルに加えて、垂直同期データ及び水平同期データを伝送するそれぞれ専用のケーブルが別個に必要であるため、コネクタや伝送ケーブルが大きくなつて取扱いが煩雑になるという欠点があつた。

【0009】

本発明は以上の点を考慮してなされたもので、画像データの送受信を中断させずに画像データ及び同期データを1つの伝送路によつて送受信し得る画像データ送信方法及び画像データ受信方法を提案しようとするものである。

【0010】

【課題を解決するための手段】

かかる課題を解決するため本発明においては、mビツト単位の画像データを送信するための画像データ送信方法であつて、画像データの同期タイミングを設定させるための同期データを送信せずにmビツトの画像データを送信する場合には、mビツトの画像データを変換することによりn(但しn>m)ビツトの変換後データを生成し、当該生成した変換後データを直列送信する第1のステツプと、同期データとmビツトの画像データとを送信する場合には、mビツトの画像データに対して同期データを示すn−mビツトの直列コードを付加することによりnビツトの付加後データを生成し、当該生成した付加後データを直列送信する第2のステツプとを有し、第1のステツプでは、mビツトのデータと、いかなる組み合わせで順次直列送信されても同一論理ビツトがk(但しk<n−m)個以上連続しないように選択されたnビツトのデータとを対応付けてなる変換表に基づいて、mビツトの画像データを変換することによりnビツトの変換後データを生成し、第2のステツプでは、mビツトの画像データに対して、同一論理ビツトがk個以上連続した特定ビツト列を含む直列コードを付加することにより、nビツトの付加後データを生成するようにした。

【0011】

また本発明においては、mビツト単位の画像データを受信するための画像データ受信方法であつて、伝送路を介して直列受信したn(但しn>m)ビツトの受信データから、画像データの同期タイミングを設定させるための同期データを示すn−mビツトの直列コードを検出する第1のステツプと、第1のステツプによつてnビツトの受信データから直列コードを検出した場合、同期タイミングを設定すると共にnビツトの受信データから直列コードを除くことによりmビツトの画像データを得る第2のステツプと、第1のステツプによつてnビツトの受信データから直列コードを検出しない場合、nビツトの受信データを変換することによりmビツトの画像データを得る第3のステツプとを有し、第1のステツプでは、nビツトの受信データから、同一論理ビツトがk(但しk<n−m)個以上連続した特定ビツト列が含まれる直列コード中の特定ビツト列を検出することにより直列コードを検出し、第3のステツプでは、いかなる組み合わせで順次直列送信されても同一論理ビツトがk個以上連続しないように選択されたnビツトのデータと、mビツトのデータとを対応付けてなる変換表に基づいて、nビツトの受信データを変換することによりmビツトの画像データを得るようにした。

【0012】

この結果、送信側から直列送信されるnビツトのデータには常に画像データが含まれる。これにより受信側は、送信側から直列受信したnビツトのデータから常に画像データを得ることができる。

【0013】

【発明の実施の形態】

以下図面について、本発明の一実施例を詳述する。

【0014】

(1)実施例の構成

(1−1)画像表示システムの構成

図1は全体として画像表示システム20を示し、本体21においてデータクロツクS40とmビツト並列の画像データS41〜S57とこれの同期データS58及びS59とを時分割多重によつて重畳してnビツト直列のデータコードS60を生成する。画像表示システム20は、このデータコードS60を1本の伝送路としての伝送ケーブル22を介して液晶表示装置23に与えて、データコードS60をデータブロツクS61とmビツト並列の画像データS62〜S78とこれの同期データS79及びS80とに戻す。

これにより、画像表示システム20は、本体21において並列処理している画像を液晶表示装置23の画像表示部24上に表示する際の表示状態を画素毎の画像データを途切れさせずにリアルタイムで制御する。

【0015】

本体21は、マイクロコンピユータ(図示せず)で制御され、外部より与えられた画像データをビデオRAM(図示せず)に展開している。本体21は、ビデオRAM上の画素毎のmビツト並列の画像データをそれぞれのビツトでなる画像データS40〜S57によつて、集積回路構成の符号化回路25に与える。これにより、本体21は、符号化回路25において画素毎のmビツトをm<nであるnビツトコードに変換して、それぞれのnビツトコードで1ワードを構成したデータコードS60を生成させる。

【0016】

但し、同期データS58及びS59を伝送するとき、本体21は、符号化回路25において同期データS58及びS59を、k<n−mとして同一論理ビツトがk個連続した特定ビツト列を含むn−mビツトコードに符号化する。またこのとき本体21は、画素の画像データの符号化を停止させる。続いて、本体21は、符号化回路25において同期データS58又はS59を示すn−mビツトコードを、符号化しなかつたmビツトの画像データの先頭に付加して、他のワードと同一のnビツトでワードを構成する。

【0017】

液晶表示装置23は、集積回路構成の復号化回路26において直列のデータコードS60から同期データを得て、この同期データに基づいたタイミングでデータコードS60をnビツト毎に区切つてそれぞれのワードを弁別する。データコードS60の全てのワードがnビツトで構成されていることにより、復号化回路26内のワードを弁別する回路を簡易に構成することができる。液晶表示装置23は、復号化回路26においてそれぞれのワードをnビツトコードからmビツトに戻し、mビツトのそれぞれのビツトでなる並列の画像データS61〜S78を画像制御回路27に与える。

【0018】

但し、ワードの先頭側のn−mビツトから同一論理ビツトがk個連続した特定ビツト列を復号化回路26において検出すると、液晶表示装置23は同期データを得たと判断する。これにより、液晶表示装置23は、特定ビツト列に応じて垂直同期データS79や水平同期データS80を復号化回路26において生成して、画像制御回路27に与える。

【0019】

続いて、液晶表示装置23は、特定ビツト列を含むn−mビツトコードを除いたmビツトを復号化回路26において復号することなく画像制御回路27に与える。これにより、液晶表示装置23は、途切れないmビツト並列の画素データS61〜S78のタイミングを画像制御回路27において垂直同期データS79や水平同期データS80によつて制御して、画像を画像表示部24に表示させる。

【0020】

復号化回路26は、例えばkが5である場合、図2に示す同期データ検出回路28を有し、直列のデータコードS60をこの同期データ検出回路28に与えて、同一論理ビツトが5個連続した特定ビツト列を検出する。同期データ検出回路28は、データコードS60を4つのDフリツプフロツプ29〜32で順次遅延させて1クロツク期間〜4クロツク期間遅延させた遅延画像データS81〜S84を生成する。

【0021】

同期データ検出回路28は、現在のデータコードS60と遅延画像データS81〜S84とをアンド回路33及びナンド回路34に条件入力として与える。

同期データ検出回路28は、4入力アンド回路33及び4入力ナンド回路34のそれぞれの出力S85及びS86をオア回路35に条件入力として与える。これにより、同期データ検出回路28は、データコードS60の論理「1」が5個連続した特定ビツト列と、論理「0」が5個連続した特定ビツト列とを検出することができる。

【0022】

(1−2)画像データ変換の規則

本体21は、符号化回路25においてmビツトをnビツトコードに変換する際に、所定の変換表を使用して、データコードS60が以下に示す第1〜第4の条件を満たすよう変換している。液晶表示装置23は、この所定の変換表を使用して、データコードS60のそれぞれのワードのnビツトコードをmビツトに逆変換する。

【0023】

この所定の変換表は、mビツトをnビツトコードに変換したときのnビツトコードの全ての組合せにおいて同一論理ビツトの最大連続数jがj<kを満たすようにnビツトの任意の論理配列のみが採用されている。またこの所定の変換表によつて任意のmビツトと任意のnビツトコードとが重複しないよう対応付けられる。

【0024】

符号化回路25は、第1〜第4の条件に加えて、上述したように、直列のデータコードS60のそれぞれのワードを常にnビツトで構成すると共に、全てのワードに画素データを含ませて画素データの伝送を途切れさせないように処理している。

【0025】

第1の条件は、直列のデータコードS60からクロツクを抽出し易くするため、データコードS60が多量のデータ遷移を含んでいることである。第2の条件は、データコードS60の論理「1」及び論理「0」の比が同等又はこれに近いことである。第3の条件は、データコードS60のnビツトコードをmビツトに戻すときのそれぞれのワードの区切りを検出できる性質をデータコードS60が有することである。第4の条件は、直列化のため冗長ビツトを元データに付加する場合、付加ビツト数が元データに比して少ないことである。

【0026】

第1の条件は、電圧が昇降を繰り返す直列のデータコードS60から直列データの論理「0」と論理「1」とを切り出すタイミング信号、即ちクロツクを復号化回路26において抽出するために必要である。復号化回路26は、クロツクをPLL(Phase Locked Loop )回路やSAWフイルタ共振等で抽出する。ところが、データ遷移が少ないと、PLL回路は離調し易くなり、フイルタの出力は低下する。このためデータ遷移は、4〜5ビツト毎に1回以上発生することが望ましい。

【0027】

例えば、撮像対象を撮像して得たいわゆる生の画像データでは、黒色を表示画面全面に表示した完全な黒色画像に対応した画像データが有り得るため、データ遷移が極端に少なくなることがある。このため、並列の画像データを直列に変換するとき、元の画像データは一般に何らかのデータ列に変換(コーデイング)されてデータ遷移が増やされる。

【0028】

データ遷移を増やす際には、一般にスクランブルやmビツトnビツト変換が使用される。前者は、疑似乱数発生回路を用いて、同一論理ビツトが長時間継続するデータが発生することを確率的に阻止する方法である。後者は、mビツトの元データをある規則に従つてnビツトのデータに変換することによつて、データ遷移を強制的に発生させる方法である。受信側においては、これらの逆変換によつて元データを再生する。

上述したように、符号化回路25は、後者を採用している。

【0029】

第2の条件は、直列データを高い伝送レートで伝送する過程で発生する信号波形の歪みや減衰に対して、受信マージンを確保する、即ち直流レベルを容易に再生するための条件である。この第2の条件を満たすには、論理「1」と論理「0」との比が1:7〜7:1以内であることが望ましい。

【0030】

第3の条件は、送信側において、ある時点の画素データとして1つのセツトであつた多ビツトのデータ(ワード)を受信側において1つのセツトとして切り出すタイミングを検出するための条件である。この第3の条件を満たすには、一般に直列データのどこかに直列データの他の部分には絶対に存在しない、又は極めて稀にしか存在しない特定ビツト列を含むデータ列いわゆるヘツダが挿入される。この直列コードとしてのヘツダによつて、ワードを切り出すタイミングを送信側から受信側に伝送することができる。上述したように、符号化回路25は、同一論理ビツトがk個連続した特定ビツト列を含むn−mビツトコードをヘツダとして挿入して同期タイミングを伝える。

【0031】

第4の条件は、上述した第3の条件を満たす目的で付加されるビツト、例えばmビツトnビツト変換で増えるビツトやヘツダのビツトが元データに比して少量であるということである。この第4の条件は、直列データの伝送レートが過度に上昇することを抑えて、直列伝送ハードウエアの負担を軽くするための条件であり、元データの1.4 倍を越えないことが望ましい。

【0032】

(2)実施例の動作

以上の構成において、液晶表示装置23の表示画面の横及び縦の画素数がそれぞれ1024及び768 であるとし、画素毎に赤色、緑色及び青色のそれぞれの階調を6ビツトで表示して6×3=18ビツト分の262,144 色を表示するとする。また表示速度は80〔画面/秒〕であるとし、同期データが垂直同期データ及び水平同期データで構成されるとする。この表示を実現する際、本体21は、80〔画面/秒〕×1024〔列〕×768 〔行〕≒62.9×106 〔個/秒〕の画素の画像データを画像制御回路27に与える必要がある。

【0033】

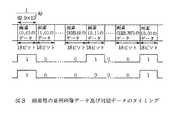

このとき図3に示すように、本体21は、1枚の画像毎に走査線上の最初の画素(0,0) から最後の画素(1023,767)までの画素毎の18ビツトの画像データを独立に、又は水平同期データや垂直同期データと共に、同期データの論理レベルに応じた異なる手順に従つて24ビツトデータコードに変換して伝送する。

【0034】

まず水平同期データ及び垂直同期データが論理「0」レベルである(以下、これを同期データが不活性であるという)ときを説明する。このとき、本体21は、符号化回路25において画素毎の18ビツト画像データを3ビツト毎に区分し、それぞれの3ビツトを図4で示す符号化変換表としての変換表TBL1に従つて対応付けて4ビツトコードに変換する。

【0035】

続いて、本体21は、18ビツトに対応して得た6つの4ビツトコードを順次直列に並べて24ビツトコードのワードを生成する。これにより、画素毎の画像データは18ビツトから24ビツトに変換されたことになる。ここで、m=18、n=24であり、これは、m<nを満たしている。

因みに、変換表TBL1上の4ビツトコード「0010」、「0011」、「0101」、「0110」、「1001」、「1010」、「1011」及び「1100」は、任意の3ビツトデータとそれぞれ対応付けて良い。

【0036】

次に、水平同期データ又は垂直同期データが1である(以下、これを同期データが活性であるという)ときを説明する。図3に示すように、このときは、水平同期データだけが論理「1」である状態と、水平同期データ及び垂直同期データが同時に論理「1」である状態とが存在する。

【0037】

同期データが活性であるとき、本体21は、符号化回路25においてn−m=6ビツトコードでなるヘツダの後に、18ビツト画素データを順次並べて24ビツトコードを生成する。水平同期データだけが論理「1」であるとき、本体21は、符号化回路25においてヘツダをビツト列「100000」で構成する。また両方の同期データが論理「1」であるとき、本体21は、符号化回路25においてヘツダをビツト列「011111」で構成する。

【0038】

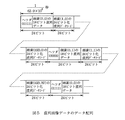

これにより、ヘツダには論理「0」又は論理「1」が5個連続した特定ビツト列が含まれていることになる。従つて、k=5となり、これは、k<n−mを満たしている。このようにして図5に示すように、本体21は、18ビツト画像データをヘツダと共に全て24ビツトコードに変換して順次連結し、画素毎の画像データが途切れない直列のデータコードS60を生成する。

【0039】

次に、図5に示す直列のデータコードS60が、上述した第1の条件〜第4の条件を満たしていることを説明する。まず、直列のデータコードS60を構成する1024ワードのうち、同期データが不活性であるときに対応したワードが圧倒的な比率(1023/1024)を占めることが分かる。図4に示した変換表TBL1では、4ビツトコードのデータ遷移が少なくとも1回発生している。これにより、直列のデータコードS60は、全体として最低25%の確率でデータ遷移を発生させてクロツクを容易に抽出することができ、第1の条件を満足させている。

【0040】

また変換表TBL1の4ビツトコードで最も論理「1」又は論理「0」に偏つたコードでも論理「1」と論理「0」との比は1:3である。これにより、画像データが特定の4ビツトコードに全て変換されても、論理「1」と論理「0」との比は1:3〜3:1に限定される。従つて、データコードS60は、直流レベルを容易に再生することができ、第2の条件を満足させている。

【0041】

次に、変換表TBL1上の4ビツトコードは、いずれをどの順序で組合せて直列に並べても論理「1」がk=5個以上連続することも、論理「0」がk=5個以上連続することも無い。これにより、24ビツトコードの先頭6ビツトから論理「1」又は論理「0」が5個連続した特定ビツト列を検出したとき、液晶表示装置23は、ヘツダが挿入されて同期データが活性であるタイミングを伝送されたと判断することができる。

【0042】

従つて、液晶表示装置23は、画素の画像データを中断することなく、このヘツダを、直列のデータコードS60の1ワード=24ビツトの区切りを認識してnビツト直列コードをmビツト並列の画像データS61〜S78に戻すためのワード同期を確立する基準として使用することができる。また液晶表示装置23は、ヘツダを受信しているときも画素の画像データを中断することがないことにより、画素の画像データを常に安定して受信することができる。

伝送中に画像データが途切れても、液晶表示装置23は、特定ビツト列を検出することによつて、新しい水平走査線の同期タイミングを容易に得ることができる。従つて、データコードS60は、第3の条件を満足させている。

【0043】

また、データコードS60のワード長さが全て同一であることにより、ヘツダのワードと画像データのワードとを別個にカウントする必要がなく、ワードをカウントする回路を簡易に構成することができる。

【0044】

因みに、同期データが活性であるとき、ヘツダに続いて、変換されていない18ビツトの画像データが伝送される。この18ビツトの画像データによつて、偶然論理「1」が5個以上連続したり、論理「0」が5個以上連続することがあり得る。このため、同期データ検出回路28においてヘツダ内の特定ビツト列を一度検出した後、少なくとも次のワードに切り換わる迄、同期データ検出回路28の検出機能を停止して、同期データが活性であるタイミングの誤検出を防止することができる。

【0045】

最後に、データコードS60は、画素毎のデータが元の画像データに比して6ビツト増加している。このときのデータコードS60の伝送レートは、62.9×106 ×24=1.51×109 ビツト/秒となる。一方、元の画像データの伝送レートは、62.9×106 ×18=1.13×109 〔ビツト/秒〕となる。データコードS60と元の画像データとの伝送レートの比は1.33となり、元データの1.4 倍を越えない。この比は、ハードウエアの負担の観点から、実際上、許容される。これにより、データコードS60は第4の条件を満足させている。

【0046】

(3)実施例の効果

以上の構成によれば、n>m及びk<n−mとして、同期データを送信しないときは、画素毎のmビツトの画像データを、いかなる組み合わせで順次直列に送信しても同一論理ビツトがk個以上連続しないnビツトコードS60に変換してこれを直列に送信し、同期データを送信するときは、画素のmビツトの画像データをコード化しないで直接直列に並べ、これに同一論理ビツトがk個連続した特定ビツト列を含むn−mビツトを直列に並べたヘツダを付加することにより、並列の画像データの送受信を中断させずに並列の画像データ及び同期データを1つの伝送ケーブル22によつて送受信することができる。

【0047】

また液晶表示装置23への画像データの伝送距離を並列デジタルやアナログで伝送する場合に比して一段と大きくすることができる。

さらに低コストで小さなコネクタと、1本だけであることによる一段と大きな柔軟性に富んだ伝送ケーブルとによつて画像データを伝送することができる。

【0048】

(4)他の実施例

なお上述の実施例においては、m=18、n=24、k=5及びj=4とする場合について述べたが、本発明はこれに限らず、n、m、k及びjをn>m、k<n−m及びj<kとなる条件下で任意の数に設定しても良い。

【0049】

また上述の実施例においては、18ビツトから24ビツトコードに変換する際、3ビツトから4ビツトコードに変換し、この4ビツトコードを組合せで24ビツトコードを得る場合について述べたが、本発明はこれに限らず、任意の数のビツトコードを組合せて目的のビツト数のコードを得る場合にも適用できる。

【0050】

さらに上述の実施例においては、液晶表示装置を使用する場合について述べたが、本発明はこれに限らず、画像をデジタル信号で制御する任意の画像表示装置、例えばプラズマデイスプレイを使用する場合にも適用できる。

【0051】

さらに上述の実施例においては、直列のデータコードS60を伝送ケーブル13によつて伝送する場合について述べたが、本発明はこれに限らず、直列化した画像データを電波や赤外線で伝送する場合にも適用できる。

【0052】

【発明の効果】

上述のように本発明によれば、送信側から直列送信されるnビツトのデータには常に画像データが含まれるので、これにより受信側は送信側から直列受信したnビツトのデータから常に画像データを得ることができ、かくして画像データを安定して受信することができる画像データ送信方法及び画像データ受信方法を実現することができる。

【図面の簡単な説明】

【図1】本発明による画像データ送信方法及び画像データ受信方法の一実施例による画像表示システムの構成を示す略線的ブロツク図である。

【図2】同期データ検出回路の説明に供する接続図である。

【図3】画素毎の並列画像データ及び同期データのタイミングを示すタイミング図である。

【図4】3ビツトデータと4ビツトコードとを対応付けた変換表を示す図表である。

【図5】直列画像データのデータ配列を示す略線図である。

【図6】従来の画像データ伝送方法を示す略線図である。

【図7】従来の画像データ伝送方法を示す略線図である。

【図8】並列伝送によるスキユー及びクロストークを示す波形図である。

【図9】画素配置及び従来の直列化による画像データの配列を示す略線図である。

【符号の説明】

1、10……液晶表示装置、2〜4……デジタルアナログコンバータ、5〜7……アナログデジタルコンバータ、8、11、27……画像制御回路、9、12、24……画像表示部、13、22……伝送ケーブル、20……画像表示システム、21……本体、23……液晶表示装置、25……符号化回路、26……復号化回路、28……同期データ検出回路、29〜32……Dフリツプフロツプ、33……アンド回路、34……ナンド回路、35……オア回路。

Claims (8)

- mビツト単位の画像データを送信するための画像データ送信方法であつて、

上記画像データの同期タイミングを設定させるための同期データを送信せずにmビツトの上記画像データを送信する場合には、mビツトの上記画像データを変換することによりn(但しn>m)ビツトの変換後データを生成し、当該生成した変換後データを直列送信する第1のステツプと、

上記同期データとmビツトの上記画像データとを送信する場合には、mビツトの上記画像データに対して上記同期データを示すn−mビツトの直列コードを付加することによりnビツトの付加後データを生成し、当該生成した付加後データを直列送信する第2のステツプと

を有し、

上記第1のステツプでは、

mビツトのデータと、いかなる組み合わせで順次直列送信されても同一論理ビツトがk(但しk<n−m)個以上連続しないように選択されたnビツトのデータとを対応付けてなる変換表に基づいて、mビツトの上記画像データを変換することによりnビツトの上記変換後データを生成し、

上記第2のステツプでは、

mビツトの上記画像データに対して、上記同一論理ビツトがk個以上連続した特定ビツト列を含む上記直列コードを付加することにより、nビツトの上記付加後データを生成する

ことを特徴とする画像データ送信方法。 - 上記変換表は、

上記mビツトのデータと上記nビツトのデータとをそれぞれ分割して対応付けている

ことを特徴とする請求項1に記載の画像データ送信方法。 - 上記直列コードは、直列化された上記画像データの前に対して付加される

ことを特徴とする請求項1に記載の画像データ送信方法。 - 上記同期データは、垂直同期データ及び水平同期データである

ことを特徴とする請求項1に記載の画像データ送信方法。 - mビツト単位の画像データを受信するための画像データ受信方法であつて、

伝送路を介して直列受信したn(但しn>m)ビツトの受信データから、上記画像データの同期タイミングを設定させるための同期データを示すn−mビツトの直列コードを検出する第1のステツプと、

上記第1のステツプによつてnビツトの上記受信データから上記直列コードを検出した場合には、上記同期タイミングを設定すると共にnビツトの上記受信データから上記直列コードを除くことによりmビツトの上記画像データを得る第2のステツプと、

上記第1のステツプによつてnビツトの上記受信データから上記直列コードを検出しない場合には、nビツトの上記受信データを変換することによりmビツトの上記画像データを得る第3のステツプと

を有し、

上記第1のステツプでは、

nビツトの上記受信データから、同一論理ビツトがk(但しk<n−m)個以上連続した特定ビツト列が含まれる上記直列コード中の上記特定ビツト列を検出することにより上記直列コードを検出し、

上記第3のステツプでは、

いかなる組み合わせで順次直列送信されても上記同一論理ビツトがk個以上連続しない ように選択されたnビツトのデータと、mビツトのデータとを対応付けてなる変換表に基づいて、nビツトの上記受信データを変換することによりmビツトの上記画像データを得る

ことを特徴とする画像データ受信方法。 - 上記変換表は、

上記mビツトのデータと上記nビツトのデータとをそれぞれ分割して対応付けている

ことを特徴とする請求項5に記載の画像データ受信方法。 - 上記直列コードが検出された上記受信データは、直列化された上記画像データの前に対して上記直列コードが付加されてなる

ことを特徴とする請求項5に記載の画像データ受信方法。 - 上記同期データは、垂直同期データ及び水平同期データである

ことを特徴とする請求項5に記載の画像データ受信方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP34778095A JP3661890B2 (ja) | 1995-12-15 | 1995-12-15 | 画像データ送信方法及び画像データ受信方法 |

| US08/762,449 US5828326A (en) | 1995-12-15 | 1996-12-09 | Method of encoding and decoding for data transmission |

| DE1996631742 DE69631742T2 (de) | 1995-12-15 | 1996-12-13 | Kodierungs- und Dekodierungsverfahren für Datenübertragung |

| EP19960402731 EP0781054B1 (en) | 1995-12-15 | 1996-12-13 | Method of encoding and decoding for data transmission |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP34778095A JP3661890B2 (ja) | 1995-12-15 | 1995-12-15 | 画像データ送信方法及び画像データ受信方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH09168147A JPH09168147A (ja) | 1997-06-24 |

| JP3661890B2 true JP3661890B2 (ja) | 2005-06-22 |

Family

ID=18392532

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP34778095A Expired - Lifetime JP3661890B2 (ja) | 1995-12-15 | 1995-12-15 | 画像データ送信方法及び画像データ受信方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US5828326A (ja) |

| EP (1) | EP0781054B1 (ja) |

| JP (1) | JP3661890B2 (ja) |

| DE (1) | DE69631742T2 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100293523B1 (ko) | 1998-02-25 | 2001-09-17 | 구본준, 론 위라하디락사 | 액정표시장치 |

| JP4250867B2 (ja) * | 1998-10-06 | 2009-04-08 | ソニー株式会社 | 符号化装置および方法、復号装置および方法並びに記録媒体 |

| JP3777884B2 (ja) * | 1999-07-23 | 2006-05-24 | セイコーエプソン株式会社 | 表示用ドライバic及びそれを用いた電子機器 |

| US6452591B1 (en) * | 1999-08-09 | 2002-09-17 | Ati International Srl | Method and apparatus for a data transmitter |

| US6703949B2 (en) * | 2001-10-11 | 2004-03-09 | Sun Microsystems, Inc. | Method and apparatus for facilitating balanced bundles of electrical signals |

| AU2003271630A1 (en) * | 2003-09-22 | 2005-04-11 | Inova Semiconductors Gmbh | System and method for forming a bidirectional multimedia link |

| JP4254492B2 (ja) | 2003-11-07 | 2009-04-15 | ソニー株式会社 | データ伝送システム、データ送信装置、データ受信装置、データ伝送方法、データ送信方法及びデータ受信方法 |

| ES2545905T3 (es) | 2004-04-16 | 2015-09-16 | Thine Electronics, Inc. | Circuito de transmisión, circuito de recepción, método y sistema de transmisión de datos |

| JP4698213B2 (ja) * | 2004-12-09 | 2011-06-08 | 富士通コンポーネント株式会社 | 遠隔再生システム |

| US20070200858A1 (en) * | 2006-02-28 | 2007-08-30 | Aten International Co., Ltd | KVM switch and a computer switching method |

| JP2010147943A (ja) * | 2008-12-19 | 2010-07-01 | Sony Corp | 情報処理装置、及び信号伝送方法 |

| EP2429114B1 (en) * | 2010-09-13 | 2013-03-27 | Alcatel Lucent | Coupling arrangement for phantom-mode transmission |

| JP5592825B2 (ja) * | 2011-03-29 | 2014-09-17 | ルネサスエレクトロニクス株式会社 | 表示装置用データ伝送システム、表示装置用データ伝送方法及び表示装置 |

| WO2013023658A2 (de) * | 2011-08-16 | 2013-02-21 | Silicon Line Gmbh | Schaltungsanordnung und verfahren zum kodieren und/oder dekodieren |

| KR101427552B1 (ko) * | 2014-03-31 | 2014-08-07 | (주) 넥스트칩 | 영상 신호 전송 방법 및 장치 |

| JP7510371B2 (ja) * | 2021-03-12 | 2024-07-03 | 株式会社東芝 | 信号送信装置及び信号送信方法 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3689699A (en) * | 1971-04-12 | 1972-09-05 | Gen Electric | Synchronizing system |

| US4247936A (en) * | 1979-06-06 | 1981-01-27 | Minnesota Mining And Manufacturing Company | Digital communications system with automatic frame synchronization and detector circuitry |

| DE3407832C2 (de) * | 1983-03-03 | 1994-08-11 | Matsushita Electric Industrial Co Ltd | Verfahren zum Kodieren und Dekodieren binärer Daten |

| JPH0661156B2 (ja) * | 1983-05-21 | 1994-08-10 | ソニー株式会社 | エラ−訂正のための符号化方法 |

| US4599722A (en) * | 1984-04-03 | 1986-07-08 | Canadian Patents And Development Limited-Societe Canadienne Des Brevets Et D'exploitation Limitee | Apparatus for encoding and decoding digital data to permit error correction |

| EP0178813B1 (en) * | 1984-10-01 | 1993-08-18 | Matsushita Electric Industrial Co., Ltd. | Method and apparatus for encoding binary data |

| JPH07118657B2 (ja) * | 1985-04-15 | 1995-12-18 | 三菱電機株式会社 | 2進デ−タ符号化及び復号化方式 |

| US4779712A (en) * | 1986-09-15 | 1988-10-25 | General Electric Company | Equipoise assembly |

| JPH0434669A (ja) * | 1990-05-31 | 1992-02-05 | Toshiba Corp | 画像処理方式 |

| DE4020963A1 (de) * | 1990-06-30 | 1992-01-02 | Philips Patentverwaltung | Uebertragungseinrichtung mit einem blockcode-codiertem hauptkanal und mit einem zusatzkanal |

| JP3355666B2 (ja) * | 1992-10-22 | 2002-12-09 | ソニー株式会社 | 変調回路 |

| DE4415288A1 (de) * | 1994-04-30 | 1995-11-02 | Ant Nachrichtentech | Verfahren zur Aufbereitung und Wiedergewinnung von Daten sowie Anordnung hierzu |

-

1995

- 1995-12-15 JP JP34778095A patent/JP3661890B2/ja not_active Expired - Lifetime

-

1996

- 1996-12-09 US US08/762,449 patent/US5828326A/en not_active Expired - Lifetime

- 1996-12-13 EP EP19960402731 patent/EP0781054B1/en not_active Expired - Lifetime

- 1996-12-13 DE DE1996631742 patent/DE69631742T2/de not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| EP0781054B1 (en) | 2004-03-03 |

| DE69631742T2 (de) | 2005-02-10 |

| DE69631742D1 (de) | 2004-04-08 |

| EP0781054A3 (en) | 1998-07-01 |

| EP0781054A2 (en) | 1997-06-25 |

| JPH09168147A (ja) | 1997-06-24 |

| US5828326A (en) | 1998-10-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3661890B2 (ja) | 画像データ送信方法及び画像データ受信方法 | |

| JP3371965B2 (ja) | シリアルリンクを介して多重データ信号を送信するためのシステムおよび方法 | |

| JP3352600B2 (ja) | 表示装置 | |

| KR100875340B1 (ko) | 데이터 비활성 기간에 부채널 데이터를 전송하는 방법 및시스템 | |

| KR20030040002A (ko) | 스큐 조정 회로 및 스큐 조정 방법과 데이터 동기 회로 및데이터 동기 방법 | |

| KR100586669B1 (ko) | 전송 시스템 | |

| US7102629B2 (en) | System and method for digital video signal transmission | |

| US6018305A (en) | Serial to parallel conversion apparatus with means to adjust the phase of a plurality of divided clock signals | |

| US5021880A (en) | Digital video signal compression | |

| EP0548649B1 (en) | Parallel DS3 AIS/Idle code generator | |

| CN116033213B (zh) | 图像信号的处理方法、装置、存储介质及电子装置 | |

| JP4781688B2 (ja) | 映像信号伝送方法及び映像信号伝送装置 | |

| US20040153936A1 (en) | Data recovery circuit and method and data receiving system using the same | |

| JP2004135344A (ja) | アドレスサブサンプリング装置及びその方法並びにイメージセンサ及びイメージセンサのアドレスサブサンプリング方法 | |

| JP3192913B2 (ja) | Yuv/rgb変換器 | |

| US7456853B1 (en) | Analog interface structures and methods that reduce display artifacts in digital displays | |

| JPH0758971B2 (ja) | 通信制御装置 | |

| JPH0637854A (ja) | データ伝送装置 | |

| JPH0595566A (ja) | デイジタル信号伝送装置 | |

| KR910007543B1 (ko) | Pip의 입력데이타 변환회로 | |

| KR850001689B1 (ko) | 디지탈 정보 인코딩 방법 | |

| JP3242491B2 (ja) | 誤り訂正装置 | |

| JPH02100436A (ja) | ブロック同期方式 | |

| JPH02156381A (ja) | イメージデータ転送方式 | |

| JPH0746143A (ja) | 並列直列変換回路の動作制御方式及び直列並列変換回路の動作制御方式 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040806 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040927 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20041224 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050207 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050304 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050317 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080401 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090401 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100401 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100401 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110401 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120401 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130401 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130401 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140401 Year of fee payment: 9 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |